Digital Systems Design 2 VHDL State Machines Veton

- Slides: 19

Digital Systems Design 2 VHDL & State Machines Veton Këpuska

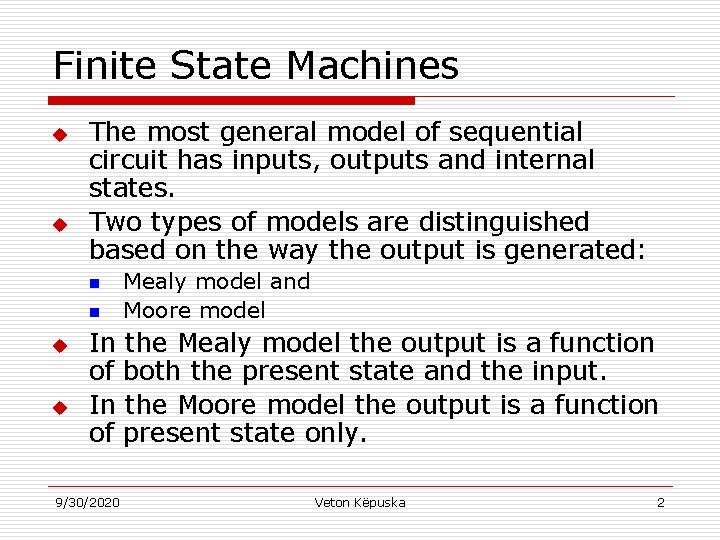

Finite State Machines u u The most general model of sequential circuit has inputs, outputs and internal states. Two types of models are distinguished based on the way the output is generated: n n u u Mealy model and Moore model In the Mealy model the output is a function of both the present state and the input. In the Moore model the output is a function of present state only. 9/30/2020 Veton Këpuska 2

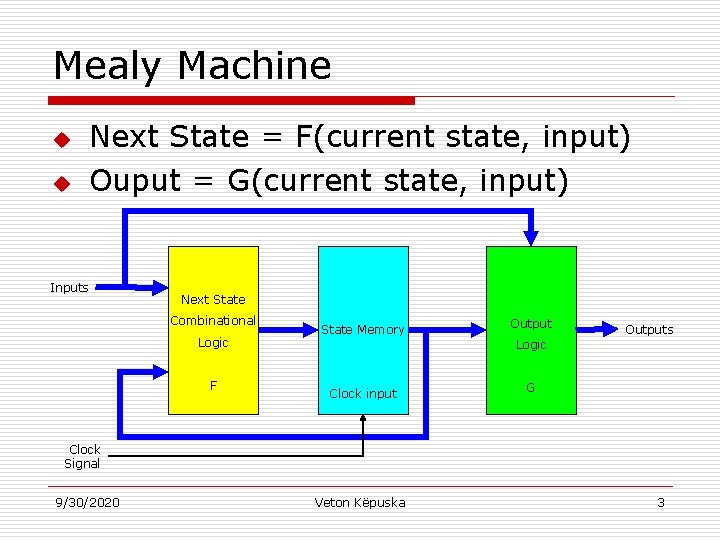

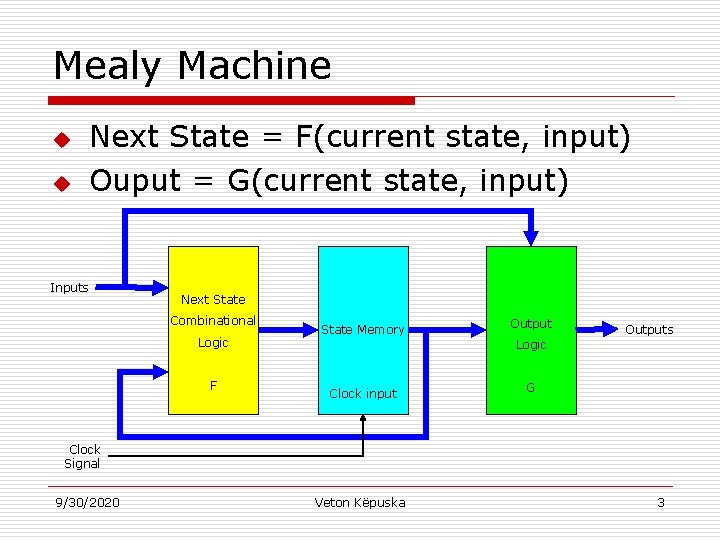

Mealy Machine u u Next State = F(current state, input) Ouput = G(current state, input) Inputs Next State Combinational Logic F State Memory Outputs Logic Clock input G Clock Signal 9/30/2020 Veton Këpuska 3

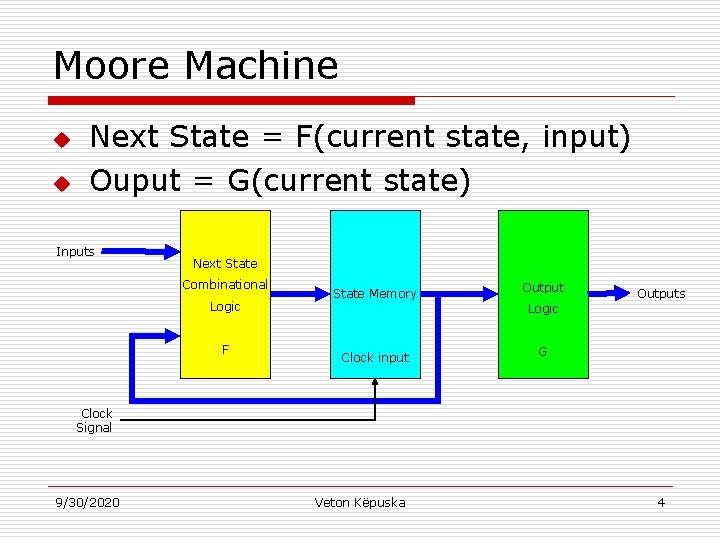

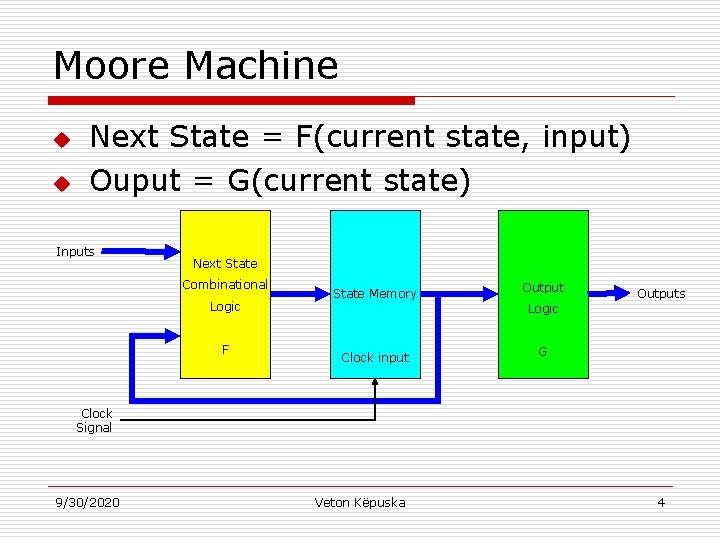

Moore Machine u u Next State = F(current state, input) Ouput = G(current state) Inputs Next State Combinational Logic F State Memory Outputs Logic Clock input G Clock Signal 9/30/2020 Veton Këpuska 4

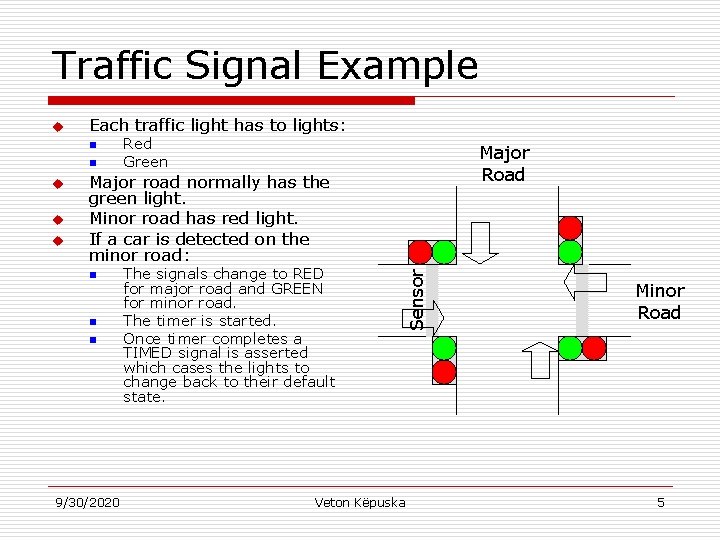

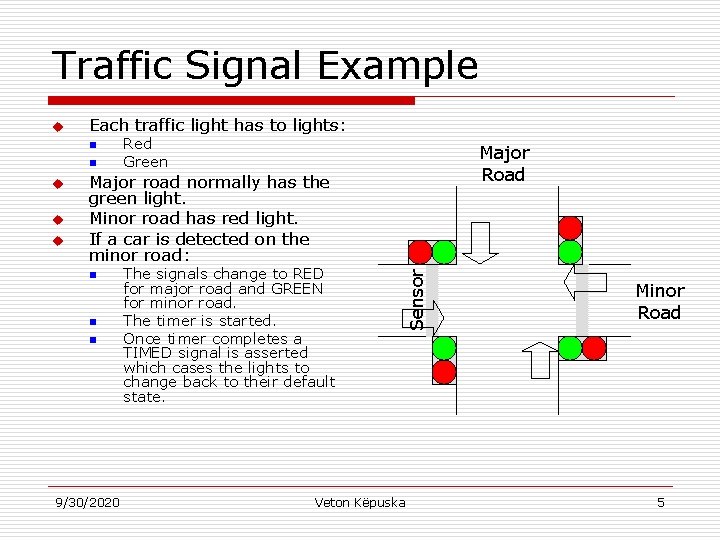

Traffic Signal Example Each traffic light has to lights: n n u u u Red Green Major Road Major road normally has the green light. Minor road has red light. If a car is detected on the minor road: n n n 9/30/2020 The signals change to RED for major road and GREEN for minor road. The timer is started. Once timer completes a TIMED signal is asserted which cases the lights to change back to their default state. Veton Këpuska Sensor u Minor Road 5

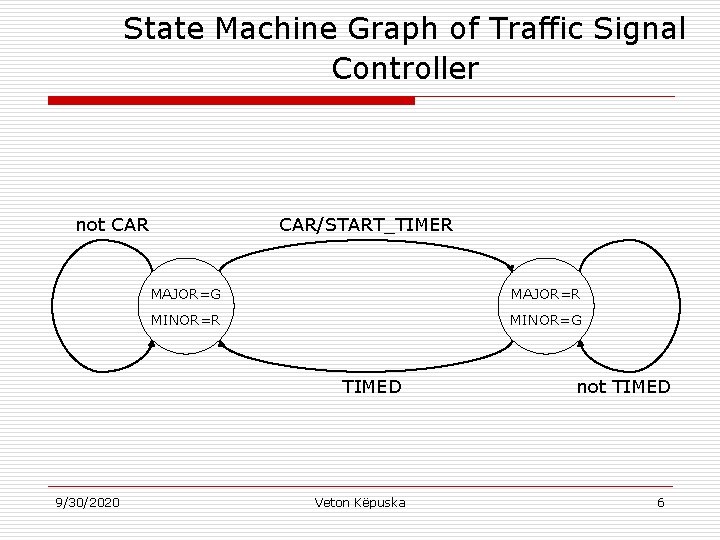

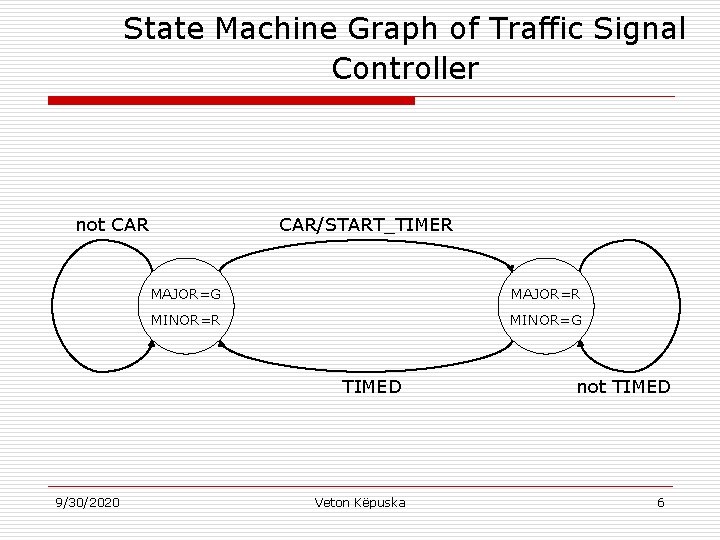

State Machine Graph of Traffic Signal Controller not CAR/START_TIMER MAJOR=G MAJOR=R MINOR=G TIMED 9/30/2020 Veton Këpuska not TIMED 6

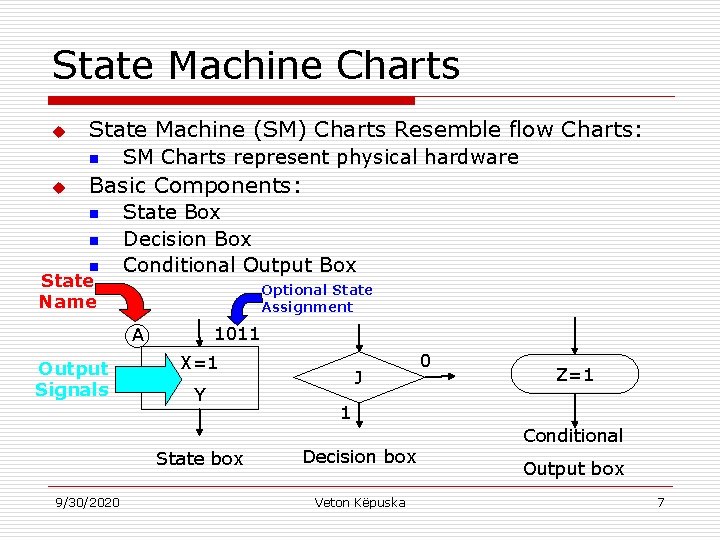

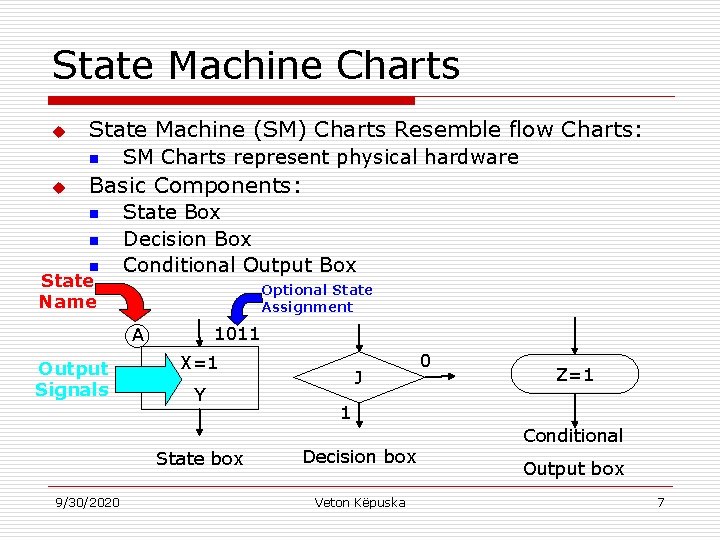

State Machine Charts u State Machine (SM) Charts Resemble flow Charts: n u SM Charts represent physical hardware Basic Components: n n n State Name State Box Decision Box Conditional Output Box Optional State Assignment 1011 A Output Signals X=1 Y State box 9/30/2020 J 0 Z=1 1 Decision box Veton Këpuska Conditional Output box 7

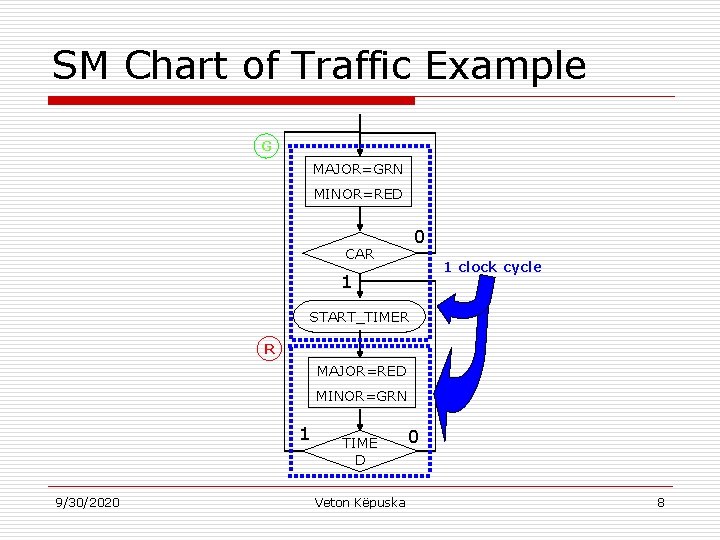

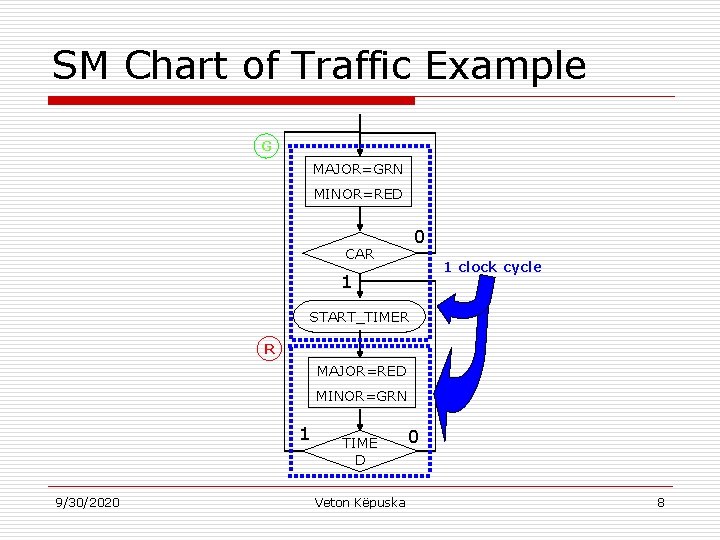

SM Chart of Traffic Example G MAJOR=GRN MINOR=RED 0 CAR 1 clock cycle 1 START_TIMER R MAJOR=RED MINOR=GRN 1 9/30/2020 TIME D Veton Këpuska 0 8

Topics from Logic Design u u u Synthesis from SM Charts State Assignment State Minimization 9/30/2020 Veton Këpuska 9

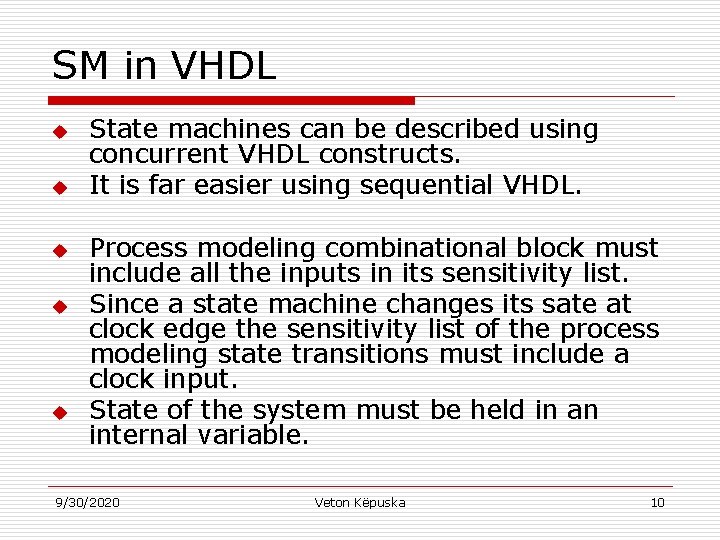

SM in VHDL u u u State machines can be described using concurrent VHDL constructs. It is far easier using sequential VHDL. Process modeling combinational block must include all the inputs in its sensitivity list. Since a state machine changes its sate at clock edge the sensitivity list of the process modeling state transitions must include a clock input. State of the system must be held in an internal variable. 9/30/2020 Veton Këpuska 10

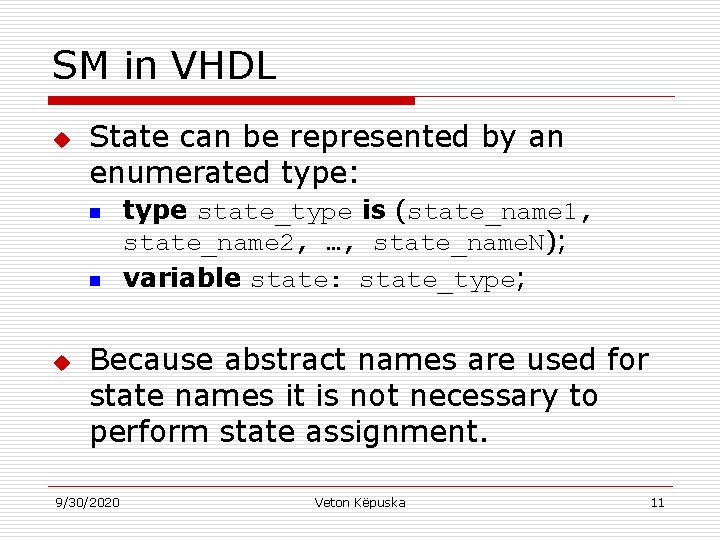

SM in VHDL u State can be represented by an enumerated type: n n u type state_type is (state_name 1, state_name 2, …, state_name. N); variable state: state_type; Because abstract names are used for state names it is not necessary to perform state assignment. 9/30/2020 Veton Këpuska 11

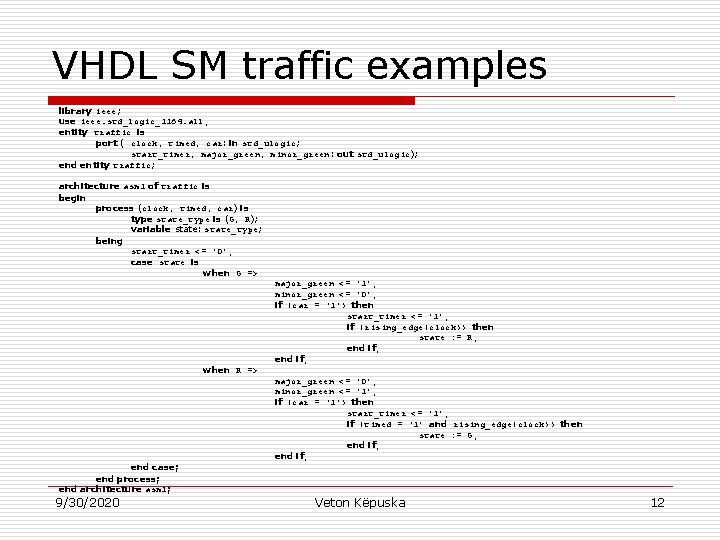

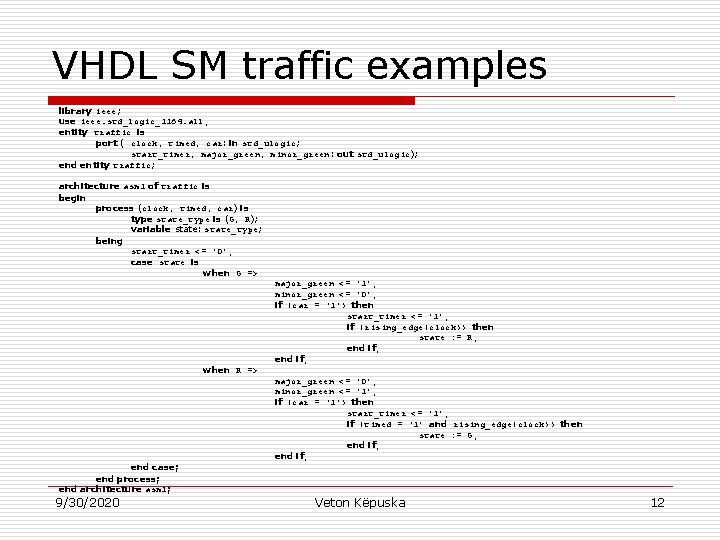

VHDL SM traffic examples library ieee; use ieee. std_logic_1164. all; entity traffic is port ( clock, timed, car: in std_ulogic; start_timer, major_green, minor_green: out std_ulogic); end entity traffic; architecture asm 1 of traffic is begin process (clock, timed, car) is type state_type is (G, R); variable state: state_type; being start_timer <= ‘ 0’; case state is when G => when R => end case; end process; end architecture asm 1; 9/30/2020 major_green <= ‘ 1’; minor_green <= ‘ 0’; if (car = ‘ 1’) then start_timer <= ‘ 1’; if (rising_edge(clock)) then state : = R; end if; major_green <= ‘ 0’; minor_green <= ‘ 1’; if (car = ‘ 1’) then start_timer <= ‘ 1’; if (timed = ‘ 1’ and rising_edge(clock)) then state : = G; end if; Veton Këpuska 12

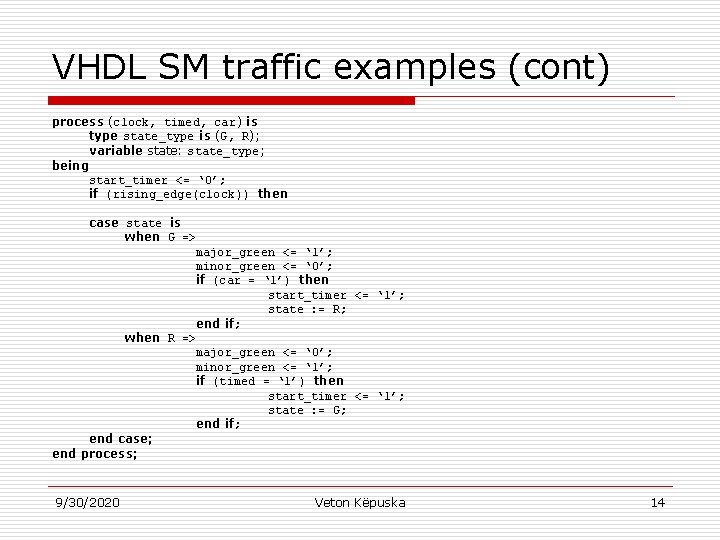

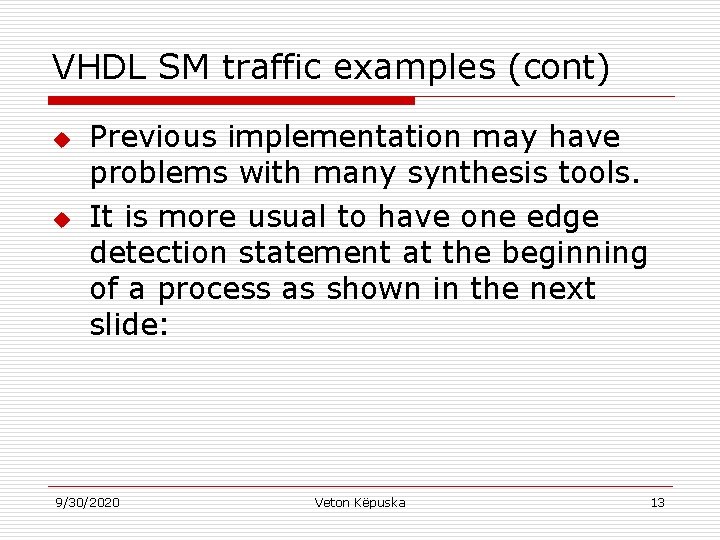

VHDL SM traffic examples (cont) u u Previous implementation may have problems with many synthesis tools. It is more usual to have one edge detection statement at the beginning of a process as shown in the next slide: 9/30/2020 Veton Këpuska 13

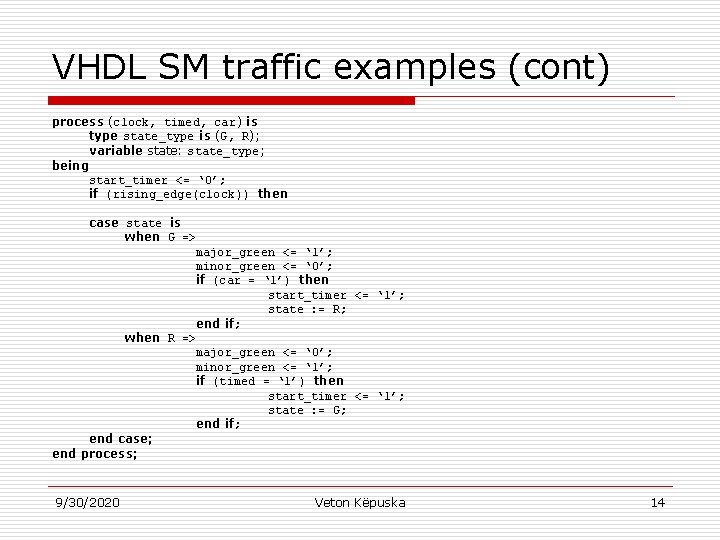

VHDL SM traffic examples (cont) process (clock, timed, car) is type state_type is (G, R); variable state: state_type; being start_timer <= ‘ 0’; if (rising_edge(clock)) then case state is when G => major_green <= ‘ 1’; minor_green <= ‘ 0’; if (car = ‘ 1’) then start_timer <= ‘ 1’; state : = R; end if; when R => major_green <= ‘ 0’; minor_green <= ‘ 1’; if (timed = ‘ 1’) then start_timer <= ‘ 1’; state : = G; end if; end case; end process; 9/30/2020 Veton Këpuska 14

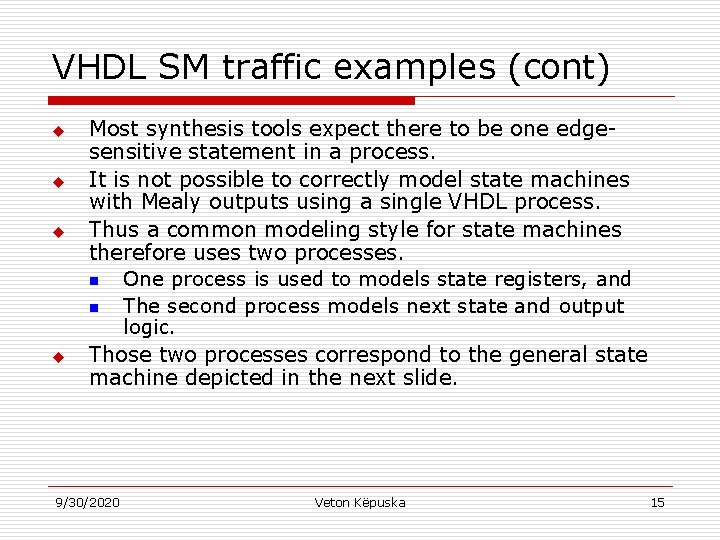

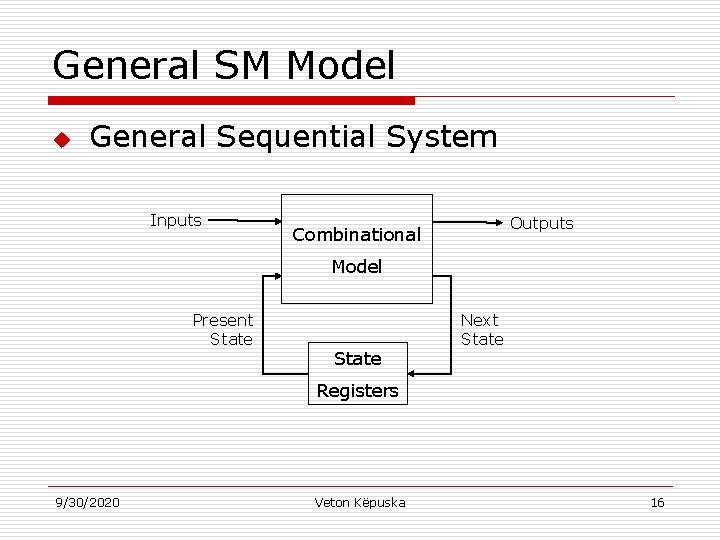

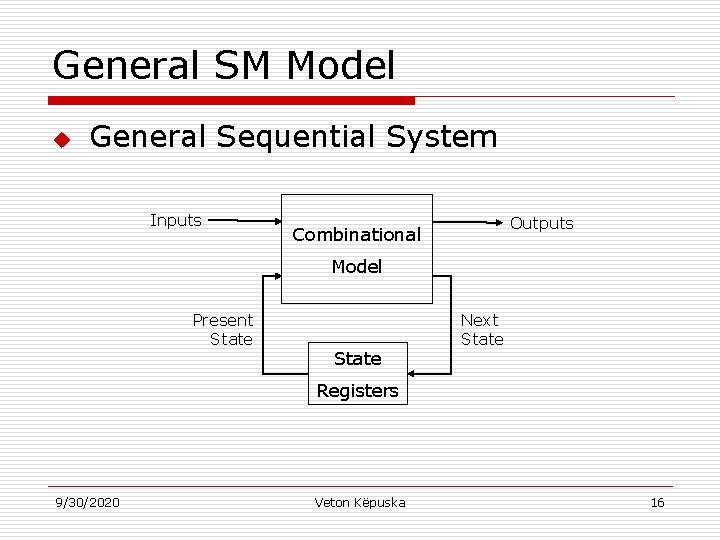

VHDL SM traffic examples (cont) u u Most synthesis tools expect there to be one edgesensitive statement in a process. It is not possible to correctly model state machines with Mealy outputs using a single VHDL process. Thus a common modeling style for state machines therefore uses two processes. n One process is used to models state registers, and n The second process models next state and output logic. Those two processes correspond to the general state machine depicted in the next slide. 9/30/2020 Veton Këpuska 15

General SM Model u General Sequential System Inputs Outputs Combinational Model Present State Next State Registers 9/30/2020 Veton Këpuska 16

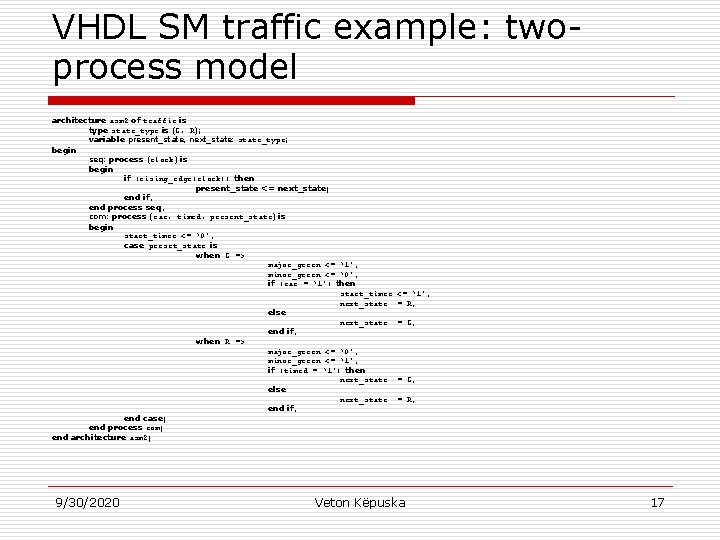

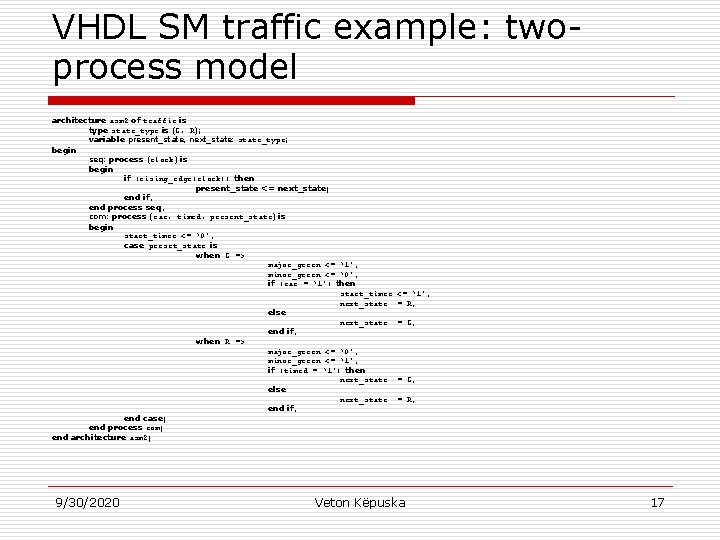

VHDL SM traffic example: twoprocess model architecture asm 2 of traffic is type state_type is (G, R); variable present_state, next_state: state_type; begin seq: process (clock) is begin if (rising_edge(clock)) then present_state <= next_state; end if; end process seq; com: process (car, timed, present_state) is begin start_timer <= ‘ 0’; case preset_state is when G => major_green <= ‘ 1’; minor_green <= ‘ 0’; if (car = ‘ 1’) then start_timer <= ‘ 1’; next_state : = R; else next_state : = G; end if; when R => major_green <= ‘ 0’; minor_green <= ‘ 1’; if (timed = ‘ 1’) then next_state : = G; else next_state : = R; end if; end case; end process com; end architecture asm 2; 9/30/2020 Veton Këpuska 17

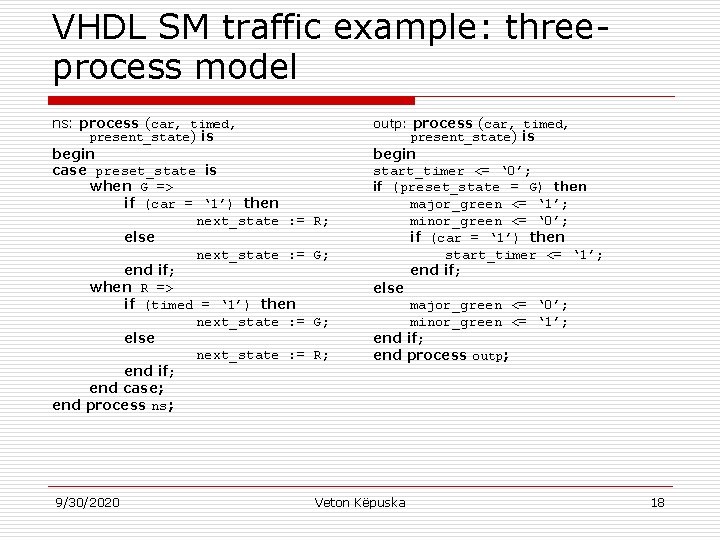

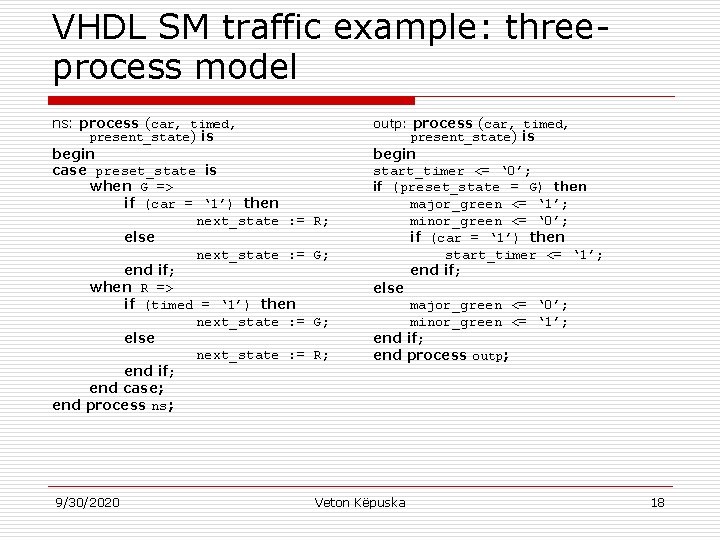

VHDL SM traffic example: threeprocess model ns: process (car, timed, present_state) is begin case preset_state is when G => if (car = ‘ 1’) then next_state : = else next_state : = end if; when R => if (timed = ‘ 1’) then next_state : = else next_state : = end if; end case; end process ns; 9/30/2020 outp: process (car, timed, present_state) is R; G; R; begin start_timer <= ‘ 0’; if (preset_state = G) then major_green <= ‘ 1’; minor_green <= ‘ 0’; if (car = ‘ 1’) then start_timer <= ‘ 1’; end if; else major_green <= ‘ 0’; minor_green <= ‘ 1’; end if; end process outp; Veton Këpuska 18

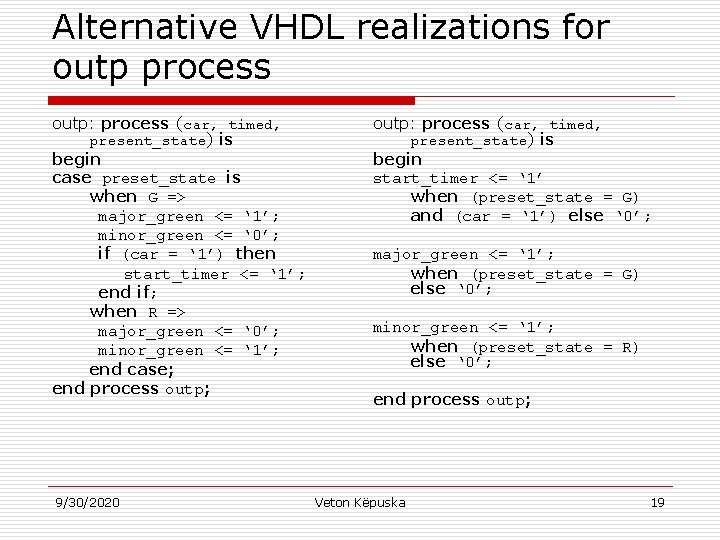

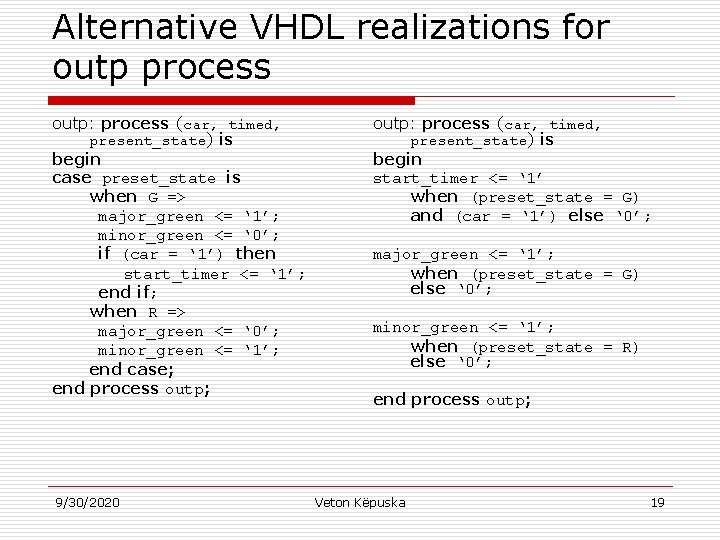

Alternative VHDL realizations for outp process outp: process (car, timed, present_state) is begin case preset_state is when G => major_green <= ‘ 1’; minor_green <= ‘ 0’; if (car = ‘ 1’) then start_timer <= ‘ 1’; end if; when R => major_green <= ‘ 0’; minor_green <= ‘ 1’; end case; end process outp; 9/30/2020 outp: process (car, timed, present_state) is begin start_timer <= ‘ 1’ when (preset_state = G) and (car = ‘ 1’) else ‘ 0’; major_green <= ‘ 1’; when (preset_state = G) else ‘ 0’; minor_green <= ‘ 1’; when (preset_state = R) else ‘ 0’; end process outp; Veton Këpuska 19