Digital System Design Verilog HDL Useful Modeling Techniques

- Slides: 30

Digital System Design Verilog® HDL Useful Modeling Techniques 2005 Verilog HDL Maziar Goudarzi

Today Program l Procedural Continuous Assignment l Overriding Parameters l Conditional Compilation and Execution l Useful System Tasks 2005 Verilog HDL 2

Procedural Continuous Assignment Useful Modeling Techniques 2005 Verilog HDL

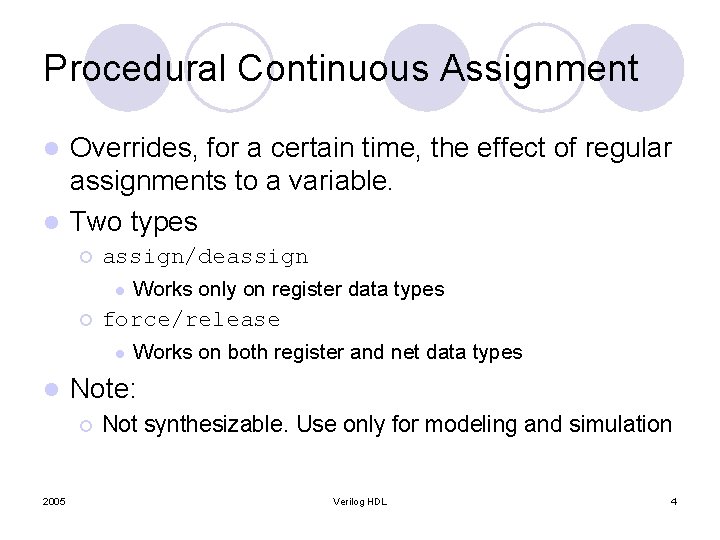

Procedural Continuous Assignment Overrides, for a certain time, the effect of regular assignments to a variable. l Two types l ¡ assign/deassign l ¡ force/release l l Works on both register and net data types Note: ¡ 2005 Works only on register data types Not synthesizable. Use only for modeling and simulation Verilog HDL 4

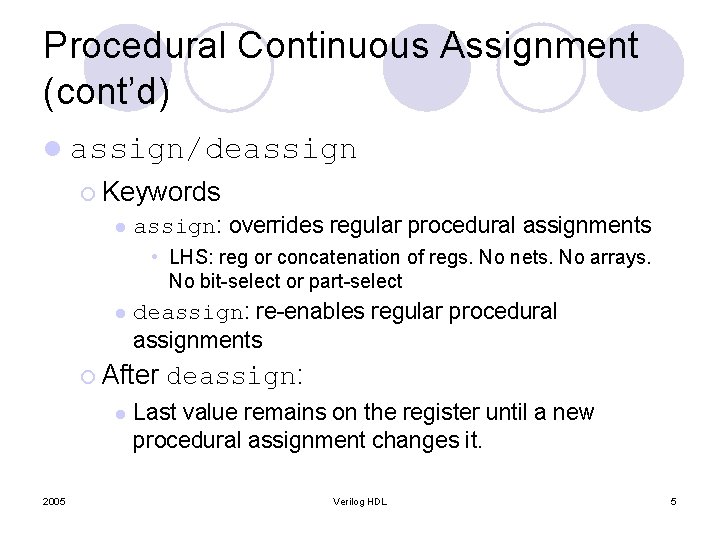

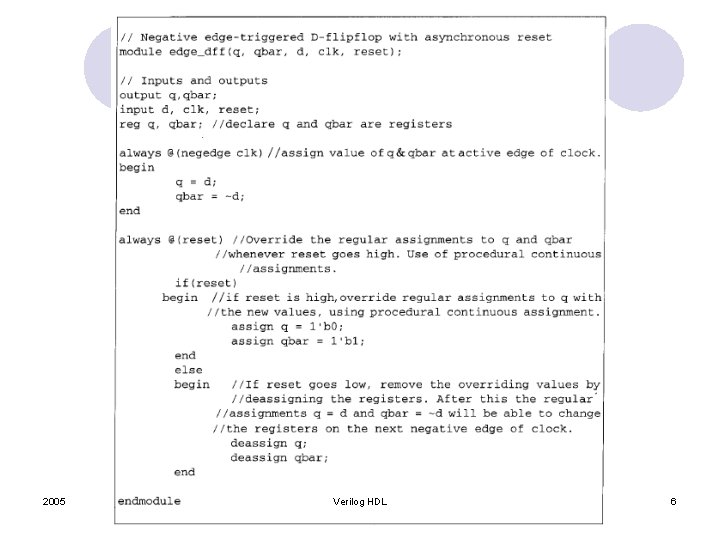

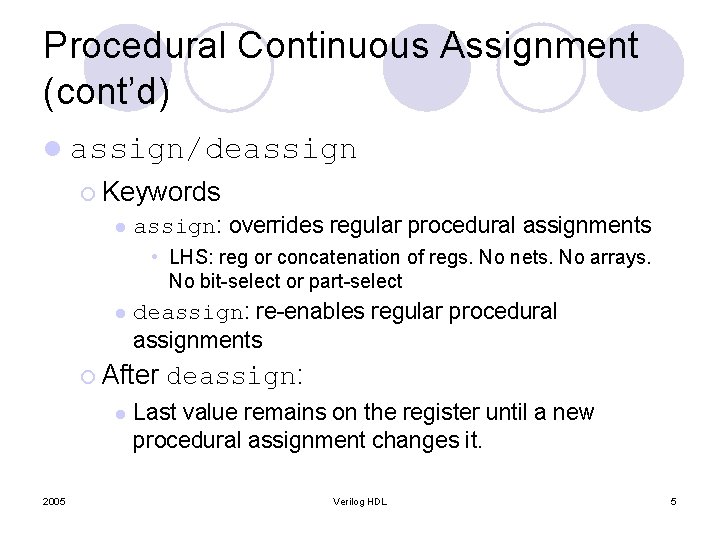

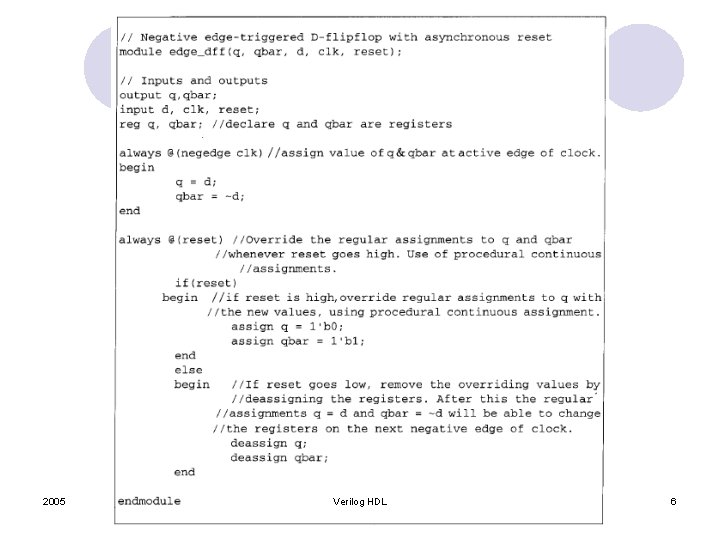

Procedural Continuous Assignment (cont’d) l assign/deassign ¡ Keywords l assign: overrides regular procedural assignments • LHS: reg or concatenation of regs. No nets. No arrays. No bit-select or part-select l deassign: re-enables regular procedural assignments ¡ After l 2005 deassign: Last value remains on the register until a new procedural assignment changes it. Verilog HDL 5

2005 Verilog HDL 6

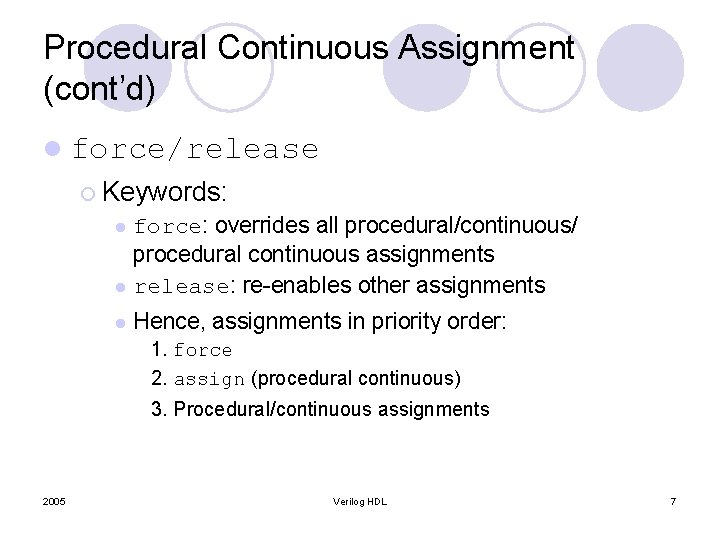

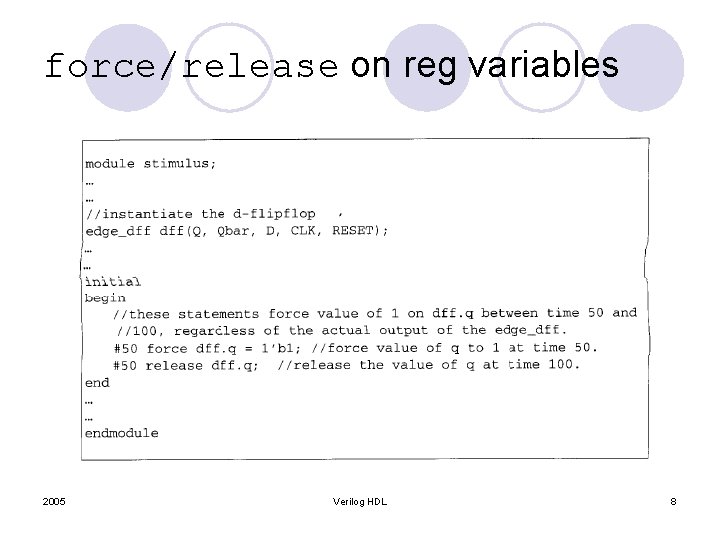

Procedural Continuous Assignment (cont’d) l force/release ¡ Keywords: force: overrides all procedural/continuous/ procedural continuous assignments l release: re-enables other assignments l l Hence, assignments in priority order: 1. force 2. assign (procedural continuous) 3. Procedural/continuous assignments 2005 Verilog HDL 7

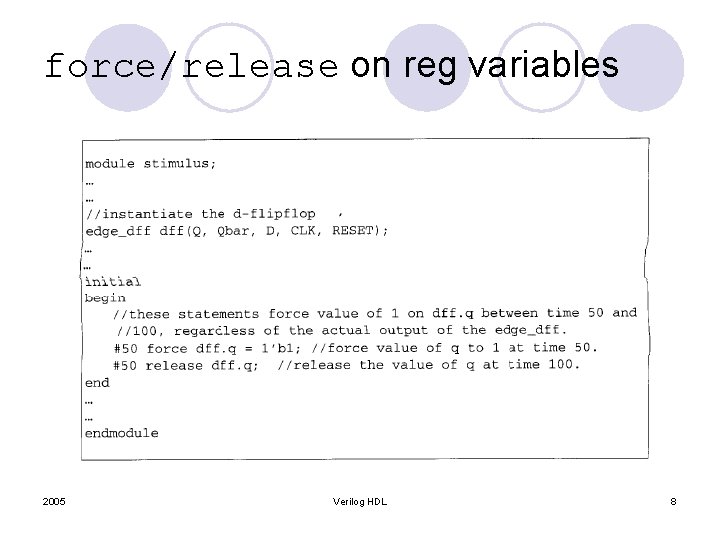

force/release on reg variables 2005 Verilog HDL 8

force/release on nets l 2005 Net value immediately returns to its normal assigned value when released Verilog HDL 9

Overriding Parameters Useful Modeling Techniques 2005 Verilog HDL

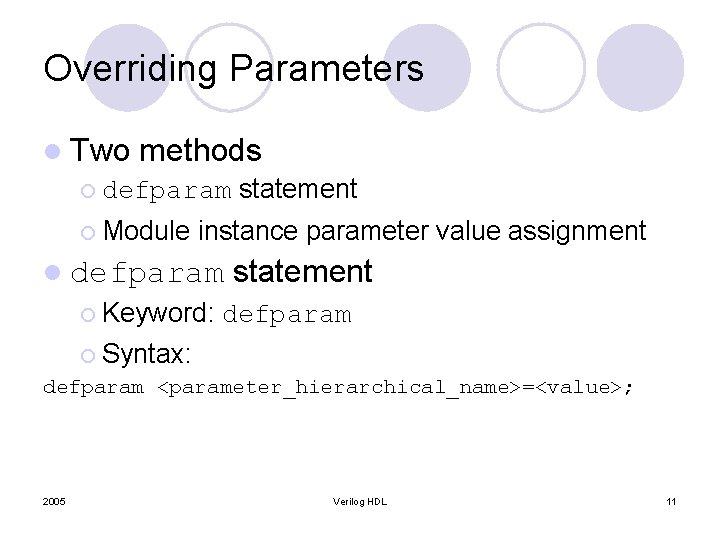

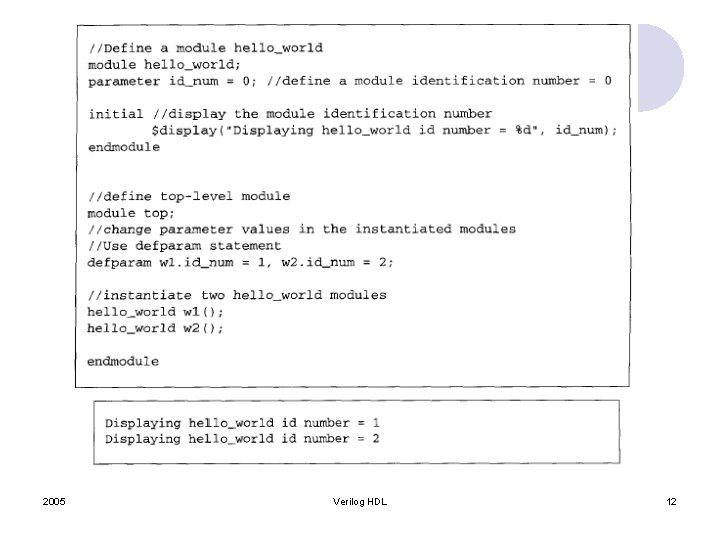

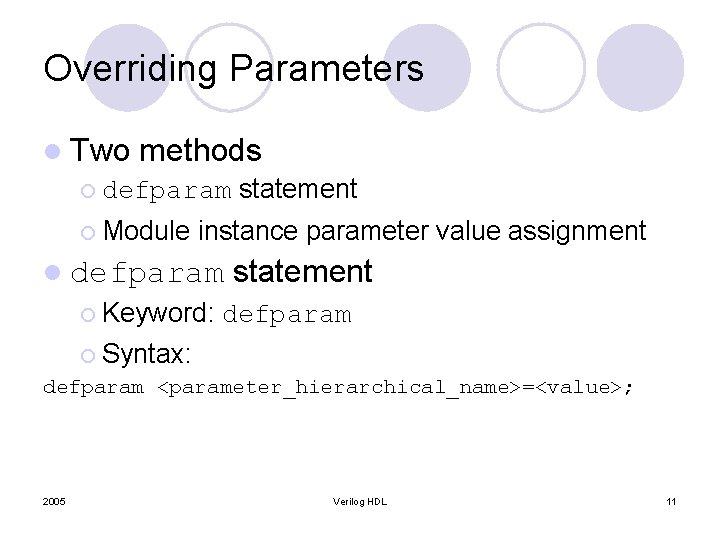

Overriding Parameters l Two methods ¡ defparam statement ¡ Module instance parameter value assignment l defparam ¡ Keyword: statement defparam ¡ Syntax: defparam <parameter_hierarchical_name>=<value>; 2005 Verilog HDL 11

2005 Verilog HDL 12

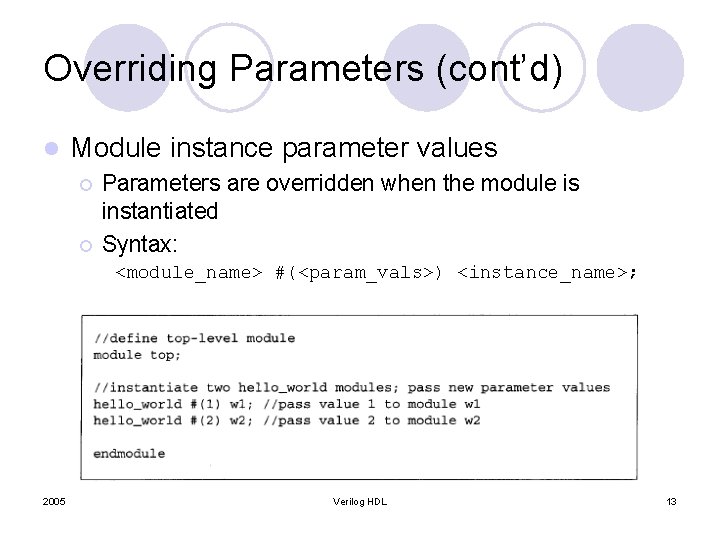

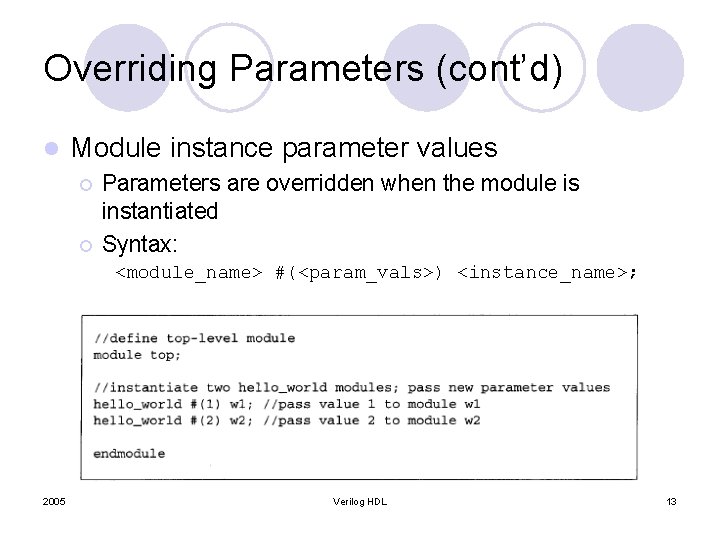

Overriding Parameters (cont’d) l Module instance parameter values ¡ ¡ Parameters are overridden when the module is instantiated Syntax: <module_name> #(<param_vals>) <instance_name>; 2005 Verilog HDL 13

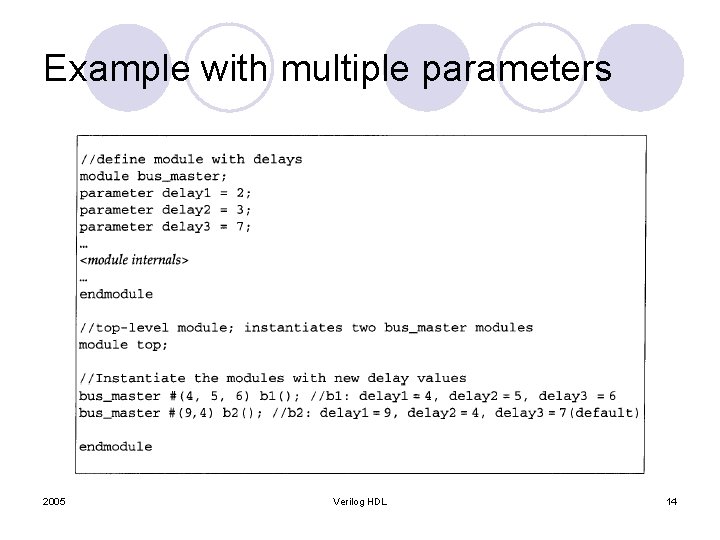

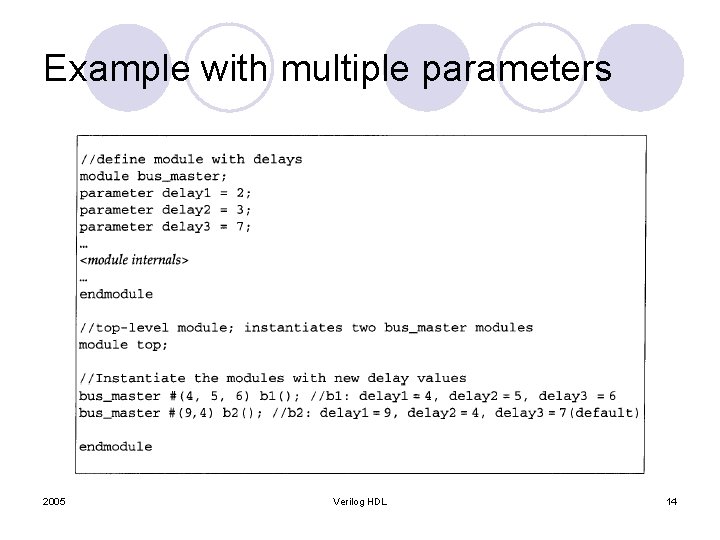

Example with multiple parameters 2005 Verilog HDL 14

Conditional Compilation and Execution Useful Modeling Techniques 2005 Verilog HDL

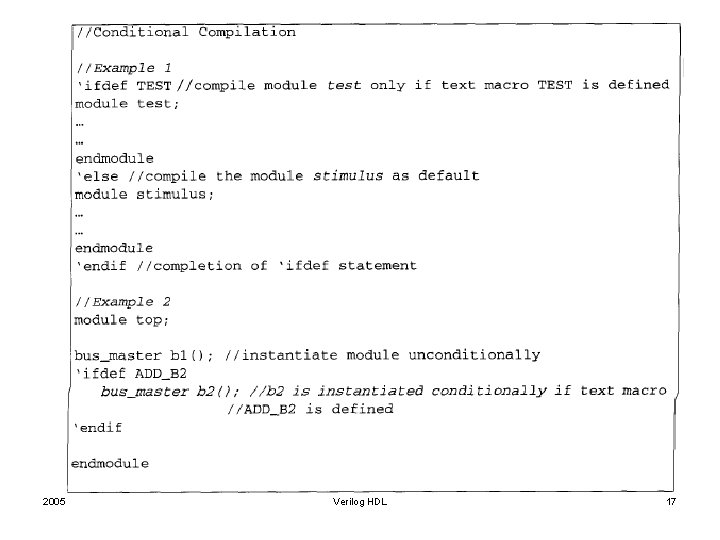

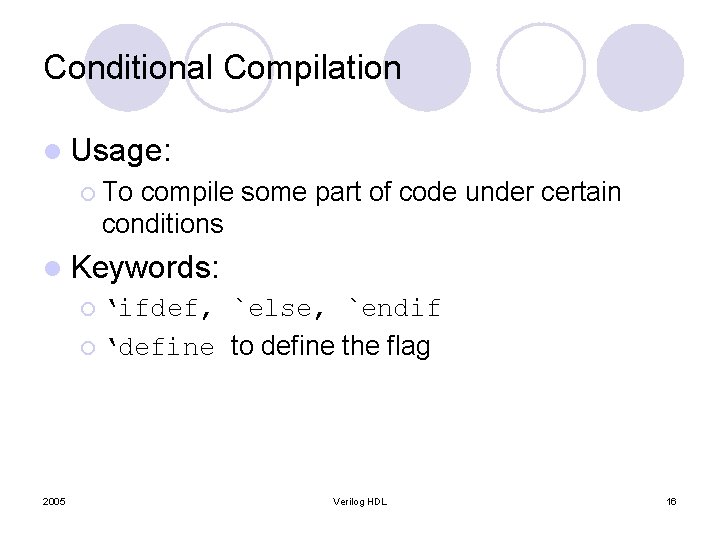

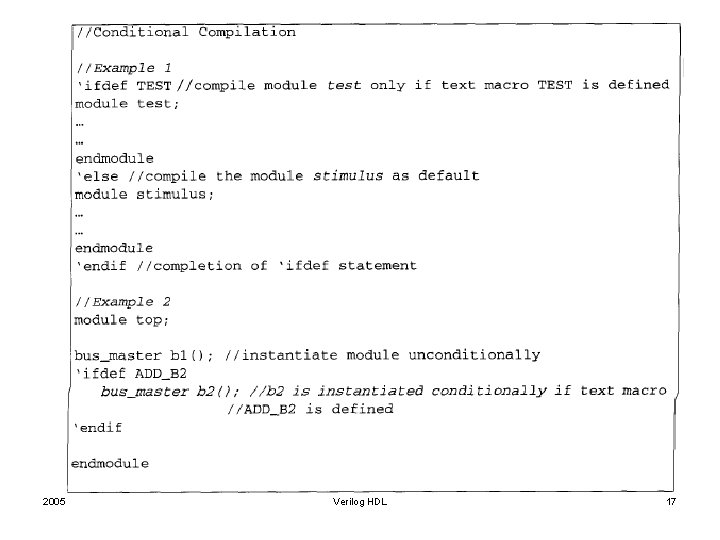

Conditional Compilation l Usage: ¡ To compile some part of code under certain conditions l Keywords: ¡ ‘ifdef, `else, `endif ¡ ‘define to define the flag 2005 Verilog HDL 16

2005 Verilog HDL 17

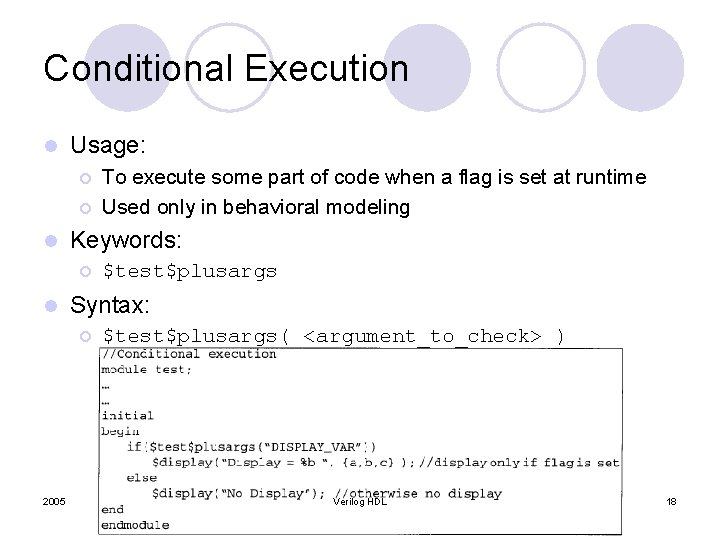

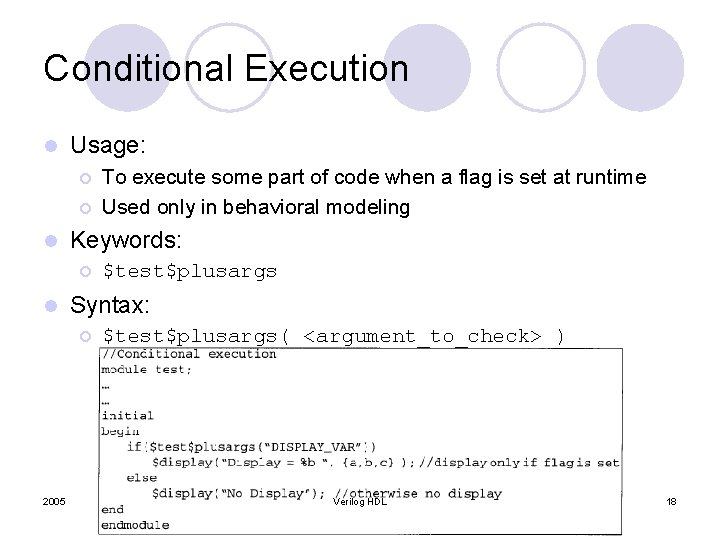

Conditional Execution l Usage: ¡ ¡ l Keywords: ¡ l $test$plusargs Syntax: ¡ 2005 To execute some part of code when a flag is set at runtime Used only in behavioral modeling $test$plusargs( <argument_to_check> ) Verilog HDL 18

2005 Verilog HDL 19

Useful System Tasks Useful Modeling Techniques 2005 Verilog HDL

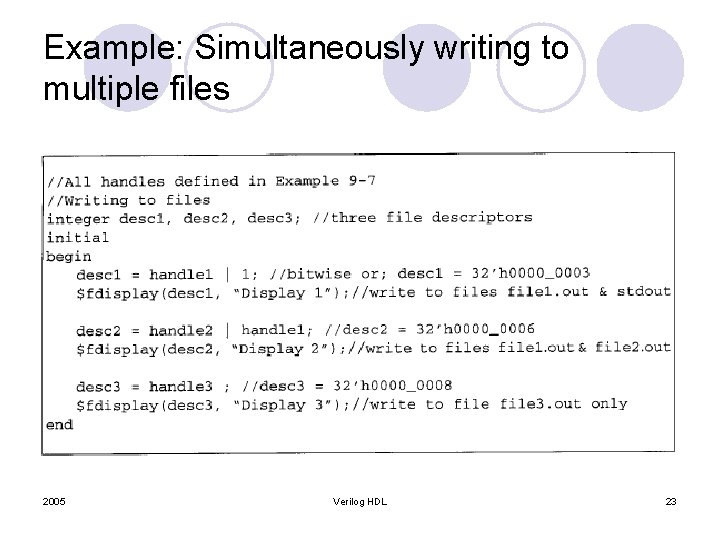

Useful System Tasks File Output l Opening a file ¡ Syntax: <file_handle> = $fopen( “<file_name>” ); ¡ <file_handle> is a 32 bit value, called multi-channel descriptor ¡ Only 1 bit is set in each descriptor Standard output has a descriptor of 1 (Channel 0) ¡ 2005 Verilog HDL 21

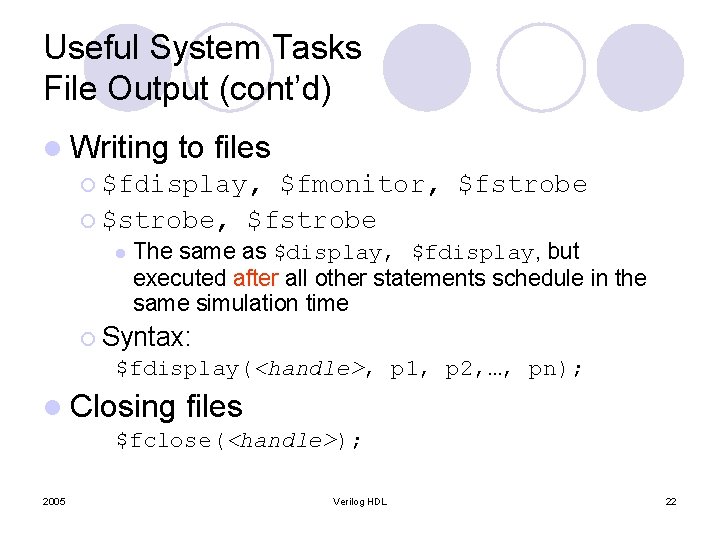

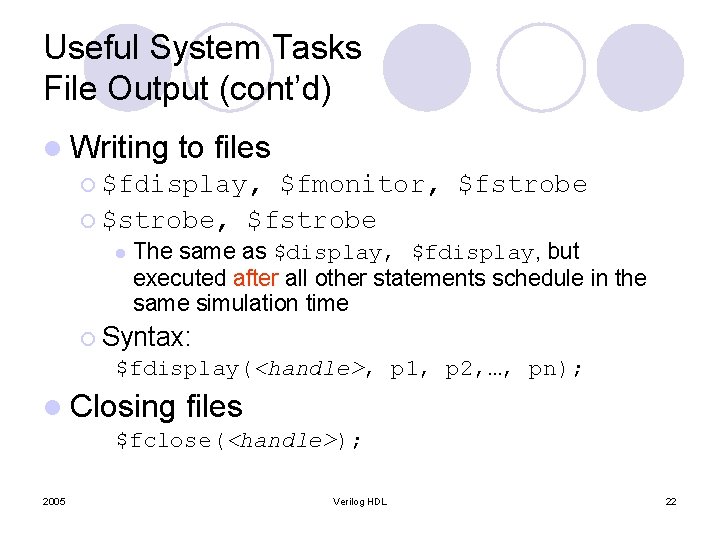

Useful System Tasks File Output (cont’d) l Writing to files ¡ $fdisplay, $fmonitor, $fstrobe ¡ $strobe, $fstrobe l The same as $display, $fdisplay, but executed after all other statements schedule in the same simulation time ¡ Syntax: $fdisplay(<handle>, p 1, p 2, …, pn); l Closing files $fclose(<handle>); 2005 Verilog HDL 22

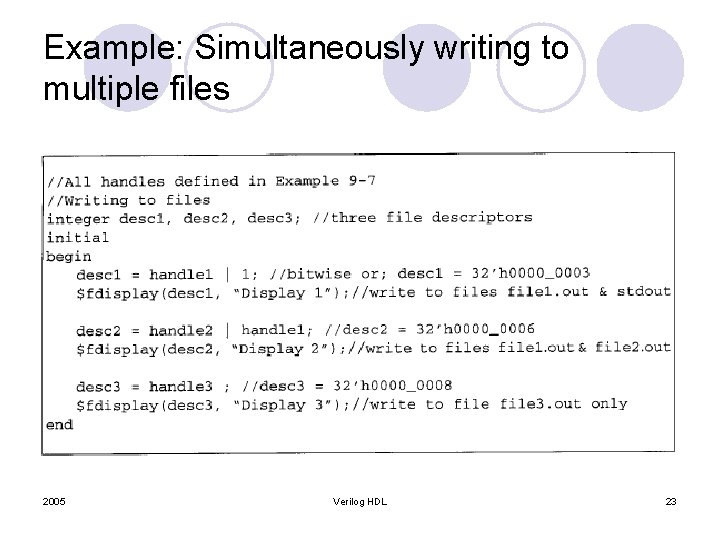

Example: Simultaneously writing to multiple files 2005 Verilog HDL 23

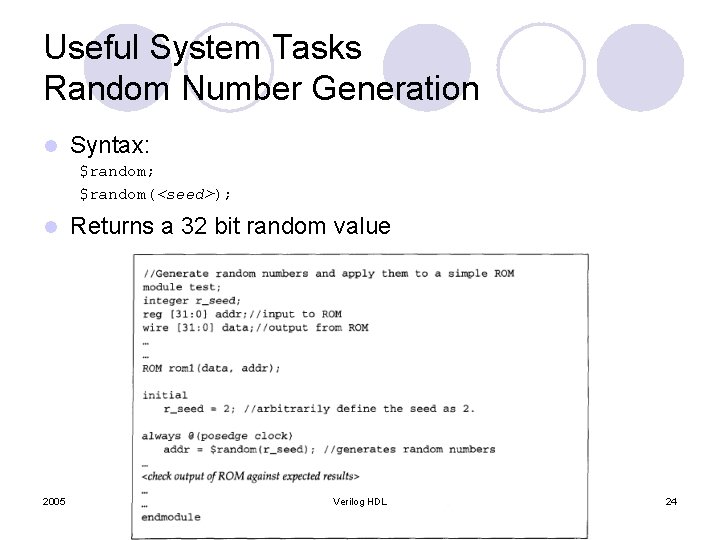

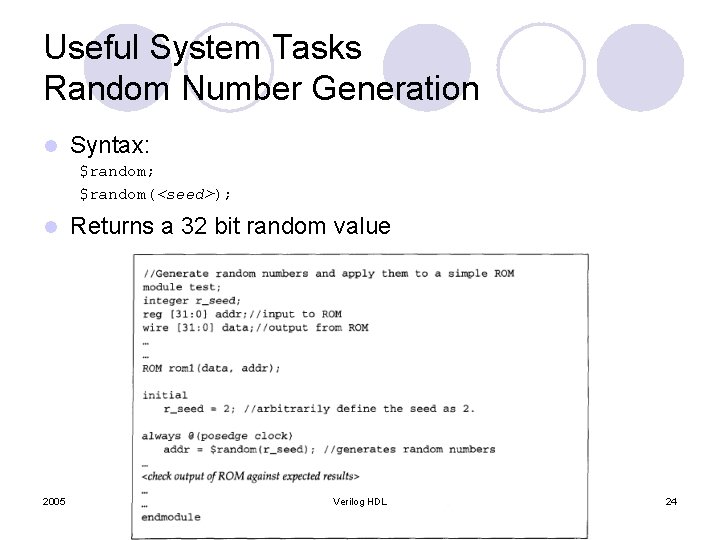

Useful System Tasks Random Number Generation l Syntax: $random; $random(<seed>); l 2005 Returns a 32 bit random value Verilog HDL 24

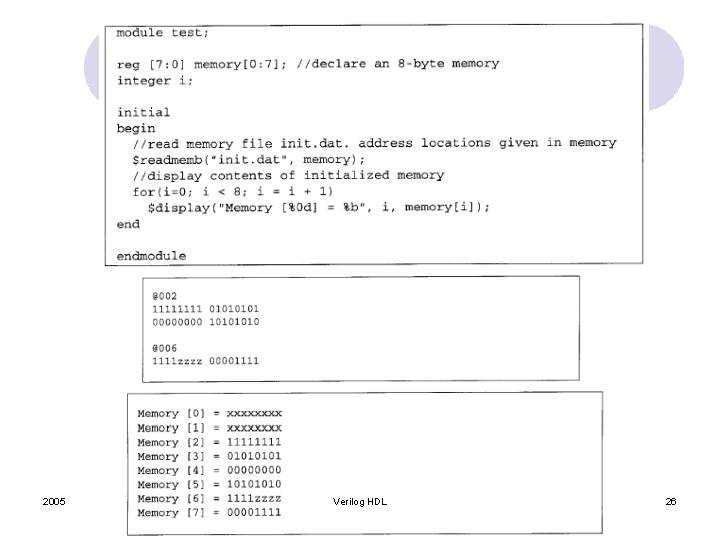

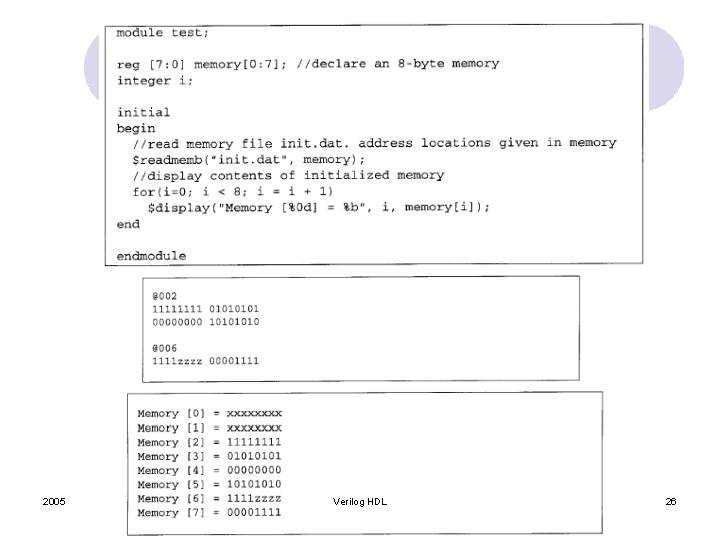

Useful System Tasks Initializing Memory from File l Keywords: ¡ $readmemb, $readmemh Used to initialize memory (reg l Syntax: l [3: 0] mem[0: 1023]) $readmemb(“<file_name>”, <memory_name>); $readmemb(“<file_name>”, <memory_name>, <start_addr>, <finish_addr>); l 2005 The same syntax for $readmemh Verilog HDL 25

2005 Verilog HDL 26

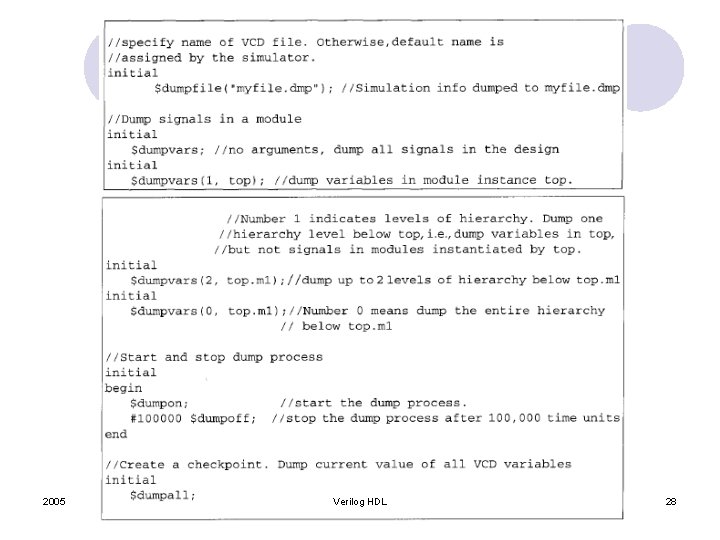

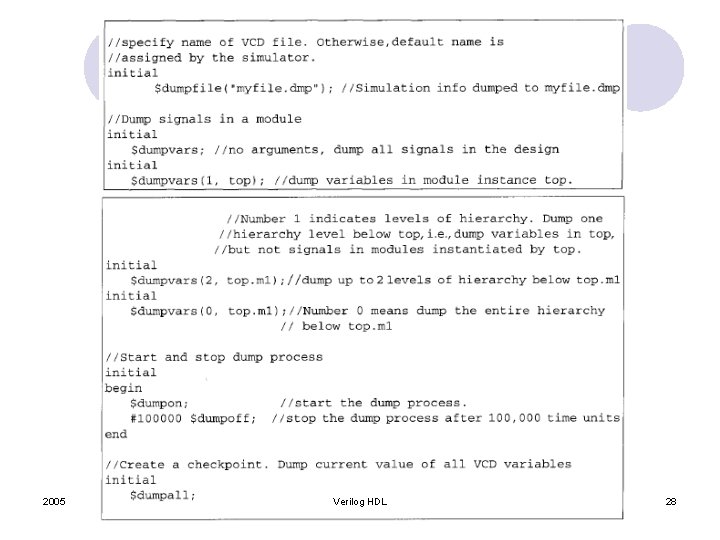

Useful System Tasks Value Change Dump (VCD) File l ASCII file containing information on ¡ ¡ ¡ l Keywords ¡ ¡ ¡ 2005 Simulation time Scope and signal definitions Signal value changes $dumpvars $dumpfile $dumpon $dumpoff $dumpall Verilog HDL 27

2005 Verilog HDL 28

Today Summary l Introduced a number of modeling techniques useful in various applications 2005 Verilog HDL 29

Other Notes l Homework ¡ Chapter 8 9: All exercises with Model. Sim, except for 3 and 5 l 3 and 5 in paper and pencil l Due date: Sunday, Day 11 th l 2005 Verilog HDL 30