Digital System Design Verilog HDL Timing and Delays

- Slides: 41

Digital System Design Verilog® HDL Timing and Delays 2005 Verilog HDL Maziar Goudarzi

Today Program l Delays and their definition and use in Verilog 2005 Verilog HDL 2

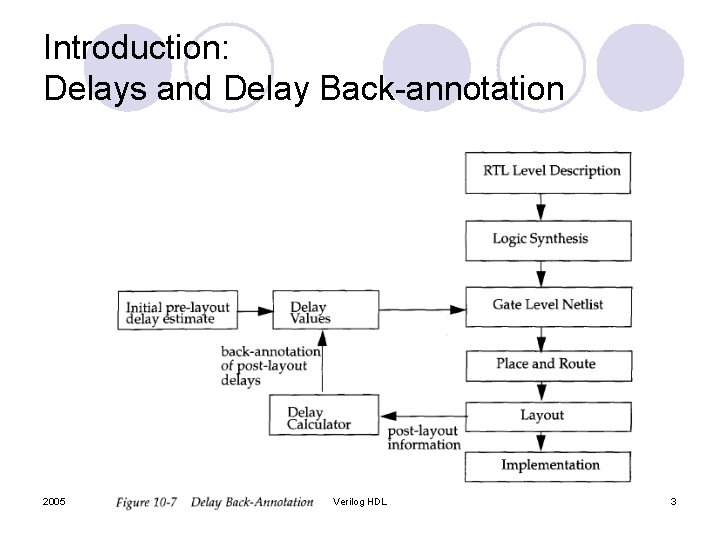

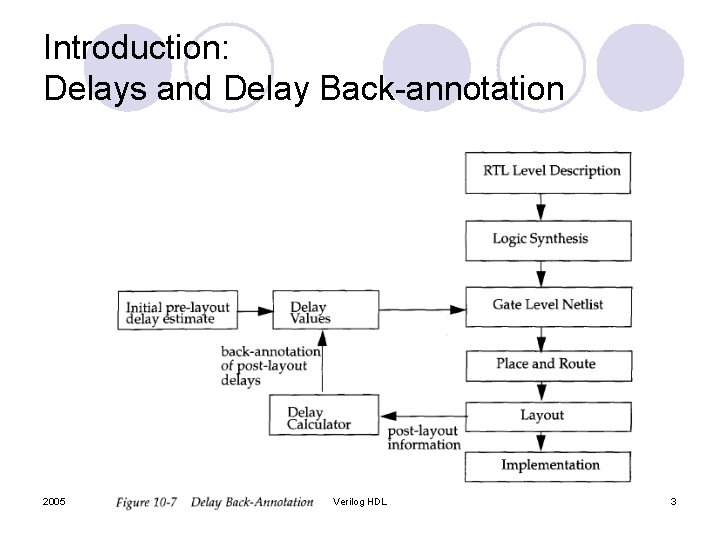

Introduction: Delays and Delay Back-annotation 2005 Verilog HDL 3

Introduction (cont’d) Functional simulation vs. Timing simulation l Delays are crucial in REAL simulations l ¡ ¡ Post-synthesis simulation Post-layout simulation l l Delay Models ¡ ¡ Represent different physical concepts Two most-famous models l l 2005 FPGA counter-part: Post-P&R simulation Inertial delay Transport delay (path delay) Verilog HDL 4

Delay Models: Inertial Delay l The inertia of a circuit node to change value l Abstractly models the RC circuit seen at the node l Different types ¡ Input inertial delay ¡ Output inertial delay 2005 Verilog HDL 5

Delay Models: Transport Delay (Path Delay) l Represents the propagation time of signals from module inputs to its outputs l Models the internal propagation delays of electrical elements 2005 Verilog HDL 6

Specifying Delays in Verilog 2005 Verilog HDL

Specifying Delays in Verilog l Delays are shown by # sign in all Verilog modeling levels l Supported delay types ¡ Rise, Fall, Turnoff types ¡ Min, Typ, Max values 2005 Verilog HDL 8

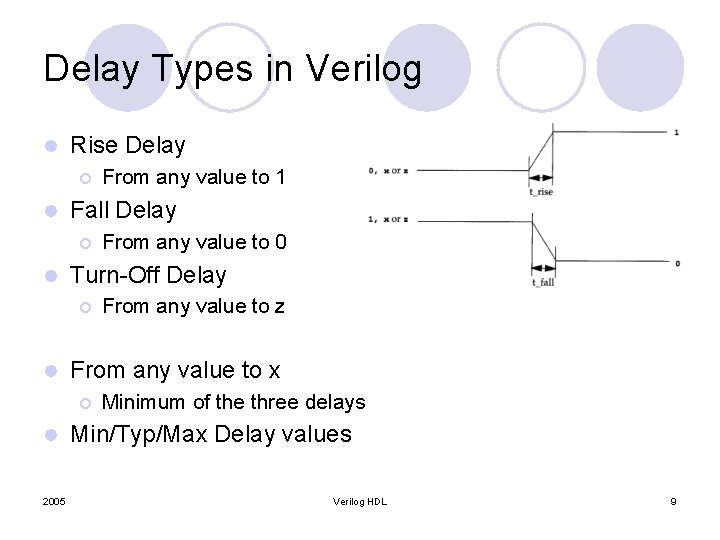

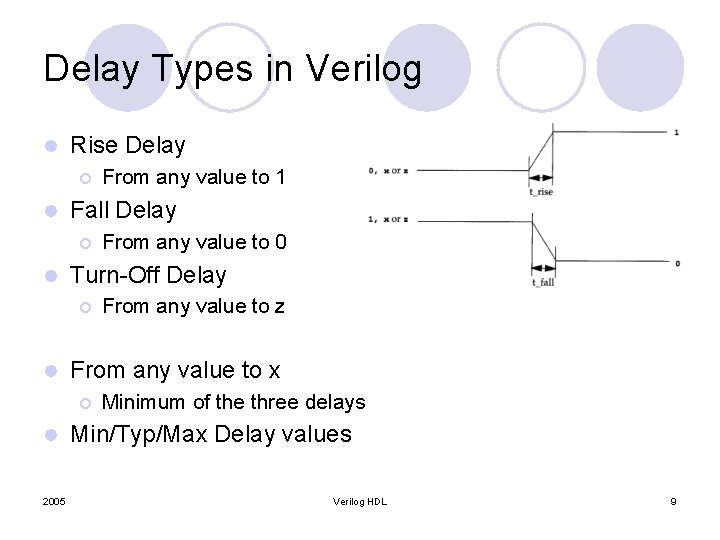

Delay Types in Verilog l Rise Delay ¡ l Fall Delay ¡ l 2005 From any value to z From any value to x ¡ l From any value to 0 Turn-Off Delay ¡ l From any value to 1 Minimum of the three delays Min/Typ/Max Delay values Verilog HDL 9

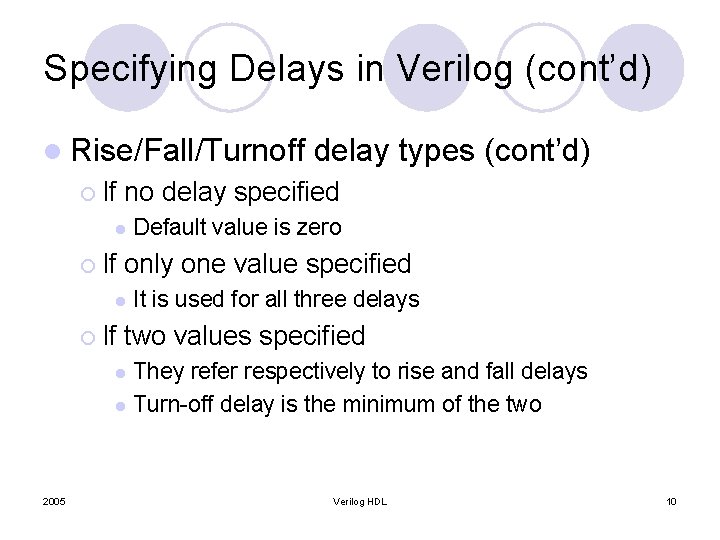

Specifying Delays in Verilog (cont’d) l Rise/Fall/Turnoff ¡ If no delay specified l ¡ If Default value is zero only one value specified l ¡ If delay types (cont’d) It is used for all three delays two values specified They refer respectively to rise and fall delays l Turn-off delay is the minimum of the two l 2005 Verilog HDL 10

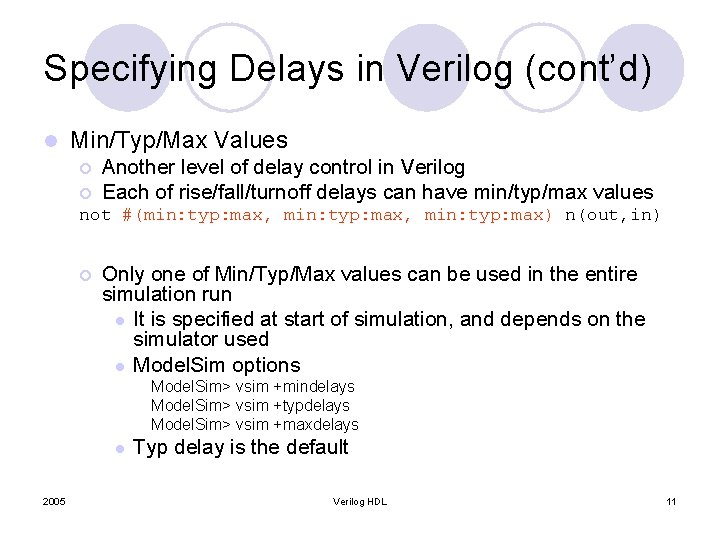

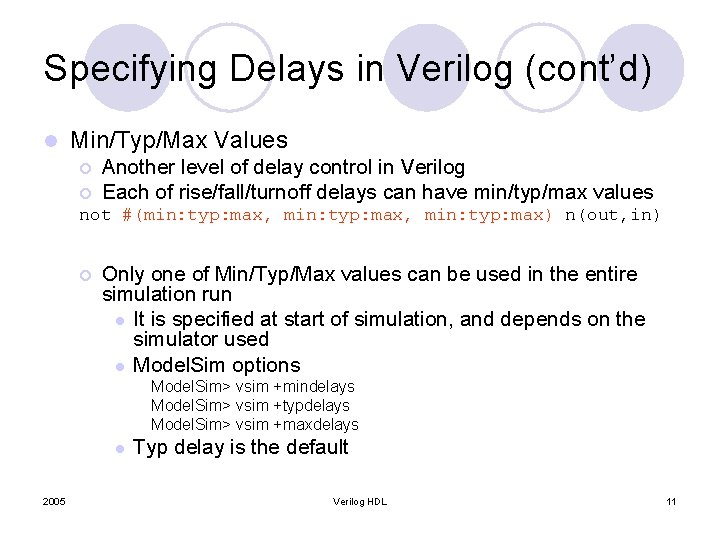

Specifying Delays in Verilog (cont’d) l Min/Typ/Max Values ¡ ¡ Another level of delay control in Verilog Each of rise/fall/turnoff delays can have min/typ/max values not #(min: typ: max, min: typ: max) n(out, in) ¡ Only one of Min/Typ/Max values can be used in the entire simulation run l It is specified at start of simulation, and depends on the simulator used l Model. Sim options Model. Sim> vsim +mindelays Model. Sim> vsim +typdelays Model. Sim> vsim +maxdelays l 2005 Typ delay is the default Verilog HDL 11

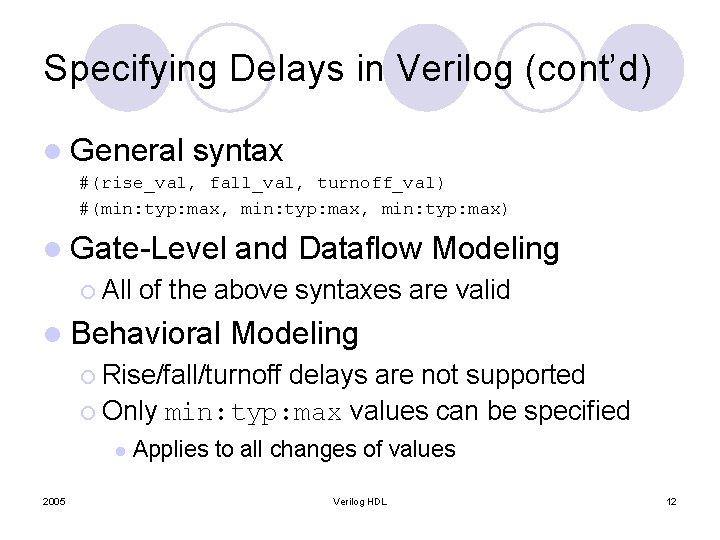

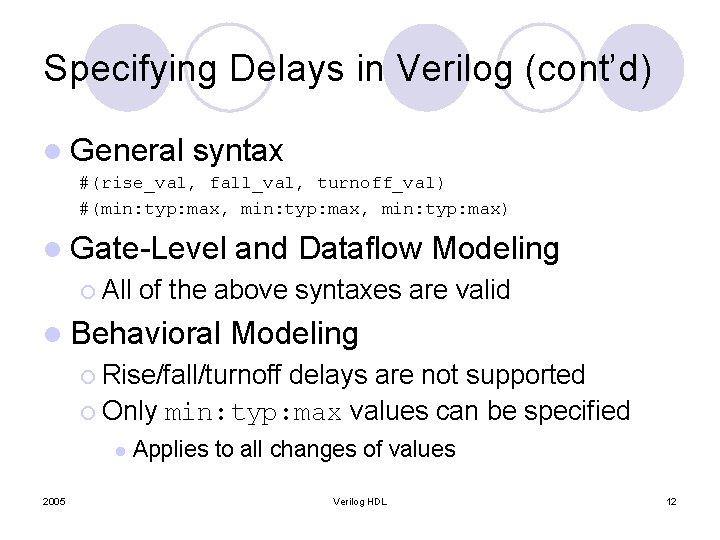

Specifying Delays in Verilog (cont’d) l General syntax #(rise_val, fall_val, turnoff_val) #(min: typ: max, min: typ: max) l Gate-Level ¡ All and Dataflow Modeling of the above syntaxes are valid l Behavioral Modeling ¡ Rise/fall/turnoff delays are not supported ¡ Only min: typ: max values can be specified l 2005 Applies to all changes of values Verilog HDL 12

Delays in Gate-Level Modeling Delays in Verilog 2005 Verilog HDL

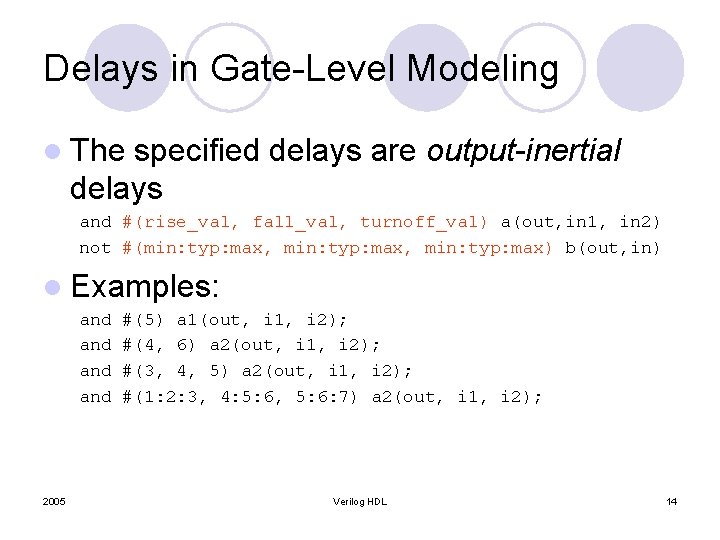

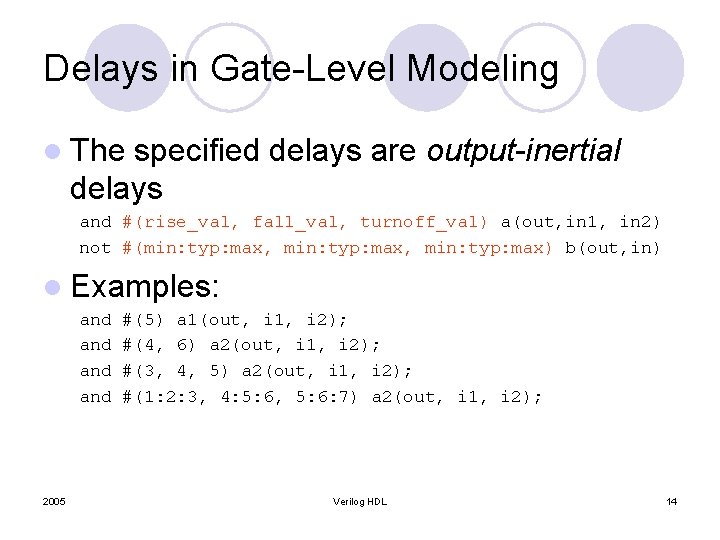

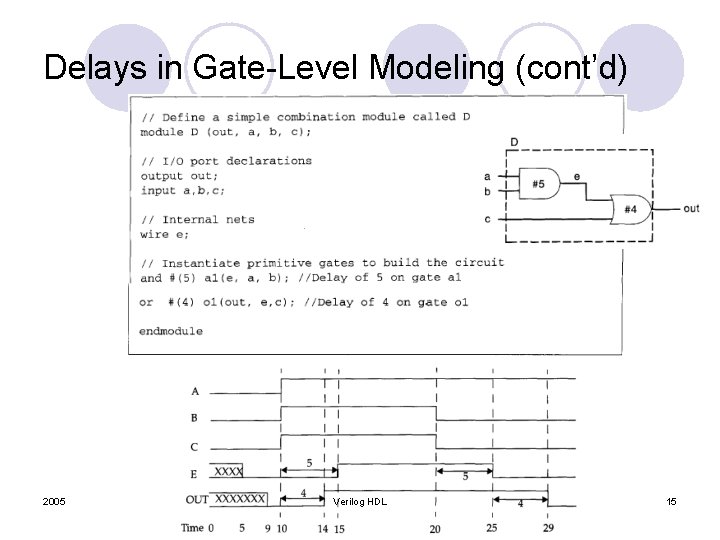

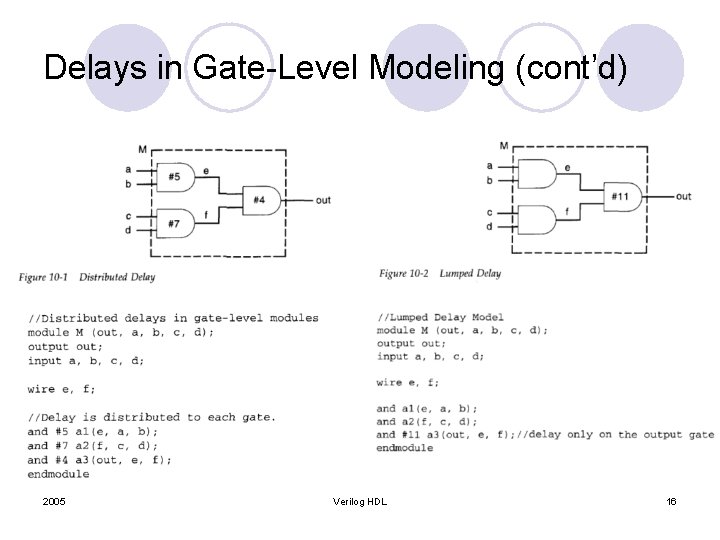

Delays in Gate-Level Modeling l The specified delays are output-inertial delays and #(rise_val, fall_val, turnoff_val) a(out, in 1, in 2) not #(min: typ: max, min: typ: max) b(out, in) l Examples: and and 2005 #(5) a 1(out, i 1, i 2); #(4, 6) a 2(out, i 1, i 2); #(3, 4, 5) a 2(out, i 1, i 2); #(1: 2: 3, 4: 5: 6, 5: 6: 7) a 2(out, i 1, i 2); Verilog HDL 14

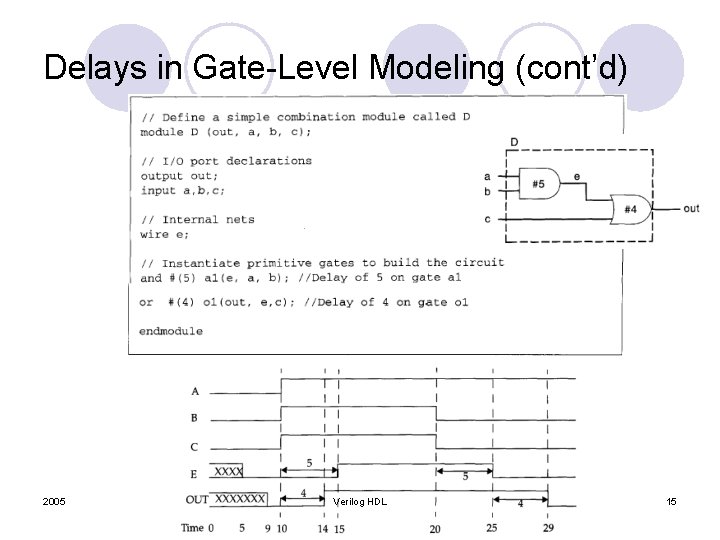

Delays in Gate-Level Modeling (cont’d) 2005 Verilog HDL 15

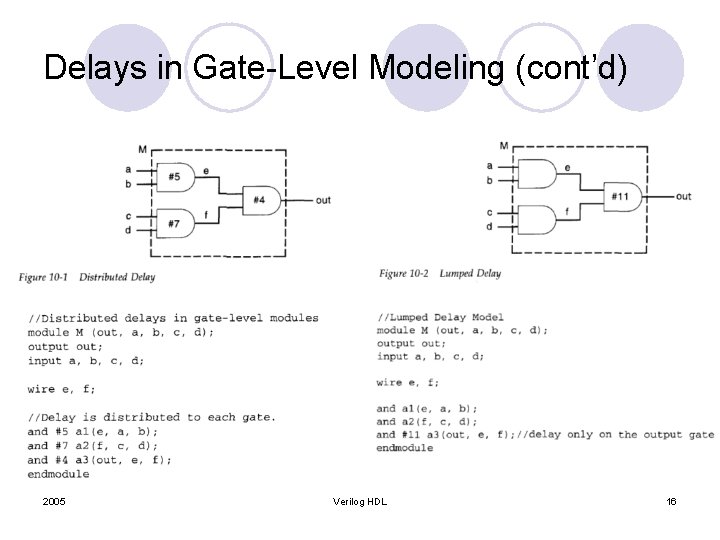

Delays in Gate-Level Modeling (cont’d) 2005 Verilog HDL 16

Delays in Dataflow Modeling Delays in Verilog 2005 Verilog HDL

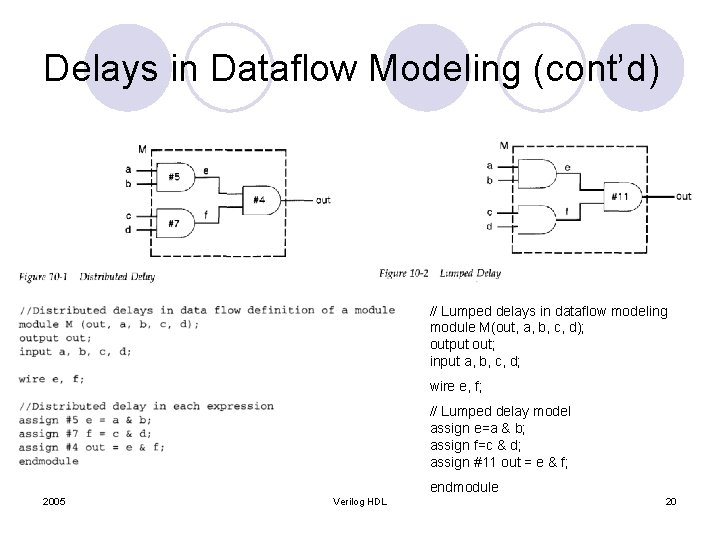

Delays in Dataflow Modeling l As in Gate-Level Modeling the delay is output-inertial delay l Regular assignment delay syntax assign #delay out = in 1 & in 2; l Implicit continuous assignment delay wire #delay out = in 1 & in 2; l Net declaration delay ¡ Can also be used in Gate-Level modeling wire #delay w; 2005 Verilog HDL 18

Delays in Dataflow Modeling (cont’d) l Examples wire #10 out = in 1 & in 2; wire #10 out; assign out = in 1 & in 2; 2005 wire out; assign #10 out = in 1 & in 2; Note: pulses with a width less than the delay are not propagated to output Verilog HDL 19

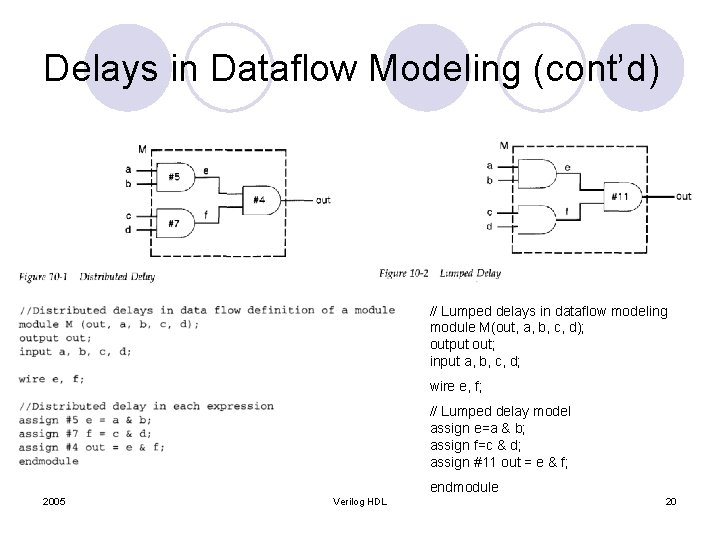

Delays in Dataflow Modeling (cont’d) // Lumped delays in dataflow modeling module M(out, a, b, c, d); output out; input a, b, c, d; wire e, f; // Lumped delay model assign e=a & b; assign f=c & d; assign #11 out = e & f; endmodule 2005 Verilog HDL 20

Delays in Behavioral Modeling Delays in Verilog 2005 Verilog HDL

Delay in Behavioral Modeling l Only min: typ: max values can be set ¡ i. e. rise/fall/turnoff delays are not supported l Three categories ¡ Regular delays ¡ Intra-assignment delays ¡ Zero delay 2005 Verilog HDL 22

Path (Transport ) Delays in Verilog 2005 Verilog HDL

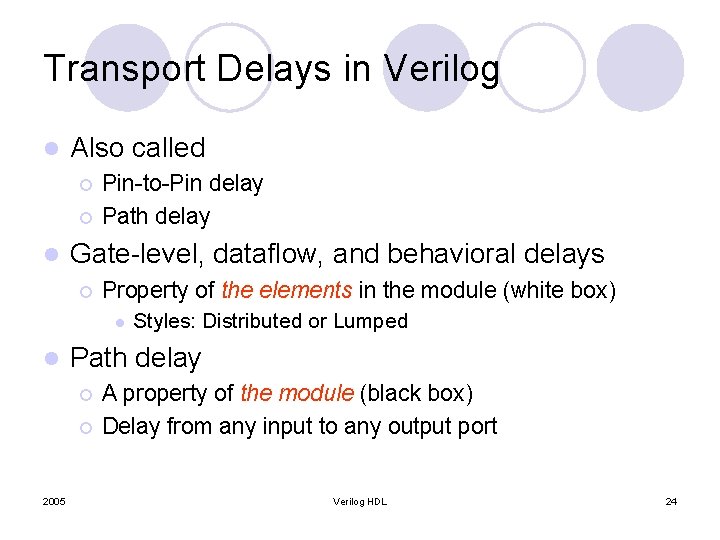

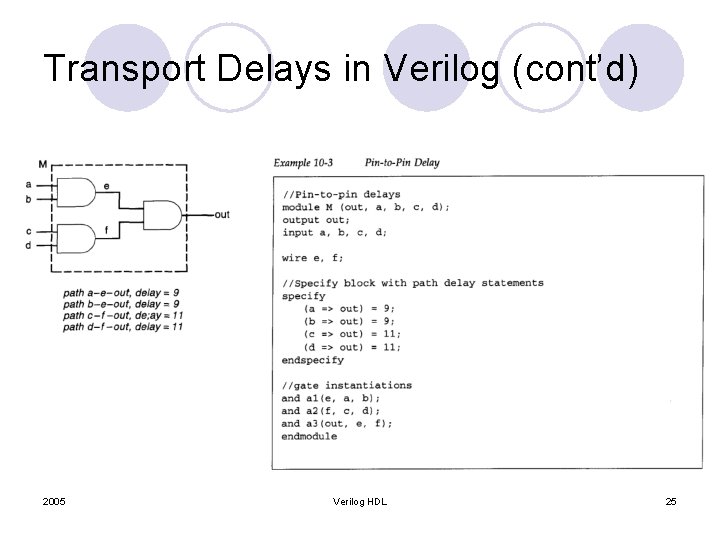

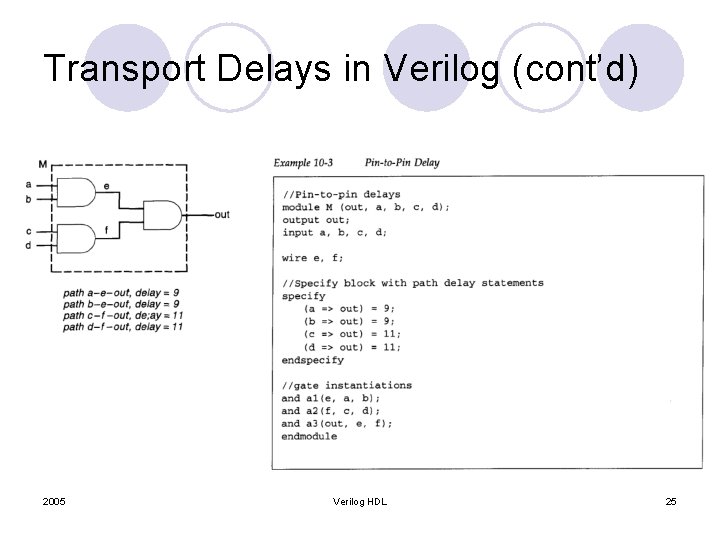

Transport Delays in Verilog l Also called ¡ ¡ l Pin-to-Pin delay Path delay Gate-level, dataflow, and behavioral delays ¡ Property of the elements in the module (white box) l l Path delay ¡ ¡ 2005 Styles: Distributed or Lumped A property of the module (black box) Delay from any input to any output port Verilog HDL 24

Transport Delays in Verilog (cont’d) 2005 Verilog HDL 25

Transport Delays in Verilog (cont’d) l specify block ¡ Assign pin-to-pin delays ¡ Define specparam constants ¡ Setup 2005 timing checks in the design Verilog HDL 26

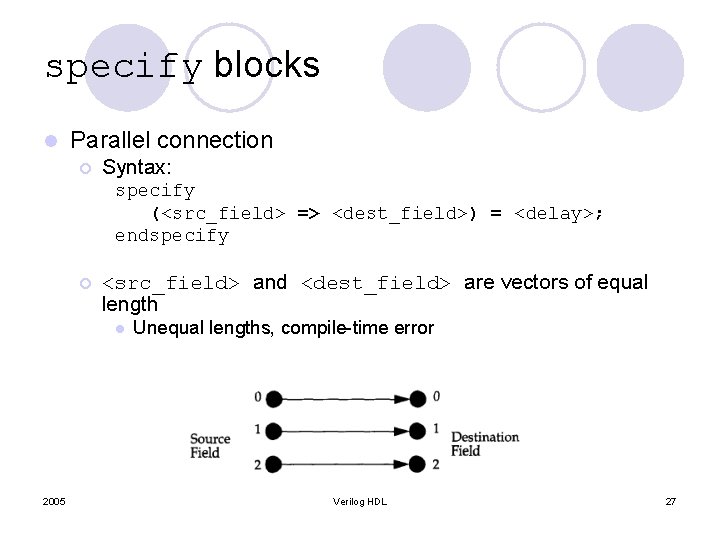

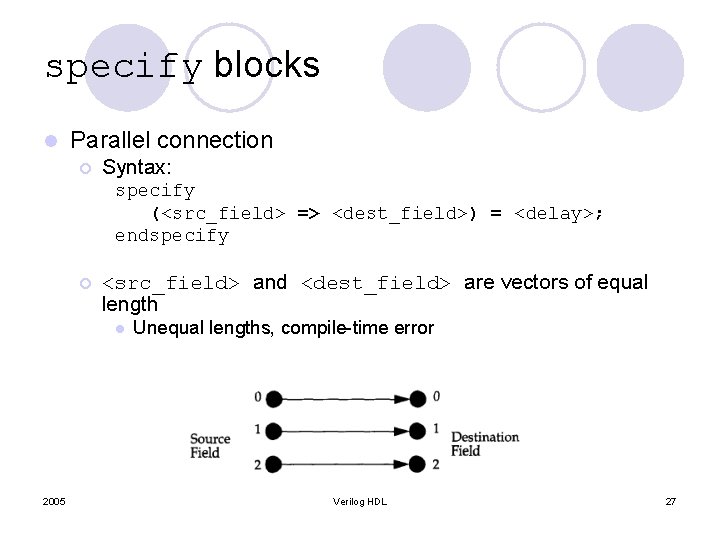

specify blocks l Parallel connection ¡ Syntax: specify (<src_field> => <dest_field>) = <delay>; endspecify ¡ <src_field> and <dest_field> are vectors of equal length l 2005 Unequal lengths, compile-time error Verilog HDL 27

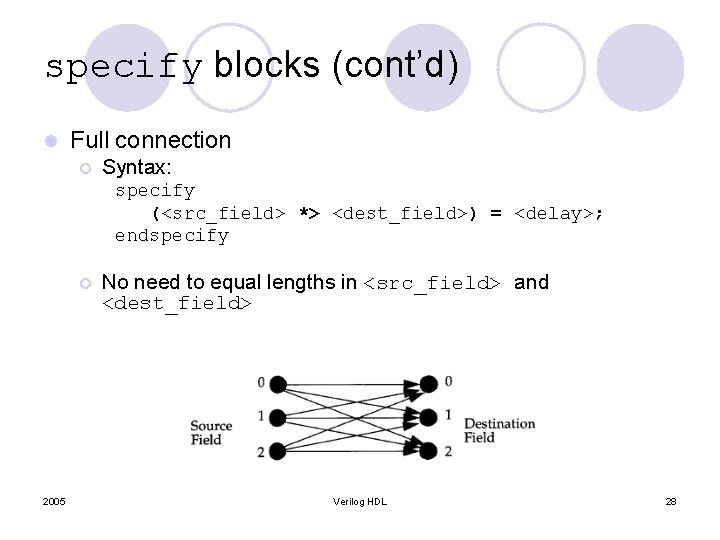

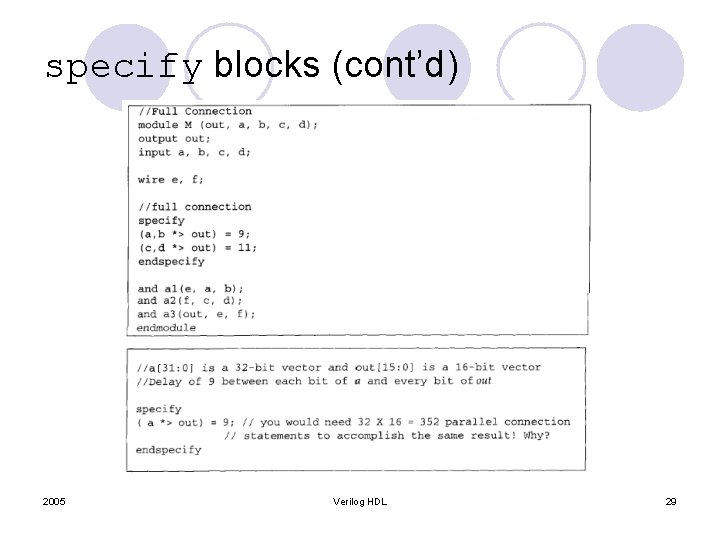

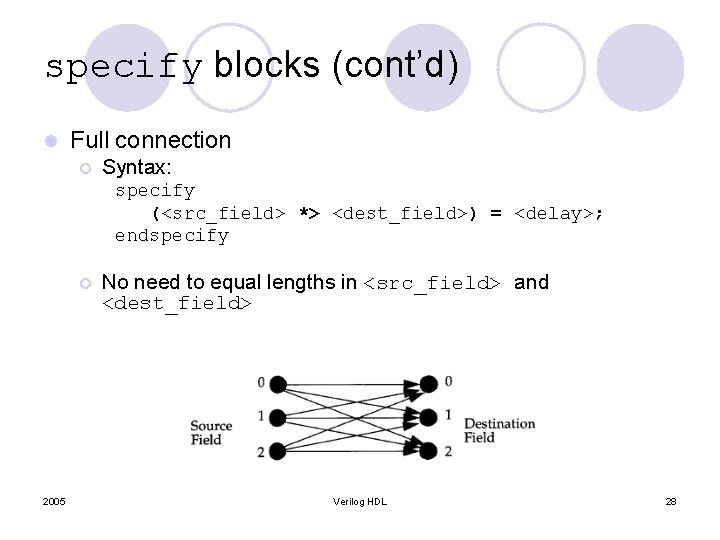

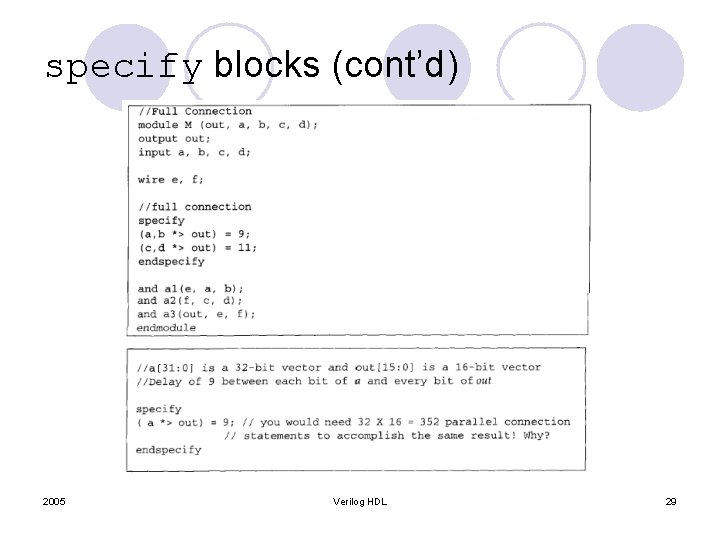

specify blocks (cont’d) l Full connection ¡ Syntax: specify (<src_field> *> <dest_field>) = <delay>; endspecify ¡ 2005 No need to equal lengths in <src_field> and <dest_field> Verilog HDL 28

specify blocks (cont’d) 2005 Verilog HDL 29

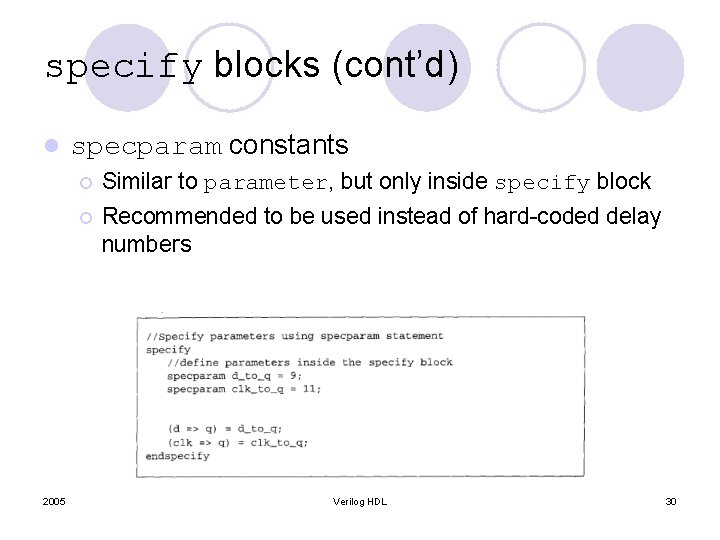

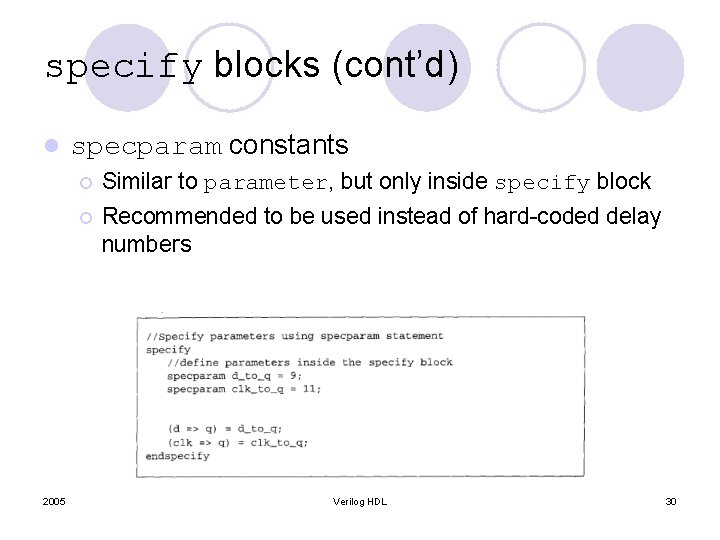

specify blocks (cont’d) l 2005 specparam constants ¡ Similar to parameter, but only inside specify block ¡ Recommended to be used instead of hard-coded delay numbers Verilog HDL 30

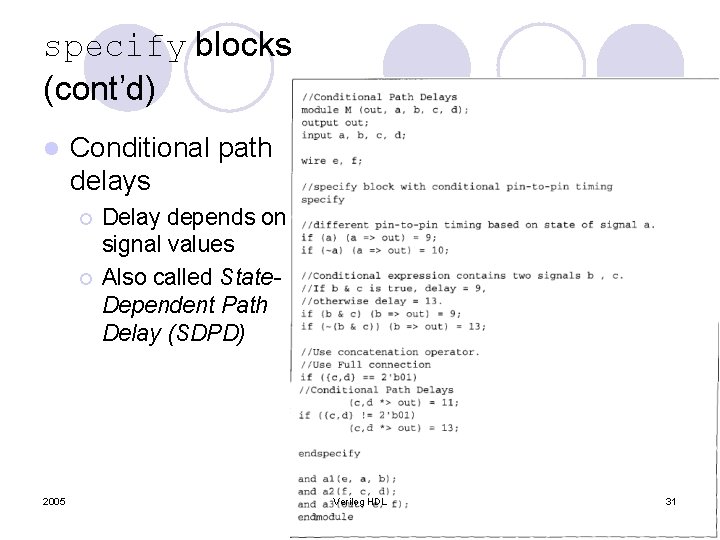

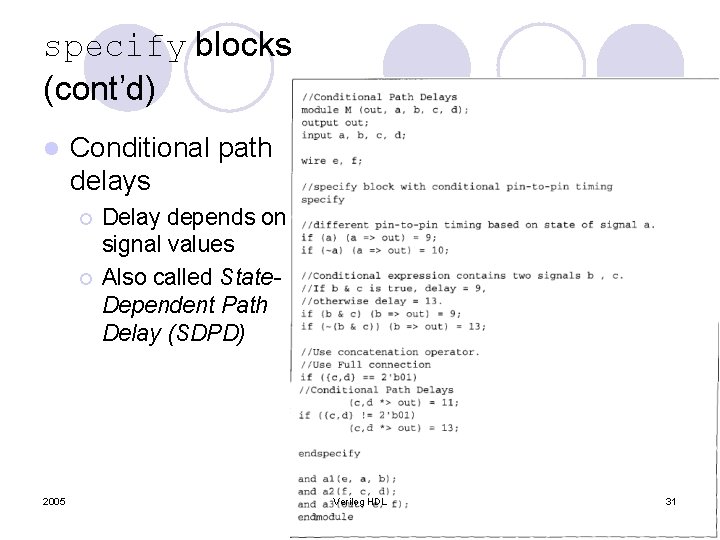

specify blocks (cont’d) l Conditional path delays ¡ ¡ 2005 Delay depends on signal values Also called State. Dependent Path Delay (SDPD) Verilog HDL 31

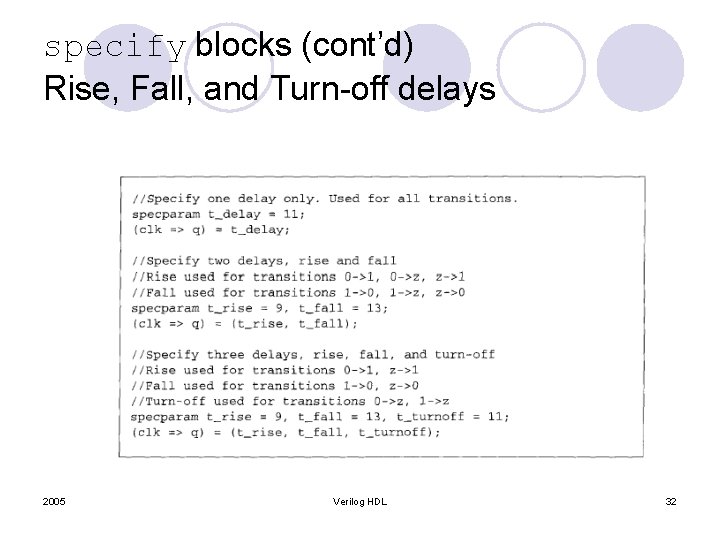

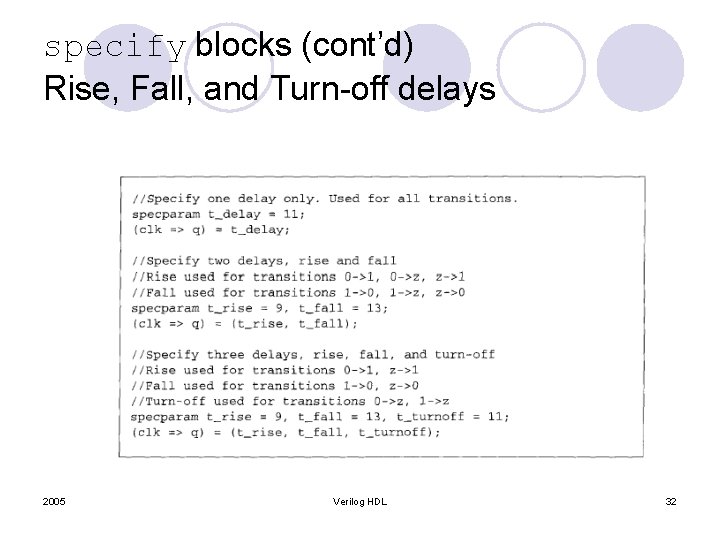

specify blocks (cont’d) Rise, Fall, and Turn-off delays 2005 Verilog HDL 32

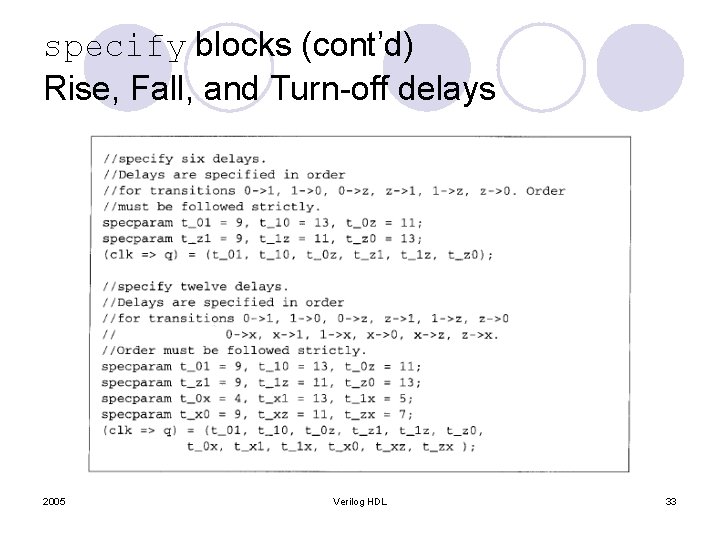

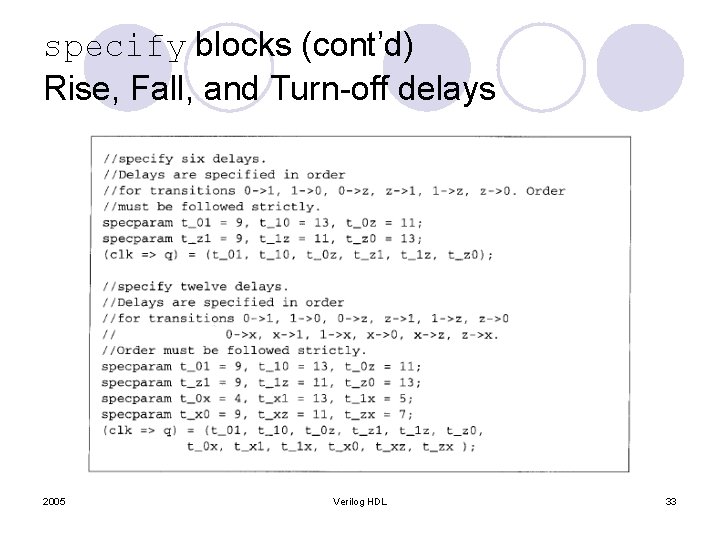

specify blocks (cont’d) Rise, Fall, and Turn-off delays 2005 Verilog HDL 33

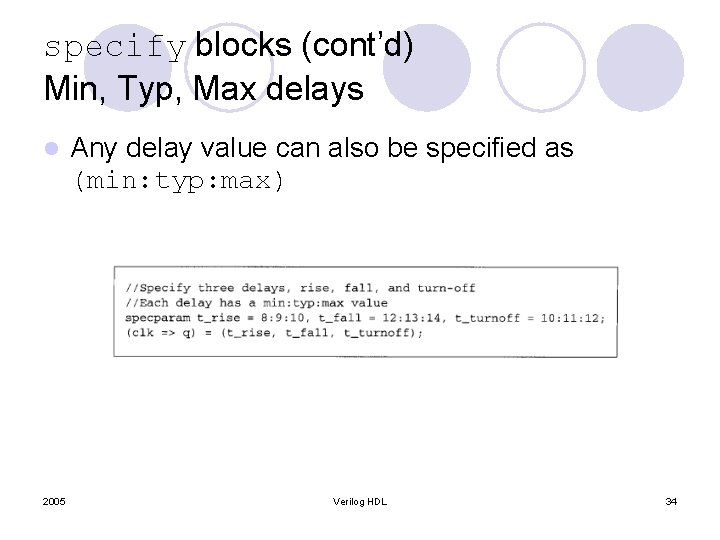

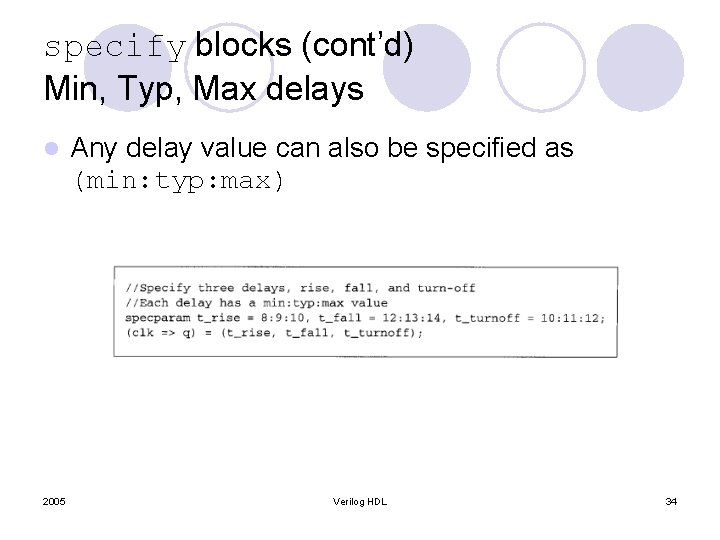

specify blocks (cont’d) Min, Typ, Max delays l 2005 Any delay value can also be specified as (min: typ: max) Verilog HDL 34

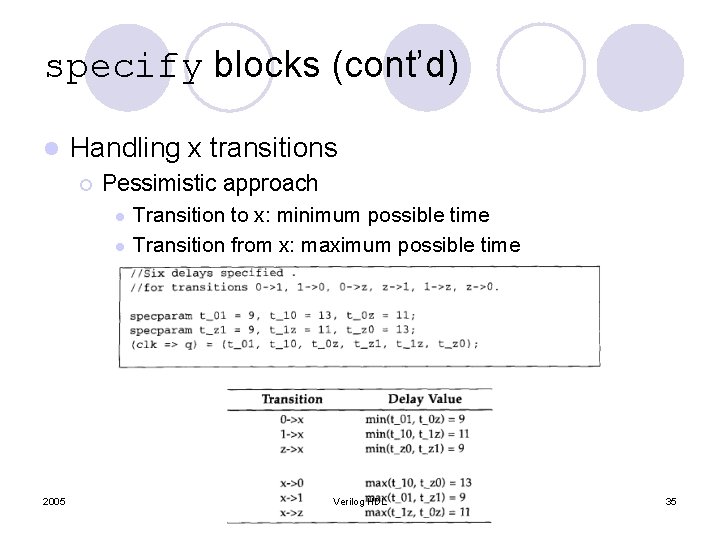

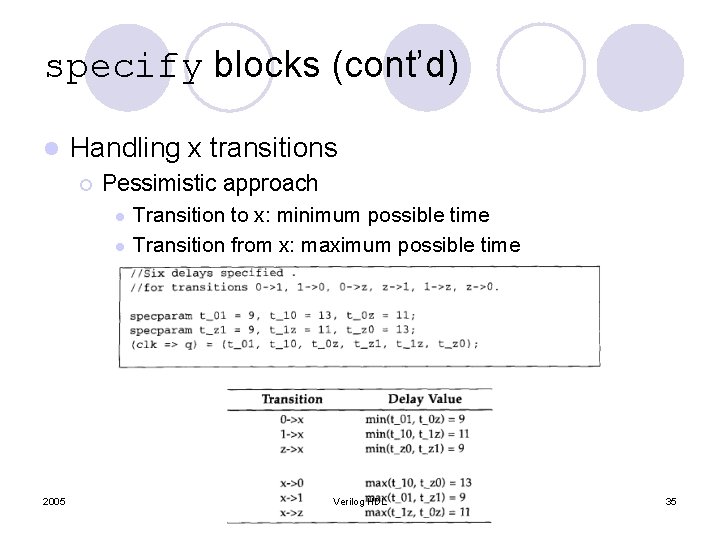

specify blocks (cont’d) l Handling x transitions ¡ Pessimistic approach l l 2005 Transition to x: minimum possible time Transition from x: maximum possible time Verilog HDL 35

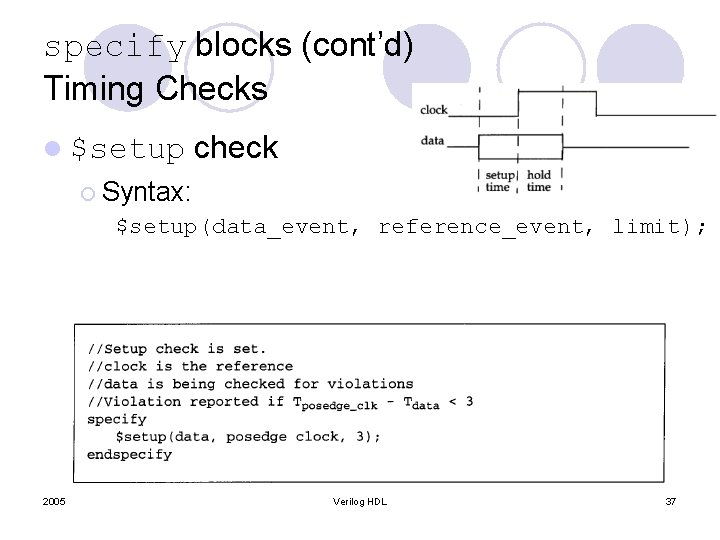

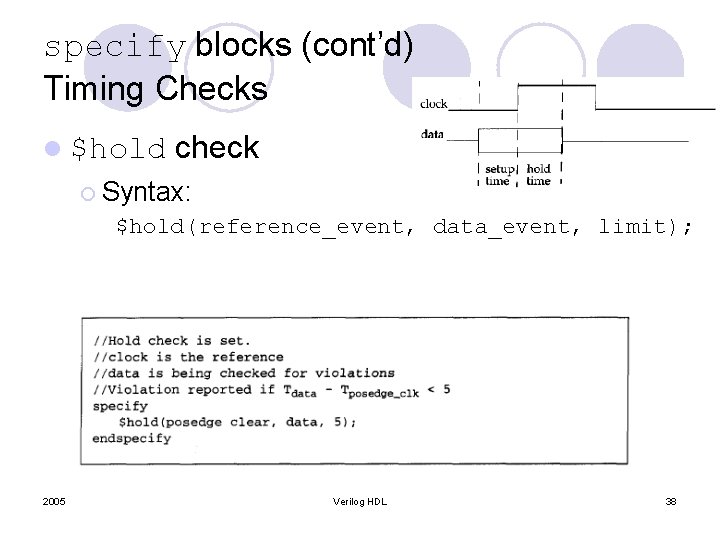

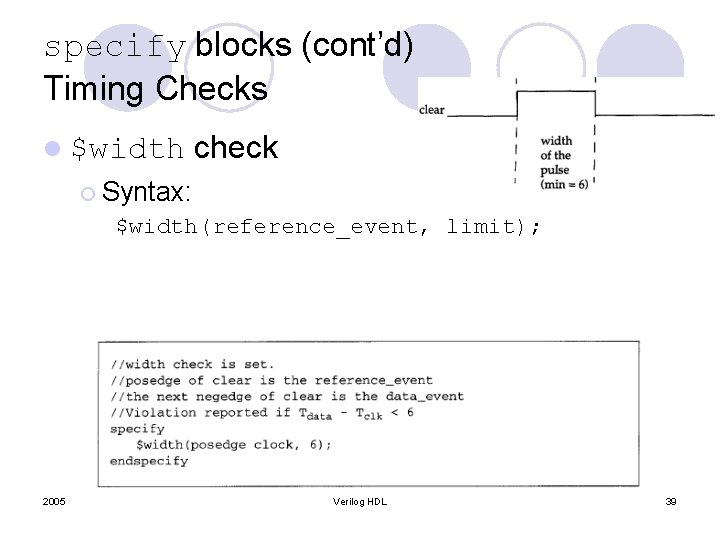

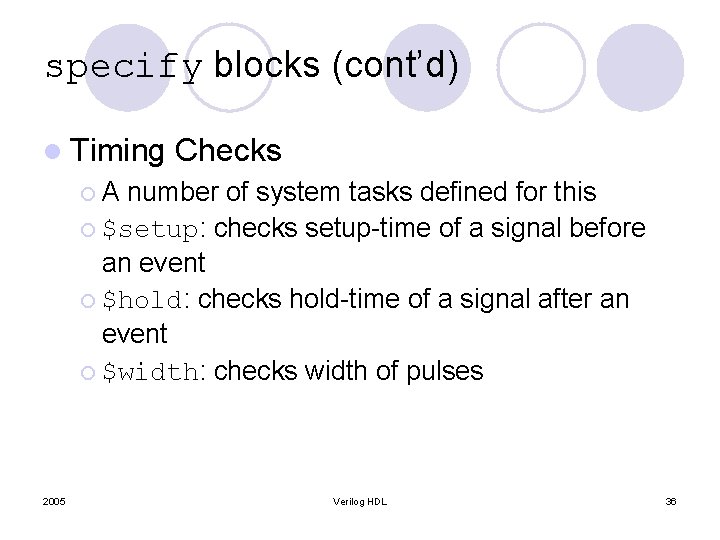

specify blocks (cont’d) l Timing Checks ¡A number of system tasks defined for this ¡ $setup: checks setup-time of a signal before an event ¡ $hold: checks hold-time of a signal after an event ¡ $width: checks width of pulses 2005 Verilog HDL 36

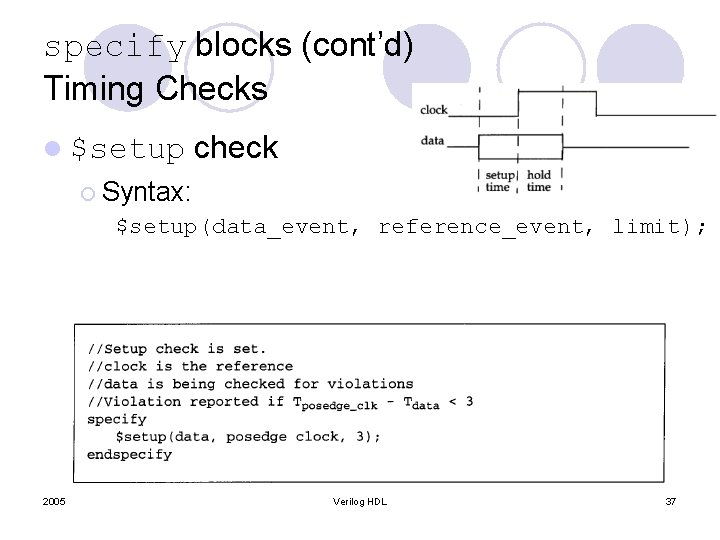

specify blocks (cont’d) Timing Checks l $setup check ¡ Syntax: $setup(data_event, reference_event, limit); 2005 Verilog HDL 37

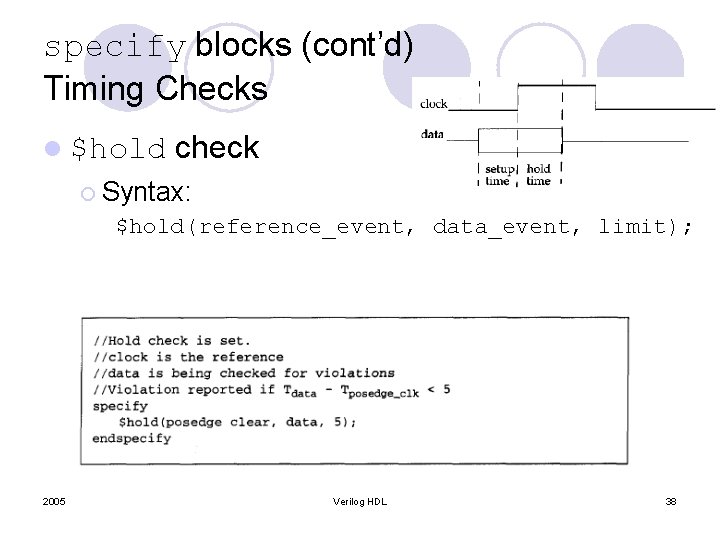

specify blocks (cont’d) Timing Checks l $hold check ¡ Syntax: $hold(reference_event, data_event, limit); 2005 Verilog HDL 38

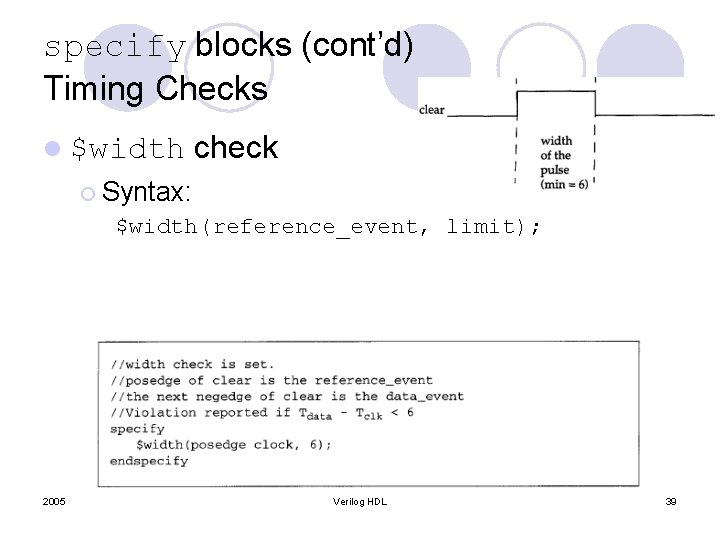

specify blocks (cont’d) Timing Checks l $width check ¡ Syntax: $width(reference_event, limit); 2005 Verilog HDL 39

Today Summary l Delays ¡ Models l l ¡ Types l l ¡ Rise/Fall/Turn-off Min/Typ/Max Values Delays in Verilog l l l 2005 Inertial (distributed and lumped delay) Transport (path/pin-to-pin delay) Syntax and other common features Gate-Level and Dataflow Modeling Behavioral Modeling Verilog HDL 40

Other Notes l Homework ¡ Chapter 9 10: All exercises l Due date: Sunday, Day 11 th l 2005 Verilog HDL 41