Digital System Design Verilog HDL Design at Structural

![ANSI C Style Port Declaration Syntax module fulladd 4(output reg [3: 0] sum, output ANSI C Style Port Declaration Syntax module fulladd 4(output reg [3: 0] sum, output](https://slidetodoc.com/presentation_image/29a3ef527552ca6378d783e9bc38098b/image-12.jpg)

![Port Connection Rules (cont’d) module Top; reg [3: 0] A, B; reg C_IN; reg Port Connection Rules (cont’d) module Top; reg [3: 0] A, B; reg C_IN; reg](https://slidetodoc.com/presentation_image/29a3ef527552ca6378d783e9bc38098b/image-17.jpg)

![Arrays of Gate Instances Multiple instantiations Array of instances wire [7: 0] OUT, IN Arrays of Gate Instances Multiple instantiations Array of instances wire [7: 0] OUT, IN](https://slidetodoc.com/presentation_image/29a3ef527552ca6378d783e9bc38098b/image-34.jpg)

![Examples: 4 -bit ripple-carry full adder (cont’d) module fulladd 4( output [3: 0] sum, Examples: 4 -bit ripple-carry full adder (cont’d) module fulladd 4( output [3: 0] sum,](https://slidetodoc.com/presentation_image/29a3ef527552ca6378d783e9bc38098b/image-39.jpg)

![Stimulus Block module stimulus; reg [3: 0] A, B; reg C_IN; wire [3: 0] Stimulus Block module stimulus; reg [3: 0] A, B; reg C_IN; wire [3: 0]](https://slidetodoc.com/presentation_image/29a3ef527552ca6378d783e9bc38098b/image-40.jpg)

- Slides: 48

Digital System Design Verilog® HDL Design at Structural Level Maziar Goudarzi

Verilog® HDL Modules and Ports 2010 DSD

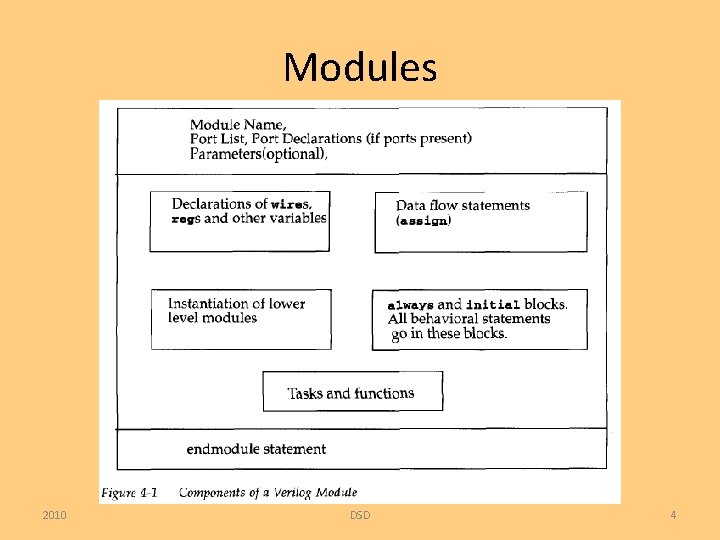

Today program • Components of a Verilog Module • Defining and Connecting Ports 2010 DSD 3

Modules 2010 DSD 4

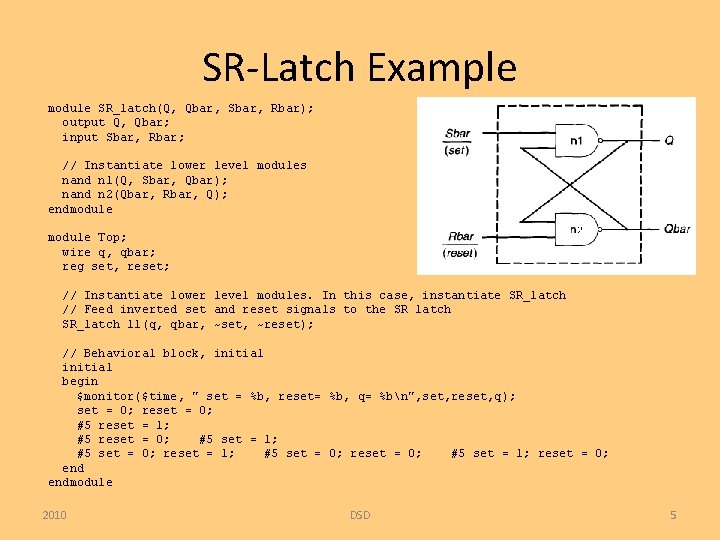

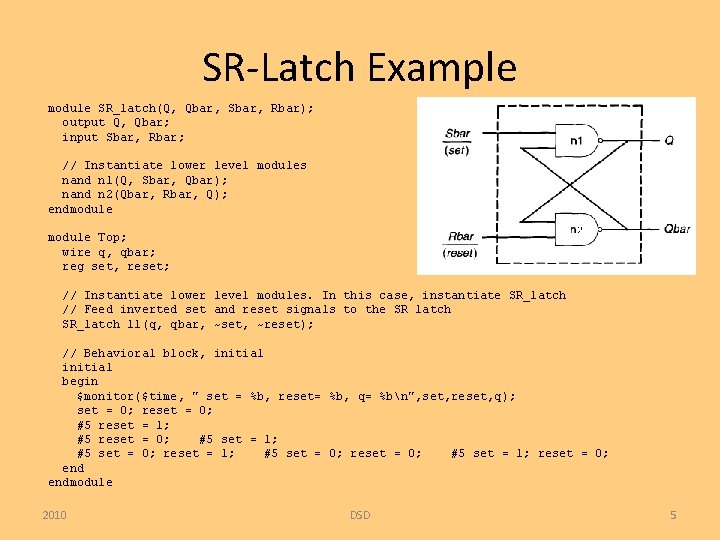

SR-Latch Example module SR_latch(Q, Qbar, Sbar, Rbar); output Q, Qbar; input Sbar, Rbar; // Instantiate lower level modules nand n 1(Q, Sbar, Qbar); nand n 2(Qbar, Rbar, Q); endmodule Top; wire q, qbar; reg set, reset; // Instantiate lower level modules. In this case, instantiate SR_latch // Feed inverted set and reset signals to the SR latch SR_latch l 1(q, qbar, ~set, ~reset); // Behavioral block, initial begin $monitor($time, " set = %b, reset= %b, q= %bn", set, reset, q); set = 0; reset = 0; #5 reset = 1; #5 reset = 0; #5 set = 1; #5 set = 0; reset = 0; #5 set = 1; reset = 0; endmodule 2010 DSD 5

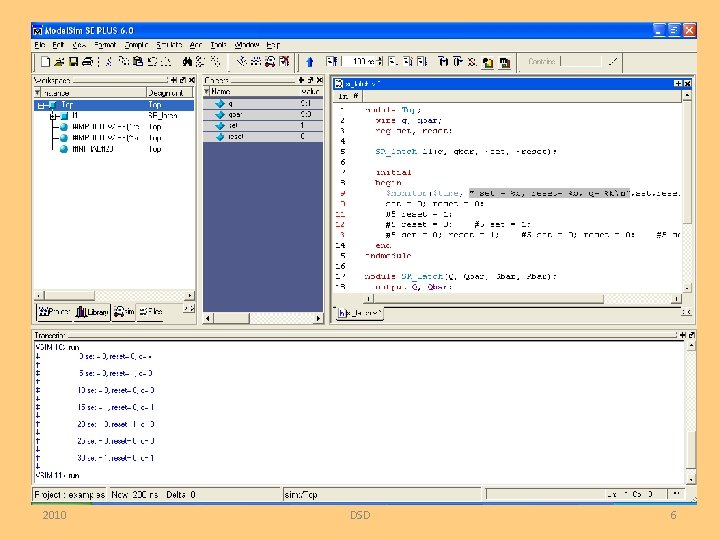

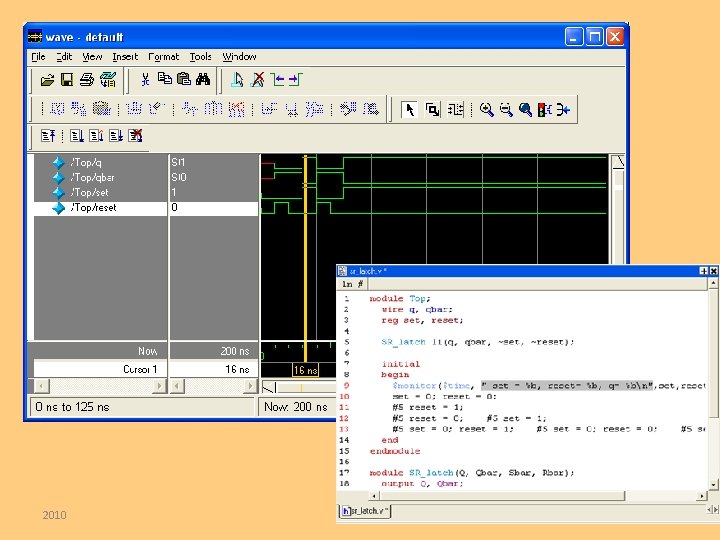

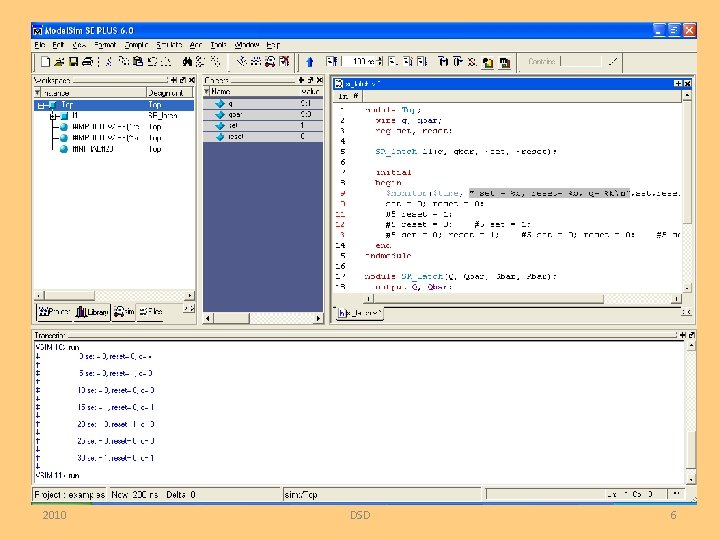

2010 DSD 6

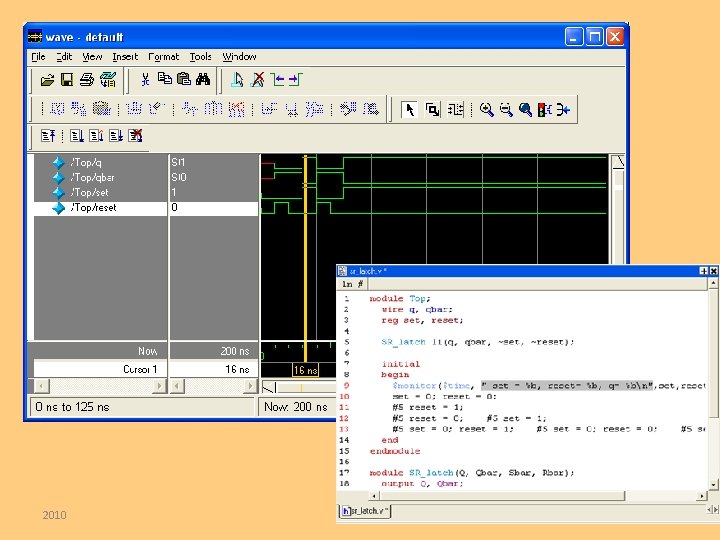

2010 DSD 7

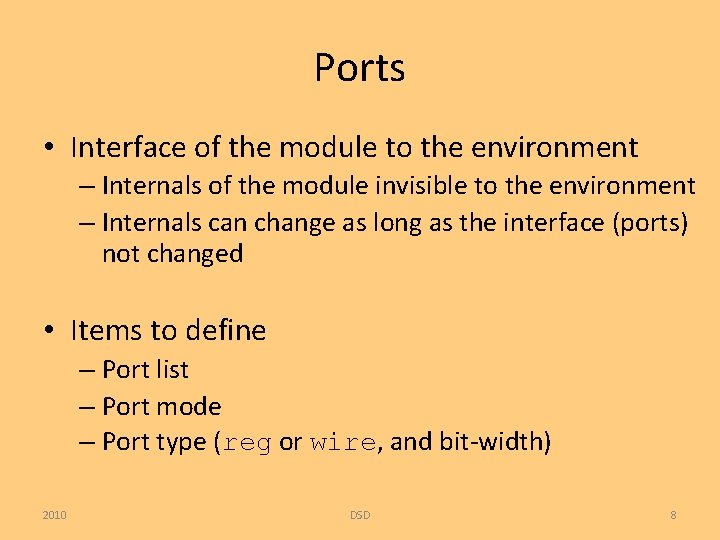

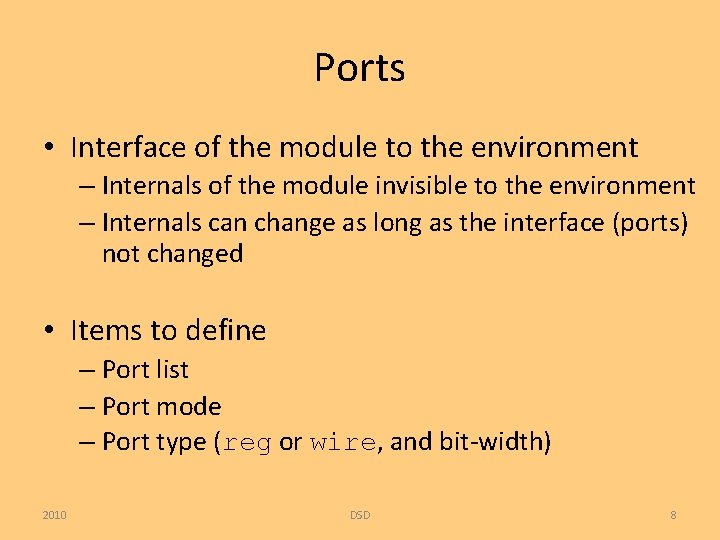

Ports • Interface of the module to the environment – Internals of the module invisible to the environment – Internals can change as long as the interface (ports) not changed • Items to define – Port list – Port mode – Port type (reg or wire, and bit-width) 2010 DSD 8

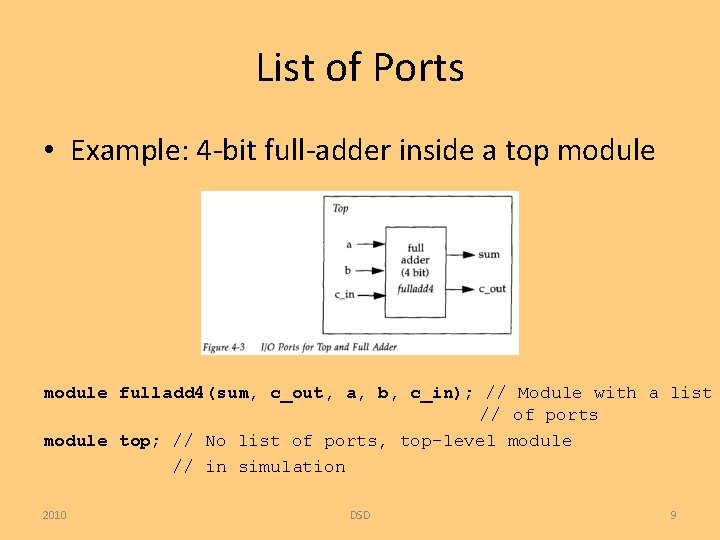

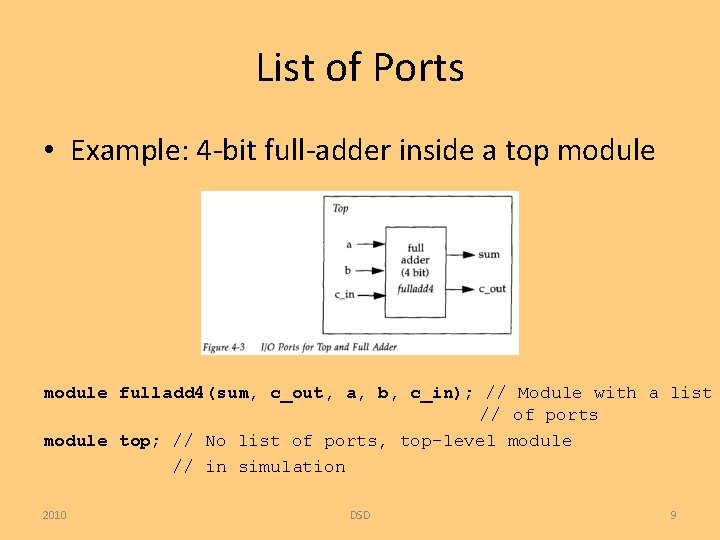

List of Ports • Example: 4 -bit full-adder inside a top module fulladd 4(sum, c_out, a, b, c_in); // Module with a list // of ports module top; // No list of ports, top-level module // in simulation 2010 DSD 9

Port Declaration • All ports in the list of ports must be declared in the module • Example: module fulladd 4(sum, c_out, a, b, c_in); output [3: 0] sum; output c_out; input [3: 0] a, b; input c_in; . . . endmodule 2010 DSD 10

Port Declaration (cont’d) • Note: all ports are wire by default – No need to declare it again as wire – If expected to be reg, the port needs to be declared again (only valid for output ports. Why? ) – Example: the q port in DFF module DFF(q, d, clk, reset); output q; reg q; // Output port q holds value => reg input d, clk, reset; . . . endmodule 2010 DSD 11

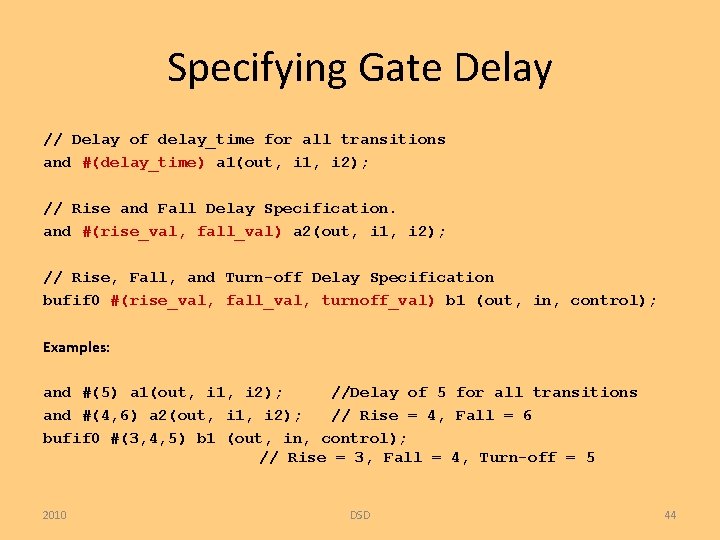

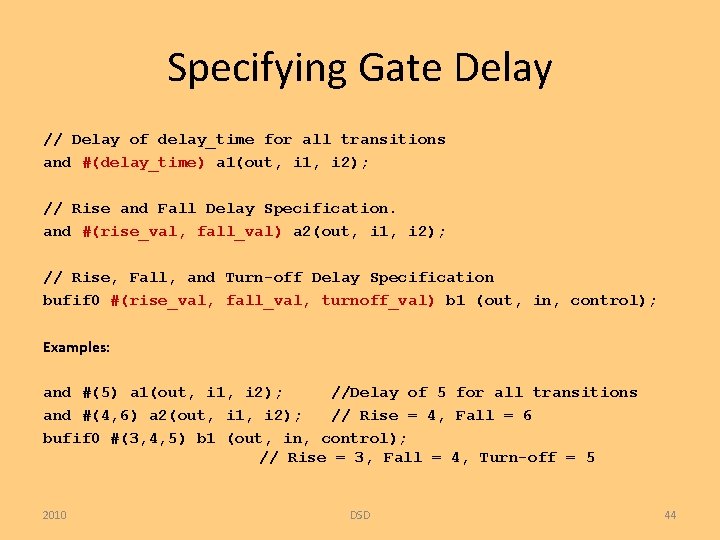

![ANSI C Style Port Declaration Syntax module fulladd 4output reg 3 0 sum output ANSI C Style Port Declaration Syntax module fulladd 4(output reg [3: 0] sum, output](https://slidetodoc.com/presentation_image/29a3ef527552ca6378d783e9bc38098b/image-12.jpg)

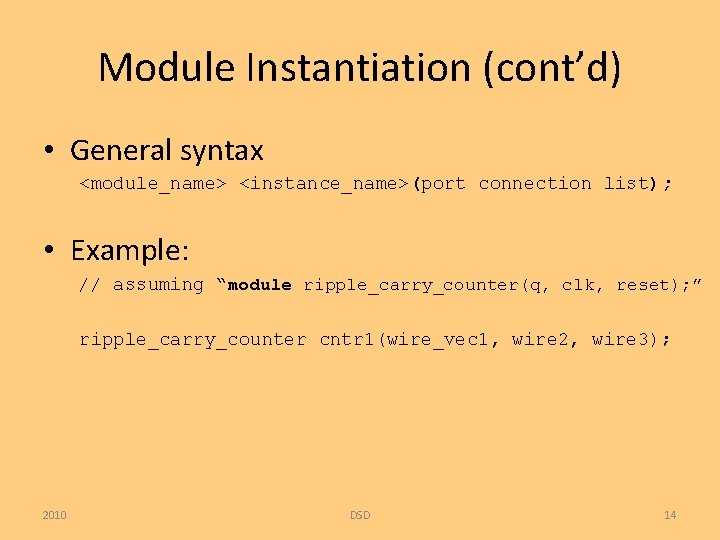

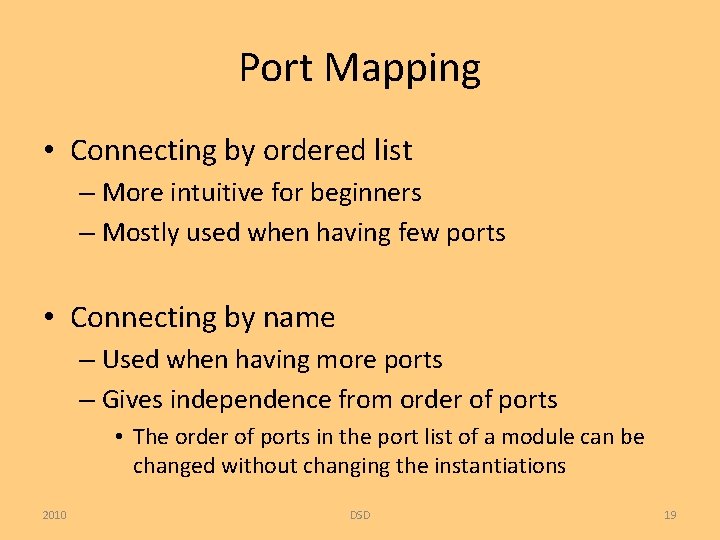

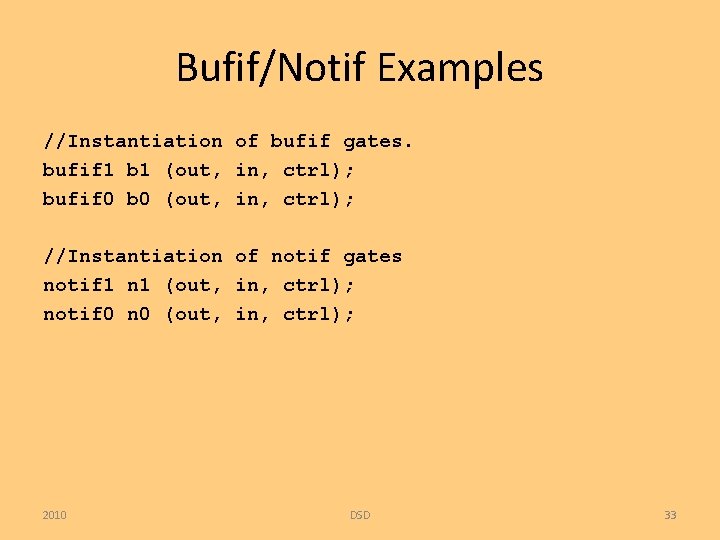

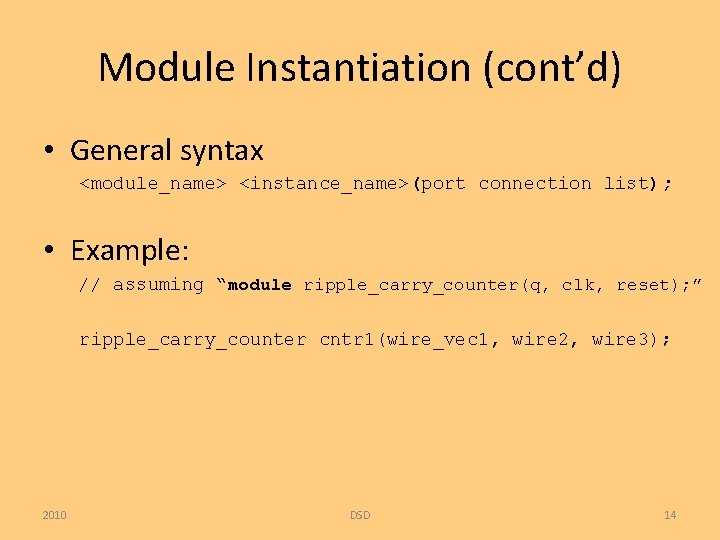

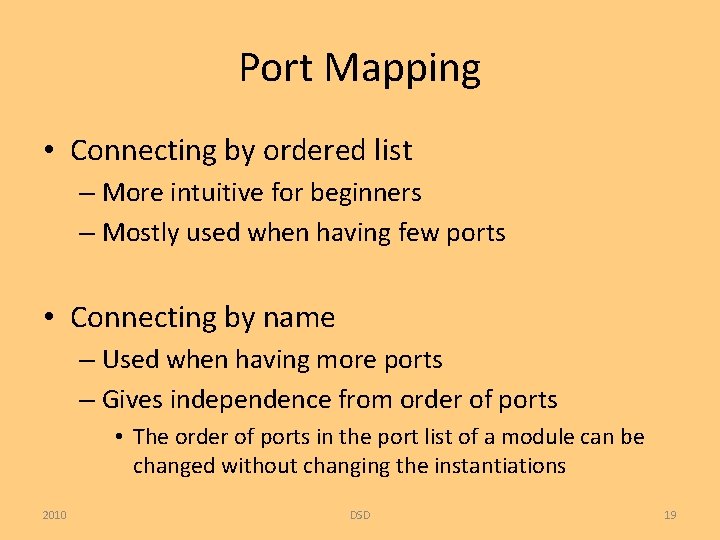

ANSI C Style Port Declaration Syntax module fulladd 4(output reg [3: 0] sum, output reg c_out, input [3: 0] a, b, //wire by default input c_in); //wire by default. . . <module internals>. . . endmodule 2010 DSD 12

Module Instantiation • Recall the Ripple-carry counter and TFF module T_FF(q, clk, reset); output q; input clk, reset; . . . endmodule ripple_carry_counter(q, clk, reset); output [3: 0] q; input clk, reset; //4 instances of the module TFF are created. T_FF tff 0(q[0], clk, reset); T_FF tff 1(q[1], q[0], reset); T_FF tff 2(q[2], q[1], reset); T_FF tff 3(q[3], q[2], reset); endmodule 2010 DSD 13

Module Instantiation (cont’d) • General syntax <module_name> <instance_name>(port connection list); • Example: // assuming “module ripple_carry_counter(q, clk, reset); ” ripple_carry_counter cntr 1(wire_vec 1, wire 2, wire 3); 2010 DSD 14

Port Connection Rules • Two parts of a port: – internal to module (when defining the module) – external to module (when instantiating the module) 2010 DSD 15

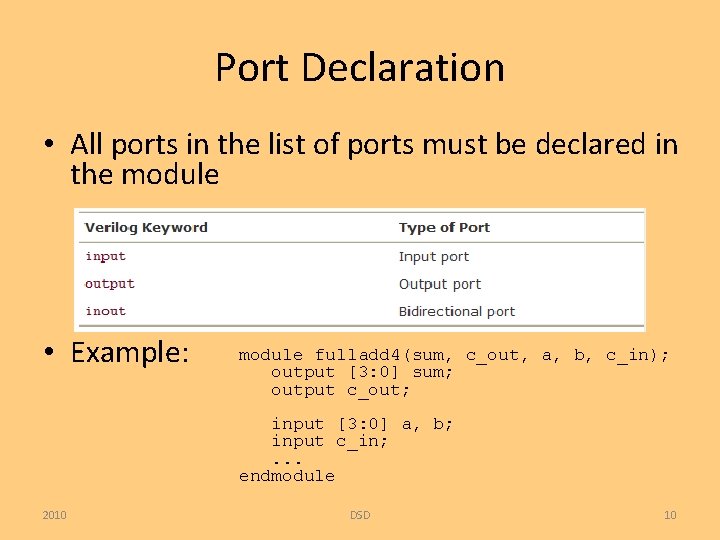

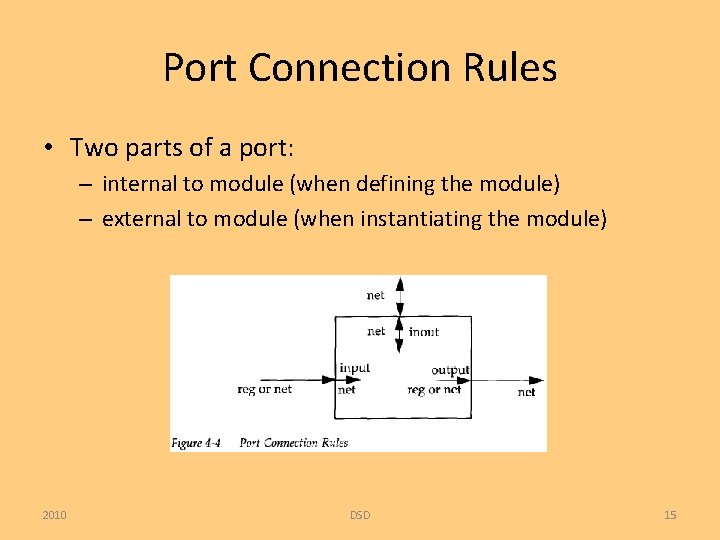

Port Connection Rules (cont’d) • Width matching – Legal to connect items of different sizes • A warning may be issued by Verilog simulator • Unconnected ports – Allowed in Verilog – Example: // assuming “module fulladd 4(sum, c_out, a, b, c_in); ” fulladd 4 fa 0(SUM, , A, B, C_IN); // output port c_out is unconnected 2010 DSD 16

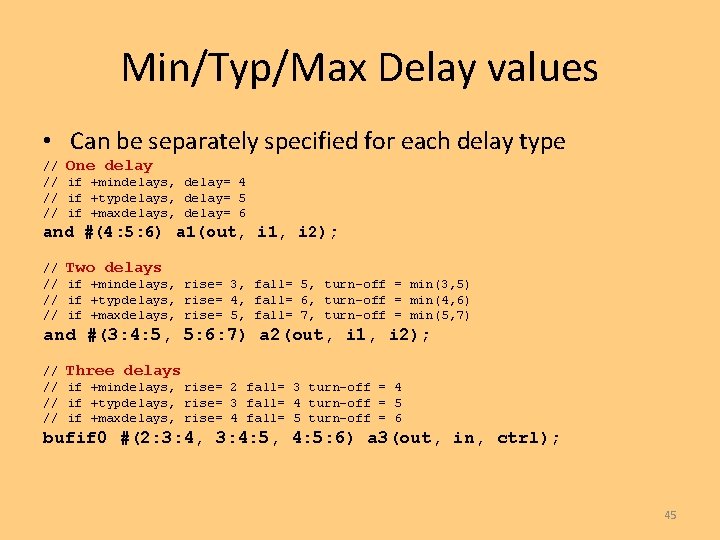

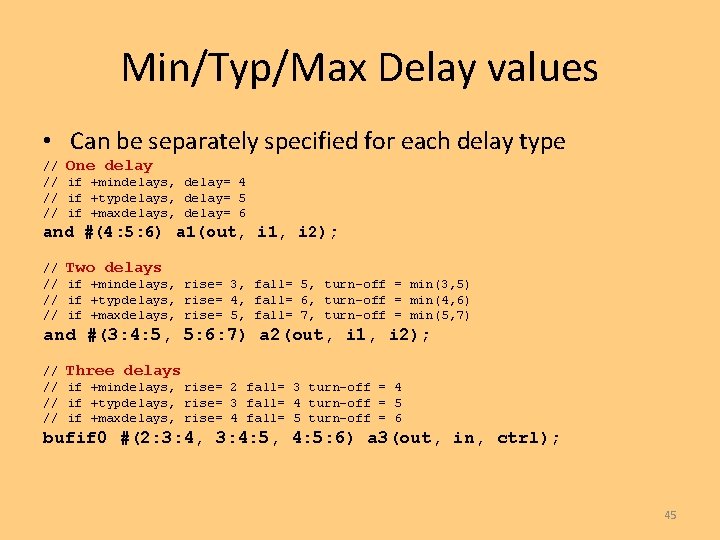

![Port Connection Rules contd module Top reg 3 0 A B reg CIN reg Port Connection Rules (cont’d) module Top; reg [3: 0] A, B; reg C_IN; reg](https://slidetodoc.com/presentation_image/29a3ef527552ca6378d783e9bc38098b/image-17.jpg)

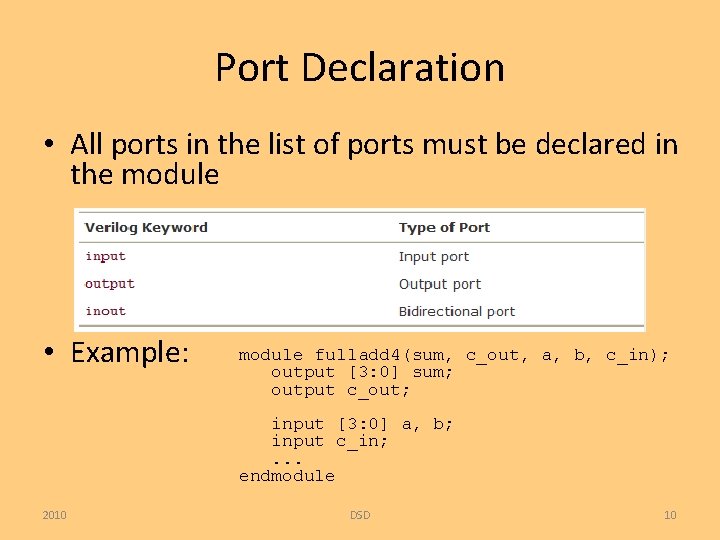

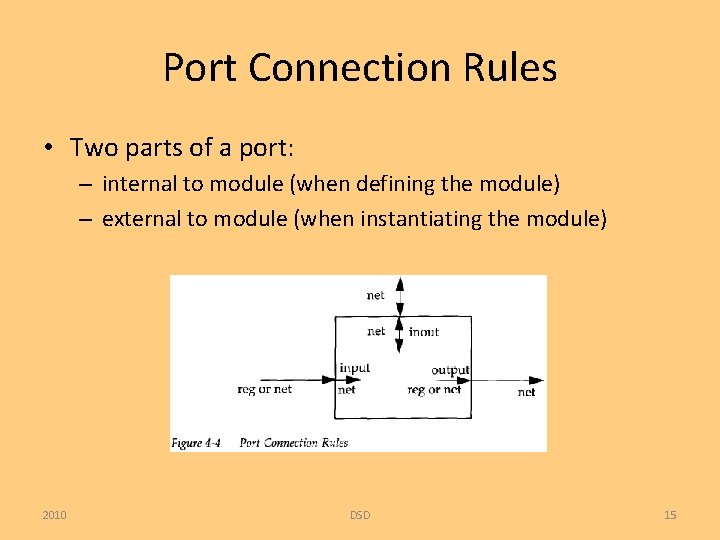

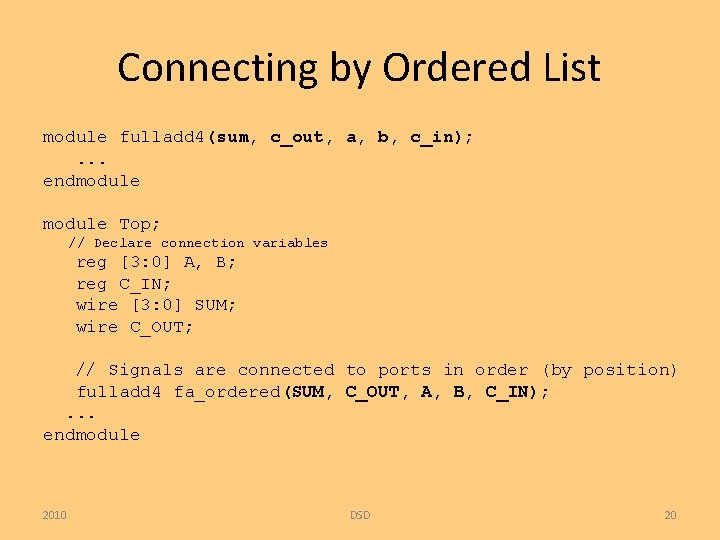

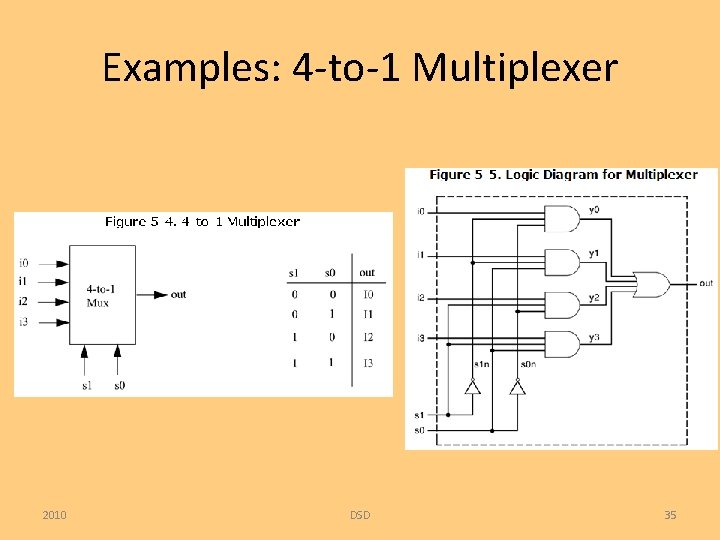

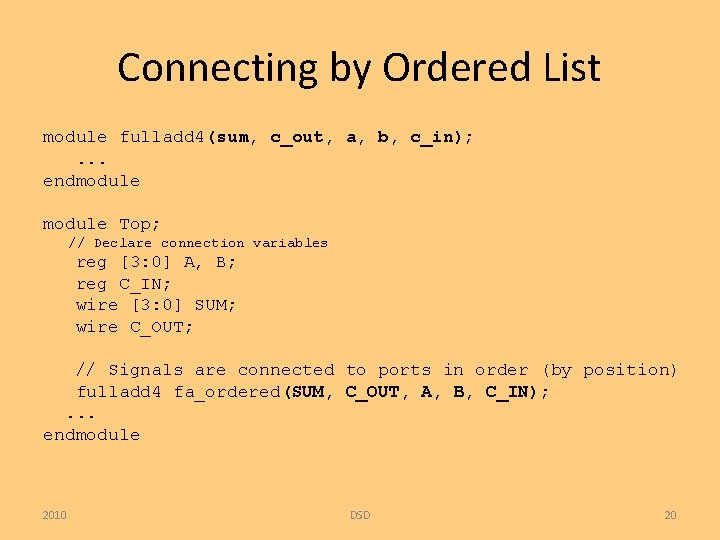

Port Connection Rules (cont’d) module Top; reg [3: 0] A, B; reg C_IN; reg [3: 0] SUM; wire C_OUT; module fulladd 4(output reg [3: 0] sum, output reg c_out, input [3: 0] a, b, input c_in); . . . endmodule // Instantiate fulladd 4, call it fa 0 fulladd 4 fa 0(SUM, C_OUT, A, B, C_IN); // legal or Illegal? Why? . . . endmodule // Top 2010 DSD 17

2010 DSD 18

Port Mapping • Connecting by ordered list – More intuitive for beginners – Mostly used when having few ports • Connecting by name – Used when having more ports – Gives independence from order of ports • The order of ports in the port list of a module can be changed without changing the instantiations 2010 DSD 19

Connecting by Ordered List module fulladd 4(sum, c_out, a, b, c_in); . . . endmodule Top; // Declare connection variables reg [3: 0] A, B; reg C_IN; wire [3: 0] SUM; wire C_OUT; // Signals are connected to ports in order (by position) fulladd 4 fa_ordered(SUM, C_OUT, A, B, C_IN); . . . endmodule 2010 DSD 20

Connecting Ports by Name module fulladd 4(sum, c_out, a, b, c_in); . . . endmodule Top; // Declare connection variables reg [3: 0] A, B; reg C_IN; wire [3: 0] SUM; wire C_OUT; // Signals are connected to ports by name fulladd 4 fa_byname(. c_out(C_OUT), . sum(SUM), . b(B), . a(A)); . . . endmodule 2010 DSD 21

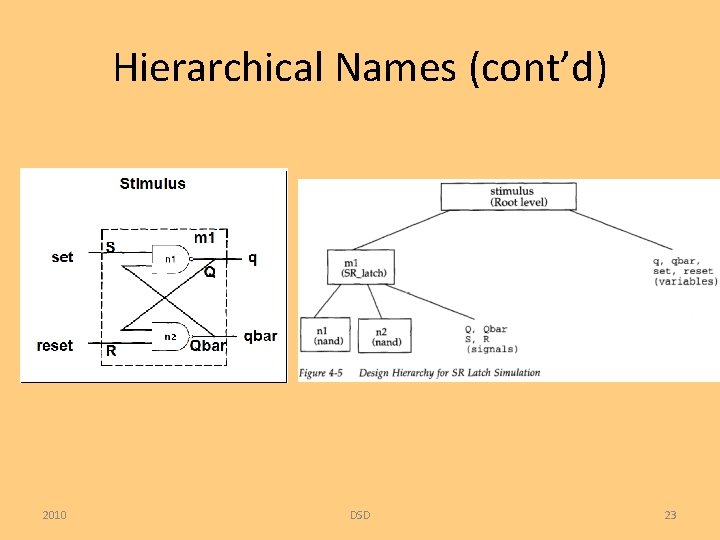

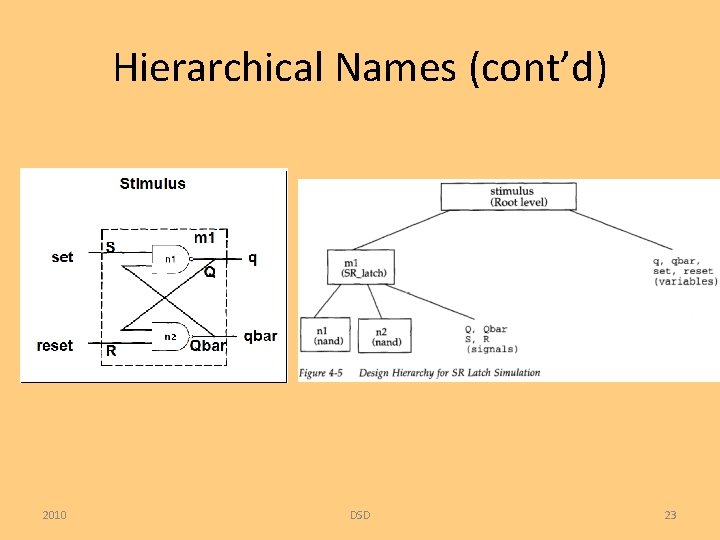

Hierarchical Names • Hierarchical design – An identifier for every signal, variable, or module instance – The same identifier can be used in different levels of the hierarchy – Hierarchical name referencing • Unique name to every identifier in the hierarchy • Syntax: <top-module-name>. <instance-name>. <identifier> 2010 DSD 22

Hierarchical Names (cont’d) 2010 DSD 23

Hierarchical Names (cont’d) module stimulus; wire q, qbar; reg set, reset; SR_latch m 1(q, qbar, ~set, ~reset); initial. . . endmodule SR_latch(Q, Qbar, S, R); output Q, Qbar; input S, R; nand n 1(Q, S, Qbar); nand n 2(Qbar, R, Q); endmodule • Hierarchical names 2010 stimulus. set stimulus. m 1. Q stimulus. m 1. R stimulus. q stimulus. reset stimulus. m 1. Qbar stimulus. m 1. n 1 DSD stimulus. qbar stimulus. m 1. S stimulus. m 1. n 2 24

Have you learned this topic? • How to – Define modules – Instantiate modules – Do port mapping • Components of a module • Hierarchical Design in Verilog HDL® 2010 DSD 25

Today Objectives • • 2010 Add Switch modeling Primitive gates in Verilog Structural design using primitive gates Gate-level delay types and syntax DSD 26

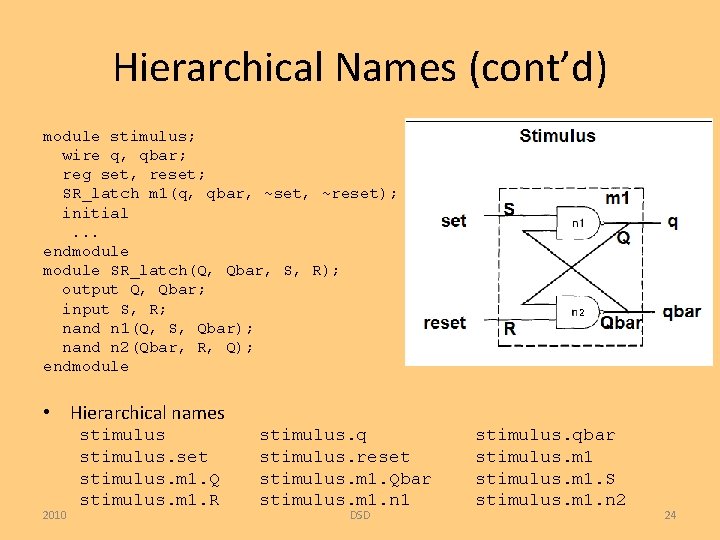

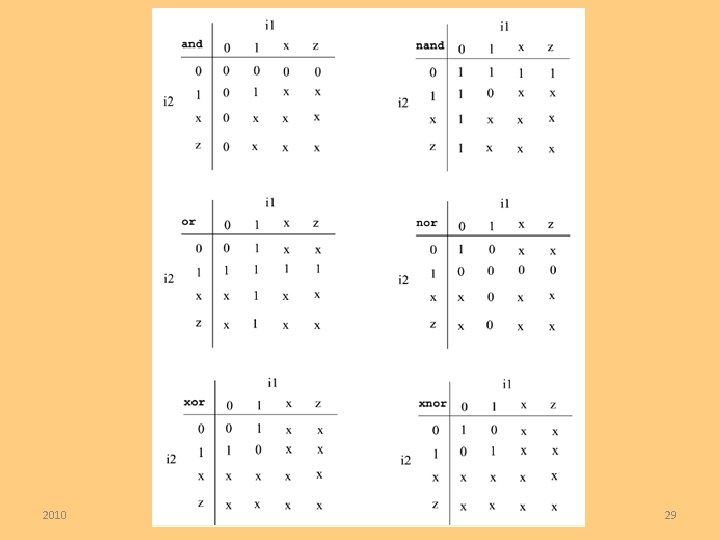

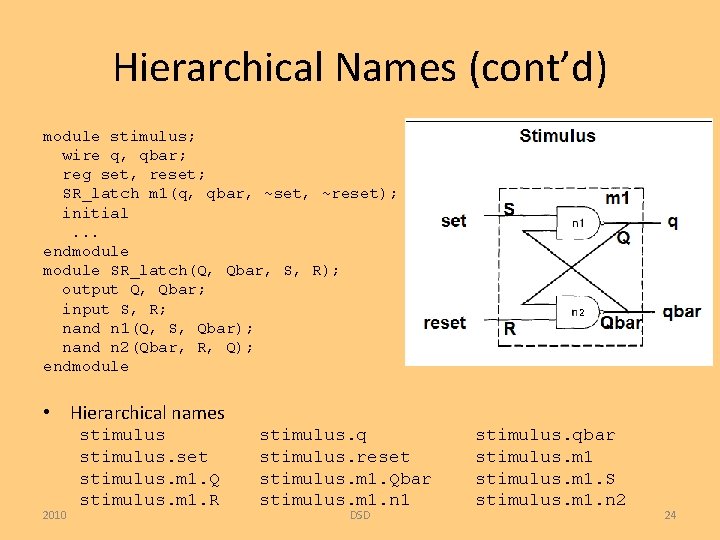

Primitive Gates in Verilog: And/Or Gates 2010 DSD 27

And/Or Gates Examples • Syntax – Similar to module instantiations • Examples wire out, in 1, in 2, in 3; and a 1(out, in 1, in 2); nand na 1_3 inp(out, in 1, in 2, in 3); and (out, in 1, in 2); // Legal gate instantiation. No need to instance name. 2010 DSD 28

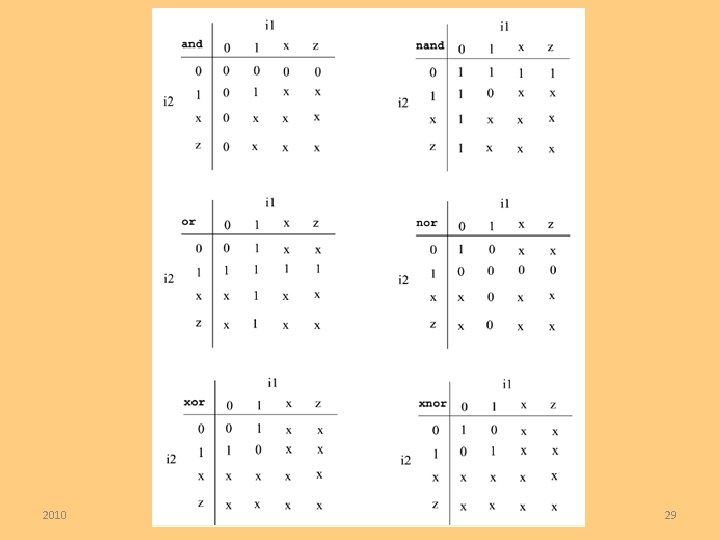

2010 29

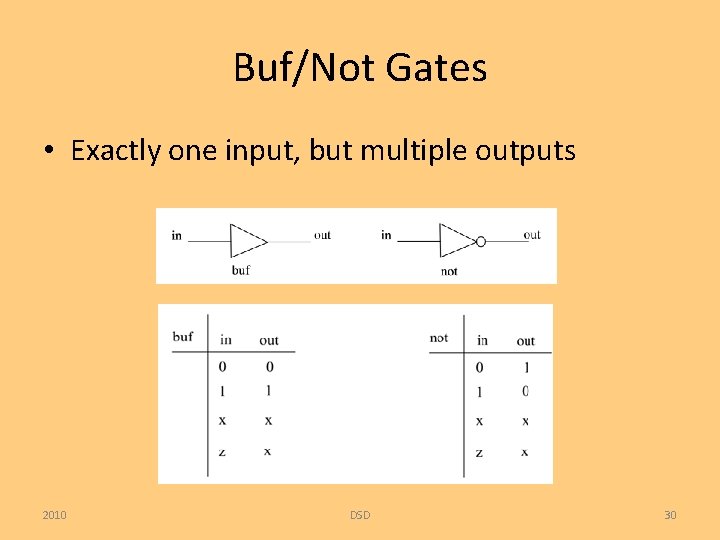

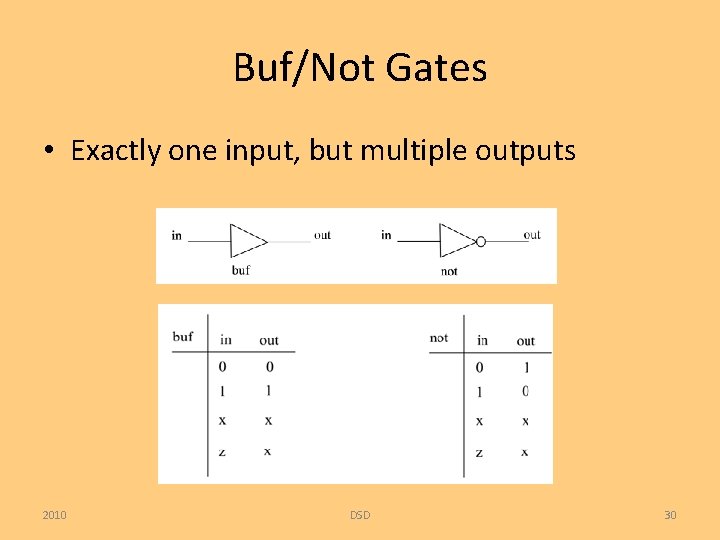

Buf/Not Gates • Exactly one input, but multiple outputs 2010 DSD 30

Buf/Not Gate Examples // basic gate instantiations. buf b 1(OUT 1, IN); not n 1(OUT 1, IN); // More than two outputs buf b 1_2 out(OUT 1, OUT 2, IN); // gate instantiation without instance name not (OUT 1, IN); // legal gate instantiation 2010 DSD 31

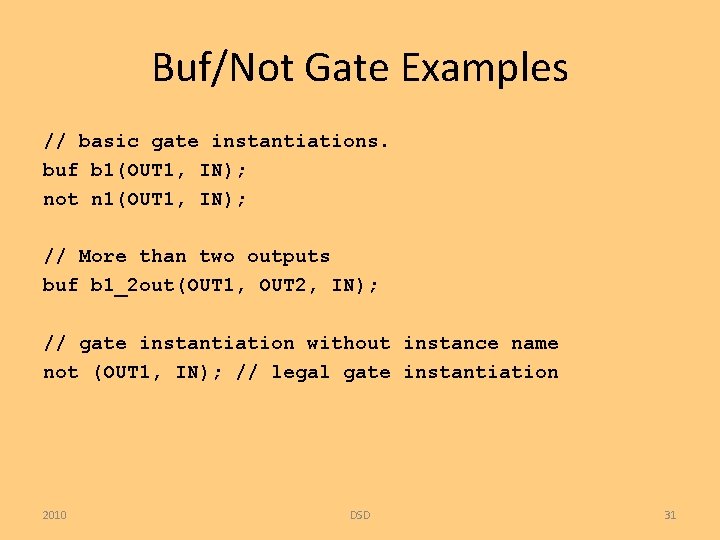

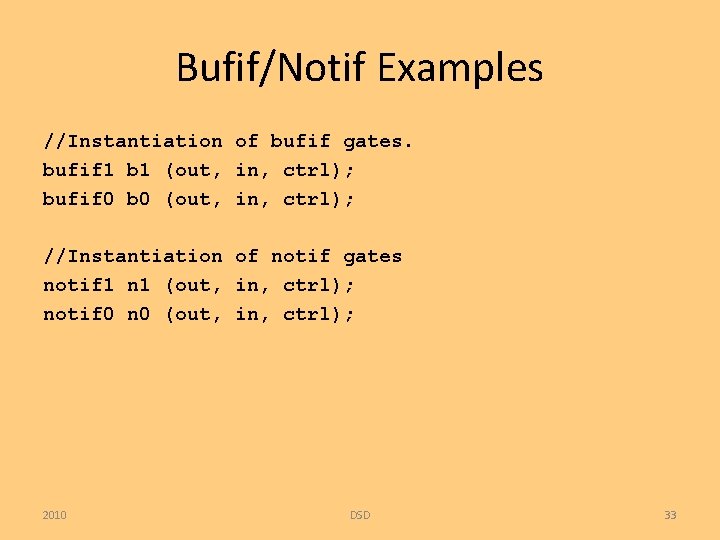

Bufif/Notif Gates 2010 DSD 32

Bufif/Notif Examples //Instantiation of bufif gates. bufif 1 b 1 (out, in, ctrl); bufif 0 b 0 (out, in, ctrl); //Instantiation of notif gates notif 1 n 1 (out, in, ctrl); notif 0 n 0 (out, in, ctrl); 2010 DSD 33

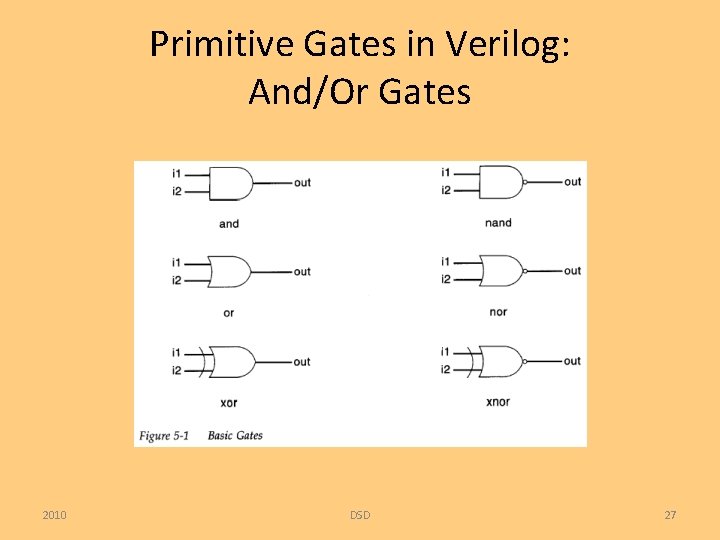

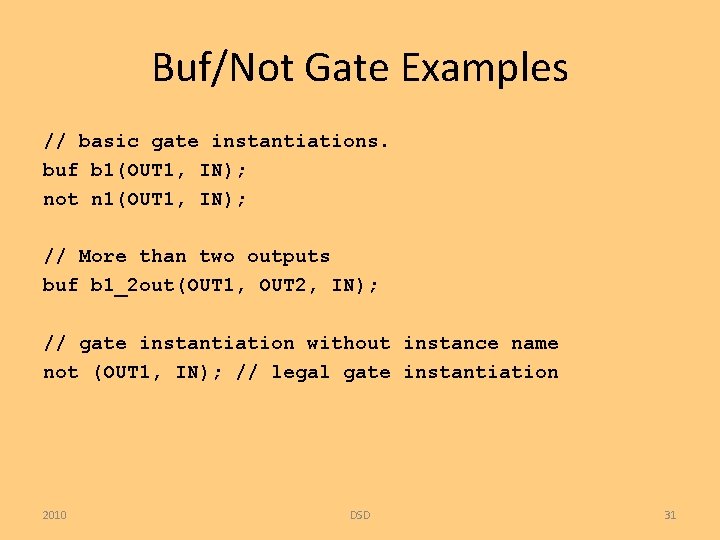

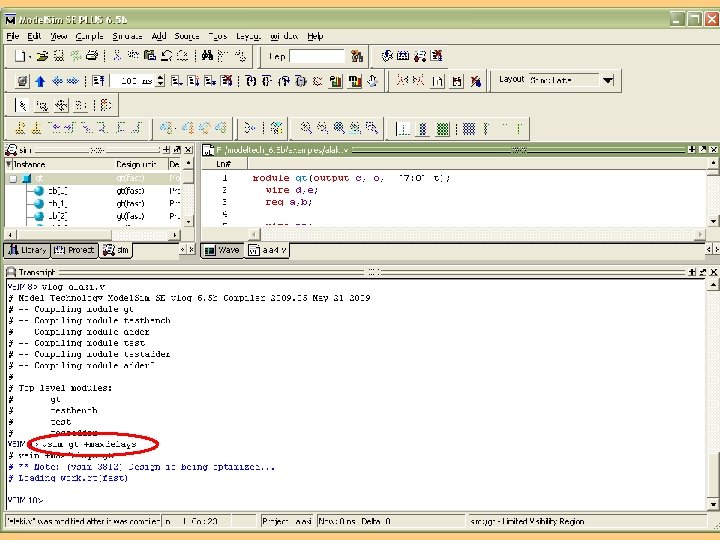

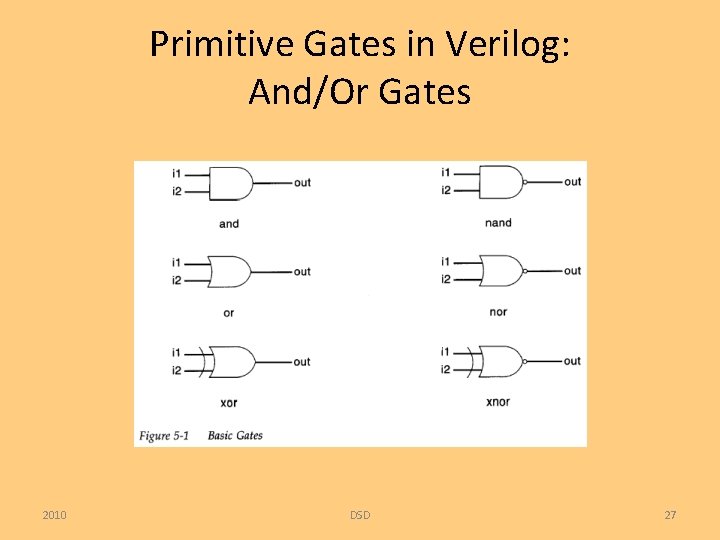

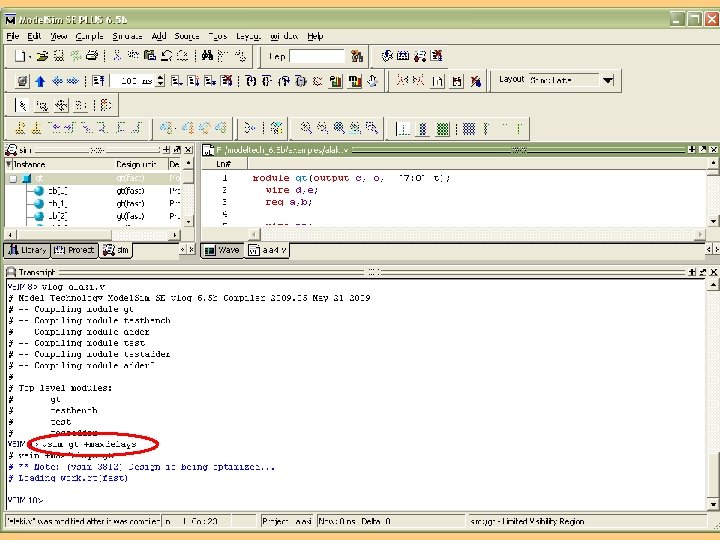

![Arrays of Gate Instances Multiple instantiations Array of instances wire 7 0 OUT IN Arrays of Gate Instances Multiple instantiations Array of instances wire [7: 0] OUT, IN](https://slidetodoc.com/presentation_image/29a3ef527552ca6378d783e9bc38098b/image-34.jpg)

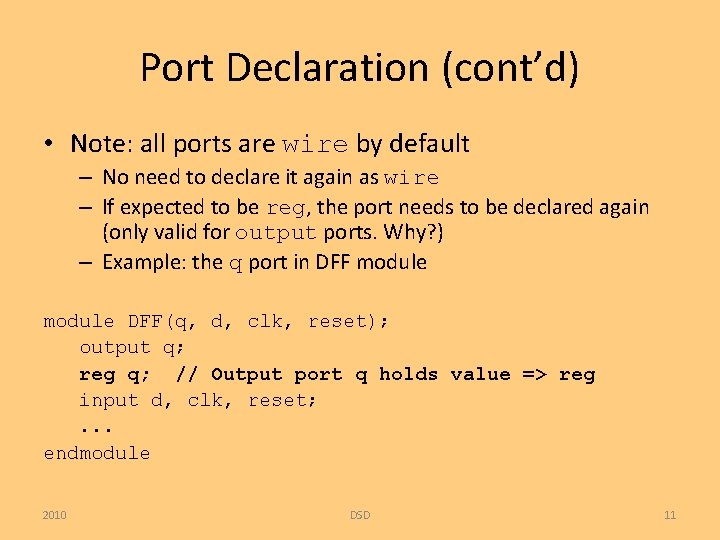

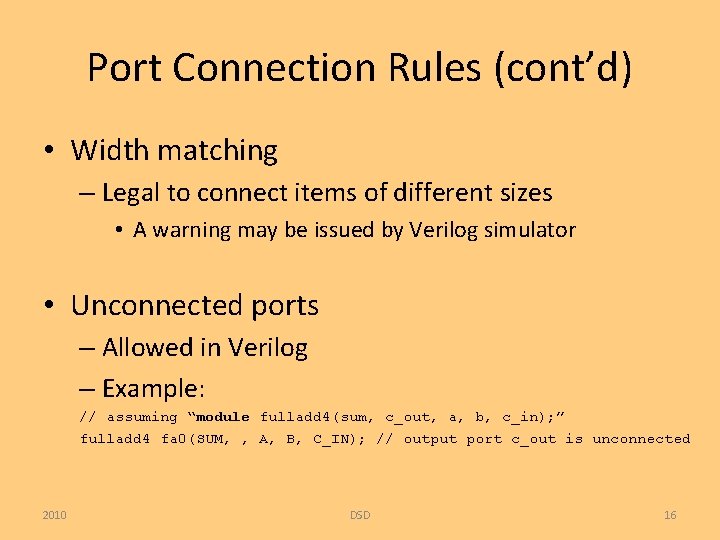

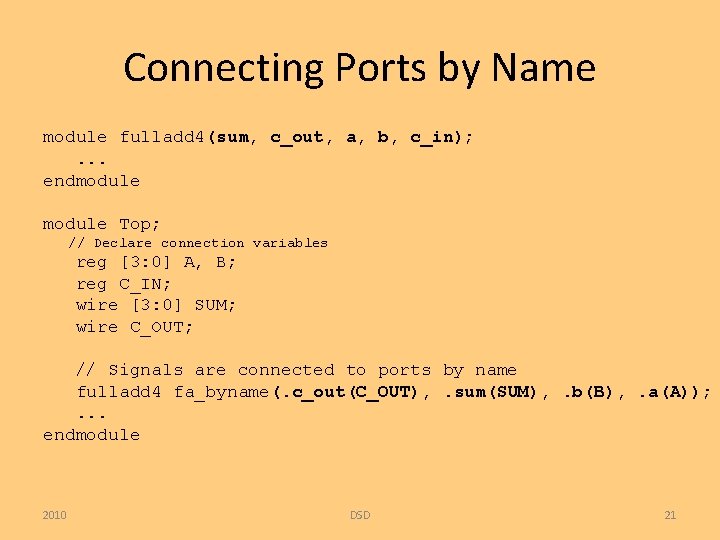

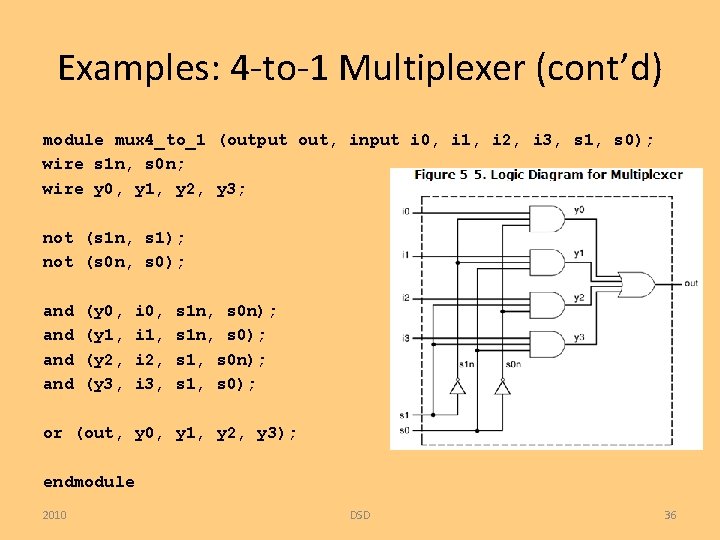

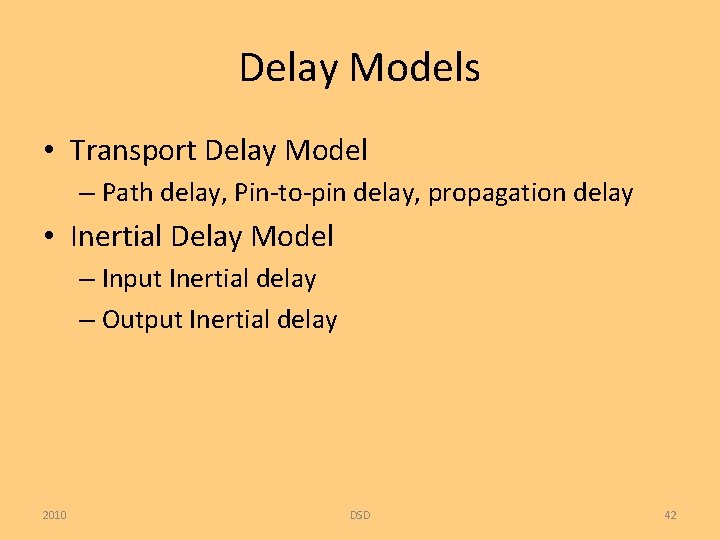

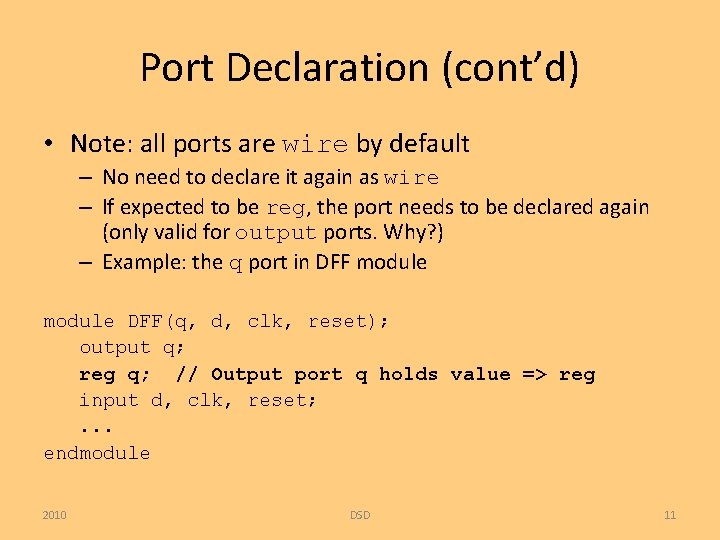

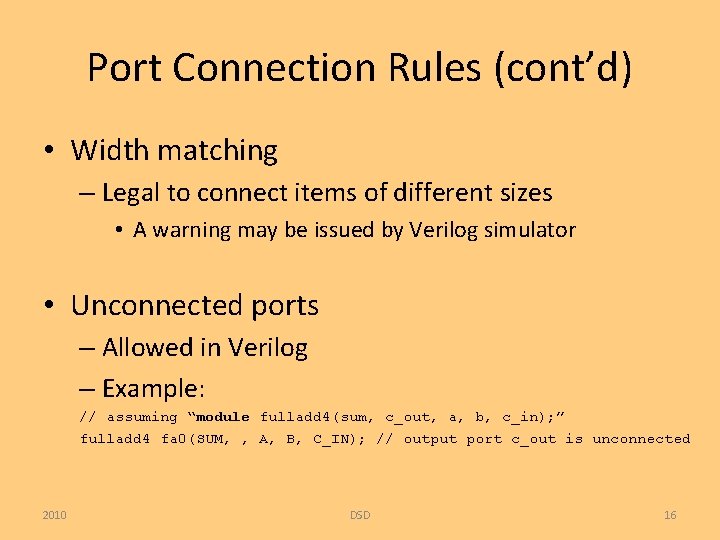

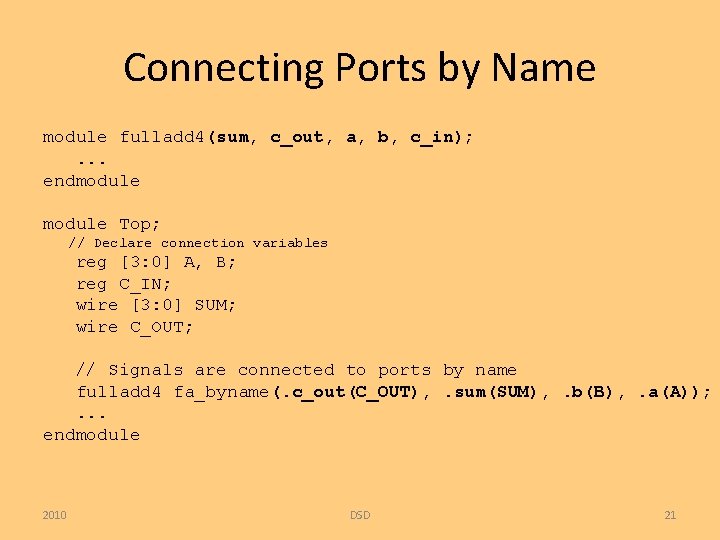

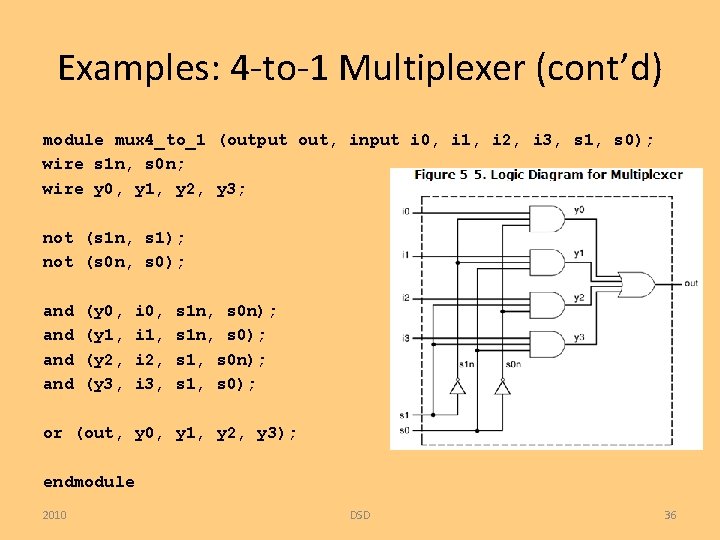

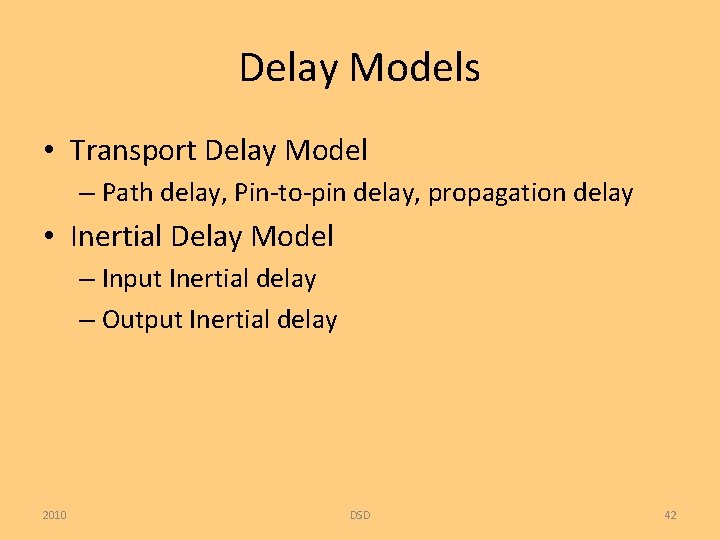

Arrays of Gate Instances Multiple instantiations Array of instances wire [7: 0] OUT, IN 1, IN 2; nand nand nand n[7: 0](OUT, IN 1, IN 2); 2010 n 0(OUT[0], n 1(OUT[1], n 2(OUT[2], n 3(OUT[3], n 4(OUT[4], n 5(OUT[5], n 6(OUT[6], n 7(OUT[7], IN 1[0], IN 2[0]); IN 1[1], IN 2[1]); IN 1[2], IN 2[2]); IN 1[3], IN 2[3]); IN 1[4], IN 2[4]); IN 1[5], IN 2[5]); IN 1[6], IN 2[6]); IN 1[7], IN 2[7]); DSD 34

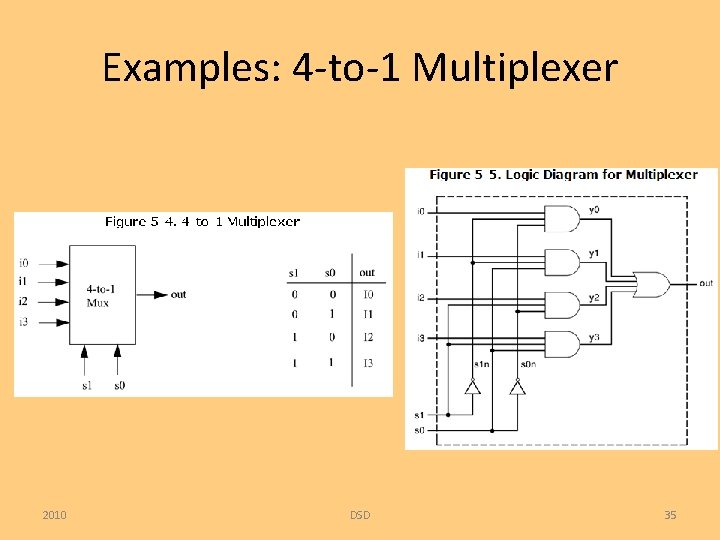

Examples: 4 -to-1 Multiplexer 2010 DSD 35

Examples: 4 -to-1 Multiplexer (cont’d) module mux 4_to_1 (output out, input i 0, i 1, i 2, i 3, s 1, s 0); wire s 1 n, s 0 n; wire y 0, y 1, y 2, y 3; not (s 1 n, s 1); not (s 0 n, s 0); and and (y 0, (y 1, (y 2, (y 3, i 0, i 1, i 2, i 3, s 1 n, s 0 n); s 1 n, s 0); s 1, s 0 n); s 1, s 0); or (out, y 0, y 1, y 2, y 3); endmodule 2010 DSD 36

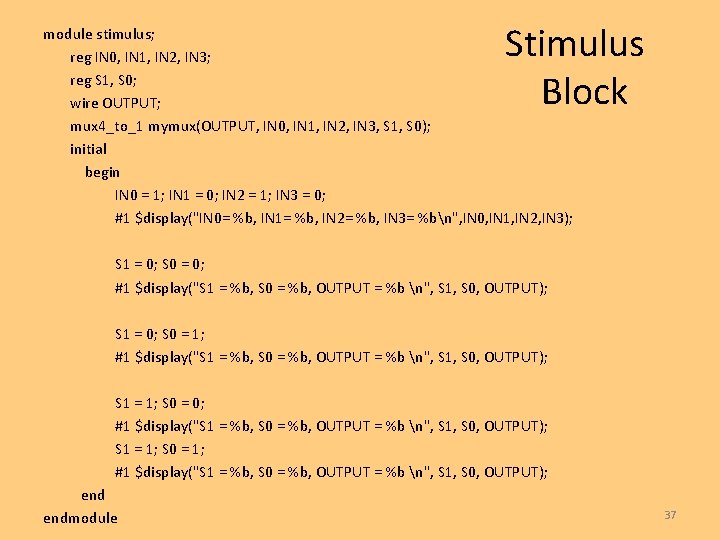

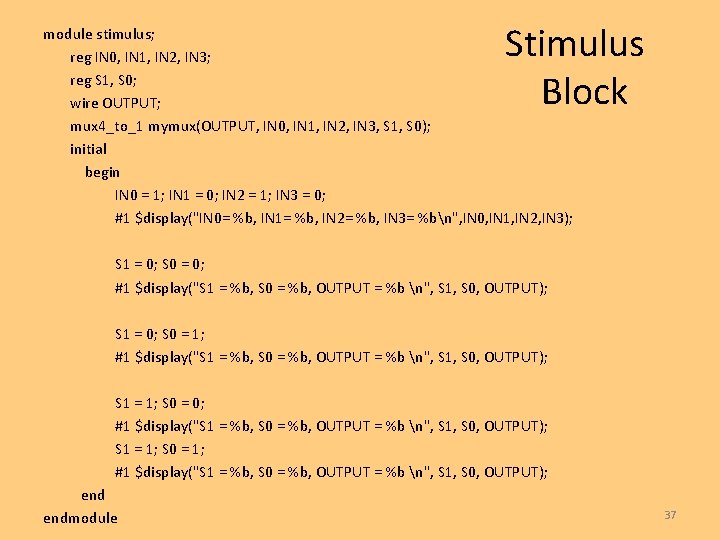

Stimulus Block module stimulus; reg IN 0, IN 1, IN 2, IN 3; reg S 1, S 0; wire OUTPUT; mux 4_to_1 mymux(OUTPUT, IN 0, IN 1, IN 2, IN 3, S 1, S 0); initial begin IN 0 = 1; IN 1 = 0; IN 2 = 1; IN 3 = 0; #1 $display("IN 0= %b, IN 1= %b, IN 2= %b, IN 3= %bn", IN 0, IN 1, IN 2, IN 3); S 1 = 0; S 0 = 0; #1 $display("S 1 = %b, S 0 = %b, OUTPUT = %b n", S 1, S 0, OUTPUT); S 1 = 0; S 0 = 1; #1 $display("S 1 = %b, S 0 = %b, OUTPUT = %b n", S 1, S 0, OUTPUT); S 1 = 1; S 0 = 0; #1 $display("S 1 = %b, S 0 = %b, OUTPUT = %b n", S 1, S 0, OUTPUT); S 1 = 1; S 0 = 1; #1 $display("S 1 = %b, S 0 = %b, OUTPUT = %b n", S 1, S 0, OUTPUT); endmodule 37

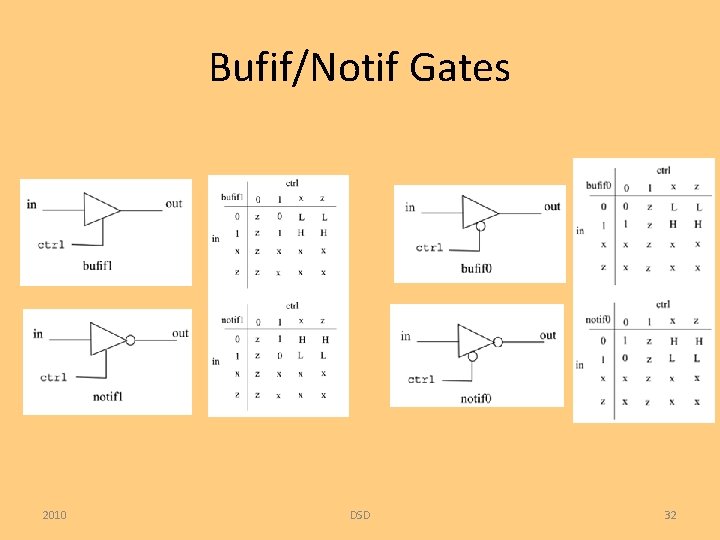

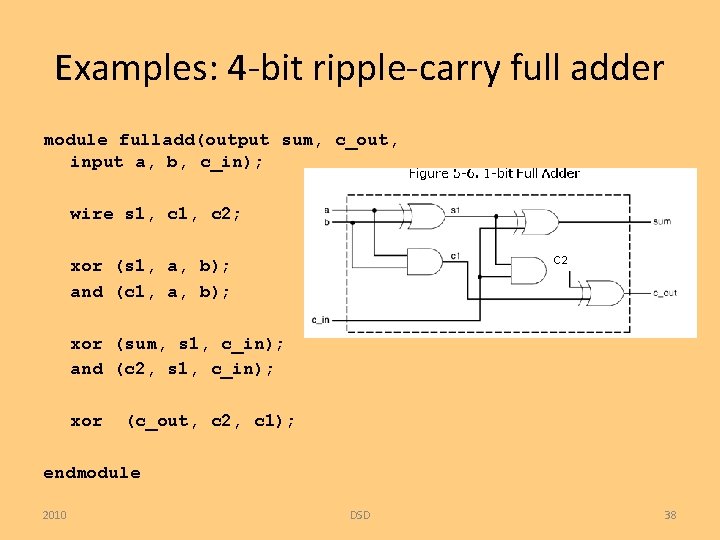

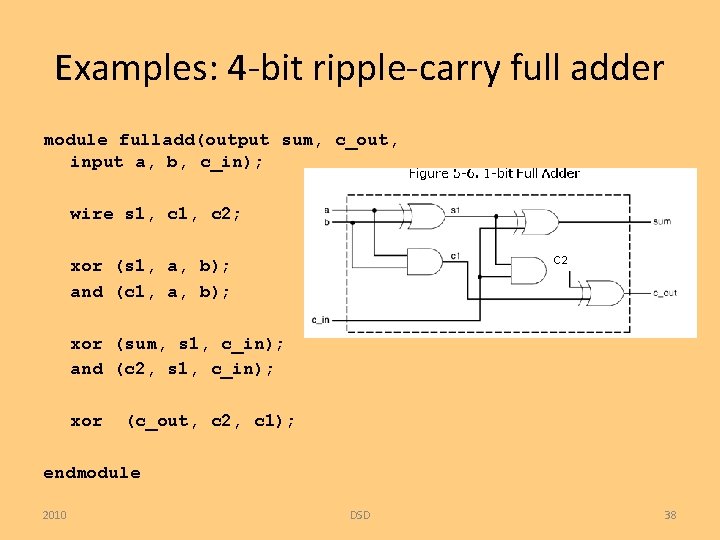

Examples: 4 -bit ripple-carry full adder module fulladd(output sum, c_out, input a, b, c_in); wire s 1, c 2; C 2 xor (s 1, a, b); and (c 1, a, b); xor (sum, s 1, c_in); and (c 2, s 1, c_in); xor (c_out, c 2, c 1); endmodule 2010 DSD 38

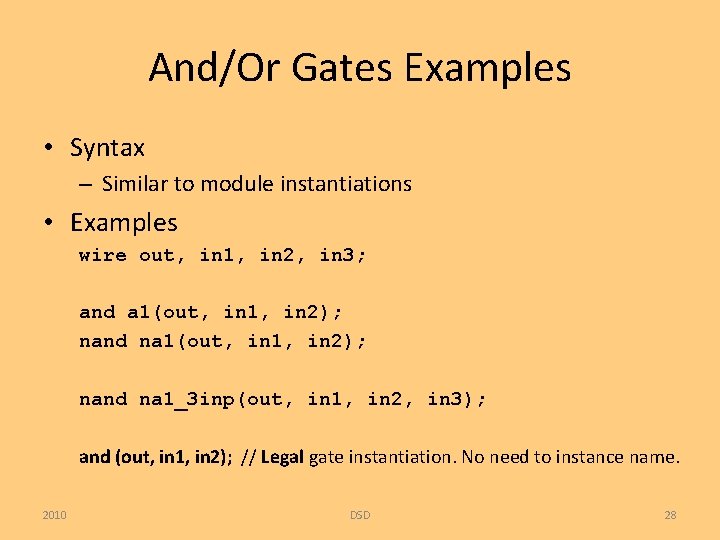

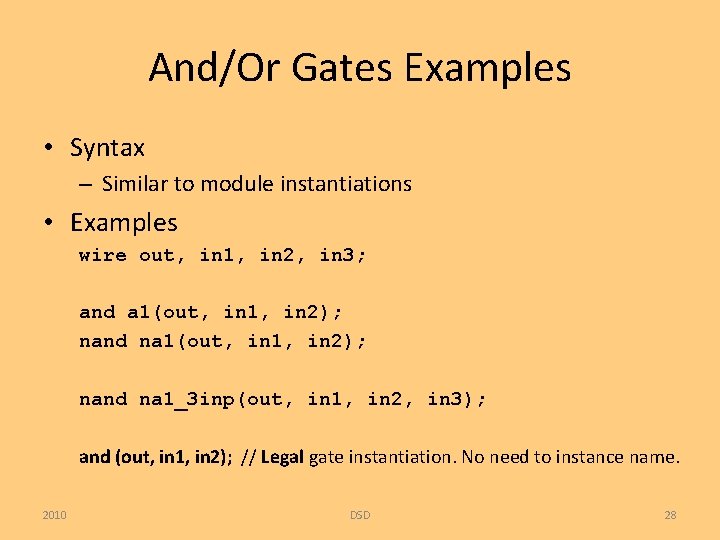

![Examples 4 bit ripplecarry full adder contd module fulladd 4 output 3 0 sum Examples: 4 -bit ripple-carry full adder (cont’d) module fulladd 4( output [3: 0] sum,](https://slidetodoc.com/presentation_image/29a3ef527552ca6378d783e9bc38098b/image-39.jpg)

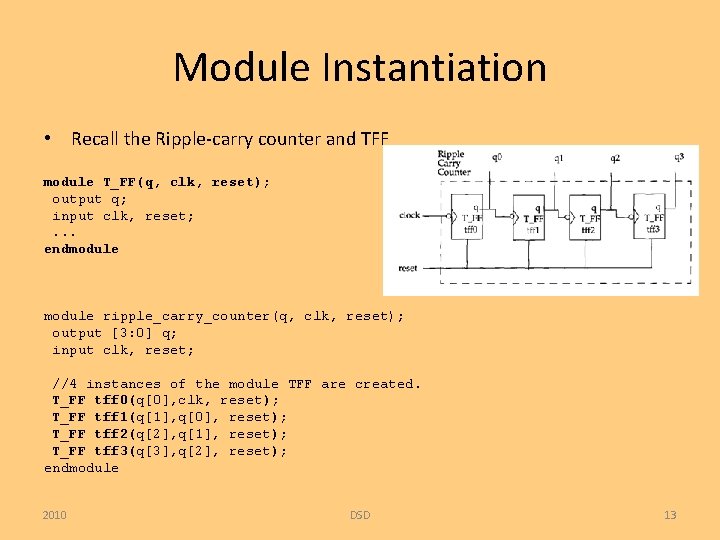

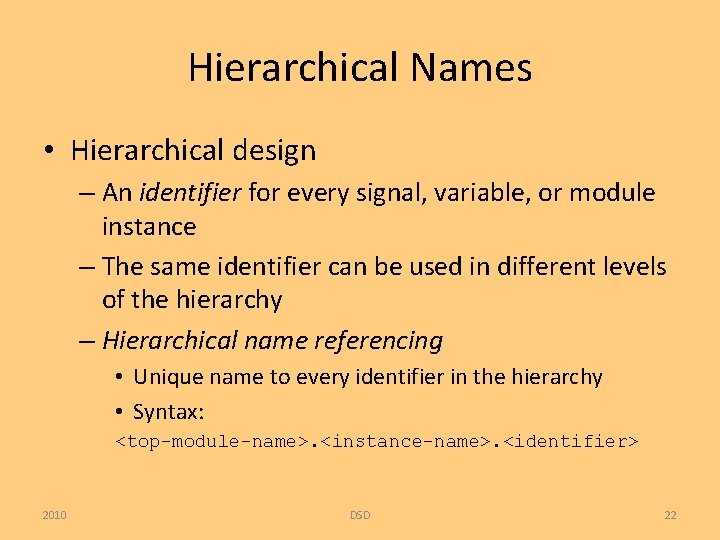

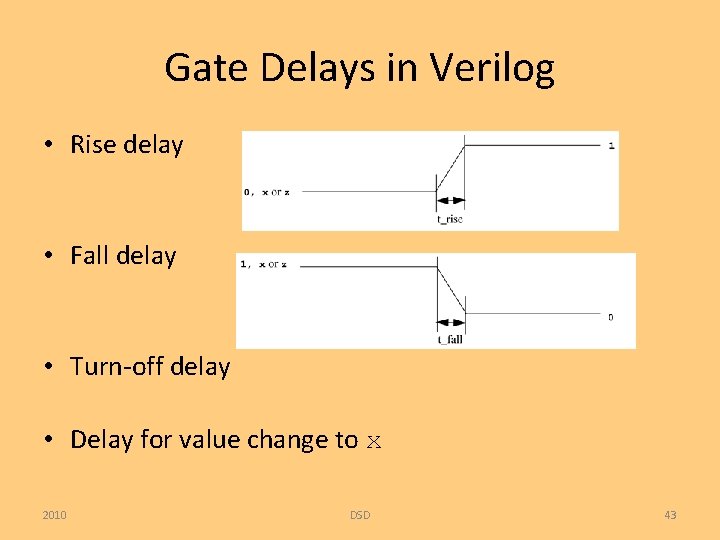

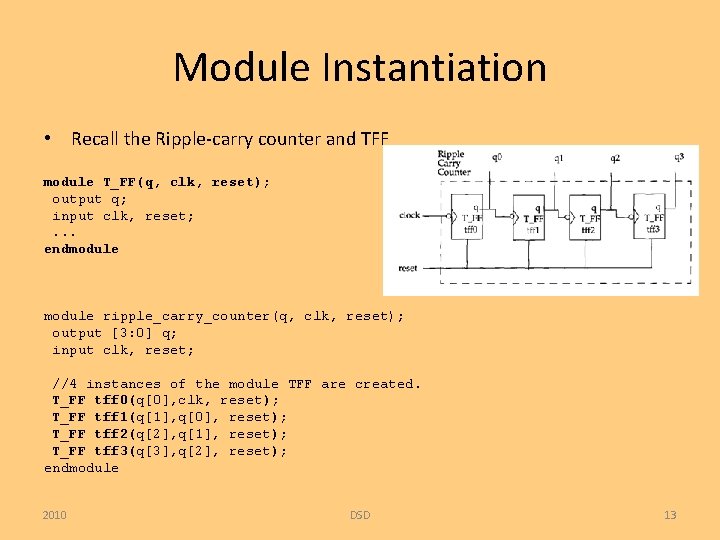

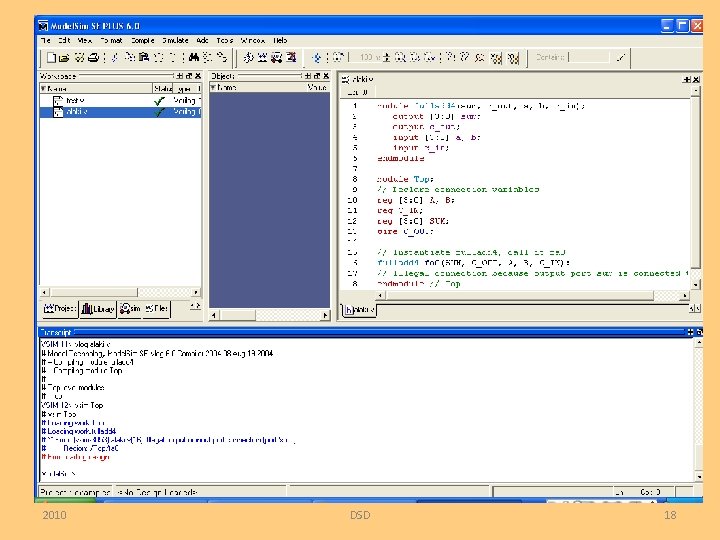

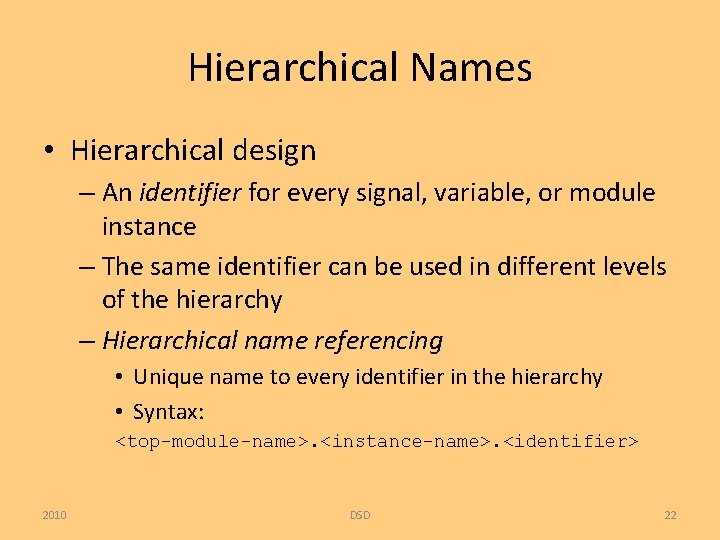

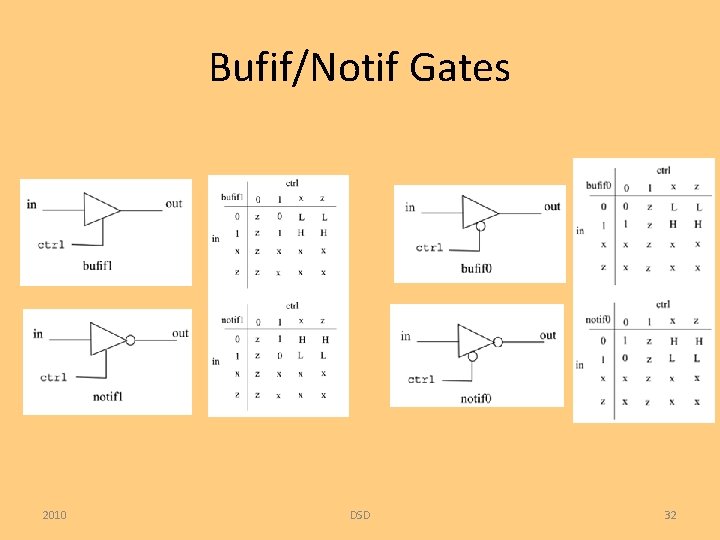

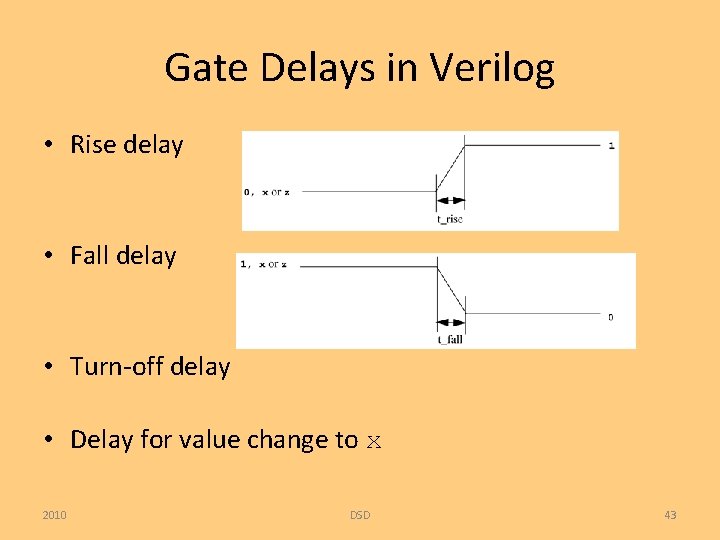

Examples: 4 -bit ripple-carry full adder (cont’d) module fulladd 4( output [3: 0] sum, output c_out, input [3: 0] a, b, input c_in); wire c 1, c 2, c 3; // Instantiate four fulladd fa 0(sum[0], fulladd fa 1(sum[1], fulladd fa 2(sum[2], fulladd fa 3(sum[3], 1 -bit full adders. c 1, a[0], b[0], c_in); c 2, a[1], b[1], c 1); c 3, a[2], b[2], c 2); c_out, a[3], b[3], c 3); endmodule 2010 DSD 39

![Stimulus Block module stimulus reg 3 0 A B reg CIN wire 3 0 Stimulus Block module stimulus; reg [3: 0] A, B; reg C_IN; wire [3: 0]](https://slidetodoc.com/presentation_image/29a3ef527552ca6378d783e9bc38098b/image-40.jpg)

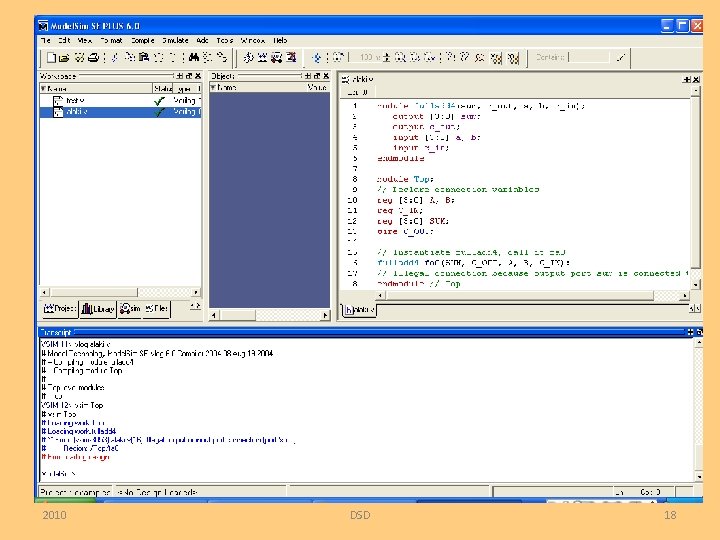

Stimulus Block module stimulus; reg [3: 0] A, B; reg C_IN; wire [3: 0] SUM; wire C_OUT; fulladd 4 FA 1_4(SUM, C_OUT, A, B, C_IN); initial $monitor($time, " A= %b, B=%b, C_IN= %b, --- C_OUT= %b, SUM= %bn“, A, B, C_IN, C_OUT, SUM); initial begin A = 4'd 0; B = 4'd 0; C_IN = 1'b 0; #5 A = 4'd 3; B = 4'd 4; #5 A = 4'd 2; B = 4'd 5; #5 A = 4'd 9; B = 4'd 9; #5 A = 4'd 10; B = 4'd 15; #5 A = 4'd 10; B = 4'd 5; C_IN = 1'b 1; endmodule 2010 DSD 40

Delay Models and Gate Level Delays 2010 DSD

Delay Models • Transport Delay Model – Path delay, Pin-to-pin delay, propagation delay • Inertial Delay Model – Input Inertial delay – Output Inertial delay 2010 DSD 42

Gate Delays in Verilog • Rise delay • Fall delay • Turn-off delay • Delay for value change to x 2010 DSD 43

Specifying Gate Delay // Delay of delay_time for all transitions and #(delay_time) a 1(out, i 1, i 2); // Rise and Fall Delay Specification. and #(rise_val, fall_val) a 2(out, i 1, i 2); // Rise, Fall, and Turn-off Delay Specification bufif 0 #(rise_val, fall_val, turnoff_val) b 1 (out, in, control); Examples: and #(5) a 1(out, i 1, i 2); //Delay of 5 for all transitions and #(4, 6) a 2(out, i 1, i 2); // Rise = 4, Fall = 6 bufif 0 #(3, 4, 5) b 1 (out, in, control); // Rise = 3, Fall = 4, Turn-off = 5 2010 DSD 44

Min/Typ/Max Delay values • Can be separately specified for each delay type // One delay // if +mindelays, delay= 4 // if +typdelays, delay= 5 // if +maxdelays, delay= 6 and #(4: 5: 6) a 1(out, i 1, i 2); // Two delays // if +mindelays, rise= 3, fall= 5, turn-off = min(3, 5) // if +typdelays, rise= 4, fall= 6, turn-off = min(4, 6) // if +maxdelays, rise= 5, fall= 7, turn-off = min(5, 7) and #(3: 4: 5, 5: 6: 7) a 2(out, i 1, i 2); // Three delays // if +mindelays, rise= 2 fall= 3 turn-off = 4 // if +typdelays, rise= 3 fall= 4 turn-off = 5 // if +maxdelays, rise= 4 fall= 5 turn-off = 6 bufif 0 #(2: 3: 4, 3: 4: 5, 4: 5: 6) a 3(out, in, ctrl); 45

2010 DSD 46

Delay Example module stimulus; reg A, B, C; wire OUT; D d 1( OUT, A, B, C); initial begin A= 1'b 0; B= 1'b 0; C= 1'b 0; #10 A= 1'b 1; B= 1'b 1; C= 1'b 1; #10 A= 1'b 1; B= 1'b 0; C= 1'b 0; #20 $finish; endmodule DSD 47

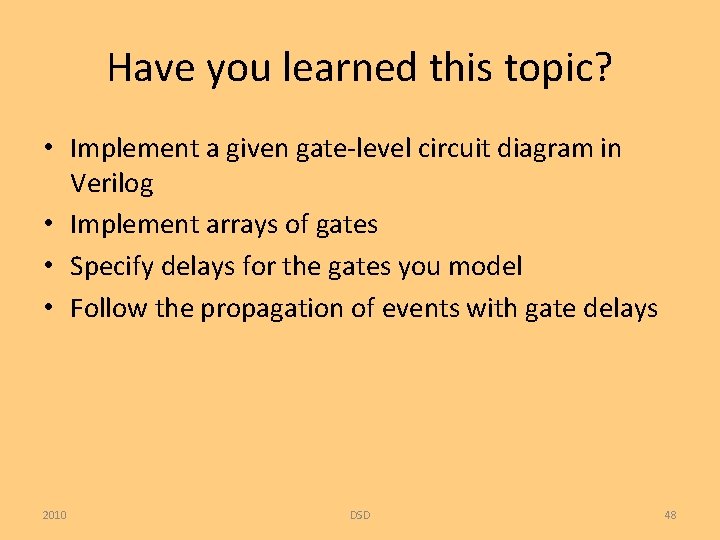

Have you learned this topic? • Implement a given gate-level circuit diagram in Verilog • Implement arrays of gates • Specify delays for the gates you model • Follow the propagation of events with gate delays 2010 DSD 48