Digital System Design Verilog HDL Behavioral Modeling Maziar

Digital System Design Verilog® HDL Behavioral Modeling Maziar Goudarzi

Objectives of this Topic • • • initial and always blocks The concept of multiple flows of control Practice simple examples Procedural assignment vs. Continuous assignment Conditional statements – if, casex, casez • Loop statements – while, for, repeat, forever 2010 DSD 2

Introduction • The move toward higher abstractions – Gate-level modeling • Netlist of gates – Dataflow modeling • Boolean function assigned to a net – Now, behavioral modeling • A sequential algorithm (quite similar to software) that determines the value(s) of variable(s) 2010 DSD 3

Structured Procedures • Two basic structured procedure statements always initial – All behavioral statements appear only inside these blocks – Each always or initial block has a separate activity flow (multithreading, concurrency) – Start from simulation time 0 – No nesting 2010 DSD 4

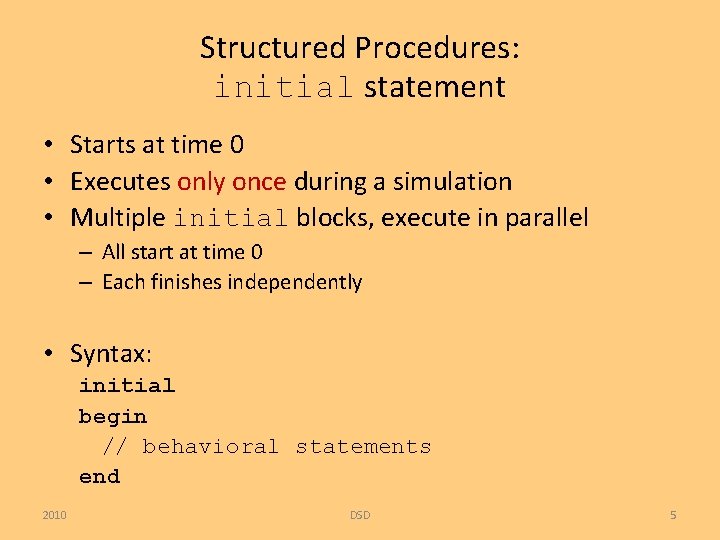

Structured Procedures: initial statement • Starts at time 0 • Executes only once during a simulation • Multiple initial blocks, execute in parallel – All start at time 0 – Each finishes independently • Syntax: initial begin // behavioral statements end 2010 DSD 5

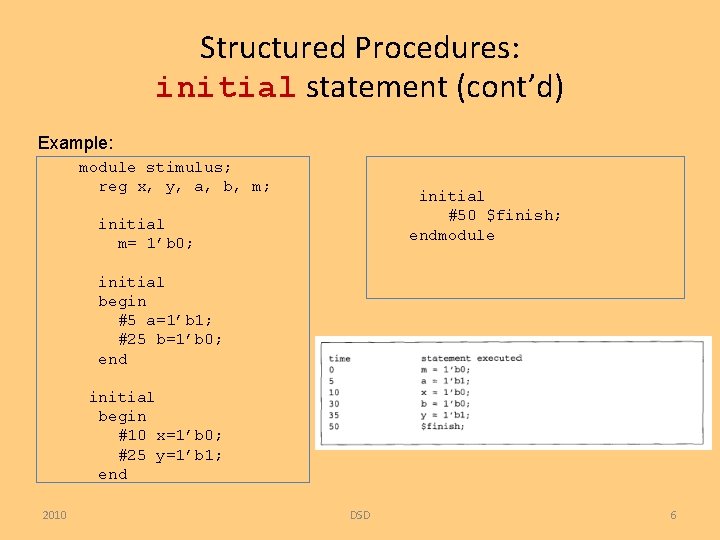

Structured Procedures: initial statement (cont’d) Example: module stimulus; reg x, y, a, b, m; initial #50 $finish; endmodule initial m= 1’b 0; initial begin #5 a=1’b 1; #25 b=1’b 0; end initial begin #10 x=1’b 0; #25 y=1’b 1; end 2010 DSD 6

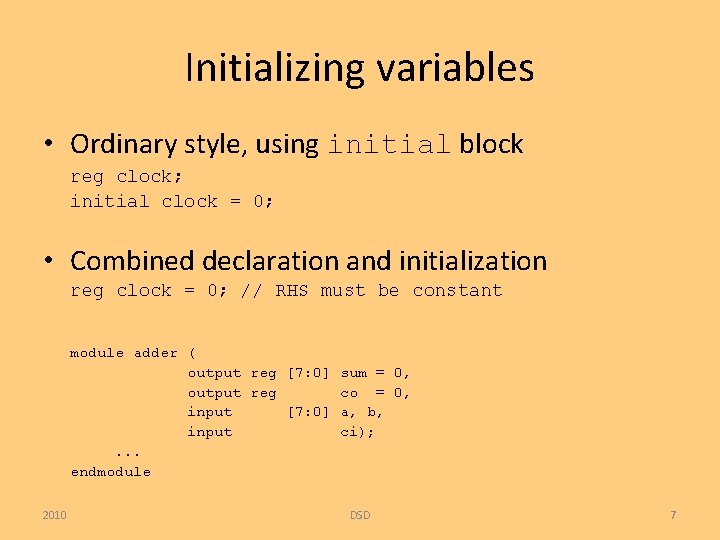

Initializing variables • Ordinary style, using initial block reg clock; initial clock = 0; • Combined declaration and initialization reg clock = 0; // RHS must be constant module adder ( output reg [7: 0] sum = 0, output reg co = 0, input [7: 0] a, b, input ci); . . . endmodule 2010 DSD 7

Structured Procedures: always statement • Start at time 0 • Execute the statements in a looping fashion • Example 2010 DSD 8

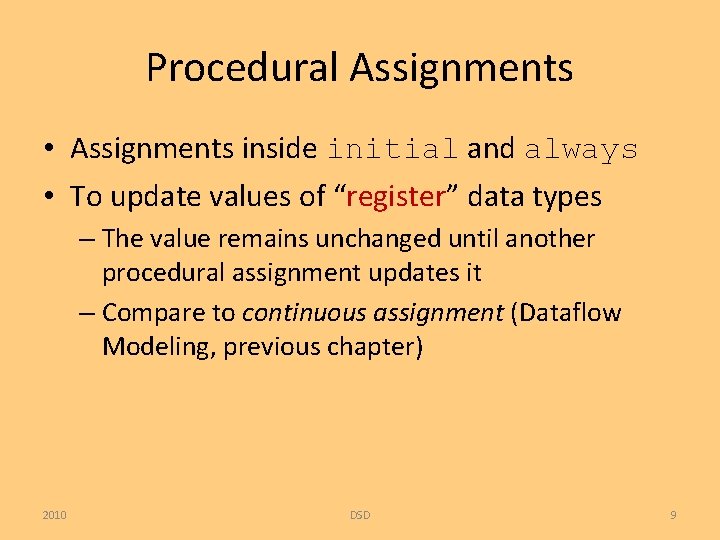

Procedural Assignments • Assignments inside initial and always • To update values of “register” data types – The value remains unchanged until another procedural assignment updates it – Compare to continuous assignment (Dataflow Modeling, previous chapter) 2010 DSD 9

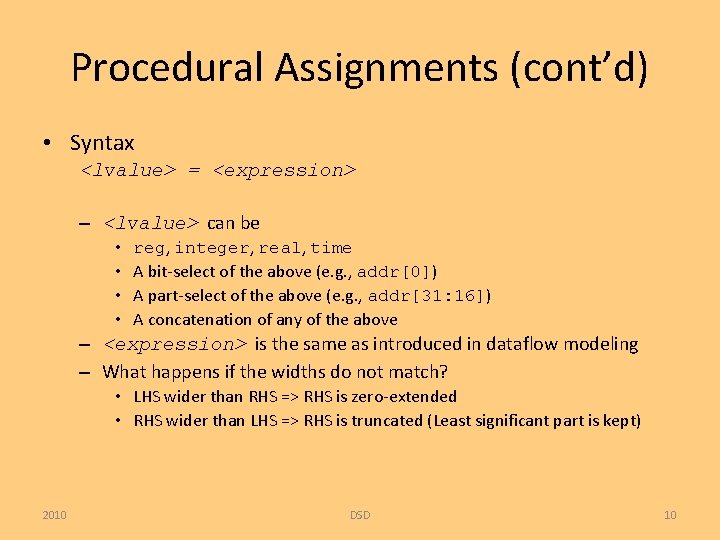

Procedural Assignments (cont’d) • Syntax <lvalue> = <expression> – <lvalue> can be • • reg, integer, real, time A bit-select of the above (e. g. , addr[0]) A part-select of the above (e. g. , addr[31: 16]) A concatenation of any of the above – <expression> is the same as introduced in dataflow modeling – What happens if the widths do not match? • LHS wider than RHS => RHS is zero-extended • RHS wider than LHS => RHS is truncated (Least significant part is kept) 2010 DSD 10

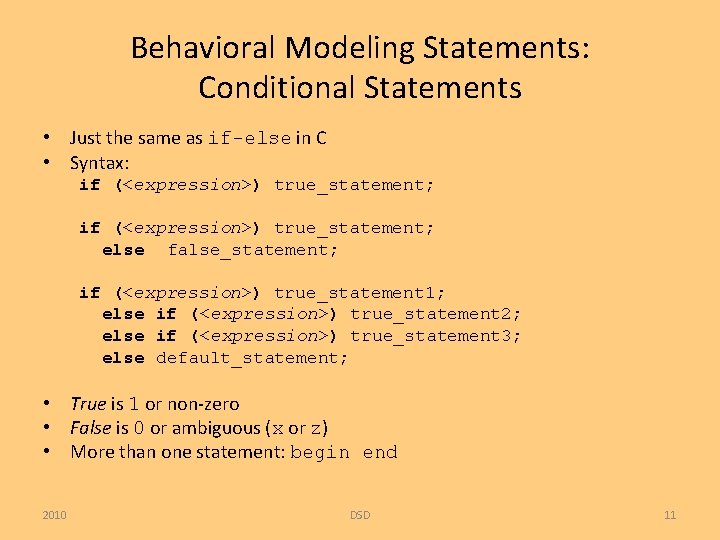

Behavioral Modeling Statements: Conditional Statements • Just the same as if-else in C • Syntax: if (<expression>) true_statement; else false_statement; if (<expression>) true_statement 1; else if (<expression>) true_statement 2; else if (<expression>) true_statement 3; else default_statement; • True is 1 or non-zero • False is 0 or ambiguous (x or z) • More than one statement: begin end 2010 DSD 11

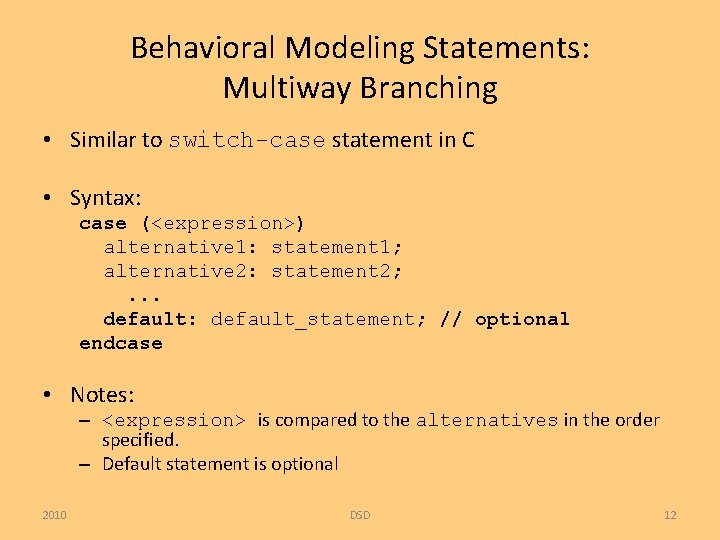

Behavioral Modeling Statements: Multiway Branching • Similar to switch-case statement in C • Syntax: case (<expression>) alternative 1: statement 1; alternative 2: statement 2; . . . default: default_statement; // optional endcase • Notes: – <expression> is compared to the alternatives in the order specified. – Default statement is optional 2010 DSD 12

Multiway Branching (cont’d) • Examples: To be provided in the class • Now, you write a 4 -to-1 multiplexer. 2010 DSD 13

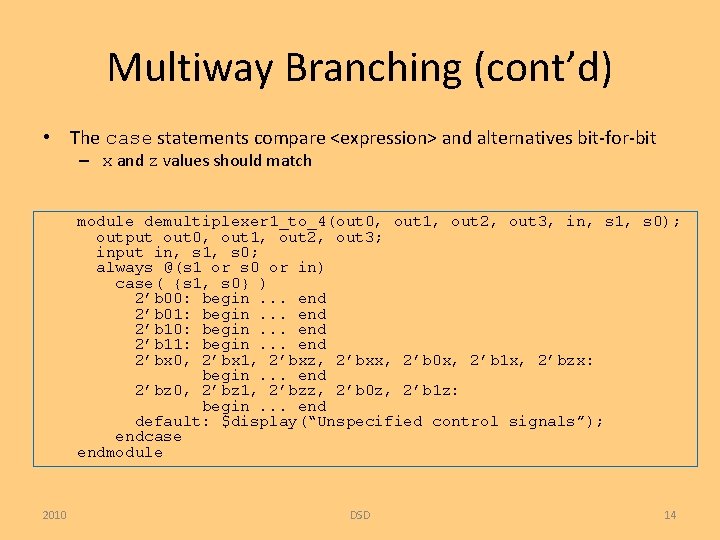

Multiway Branching (cont’d) • The case statements compare <expression> and alternatives bit-for-bit – x and z values should match module demultiplexer 1_to_4(out 0, out 1, out 2, out 3, in, s 1, s 0); output out 0, out 1, out 2, out 3; input in, s 1, s 0; always @(s 1 or s 0 or in) case( {s 1, s 0} ) 2’b 00: begin. . . end 2’b 01: begin. . . end 2’b 10: begin. . . end 2’b 11: begin. . . end 2’bx 0, 2’bx 1, 2’bxz, 2’bxx, 2’b 0 x, 2’b 1 x, 2’bzx: begin. . . end 2’bz 0, 2’bz 1, 2’bzz, 2’b 0 z, 2’b 1 z: begin. . . end default: $display(“Unspecified control signals”); endcase endmodule 2010 DSD 14

Multiway Branching (cont’d) • casex and casez keywords – casez treats all z values as “don’t care” – casex treats all x and z values as “don’t care” • Example: To be provided in the class 2010 DSD 15

Behavioral Modeling Statements: Loops • Loops in Verilog – while, for, repeat, forever • The while loop syntax: while (<expression>) statement; 2010 DSD 16

while Loop Example To be provided in the class 2010 DSD 17

Loops (cont’d) • The for loop – Similar to C – Syntax: for( init_expr; cond_expr; change_expr) statement; – Example: Provided in the class 2010 DSD 18

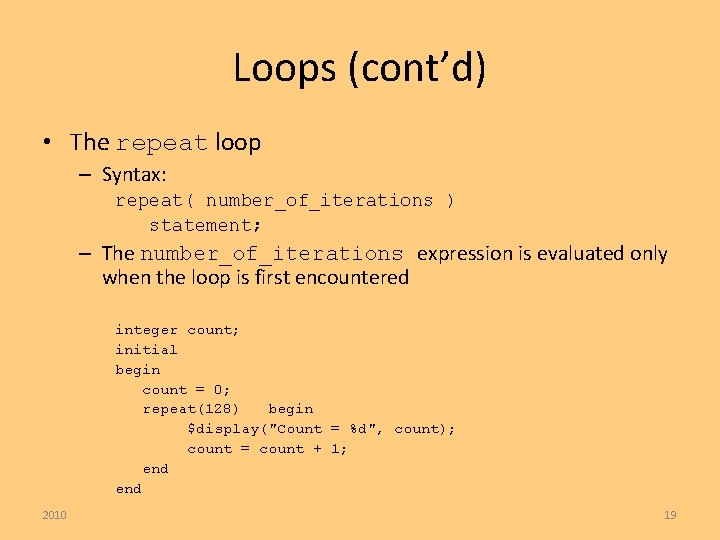

Loops (cont’d) • The repeat loop – Syntax: repeat( number_of_iterations ) statement; – The number_of_iterations expression is evaluated only when the loop is first encountered integer count; initial begin count = 0; repeat(128) begin $display("Count = %d", count); count = count + 1; end 2010 19

Loops (cont’d) • The forever loop – Syntax: forever statement; – Equivalent to while(1) 2010 DSD 20

Have your learned this topic • What is behavioral modeling • What are the Verilog constructs for behavioral modeling • Statements used in behavioral modeling – Conditional – Multiway branching – Loops 2010 DSD 21

Objectives of This Topic • Internal operations of Event-Driven simulators • Behavioral Modeling (cont’d) – Blocking vs. non-blocking assignments – Race condition – Timing control by delays, events, and level – Other features 2010 DSD 22

Two Types of Simulators • Oblivious Simulators – Evaluate outputs repetitively at predefined time intervals • Event Driven Simulators – Evaluate outputs only when an event occurs on the inputs 2010 DSD 23

Internal Operations of Event-Driven Simulators • Event • Transaction • The simulation cycle 2010 DSD 24

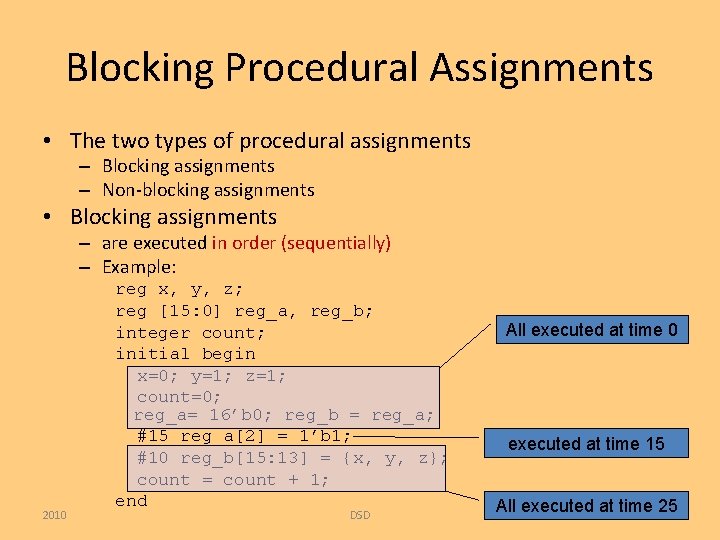

Blocking Procedural Assignments • The two types of procedural assignments – Blocking assignments – Non-blocking assignments • Blocking assignments – are executed in order (sequentially) – Example: 2010 reg x, y, z; reg [15: 0] reg_a, reg_b; integer count; initial begin x=0; y=1; z=1; count=0; reg_a= 16’b 0; reg_b = reg_a; #15 reg_a[2] = 1’b 1; #10 reg_b[15: 13] = {x, y, z}; count = count + 1; end DSD All executed at time 0 executed at time 15 All executed at time 25 25

Non-Blocking Procedural Assignments • Non-blocking assignments – Processing of the next statements is not blocked for this one – Transactions created sequentially (in order), but executed after all blocking assignments in the corresponding simulation cycle – Syntax: <lvalue> <= <expression> – Example: 2010 reg x, y, z; reg [15: 0] reg_a, reg_b; All executed at time 0 integer count; initial begin x=0; y=1; z=1; count=0; reg_a= 16’b 0; reg_b = reg_a; reg_a[2] <= #15 1’b 1; Scheduled to run at time 15 reg_b[15: 13] <= #10 {x, y, z}; count <= count + 1; Scheduled to run at time 10 end

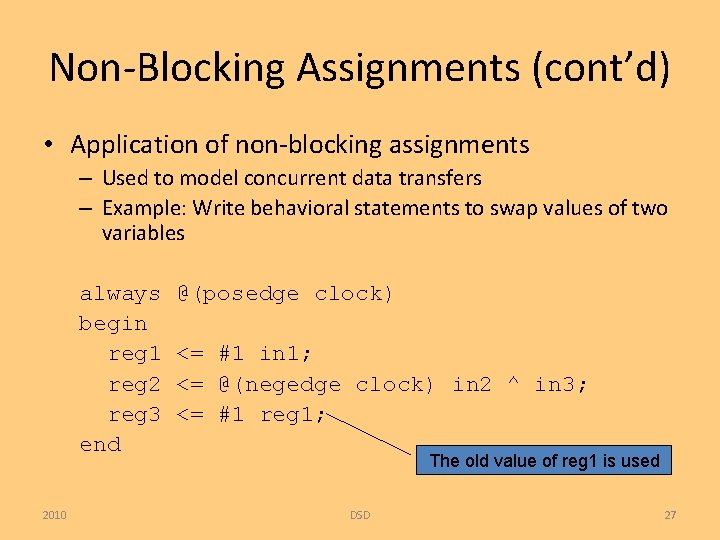

Non-Blocking Assignments (cont’d) • Application of non-blocking assignments – Used to model concurrent data transfers – Example: Write behavioral statements to swap values of two variables always begin reg 1 reg 2 reg 3 end 2010 @(posedge clock) <= #1 in 1; <= @(negedge clock) in 2 ^ in 3; <= #1 reg 1; The old value of reg 1 is used DSD 27

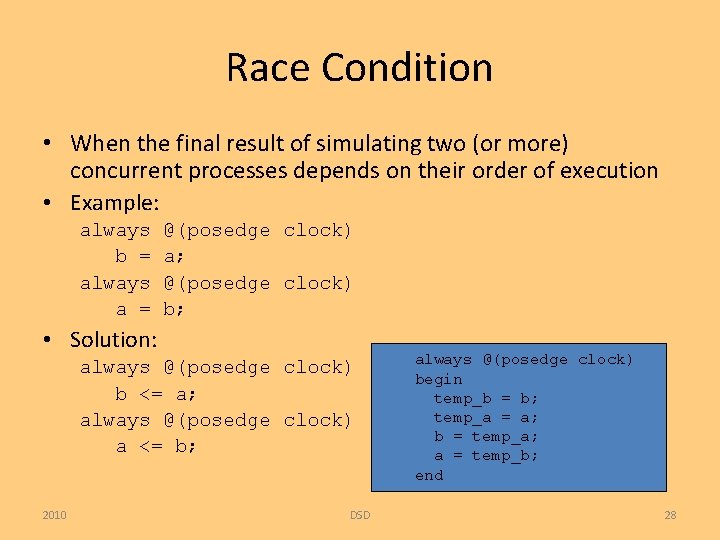

Race Condition • When the final result of simulating two (or more) concurrent processes depends on their order of execution • Example: always b = always a = @(posedge clock) a; @(posedge clock) b; • Solution: always @(posedge clock) b <= a; always @(posedge clock) a <= b; 2010 DSD always @(posedge clock) begin temp_b = b; temp_a = a; b = temp_a; a = temp_b; end 28

Race Condition (cont’d) • Recommendation – Concurrent data transfers => race condition – Use non-blocking assignments for concurrent data transfers – Example: pipeline modelling – Disadvantage: • Lower simulation performance • Higher memory usage in the simulator 2010 DSD 29

Timing Controls in Behavioral Modeling

Introduction • No timing controls No advance in simulation time • Three methods of timing control – delay-based – event-based – level-sensitive 2010 DSD 31

Delay-based Timing Controls • Delay Duration between encountering and executing a statement • Delay symbol: # • Delay specification syntax: #5 #(1: 2: 3) 2010 DSD 32

Delay-based Timing Controls (cont’d) • Types of delay-based timing controls 1. Regular delay control 2. Intra-assignment delay control 3. Zero-delay control 2010 DSD 33

Regular Delay Control • Symbol: non-zero delay before a procedural assignment 2010 DSD 34

Intra-assignment Delay Control • Symbol: non-zero delay to the right of the assignment operator • Operation sequence: 1. Compute the RHS expression at current time. 2. Defer the assignment of the above computed value to the LHS by the specified delay. 2010 DSD 35

Zero-Delay Control • Symbol: #0 • Different initial/always blocks in the same simulation time – Execution order non-deterministic • #0 ensures execution after all other statements – Eliminates race conditions (only in simulation) • Multiple zero-delay statements – Non-deterministic execution order 2010 DSD 36

Event-based Timing Control • Event – Change in the value of a register or net – Used to trigger execution of a statement or block (reactive behavior/reactivity) • Types of Event-based timing control 1. Regular event control 2. Named event control 3. Event OR control 2010 DSD 37

Regular Event Control • Symbol: @(<event>) • Events to specify: – posedge sig • Change of sig from any value to 1 or from 0 to any value – negedge sig • Change of sig from any value to 0 or from 1 to any value – sig • Any change in sig value 2010 DSD 38

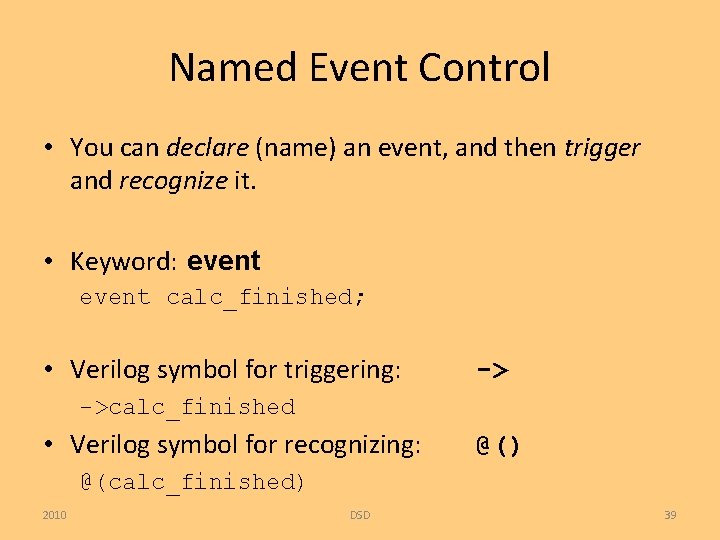

Named Event Control • You can declare (name) an event, and then trigger and recognize it. • Keyword: event calc_finished; • Verilog symbol for triggering: -> ->calc_finished • Verilog symbol for recognizing: @() @(calc_finished) 2010 DSD 39

Event OR control • Used when need to trigger a block upon occurrence of any of a set of events. • The list of the events: sensitivity list • Keyword: or 2010 DSD 40

Event OR control • Simpler syntax – always @( reset, clock, d) – @* and @(*) 2010 DSD 41

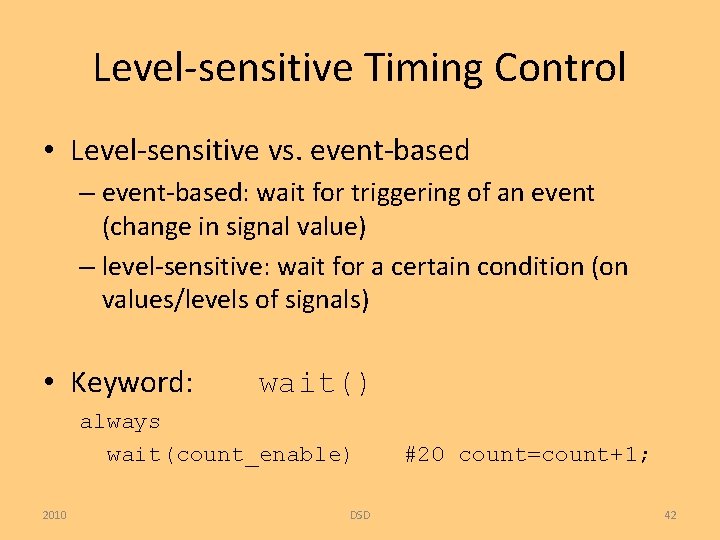

Level-sensitive Timing Control • Level-sensitive vs. event-based – event-based: wait for triggering of an event (change in signal value) – level-sensitive: wait for a certain condition (on values/levels of signals) • Keyword: wait() always wait(count_enable) 2010 DSD #20 count=count+1; 42

Have you learned this topic? • Race conditions – Blocking vs. non-blocking assignments – Zero delay control • Timing control in behavioral statements – Required to advance the simulation time – Different types • Delay-based • Event-based • Level-sensitive 2010 DSD 43

Objectives of This Topic • Some more constructs on Behavioral Modeling – Parallel blocks – Nested blocks – disable keyword • Verilog® Scheduling Semantics 2011 DSD 44

Blocks, Sequential blocks • Used to group multiple statements • Sequential blocks – Keywords: begin end – Statements are processed in order. – A statement is executed only after its preceding one completes. • Exceptions: non-blocking assignments and intra-assignment delays – A delay or event is relative to the simulation time when the previous statement completed execution 2011 DSD 45

Parallel Blocks • Parallel Blocks – Keywords: fork, join – Statements in the blocks are executed concurrently – Timing controls specify the order of execution of the statements – All delays are relative to the time the block was entered • The written order of statements is not important • The join is done when all the parallel statements are finished 2011 DSD 46

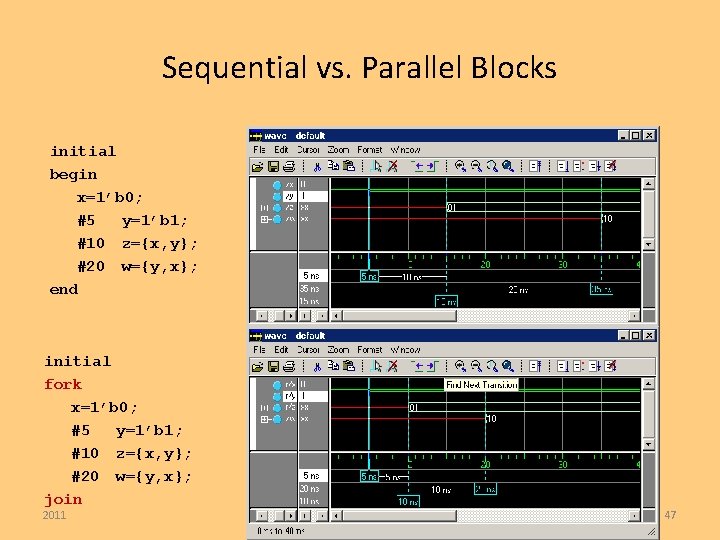

Sequential vs. Parallel Blocks initial begin x=1’b 0; #5 y=1’b 1; #10 z={x, y}; #20 w={y, x}; end initial fork x=1’b 0; #5 y=1’b 1; #10 z={x, y}; #20 w={y, x}; join 2011 DSD 47

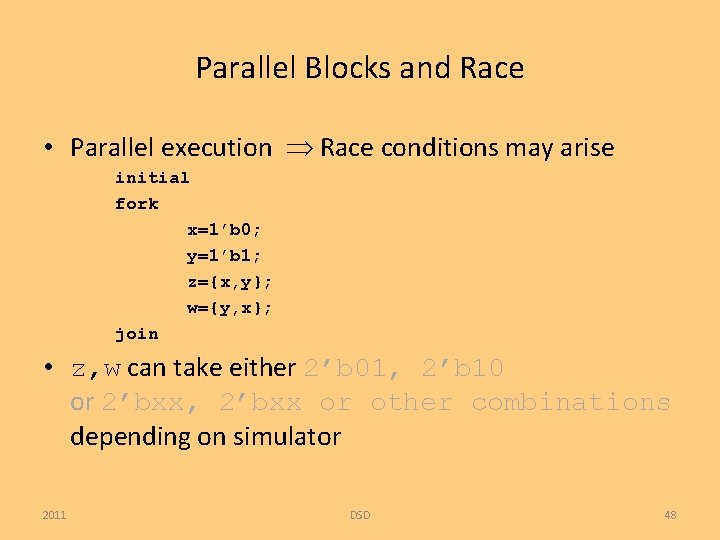

Parallel Blocks and Race • Parallel execution Race conditions may arise initial fork x=1’b 0; y=1’b 1; z={x, y}; w={y, x}; join • z, w can take either 2’b 01, 2’b 10 or 2’bxx, 2’bxx or other combinations depending on simulator 2011 DSD 48

Special Features of Blocks • Contents – Nested blocks – Named blocks – Disabling named blocks 2011 DSD 49

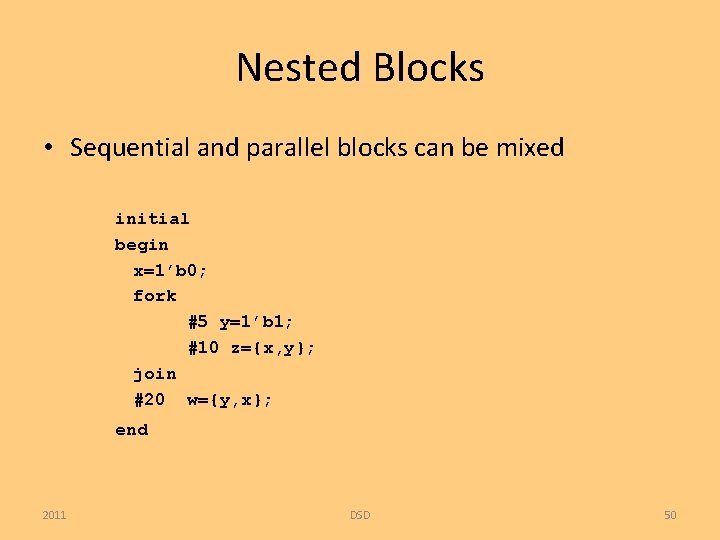

Nested Blocks • Sequential and parallel blocks can be mixed initial begin x=1’b 0; fork #5 y=1’b 1; #10 z={x, y}; join #20 w={y, x}; end 2011 DSD 50

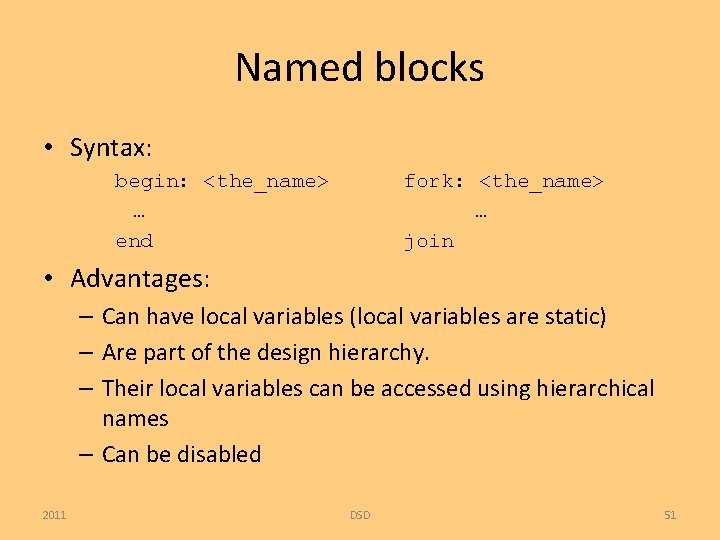

Named blocks • Syntax: begin: <the_name> … end fork: <the_name> … join • Advantages: – Can have local variables (local variables are static) – Are part of the design hierarchy. – Their local variables can be accessed using hierarchical names – Can be disabled 2011 DSD 51

Disabling Named Blocks • Keyword: disable • Action: – Similar to break in C/C++, but can disable any named block not just the inner-most block. 2011 DSD 52

Behavioral Modeling Some Examples

4 -to-1 Multiplexer 2011 DSD 54

4 -bit Counter 2011 DSD 55

Have you learned this topic? • Sequential and Parallel Blocks • Special Features of Blocks – Nested blocks – Named blocks – Disabling named blocks 2011 DSD 56

Objectives of This Topic • Use Tasks and Functions for better structured code 2010 DSD 57

Introduction • Procedures/Subroutines/Functions in SW programming languages – The same functionality, in different places • Verilog equivalence: – Tasks and Functions – Used in behavioral modeling – Part of design hierarchy Hierarchical name 2010 DSD 58

Functions • Keyword: function, endfunction • Can be used if the procedure – does not have any timing control constructs – returns exactly one single value – has at least one input argument 2010 DSD 59

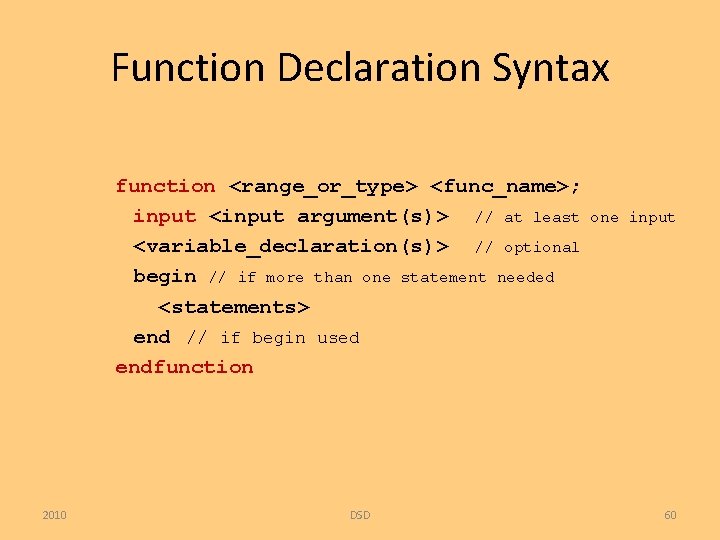

Function Declaration Syntax function <range_or_type> <func_name>; input <input argument(s)> // at least <variable_declaration(s)> // optional begin // if more than one statement needed <statements> end // if begin used endfunction 2010 DSD one input 60

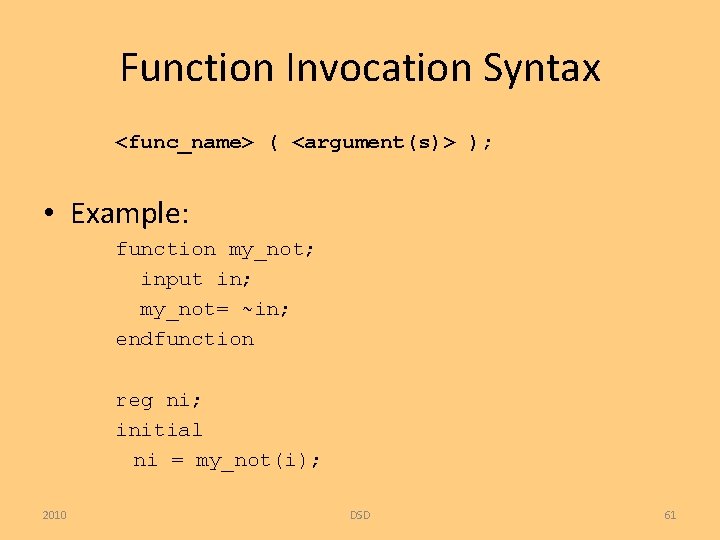

Function Invocation Syntax <func_name> ( <argument(s)> ); • Example: function my_not; input in; my_not= ~in; endfunction reg ni; initial ni = my_not(i); 2010 DSD 61

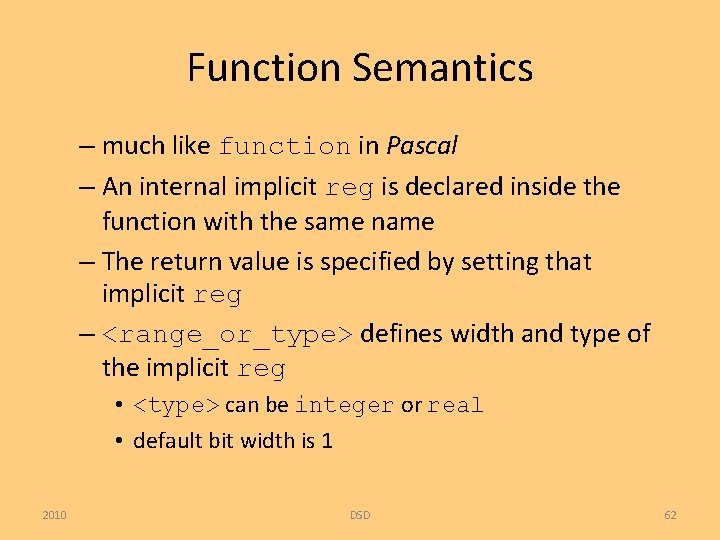

Function Semantics – much like function in Pascal – An internal implicit reg is declared inside the function with the same name – The return value is specified by setting that implicit reg – <range_or_type> defines width and type of the implicit reg • <type> can be integer or real • default bit width is 1 2010 DSD 62

Two Function Examples: Parity Generator, and Controllable Shifter 2010 DSD 63

Tasks • Keywords: task, endtask • Must be used if the procedure has – any timing control constructs – zero or more than one output arguments – no input arguments 2010 DSD 64

Task Declaration Syntax task <task_name>; <I/O declarations> // optional <variable and event declarations> begin // if more than one statement needed <statement(s)> end // if begin used! endtask 2010 DSD 65

Task Invocation Syntax <task_name>; <task_name> (<arguments>); – input and inout arguments are passed into the task – output and inout arguments are passed back to the invoking statement when task is completed 2010 DSD 66

I/O declaration in modules vs. tasks – Both use keywords: input, output, inout – In modules, represent ports • connect to external signals – In tasks, represent arguments • pass values to and from the task 2010 DSD 67

Task Examples • Use of input and output arguments • Use of module local variables 2010 DSD 68

Automatic Tasks and Functions • Used for re-entrant code – Task called from multiple locations – Recursive function calls • Keyword – automatic • Example function automatic integer factorial; task automatic bitwise_xor; 2010 DSD 69

Automatic Function Example Factorial 2010 DSD 70

Tasks and Functions Differences between Tasks and Functions

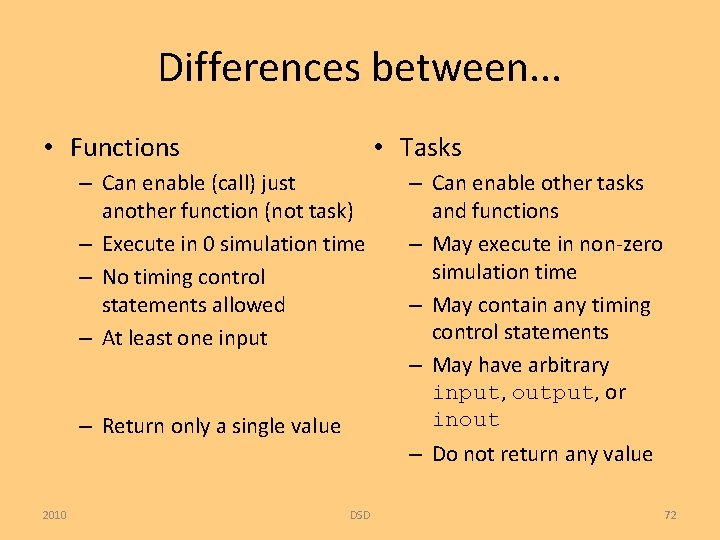

Differences between. . . • Functions • Tasks – Can enable (call) just another function (not task) – Execute in 0 simulation time – No timing control statements allowed – At least one input – Return only a single value 2010 DSD – Can enable other tasks and functions – May execute in non-zero simulation time – May contain any timing control statements – May have arbitrary input, output, or inout – Do not return any value 72

Have you learned this topic? • How to define tasks and functions • Where to use each of them – The same purpose as subroutines in SW – Provide more readability, easier code management – Are part of design hierarchy – Tasks are more general than functions • Can represent almost any common Verilog code – Functions can only model purely combinational calculations 2010 DSD 73

- Slides: 73