Digital och Datorteknik EDA 451 20092010 EDA 451

- Slides: 35

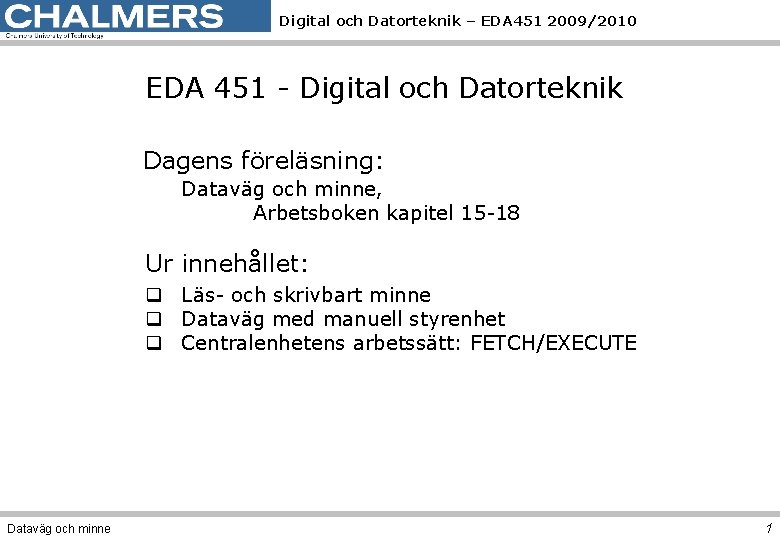

Digital och Datorteknik – EDA 451 2009/2010 EDA 451 - Digital och Datorteknik Dagens föreläsning: Dataväg och minne, Arbetsboken kapitel 15 -18 Ur innehållet: q Läs- och skrivbart minne q Dataväg med manuell styrenhet q Centralenhetens arbetssätt: FETCH/EXECUTE Dataväg och minne 1

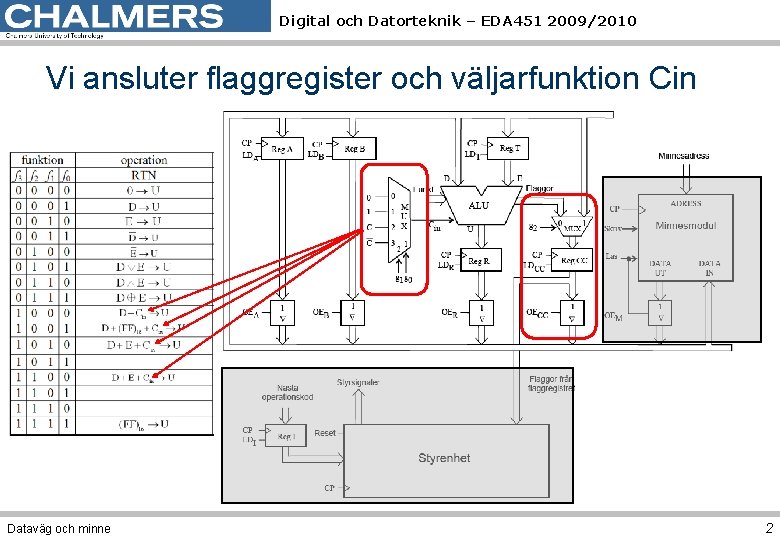

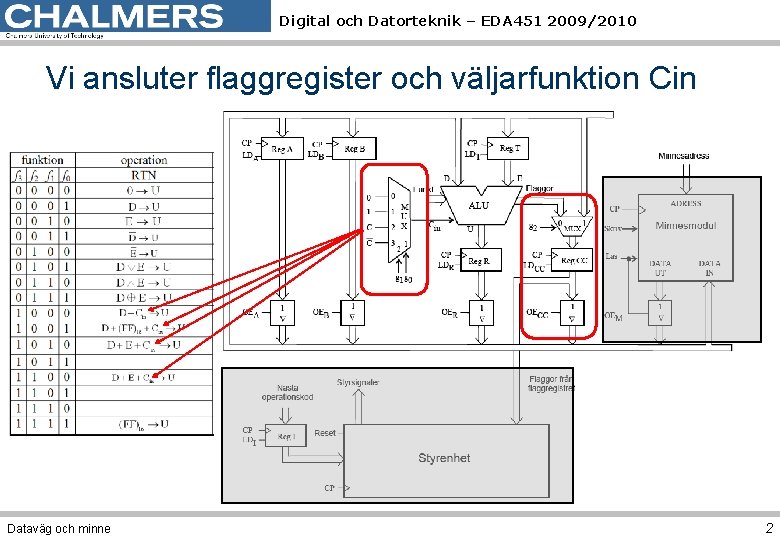

Digital och Datorteknik – EDA 451 2009/2010 Vi ansluter flaggregister och väljarfunktion Cin Dataväg och minne 2

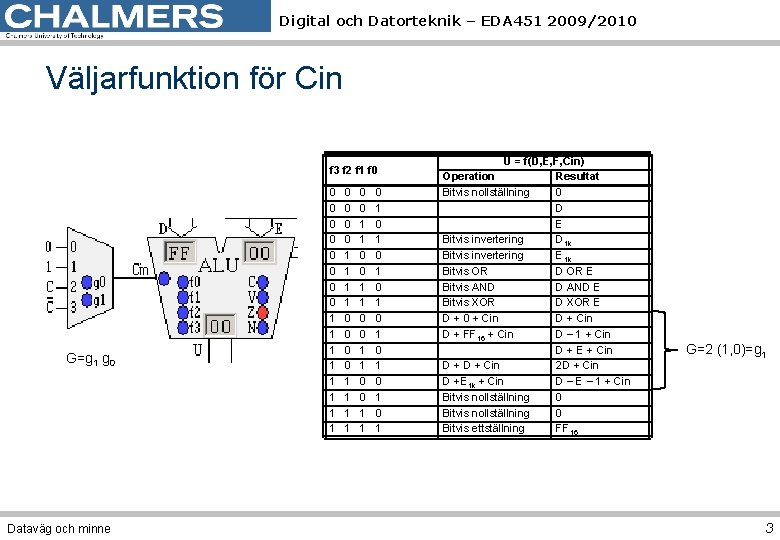

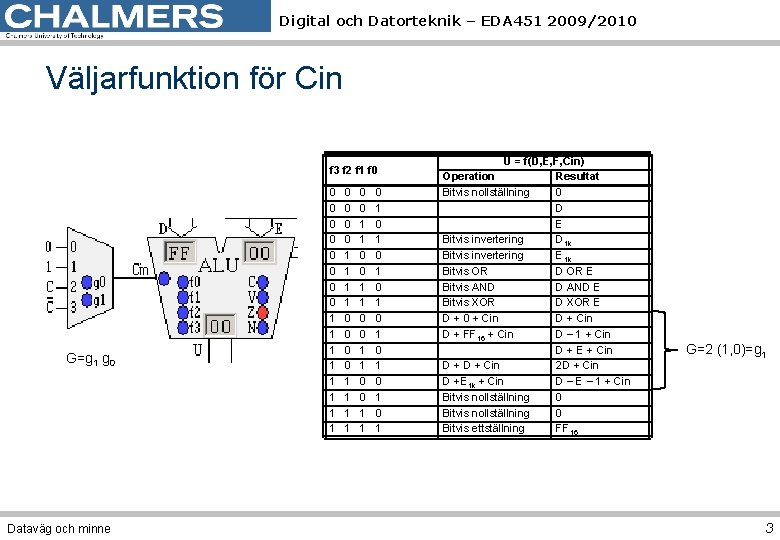

Digital och Datorteknik – EDA 451 2009/2010 Väljarfunktion för Cin f 3 f 2 f 1 f 0 G=g 1 g 0 Dataväg och minne 0 0 0 0 1 1 1 1 0 0 1 1 0 1 0 1 U = f(D, E, F, Cin) Operation Resultat Bitvis nollställning 0 D E Bitvis invertering D 1 k Bitvis invertering E 1 k Bitvis OR D OR E Bitvis AND D AND E Bitvis XOR D XOR E D + 0 + Cin D + FF 16 + Cin D 1 + Cin D + E + Cin D + Cin 2 D + Cin D +E 1 k + Cin D E 1 + Cin Bitvis nollställning 0 Bitvis ettställning FF 16 G=2 (1, 0)=g 1 3

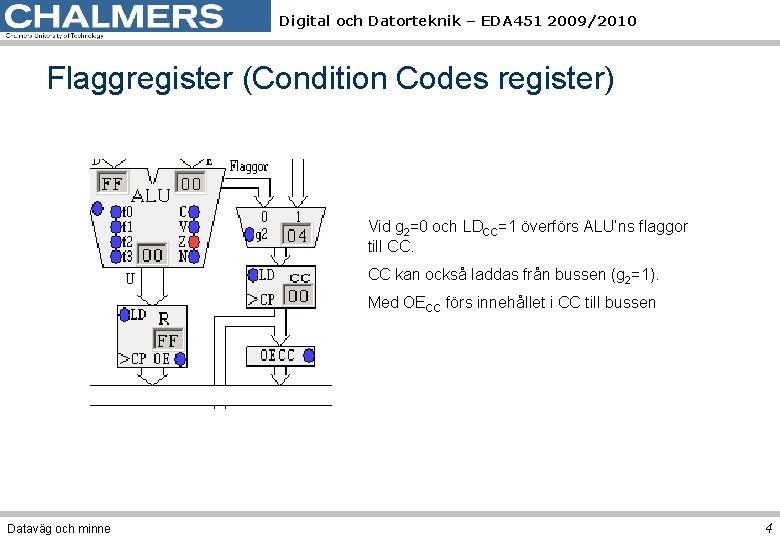

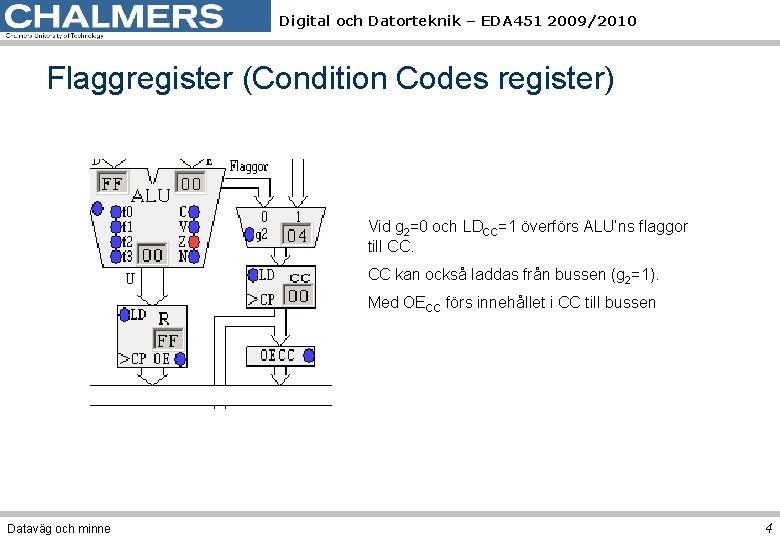

Digital och Datorteknik – EDA 451 2009/2010 Flaggregister (Condition Codes register) Vid g 2=0 och LDCC=1 överförs ALU’ns flaggor till CC. CC kan också laddas från bussen (g 2=1). Med OECC förs innehållet i CC till bussen Dataväg och minne 4

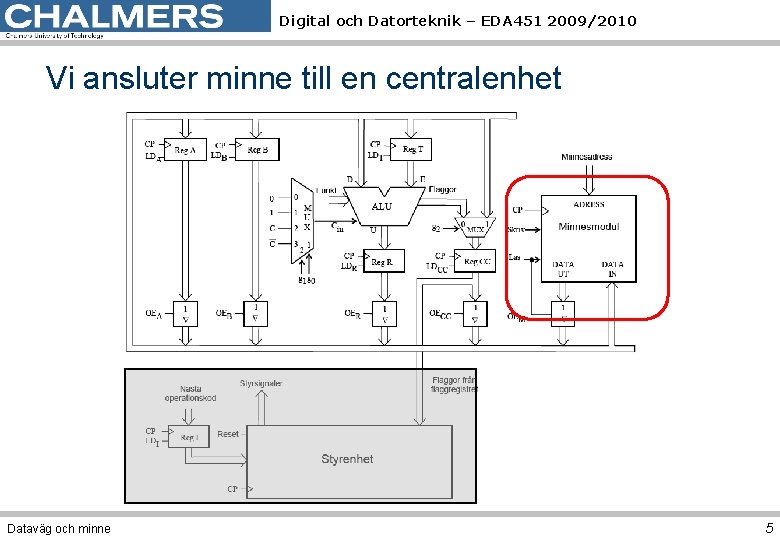

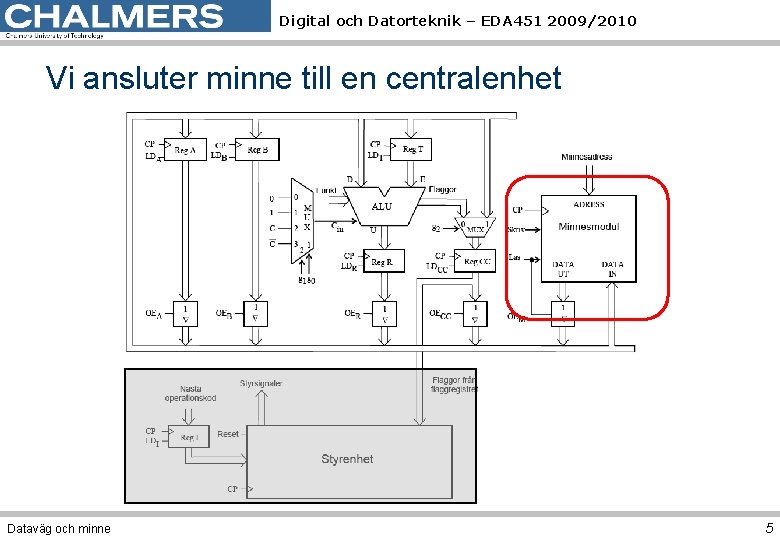

Digital och Datorteknik – EDA 451 2009/2010 Vi ansluter minne till en centralenhet Dataväg och minne 5

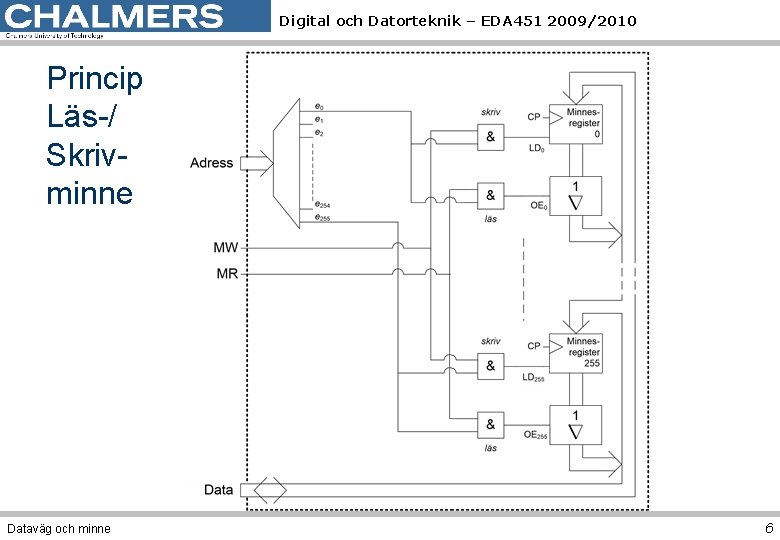

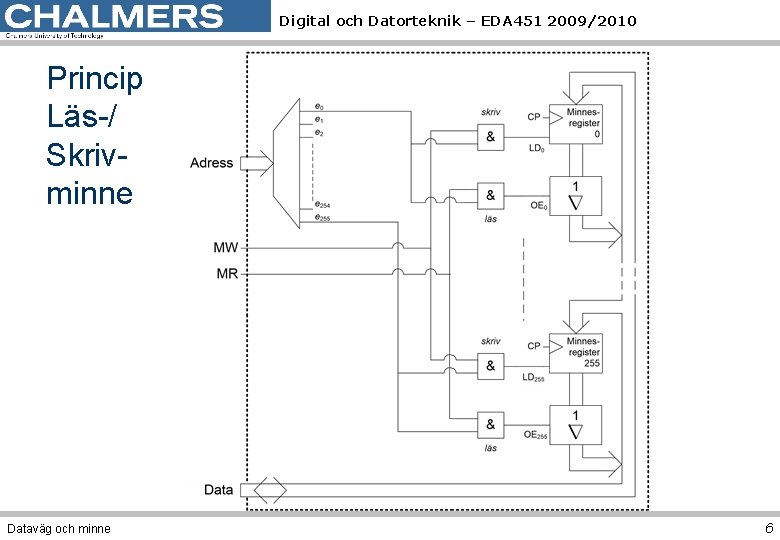

Digital och Datorteknik – EDA 451 2009/2010 Princip Läs-/ Skrivminne Dataväg och minne 6

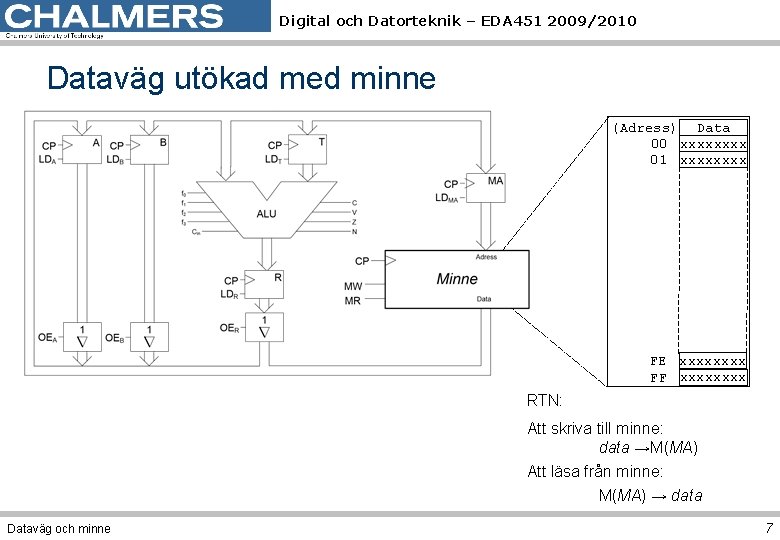

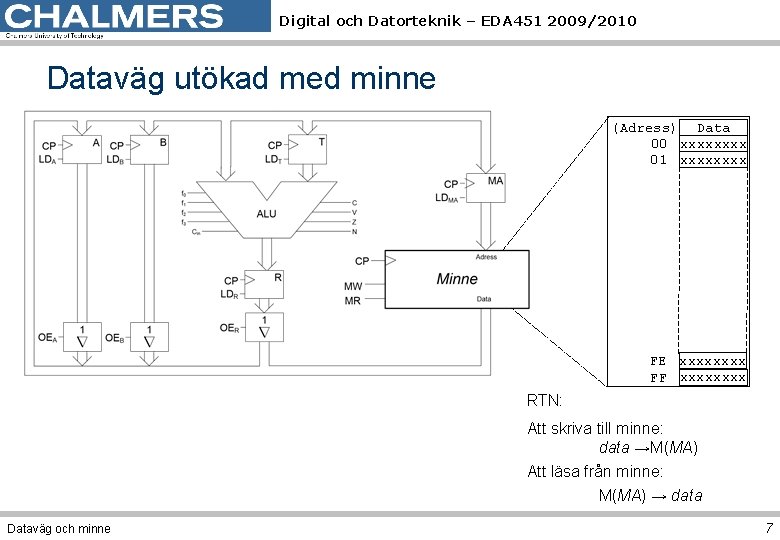

Digital och Datorteknik – EDA 451 2009/2010 Dataväg utökad med minne (Adress) Data 1600 xxxx 01 xxxx FE xxxx FF xxxx RTN: Att skriva till minne: data →M(MA) Att läsa från minne: M(MA) → data Dataväg och minne 7

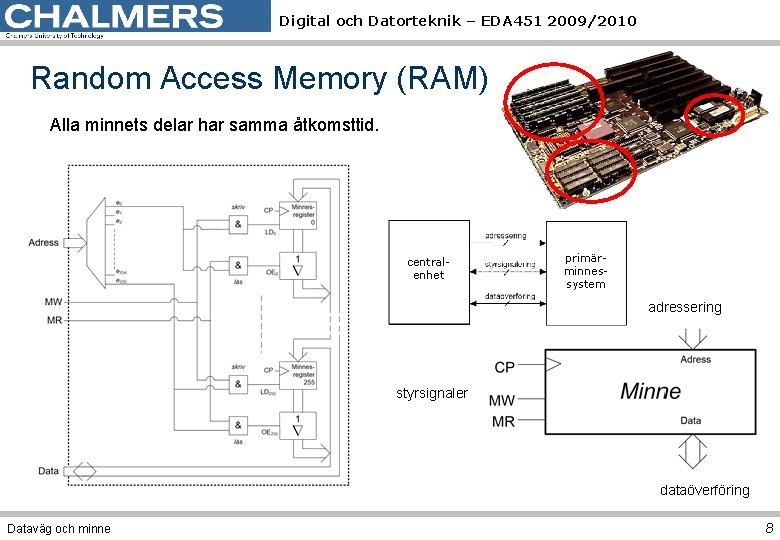

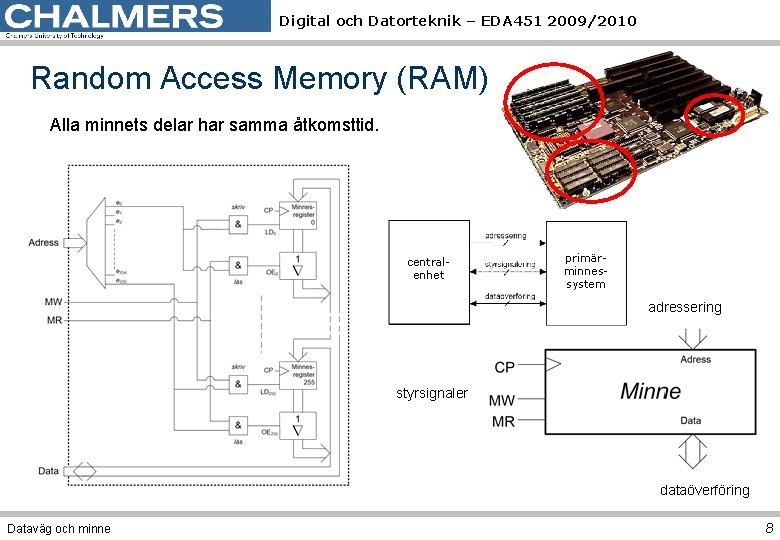

Digital och Datorteknik – EDA 451 2009/2010 Random Access Memory (RAM) Alla minnets delar har samma åtkomsttid. centralenhet primärminnessystem adressering styrsignaler dataöverföring Dataväg och minne 8

Digital och Datorteknik – EDA 451 2009/2010 RAM - Minnestyper Volatile (”Flyktigt”) innehållet försvinner vid spänningsbortfall, vid spänningstillslag är innehållet oftast slumpmässigt bestämt. Kallas ofta “RAM”. n RWM (Read Write Memory) NON Volatile (”Icke flyktigt”) behåller sitt innehåll även efter spänningsbortfall n ROM (Read Only Memory) – programmeras vid tillverkningen, innehållet kan därefter inte ändras n PROM (Programmable ROM) – minnestypen kan programmeras (kräver speciell utrustning) en gång n EPROM (Erasable PROM) – minnestypen kan programmeras och raderas med speciell utrustning n FLASH – minnestypen kan programmeras/raderas utan speciell typ av utrustning Dataväg och minne 9

Digital och Datorteknik – EDA 451 2009/2010 Snabb tillbakablick n n Skriv/läs-minnen, kallas ibland ”dataminne” – Williamstub – Kärnminnen – Halvledarminnen, SRAM/DRAM Läs-minnen, kallas ibland”Programminne” – Halvledarminne, ROM – Halvledarminne, EPROM – Halvledarminne, FLASH Dataväg och minne 10

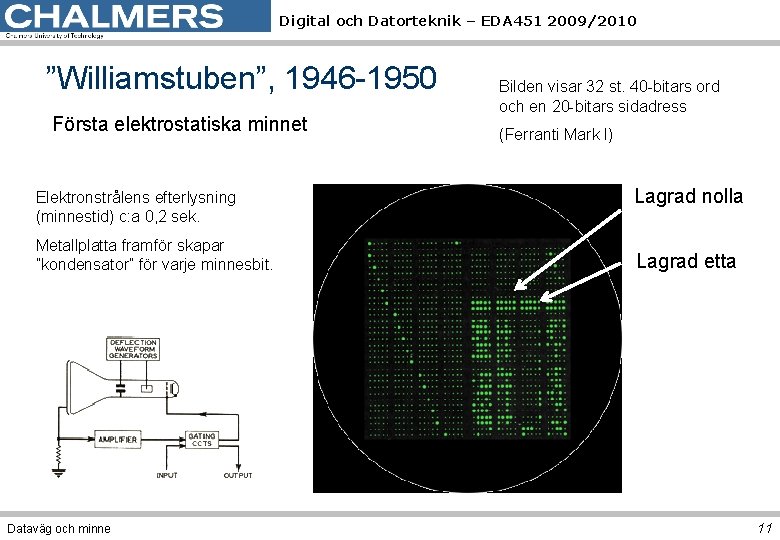

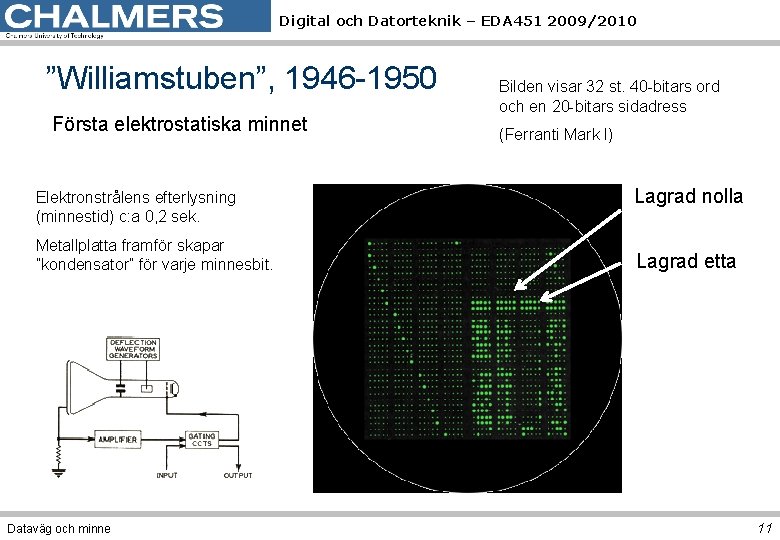

Digital och Datorteknik – EDA 451 2009/2010 ”Williamstuben”, 1946 -1950 Första elektrostatiska minnet Elektronstrålens efterlysning (minnestid) c: a 0, 2 sek. Metallplatta framför skapar ”kondensator” för varje minnesbit. Dataväg och minne Bilden visar 32 st. 40 -bitars ord och en 20 -bitars sidadress (Ferranti Mark I) Lagrad nolla Lagrad etta 11

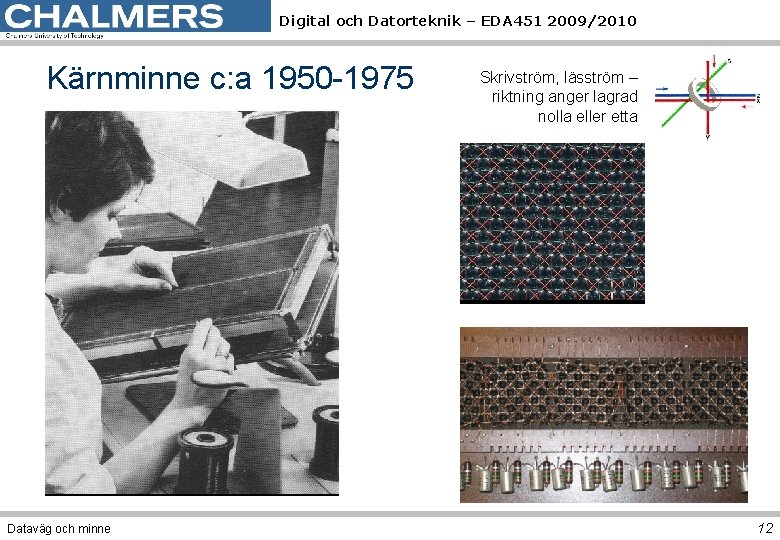

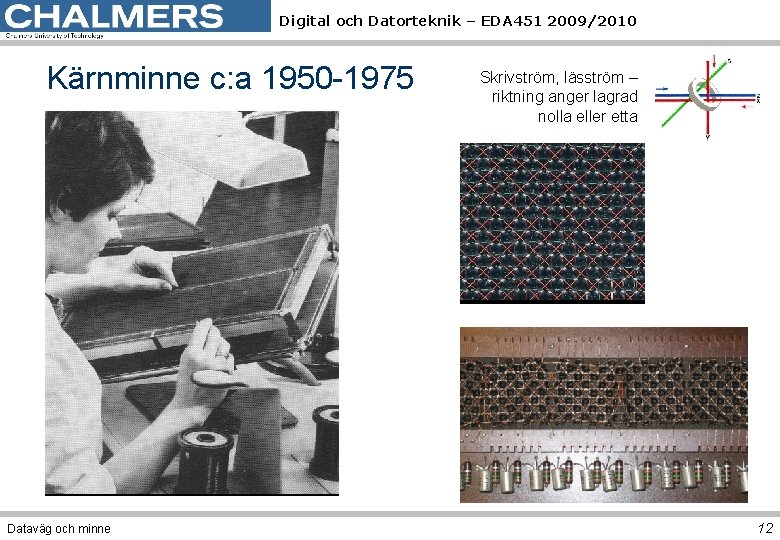

Digital och Datorteknik – EDA 451 2009/2010 Kärnminne c: a 1950 -1975 Dataväg och minne Skrivström, läsström – riktning anger lagrad nolla eller etta 12

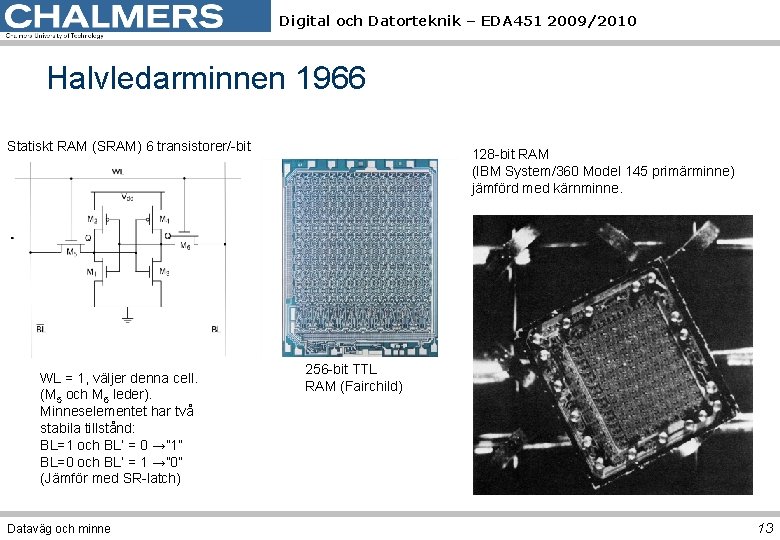

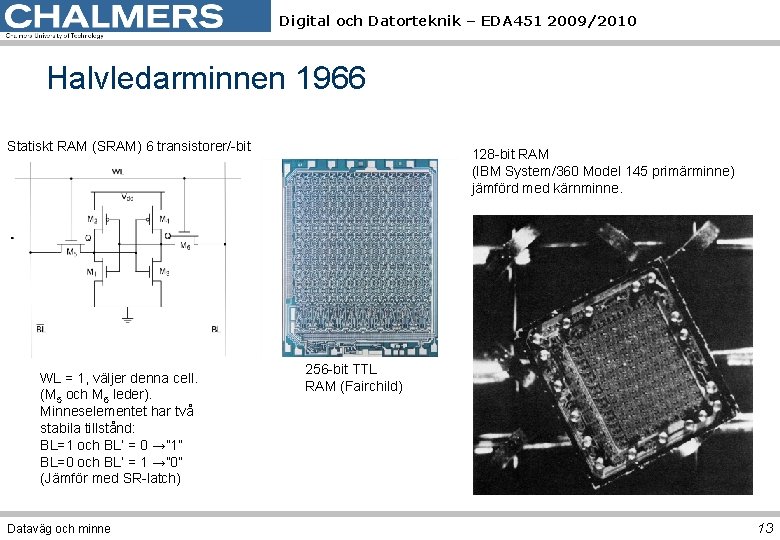

Digital och Datorteknik – EDA 451 2009/2010 Halvledarminnen 1966 Statiskt RAM (SRAM) 6 transistorer/-bit WL = 1, väljer denna cell. (M 5 och M 6 leder). Minneselementet har två stabila tillstånd: BL=1 och BL’ = 0 →” 1” BL=0 och BL’ = 1 →” 0” (Jämför med SR-latch) Dataväg och minne 128 -bit RAM (IBM System/360 Model 145 primärminne) jämförd med kärnminne. 256 -bit TTL RAM (Fairchild) 13

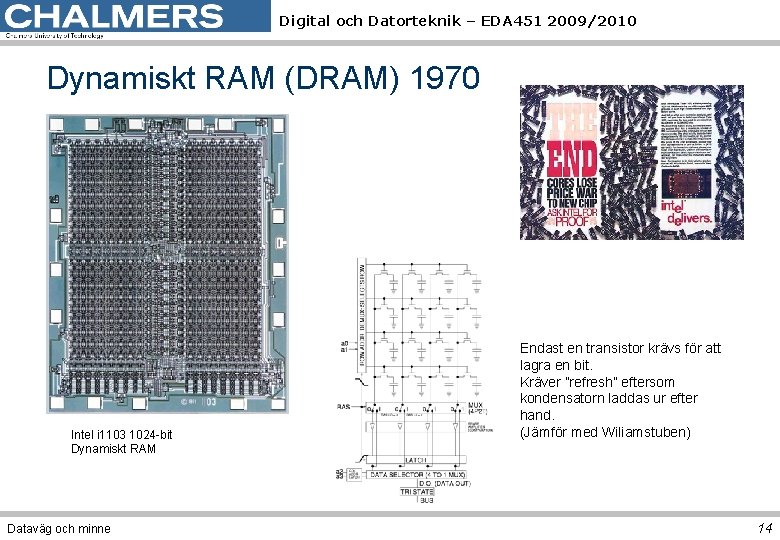

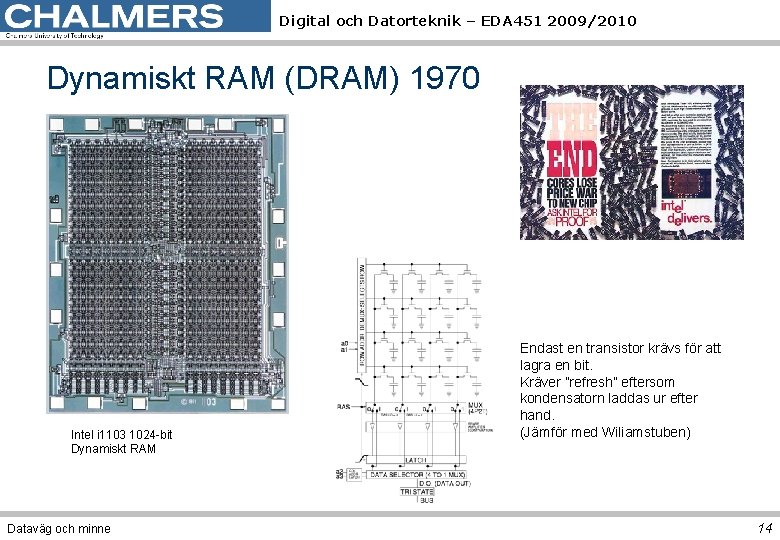

Digital och Datorteknik – EDA 451 2009/2010 Dynamiskt RAM (DRAM) 1970 Intel i 1103 1024 -bit Dynamiskt RAM Dataväg och minne Endast en transistor krävs för att lagra en bit. Kräver ”refresh” eftersom kondensatorn laddas ur efter hand. (Jämför med Wiliamstuben) 14

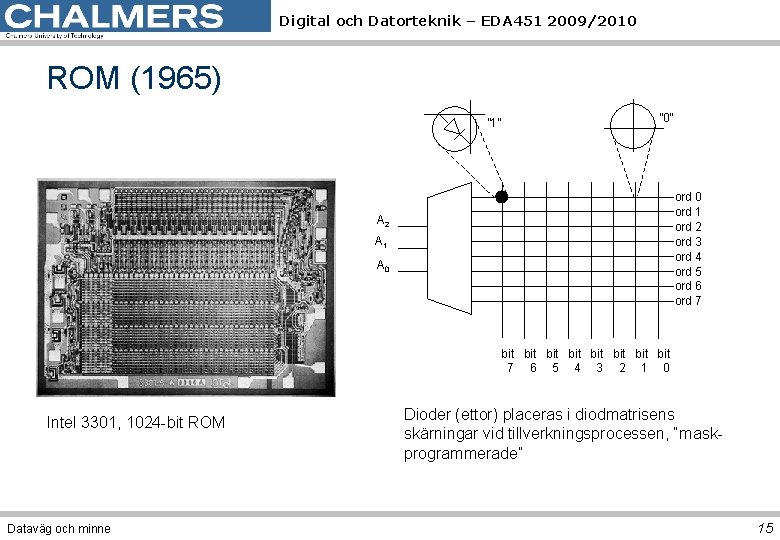

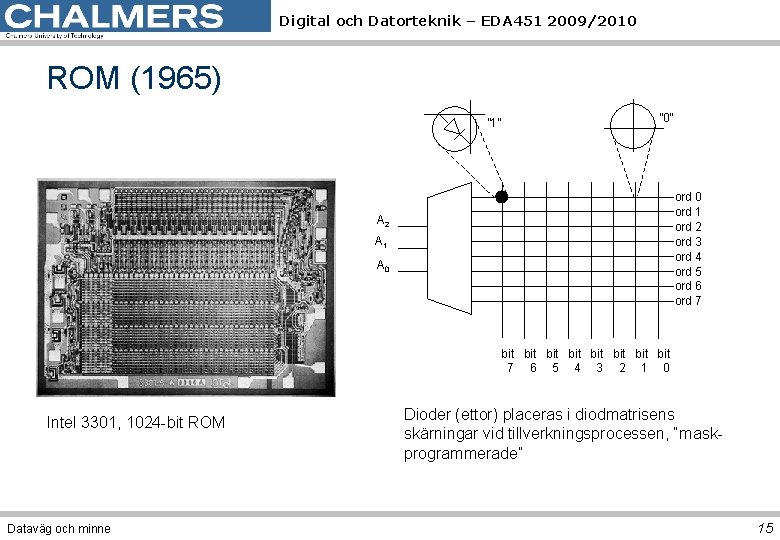

Digital och Datorteknik – EDA 451 2009/2010 ROM (1965) ” 1” ” 0” ord 0 ord 1 ord 2 ord 3 ord 4 ord 5 ord 6 ord 7 A 2 A 1 A 0 bit bit 7 6 5 4 3 2 1 0 Intel 3301, 1024 -bit ROM Dataväg och minne Dioder (ettor) placeras i diodmatrisens skärningar vid tillverkningsprocessen, “maskprogrammerade” 15

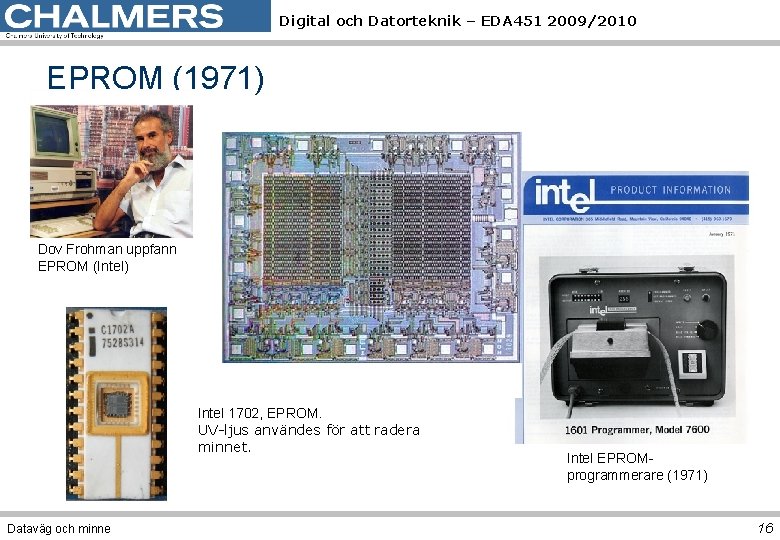

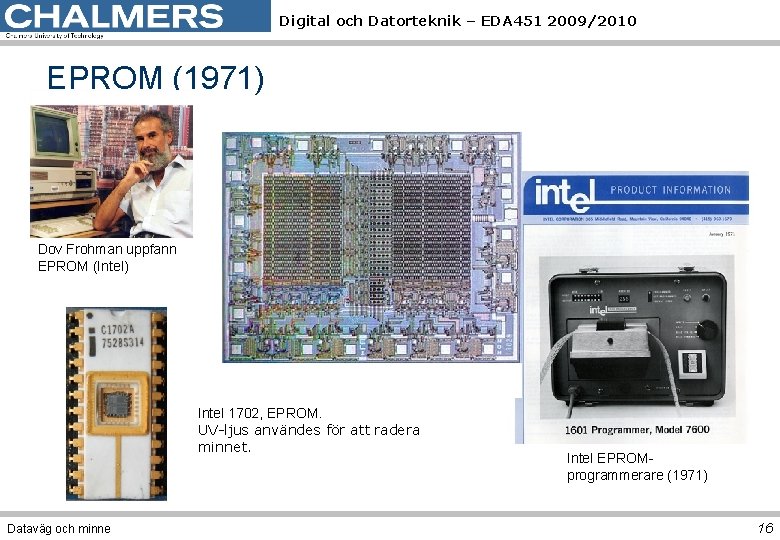

Digital och Datorteknik – EDA 451 2009/2010 EPROM (1971) Dov Frohman uppfann EPROM (Intel) Intel 1702, EPROM. UV-ljus användes för att radera minnet. Dataväg och minne Intel EPROMprogrammerare (1971) 16

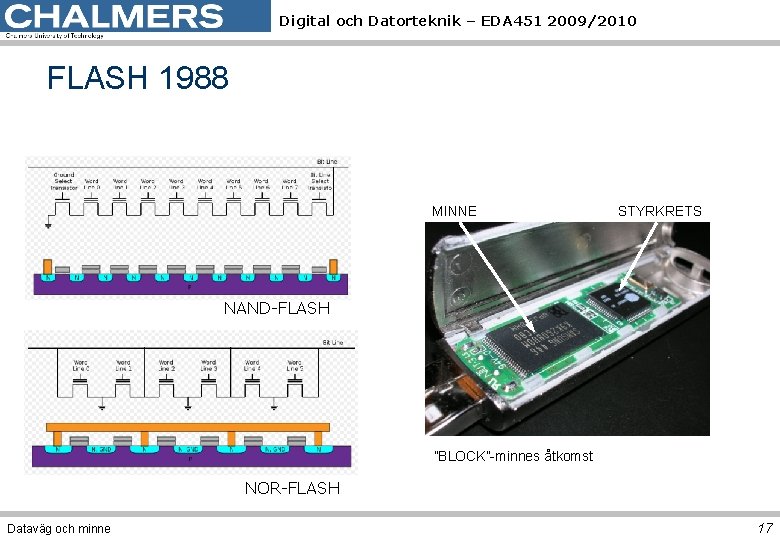

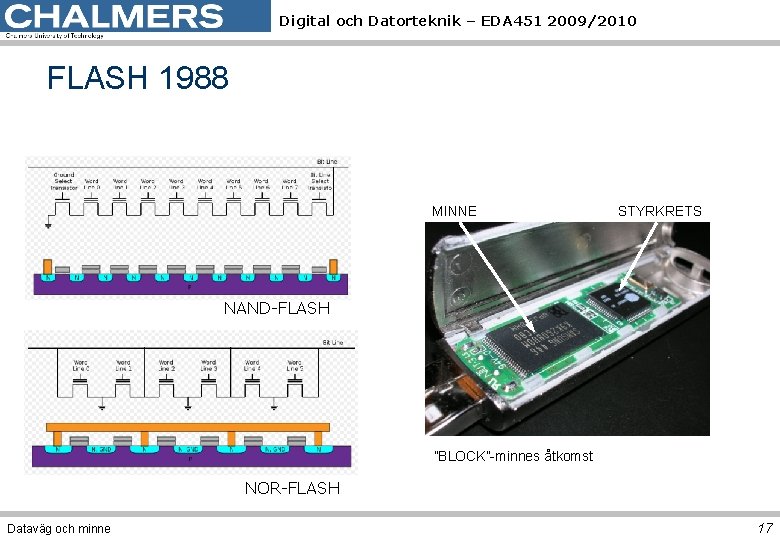

Digital och Datorteknik – EDA 451 2009/2010 FLASH 1988 MINNE STYRKRETS NAND-FLASH ”BLOCK”-minnes åtkomst NOR-FLASH Dataväg och minne 17

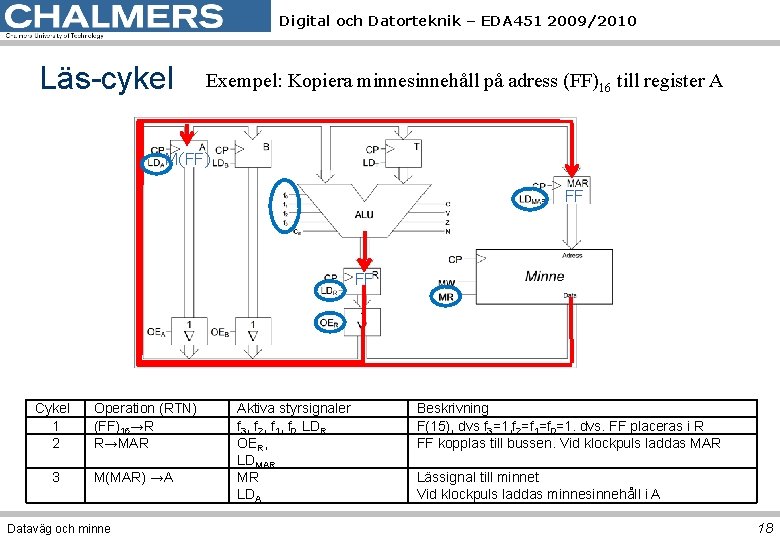

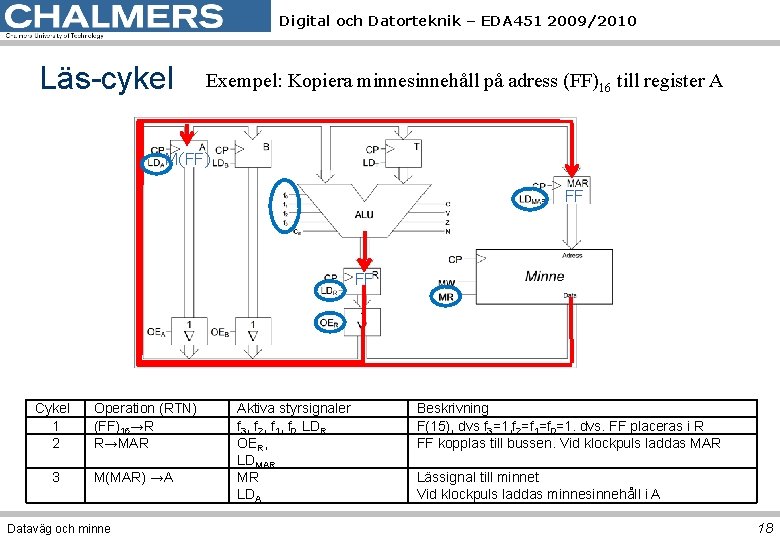

Digital och Datorteknik – EDA 451 2009/2010 Läs-cykel Exempel: Kopiera minnesinnehåll på adress (FF)16 till register A M(FF) FF FF Cykel 1 2 3 Operation (RTN) (FF)16→R R→MAR M(MAR) →A Dataväg och minne Aktiva styrsignaler f 3, f 2, f 1, f 0, LDR OER, LDMAR MR LDA Beskrivning F(15), dvs f 3=1, f 2=f 1=f 0=1. dvs. FF placeras i R FF kopplas till bussen. Vid klockpuls laddas MAR Lässignal till minnet Vid klockpuls laddas minnesinnehåll i A 18

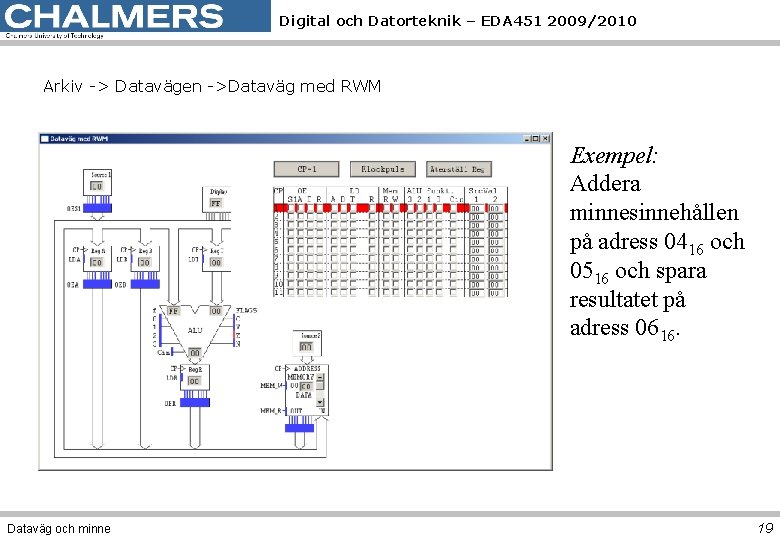

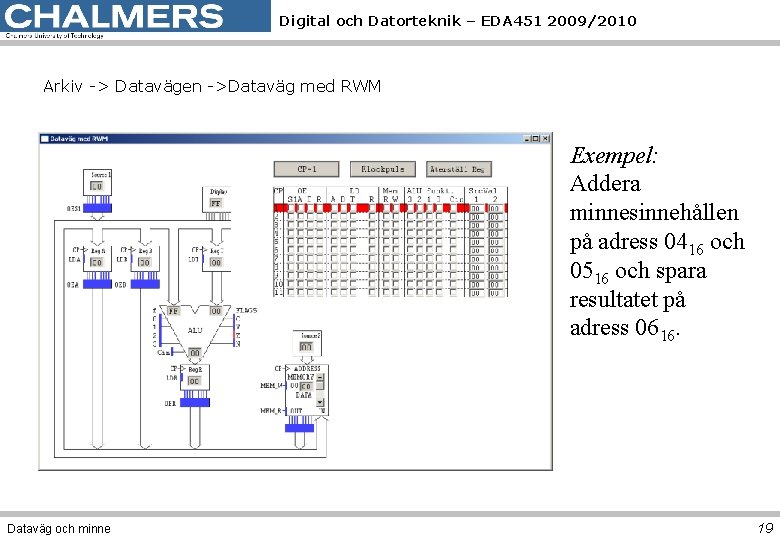

Digital och Datorteknik – EDA 451 2009/2010 Arkiv -> Datavägen ->Dataväg med RWM Exempel: Addera minnesinnehållen på adress 0416 och 0516 och spara resultatet på adress 0616. Dataväg och minne 19

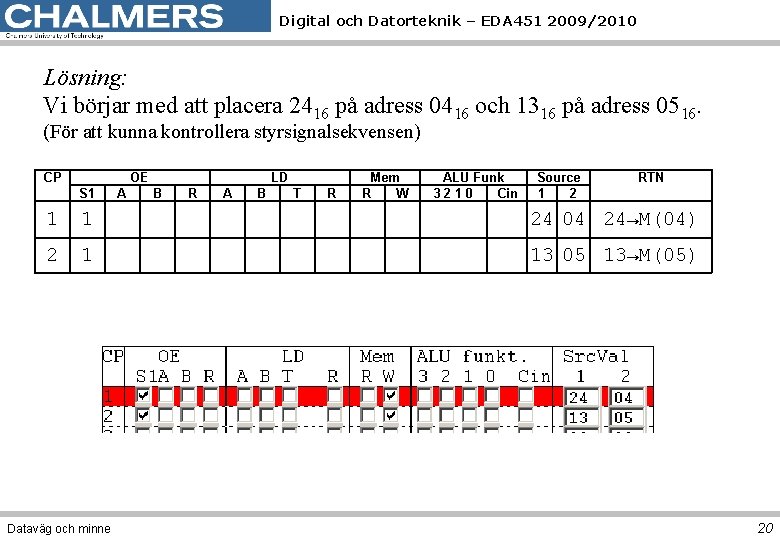

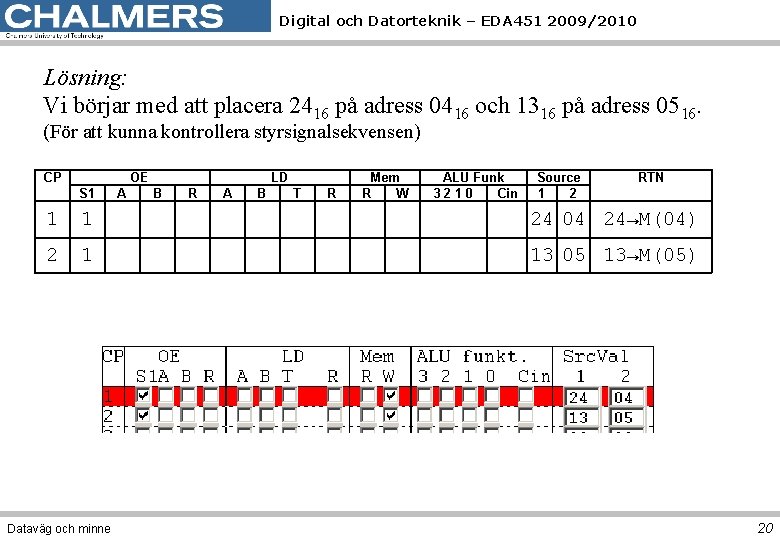

Digital och Datorteknik – EDA 451 2009/2010 Lösning: Vi börjar med att placera 2416 på adress 0416 och 1316 på adress 0516. (För att kunna kontrollera styrsignalsekvensen) CP OE S 1 A LD B R A B T R Mem R W ALU Funk 3210 Cin Source 1 2 RTN 1 1 24 04 24→M(04) 2 1 13 05 13→M(05) Dataväg och minne 20

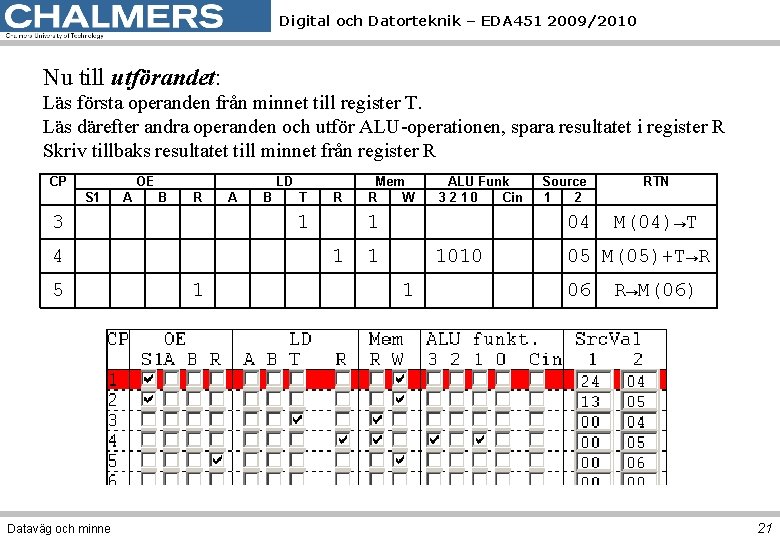

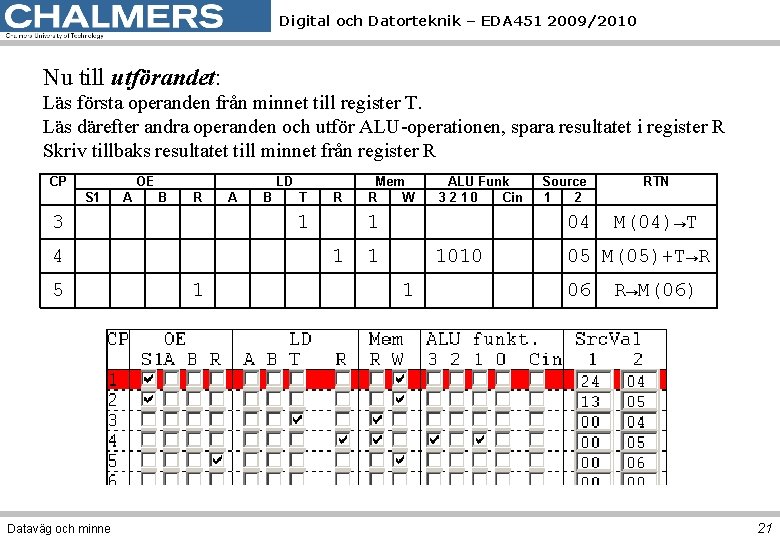

Digital och Datorteknik – EDA 451 2009/2010 Nu till utförandet: Läs första operanden från minnet till register T. Läs därefter andra operanden och utför ALU-operationen, spara resultatet i register R Skriv tillbaks resultatet till minnet från register R CP OE S 1 A LD B R 3 Dataväg och minne B T R 1 4 5 A ALU Funk 3210 Cin 1 1 1 Mem R W Source 1 2 04 1 1010 1 RTN M(04)→T 05 M(05)+T→R 06 R→M(06) 21

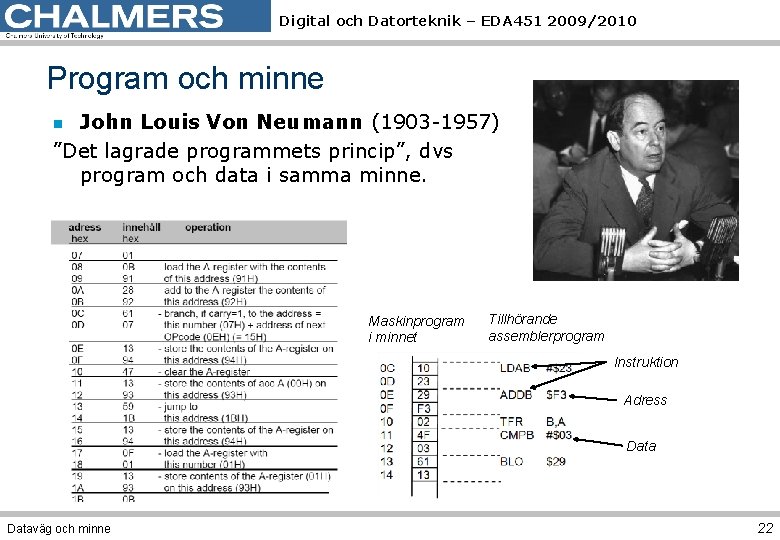

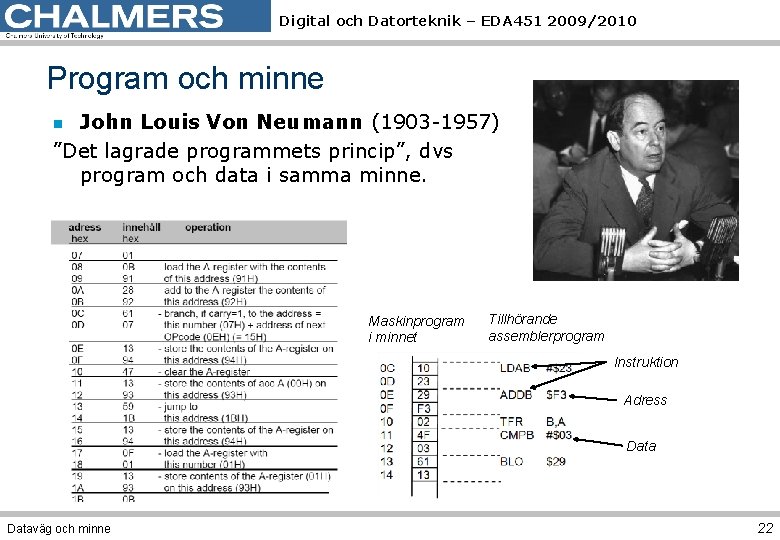

Digital och Datorteknik – EDA 451 2009/2010 Program och minne John Louis Von Neumann (1903 -1957) ”Det lagrade programmets princip”, dvs program och data i samma minne. n Maskinprogram i minnet Tillhörande assemblerprogram Instruktion Adress Dataväg och minne 22

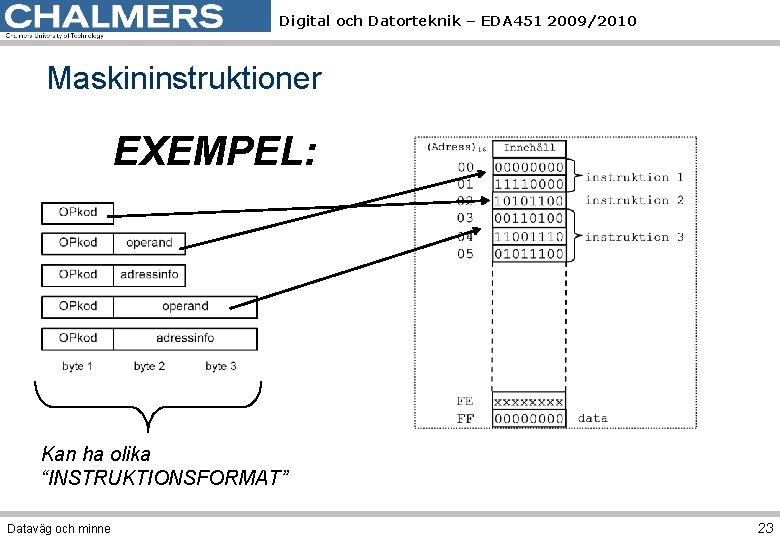

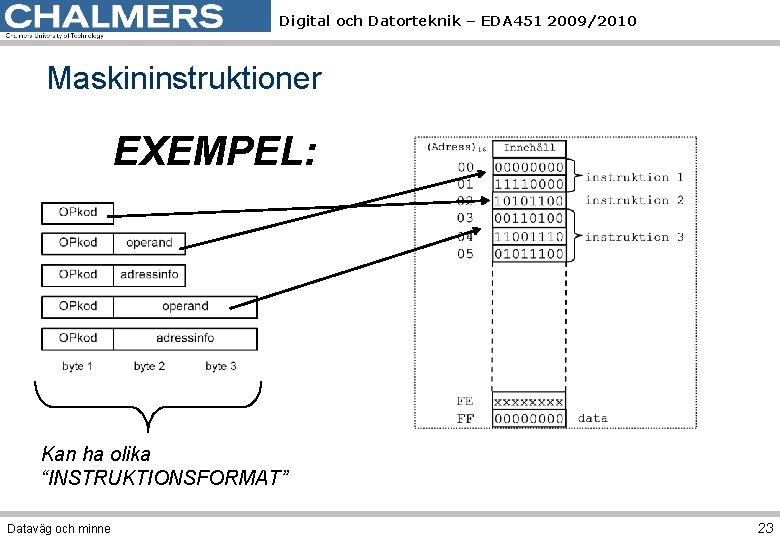

Digital och Datorteknik – EDA 451 2009/2010 Maskininstruktioner EXEMPEL: Kan ha olika “INSTRUKTIONSFORMAT” Dataväg och minne 23

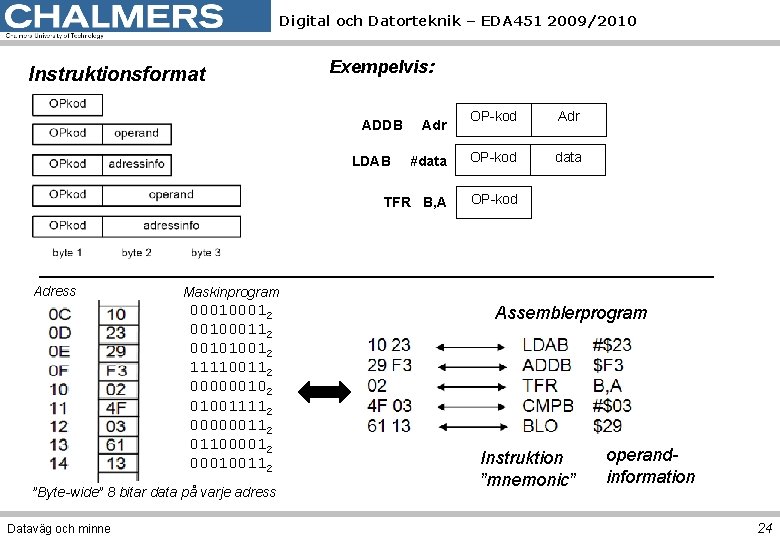

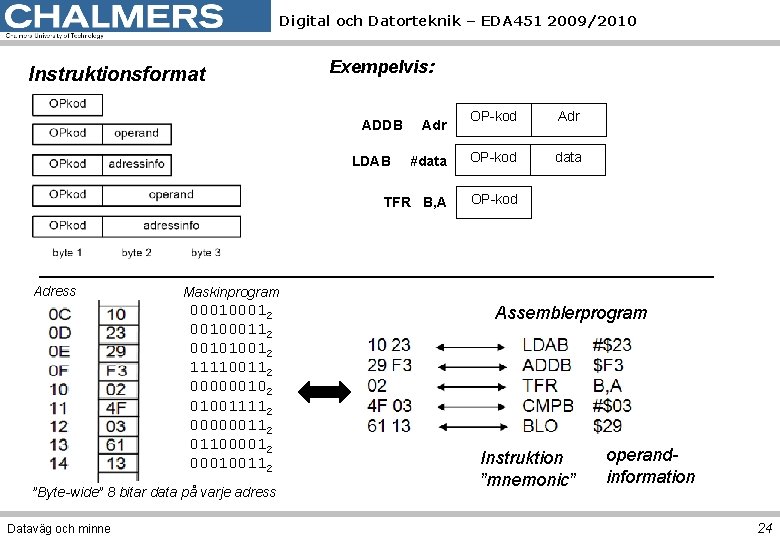

Digital och Datorteknik – EDA 451 2009/2010 Instruktionsformat Exempelvis: OP-kod Adr #data OP-kod data TFR B, A OP-kod ADDB LDAB Adress Maskinprogram 00012 001000112 001010012 111100112 000000102 010011112 000000112 011000012 000100112 ”Byte-wide” 8 bitar data på varje adress Dataväg och minne Adr Assemblerprogram Instruktion ”mnemonic” operandinformation 24

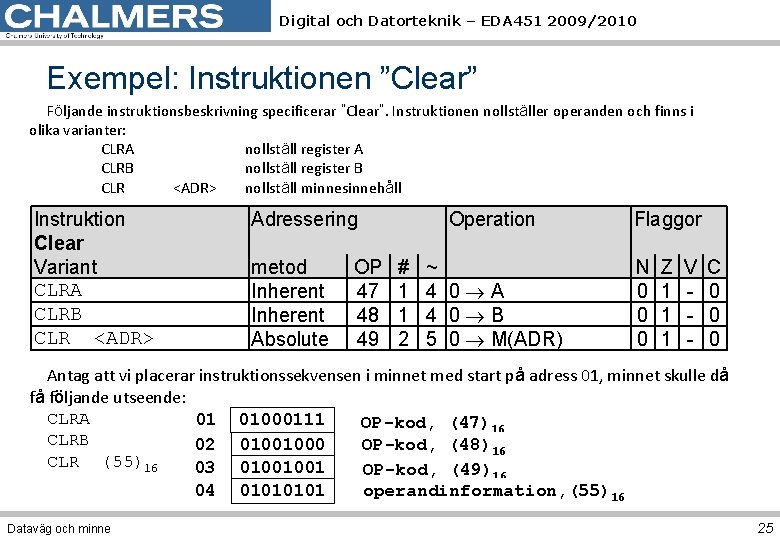

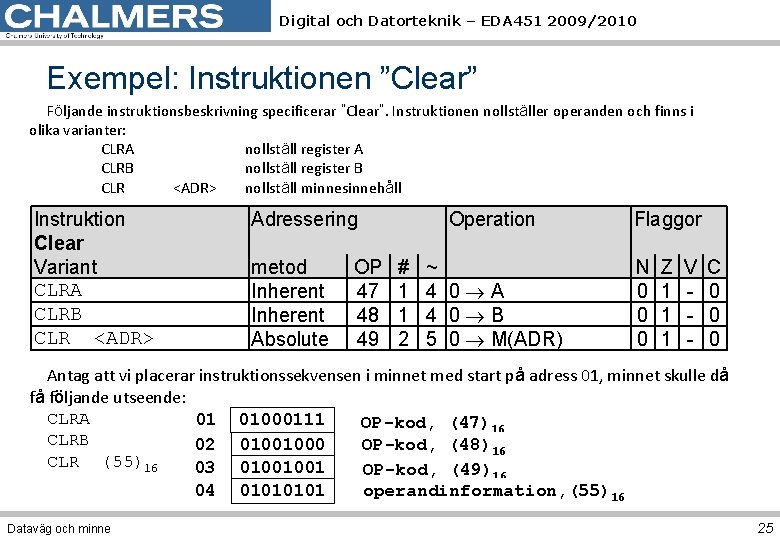

Digital och Datorteknik – EDA 451 2009/2010 Exempel: Instruktionen ”Clear” Följande instruktionsbeskrivning specificerar ”Clear”. Instruktionen nollställer operanden och finns i olika varianter: CLRA nollställ register A CLRB nollställ register B CLR <ADR> nollställ minnesinnehåll Instruktion Clear Variant CLRA CLRB CLR <ADR> Adressering metod Inherent Absolute OP 47 48 49 Operation # 1 1 2 ~ 4 0 A 4 0 B 5 0 M(ADR) Flaggor N 0 0 0 Z 1 1 1 V - C 0 0 0 Antag att vi placerar instruktionssekvensen i minnet med start på adress 01, minnet skulle då få följande utseende: CLRA 01 01000111 OP-kod, (47)16 CLRB 02 01001000 OP-kod, (48)16 CLR (55)16 03 01001001 OP-kod, (49)16 04 0101 operandinformation, (55)16 Dataväg och minne 25

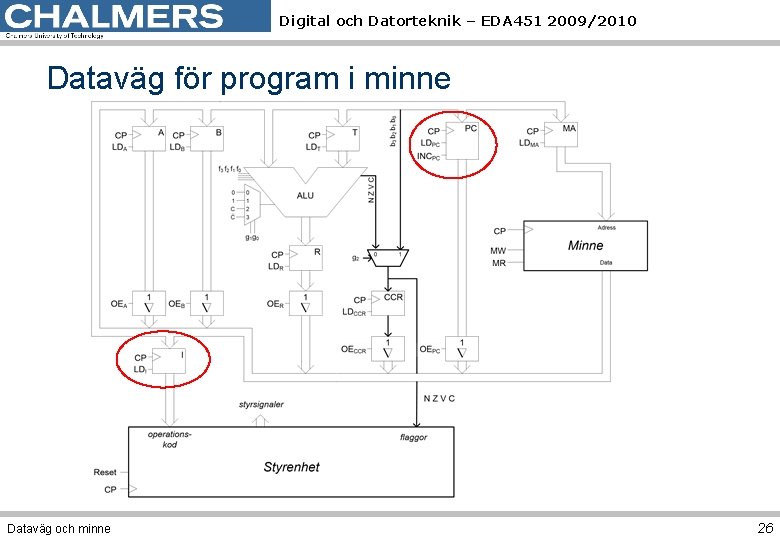

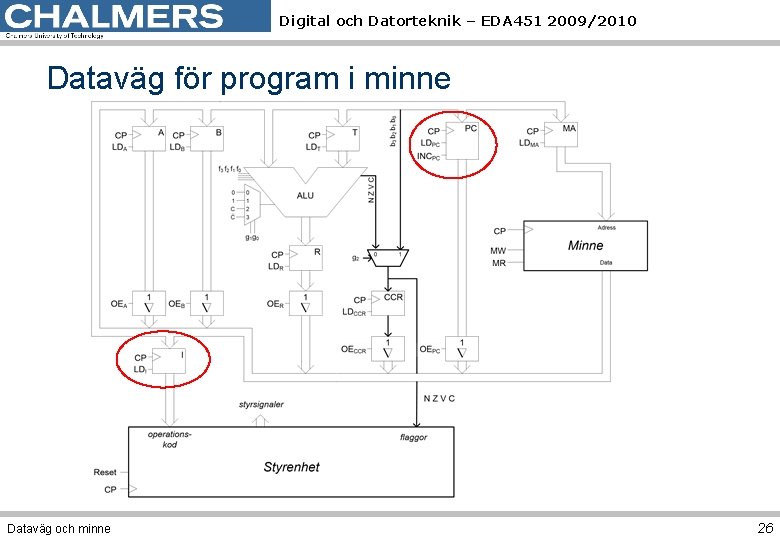

Digital och Datorteknik – EDA 451 2009/2010 Dataväg för program i minne Dataväg och minne 26

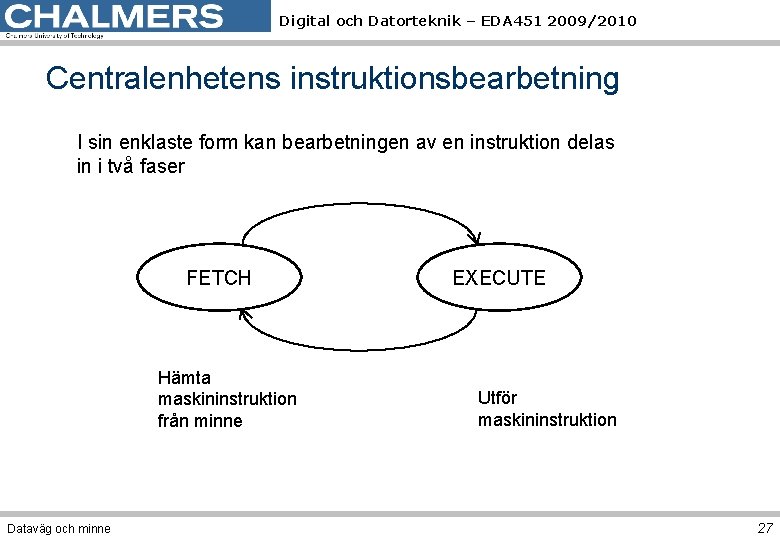

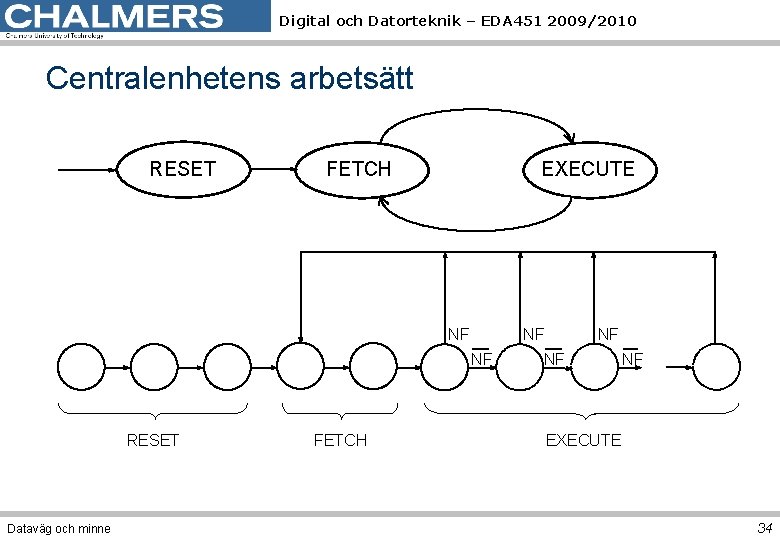

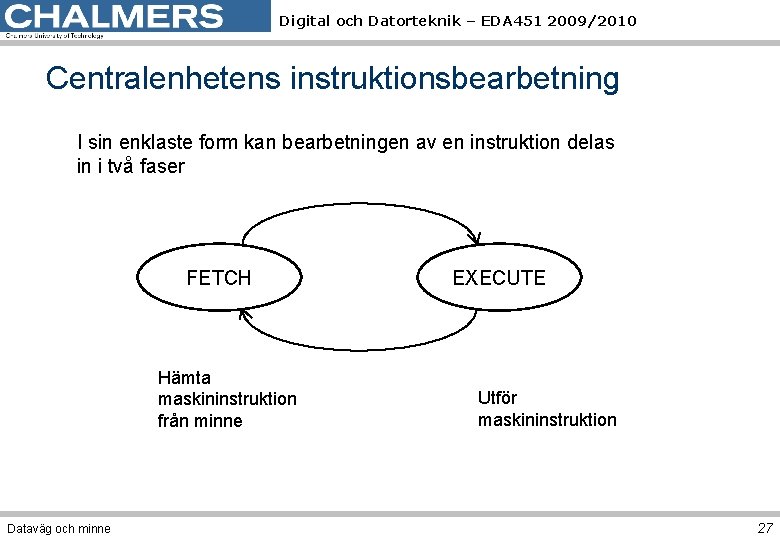

Digital och Datorteknik – EDA 451 2009/2010 Centralenhetens instruktionsbearbetning I sin enklaste form kan bearbetningen av en instruktion delas in i två faser FETCH Hämta maskininstruktion från minne Dataväg och minne EXECUTE Utför maskininstruktion 27

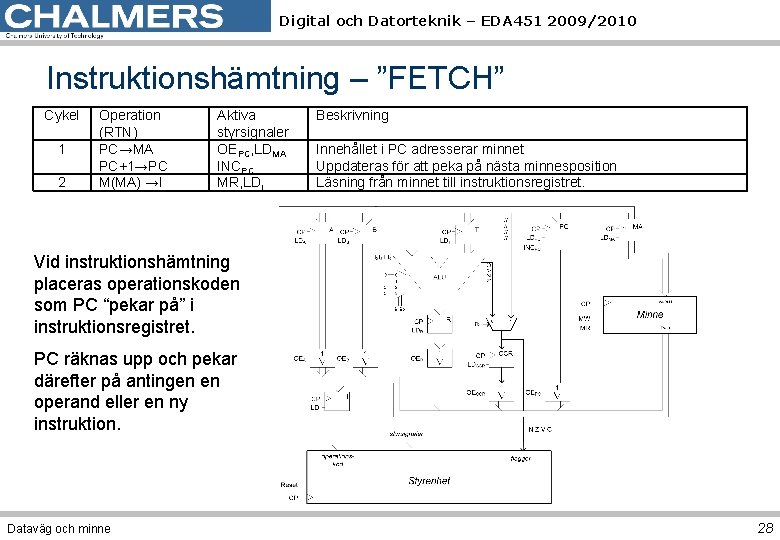

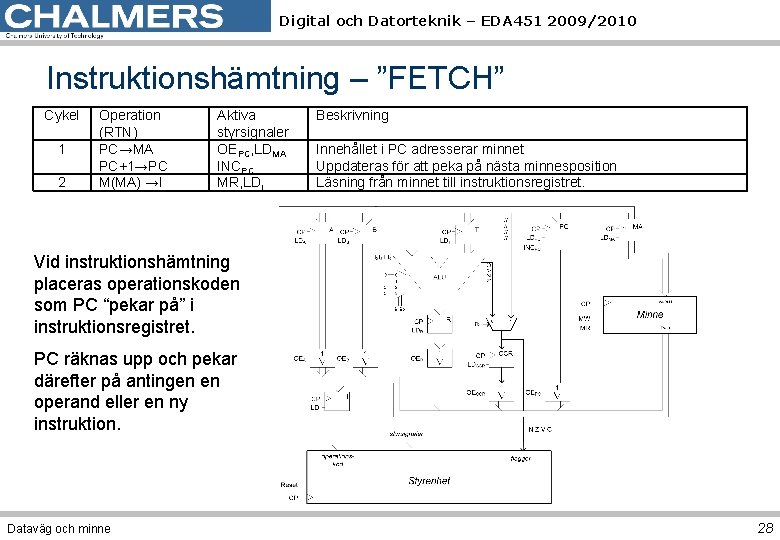

Digital och Datorteknik – EDA 451 2009/2010 Instruktionshämtning – ”FETCH” Cykel 1 2 Operation (RTN) PC→MA PC+1→PC M(MA) →I Aktiva styrsignaler OEPC, LDMA INCPC MR, LDI Beskrivning Innehållet i PC adresserar minnet Uppdateras för att peka på nästa minnesposition Läsning från minnet till instruktionsregistret. Vid instruktionshämtning placeras operationskoden som PC “pekar på” i instruktionsregistret. PC räknas upp och pekar därefter på antingen en operand eller en ny instruktion. Dataväg och minne 28

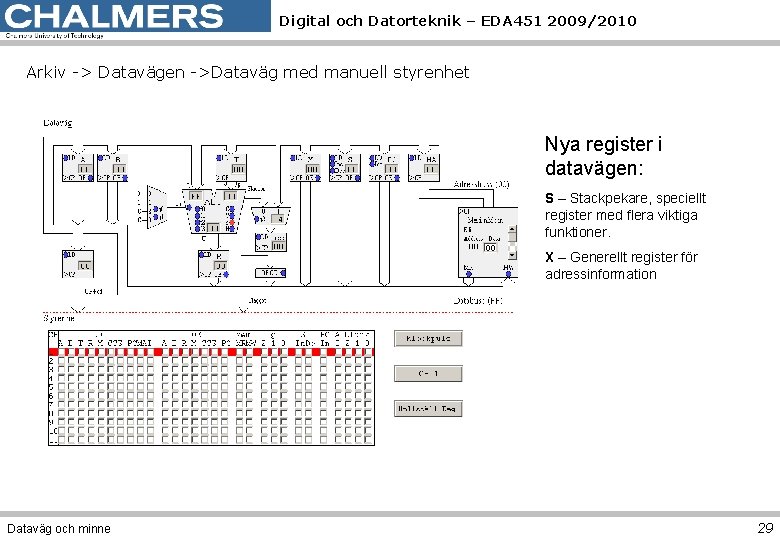

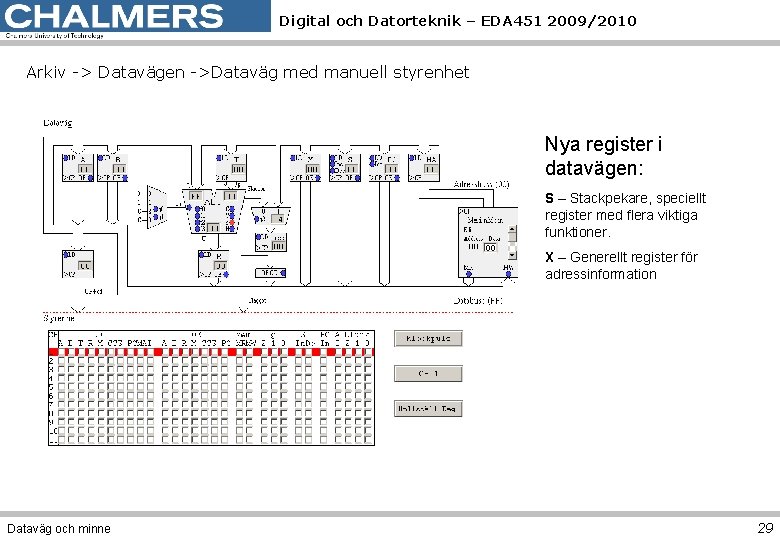

Digital och Datorteknik – EDA 451 2009/2010 Arkiv -> Datavägen ->Dataväg med manuell styrenhet Nya register i datavägen: S – Stackpekare, speciellt register med flera viktiga funktioner. X – Generellt register för adressinformation Dataväg och minne 29

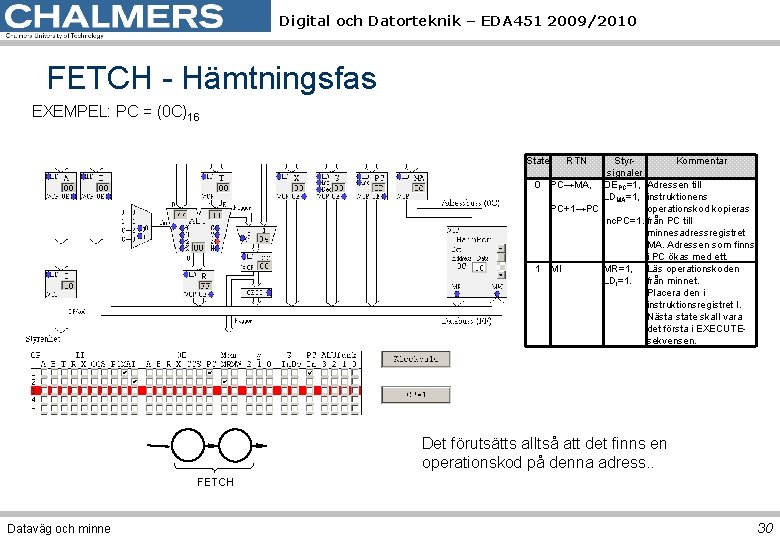

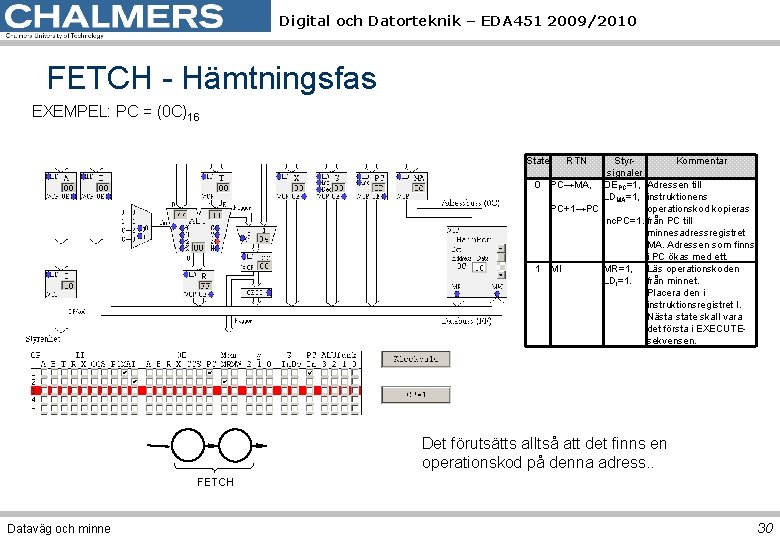

Digital och Datorteknik – EDA 451 2009/2010 FETCH - Hämtningsfas EXEMPEL: PC = (0 C)16 State RTN Styr. Kommentar signaler 0 PC→MA, OEPC=1, Adressen till LDMA=1, instruktionens PC+1→PC operationskod kopieras Inc. PC=1. från PC till minnesadressregistret MA. Adressen som finns i PC ökas med ett. 1 MI MR=1, Läs operationskoden LDI=1. från minnet. Placera den i instruktionsregistret I. Nästa state skall vara det första i EXECUTEsekvensen. Det förutsätts alltså att det finns en operationskod på denna adress. . FETCH Dataväg och minne 30

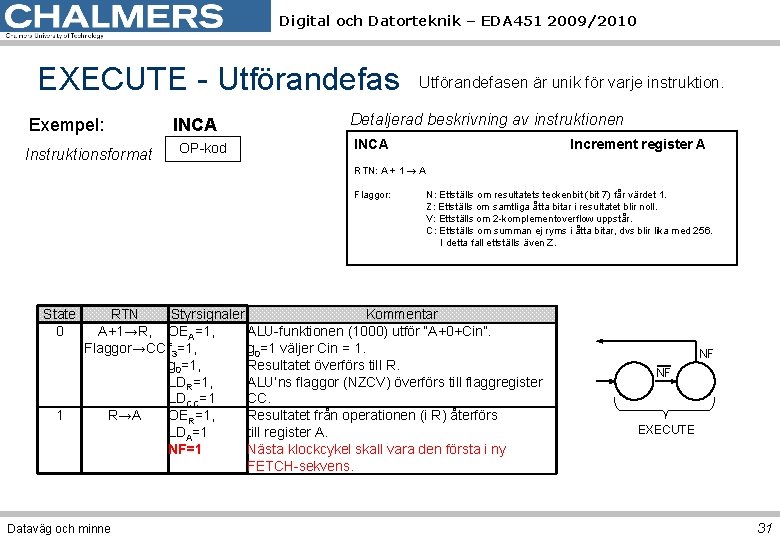

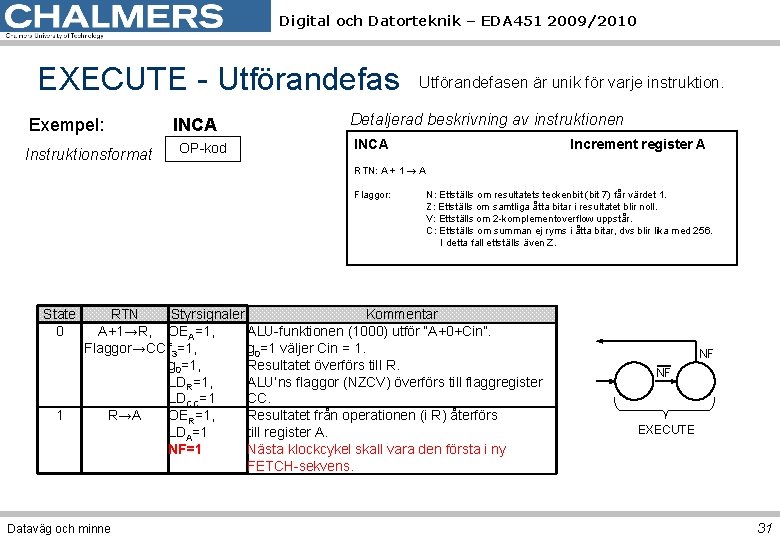

Digital och Datorteknik – EDA 451 2009/2010 EXECUTE - Utförandefas Exempel: Instruktionsformat INCA OP-kod Utförandefasen är unik för varje instruktion. Detaljerad beskrivning av instruktionen INCA Increment register A RTN: A + 1 A Flaggor: State 0 1 N: Ettställs om resultatets teckenbit (bit 7) får värdet 1. Z: Ettställs om samtliga åtta bitar i resultatet blir noll. V: Ettställs om 2 -komplementoverflow uppstår. C: Ettställs om summan ej ryms i åtta bitar, dvs blir lika med 256. I detta fall ettställs även Z. RTN Styrsignaler Kommentar A+1→R, OEA=1, ALU-funktionen (1000) utför “A+0+Cin”. Flaggor→CC f 3=1, g 0=1 väljer Cin = 1. g 0=1, Resultatet överförs till R. LDR=1, ALU’ns flaggor (NZCV) överförs till flaggregister LDCC=1 CC. R→A OER=1, Resultatet från operationen (i R) återförs LDA=1 till register A. NF=1 Nästa klockcykel skall vara den första i ny FETCH-sekvens. Dataväg och minne NF NF EXECUTE 31

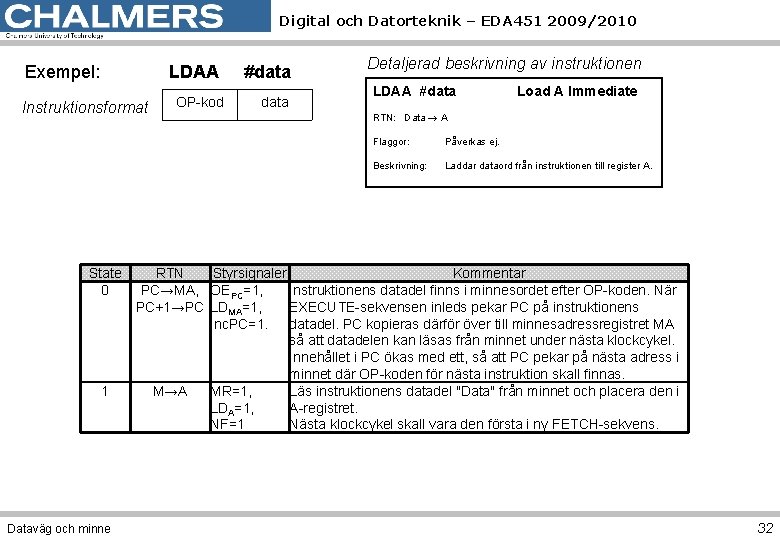

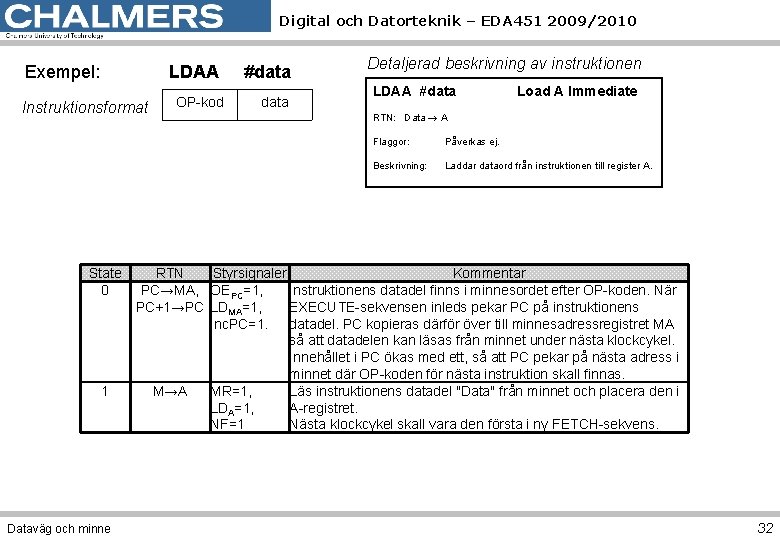

Digital och Datorteknik – EDA 451 2009/2010 Exempel: LDAA Instruktionsformat State 0 1 Dataväg och minne OP-kod #data Detaljerad beskrivning av instruktionen LDAA #data Load A Immediate RTN: Data A Flaggor: Påverkas ej. Beskrivning: Laddar dataord från instruktionen till register A. RTN Styrsignaler Kommentar PC→MA, OEPC=1, Instruktionens datadel finns i minnesordet efter OP-koden. När PC+1→PC LDMA=1, EXECUTE-sekvensen inleds pekar PC på instruktionens Inc. PC=1. datadel. PC kopieras därför över till minnesadressregistret MA så att datadelen kan läsas från minnet under nästa klockcykel. Innehållet i PC ökas med ett, så att PC pekar på nästa adress i minnet där OP-koden för nästa instruktion skall finnas. M→A MR=1, Läs instruktionens datadel "Data" från minnet och placera den i LDA=1, A-registret. NF=1 Nästa klockcykel skall vara den första i ny FETCH-sekvens. 32

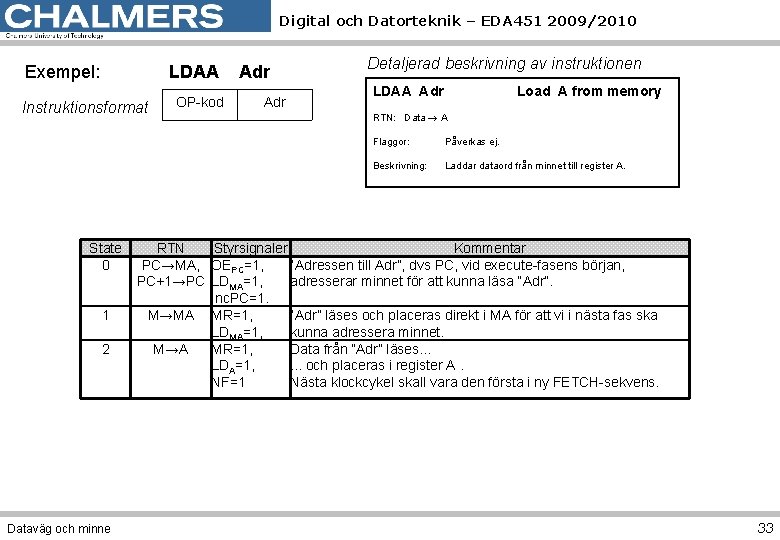

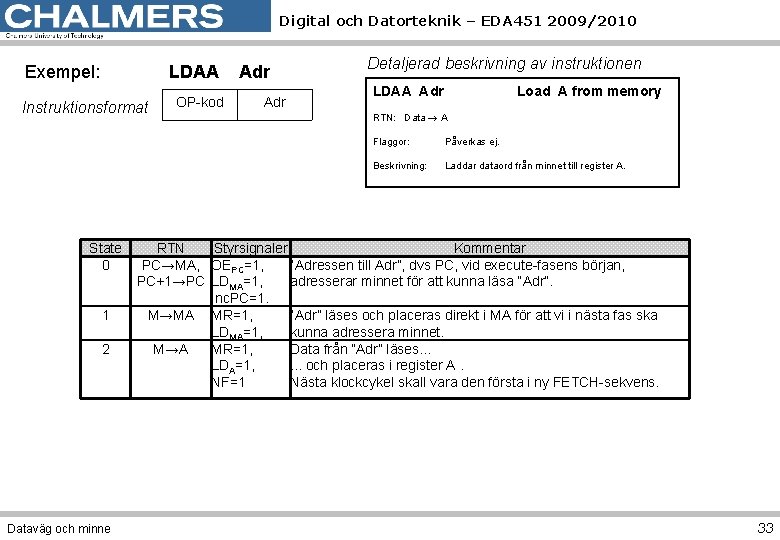

Digital och Datorteknik – EDA 451 2009/2010 Exempel: LDAA Instruktionsformat State 0 1 2 Dataväg och minne OP-kod Adr Detaljerad beskrivning av instruktionen LDAA Adr Load A from memory RTN: Data A Flaggor: Påverkas ej. Beskrivning: Laddar dataord från minnet till register A. RTN Styrsignaler Kommentar PC→MA, OEPC=1, “Adressen till Adr”, dvs PC, vid execute-fasens början, PC+1→PC LDMA=1, adresserar minnet för att kunna läsa “Adr”. Inc. PC=1. M→MA MR=1, “Adr” läses och placeras direkt i MA för att vi i nästa fas ska LDMA=1, kunna adressera minnet. M→A MR=1, Data från “Adr” läses. . . LDA=1, . . . och placeras i register A. NF=1 Nästa klockcykel skall vara den första i ny FETCH-sekvens. 33

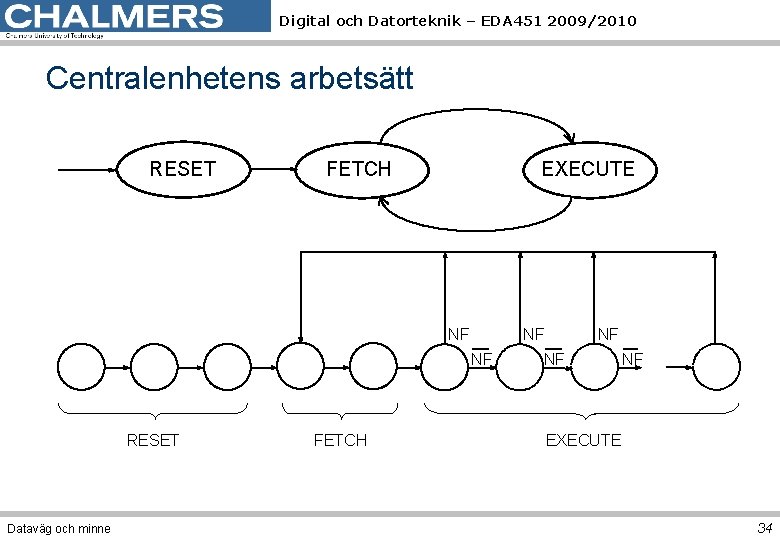

Digital och Datorteknik – EDA 451 2009/2010 Centralenhetens arbetsätt RESET FETCH EXECUTE NF NF NF RESET Dataväg och minne FETCH NF NF NF EXECUTE 34

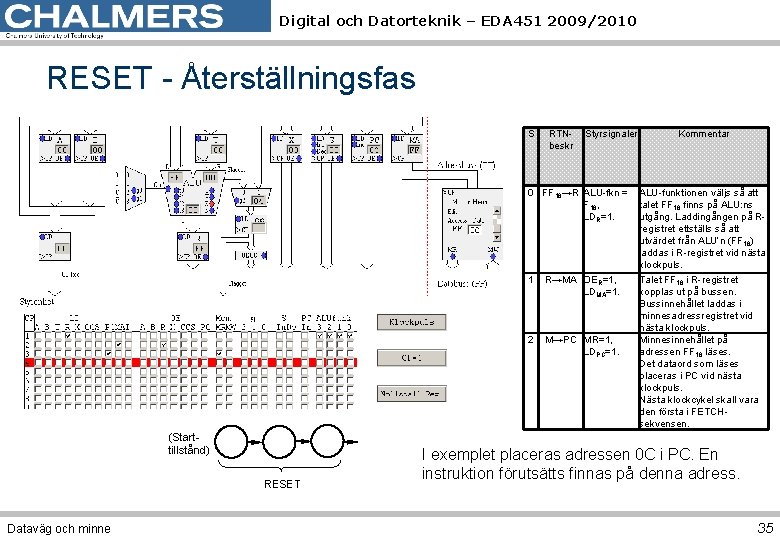

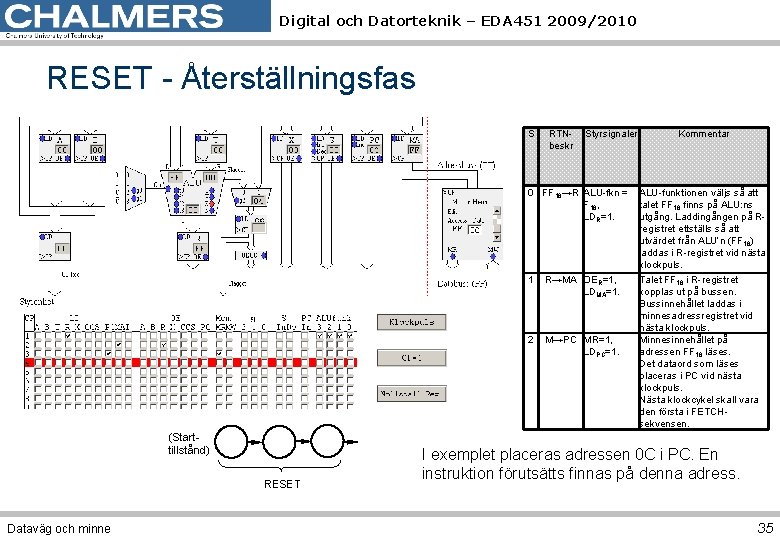

Digital och Datorteknik – EDA 451 2009/2010 RESET - Återställningsfas S (Starttillstånd) RESET Dataväg och minne RTNbeskr Styrsignaler Kommentar 0 FF 16→R ALU-fkn = F 16, LDR=1. ALU-funktionen väljs så att talet FF 16 finns på ALU: ns utgång. Laddingången på Rregistret ettställs så att utvärdet från ALU’n (FF 16) laddas i R-registret vid nästa klockpuls. 1 R→MA OER=1, LDMA=1. 2 M→PC MR=1, LDPC=1. Talet FF 16 i R-registret kopplas ut på bussen. Bussinnehållet laddas i minnesadressregistret vid nästa klockpuls. Minnesinnehållet på adressen FF 16 läses. Det dataord som läses placeras i PC vid nästa klockpuls. Nästa klockcykel skall vara den första i FETCHsekvensen. I exemplet placeras adressen 0 C i PC. En instruktion förutsätts finnas på denna adress. 35