Digital ModelingImplementation of Valve Amplifiers Cody Frye Mitchell

- Slides: 30

Digital Modeling/Implementation of Valve Amplifiers Cody Frye & Mitchell Gould 1

Agenda 1. 2. 3. 4. 5. 6. 7. 8. Introduction Motivation System Description Methods Preliminary Results Hardware Implementation Consideration Bill of Materials Schedule of Work 2

Introduction 3

Introduction ● Significance of valve amplifiers ● Pros of valve amplifiers ○ ○ Smooth clipping Warm tone characteristics ● Cons of valve amplifiers ○ ○ ○ Weight Heat Cost 4

Motivation ● Affordable, Cheap, and Convenient ● Multiple Amplifiers to choose from ● No Analog Components for reduced Component Size 5

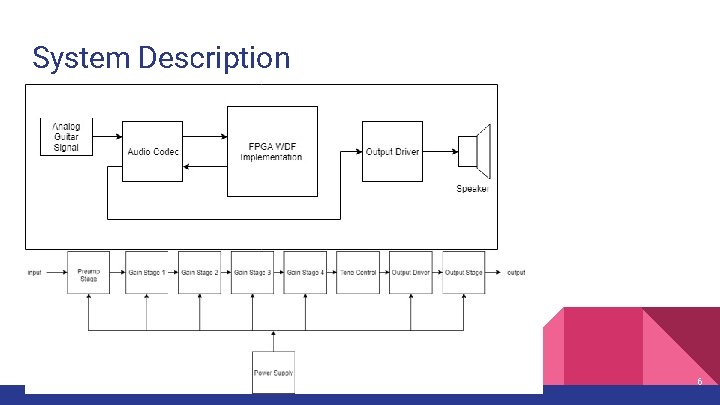

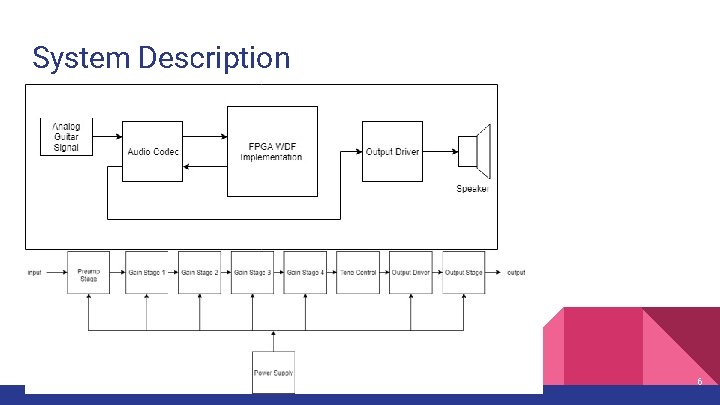

System Description 6

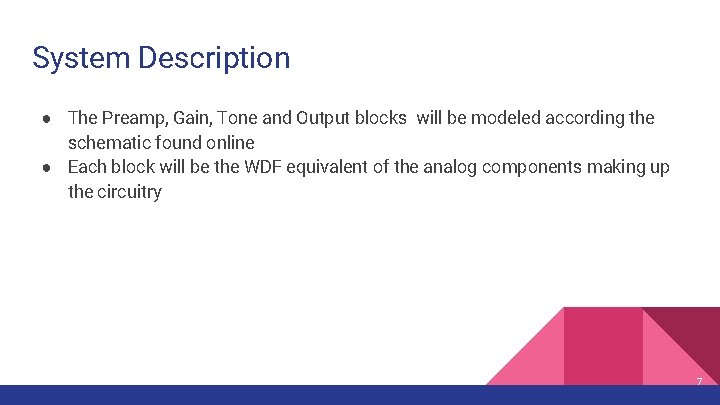

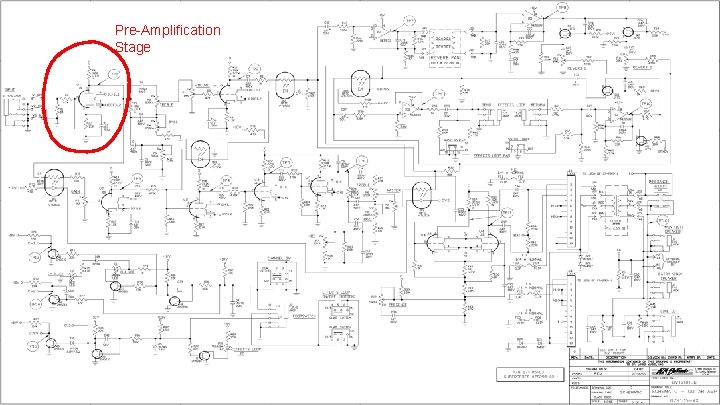

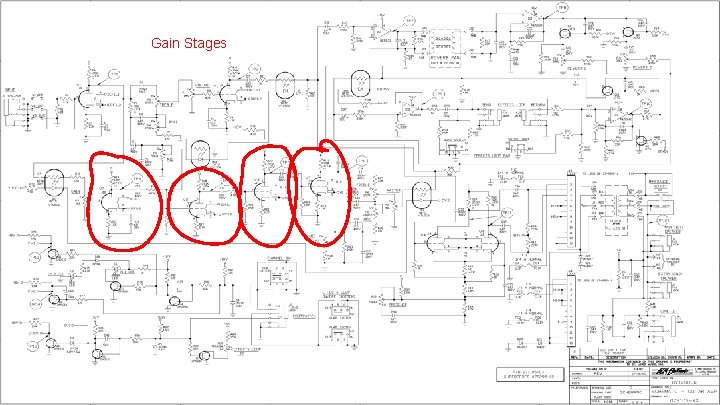

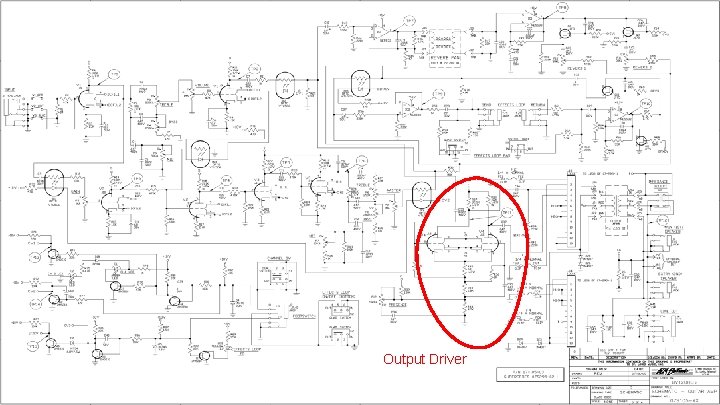

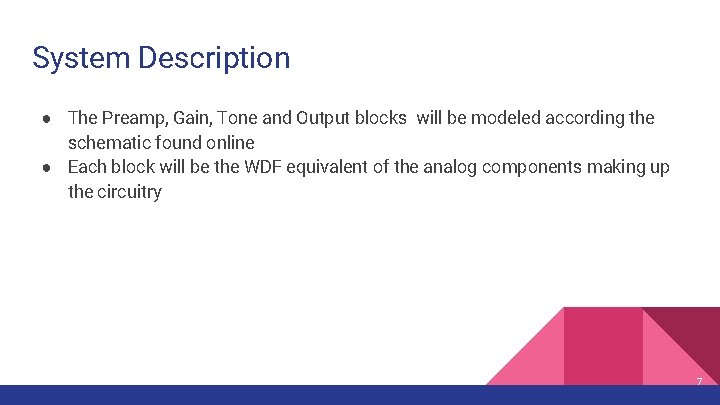

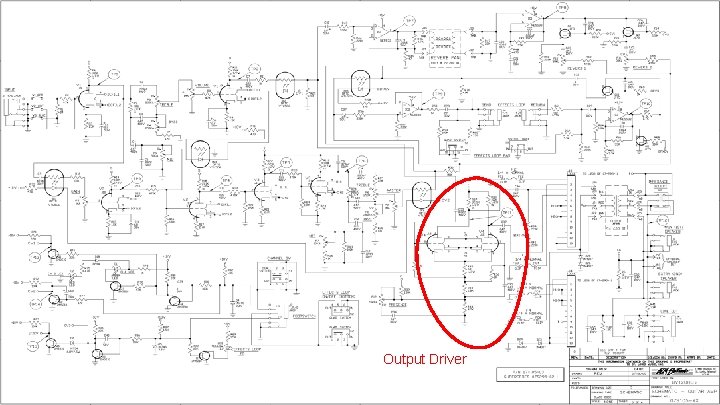

System Description ● The Preamp, Gain, Tone and Output blocks will be modeled according the schematic found online ● Each block will be the WDF equivalent of the analog components making up the circuitry 7

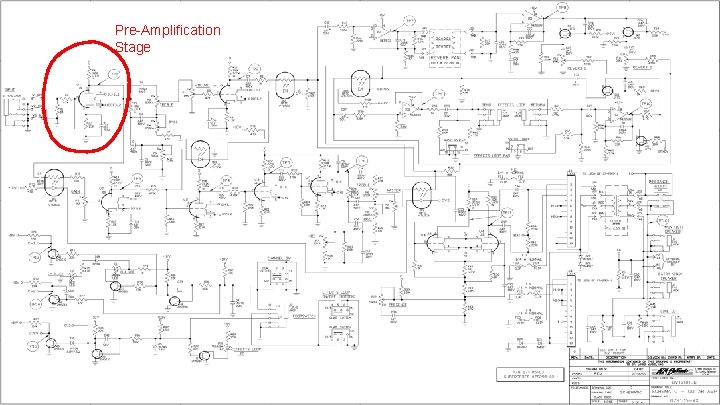

Pre-Amplification Stage 8

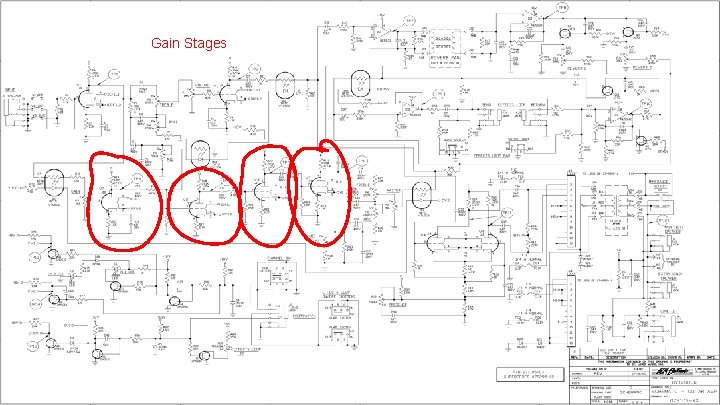

Gain Stages 9

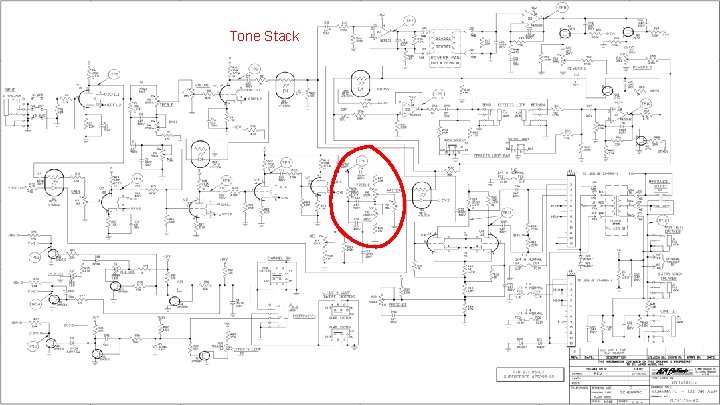

Tone Stack 10

Output Driver 11

Methods ● Frequency Bin / Lookup Table Method ● Model Individual Blocks of System ● Wave Digital Filtering 12

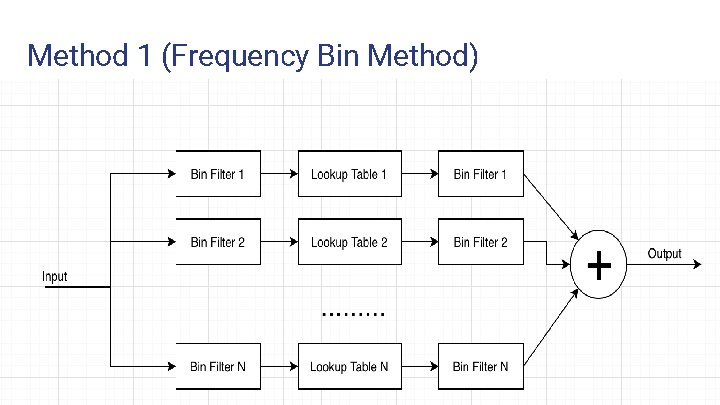

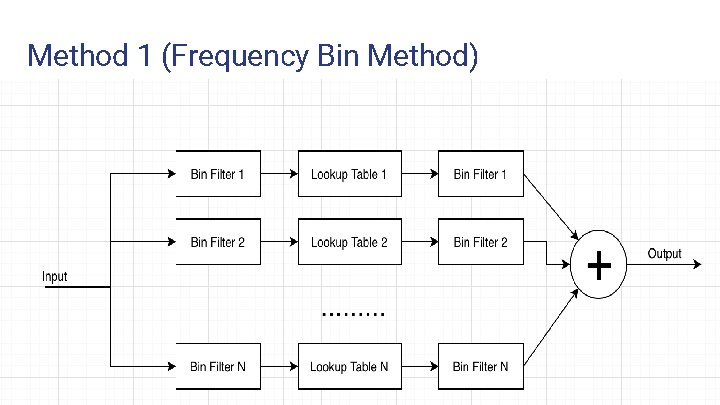

Method 1 (Frequency Bin Method). . . 13

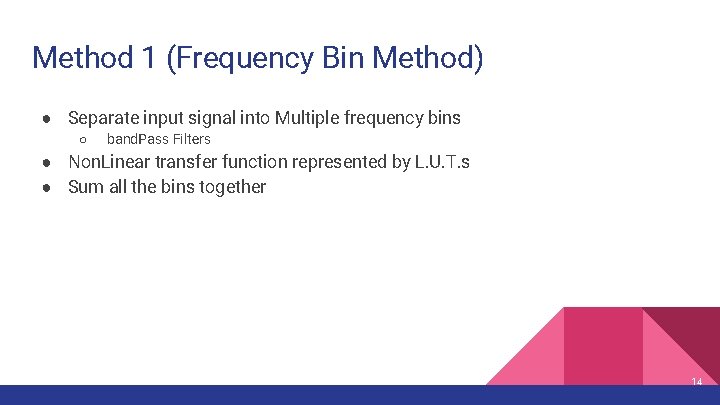

Method 1 (Frequency Bin Method) ● Separate input signal into Multiple frequency bins ○ band. Pass Filters ● Non. Linear transfer function represented by L. U. T. s ● Sum all the bins together 14

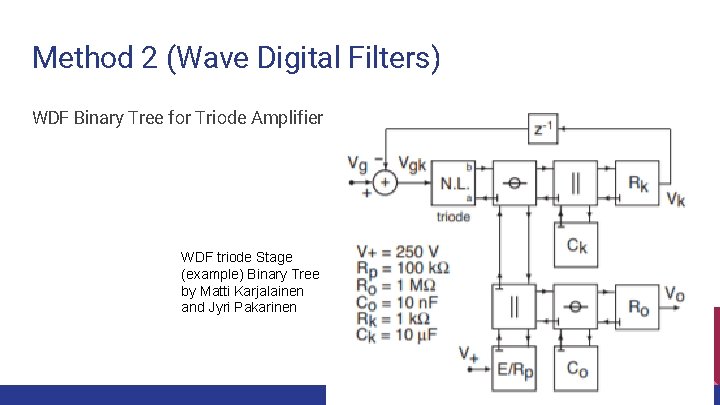

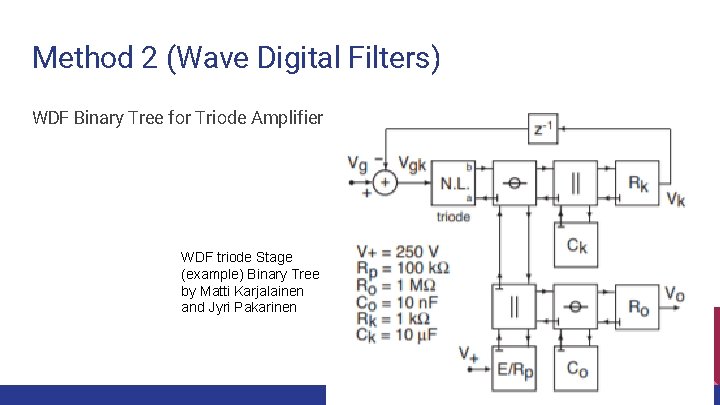

Method 2 (Wave Digital Filters) WDF Binary Tree for Triode Amplifier WDF triode Stage (example) Binary Tree by Matti Karjalainen and Jyri Pakarinen 15

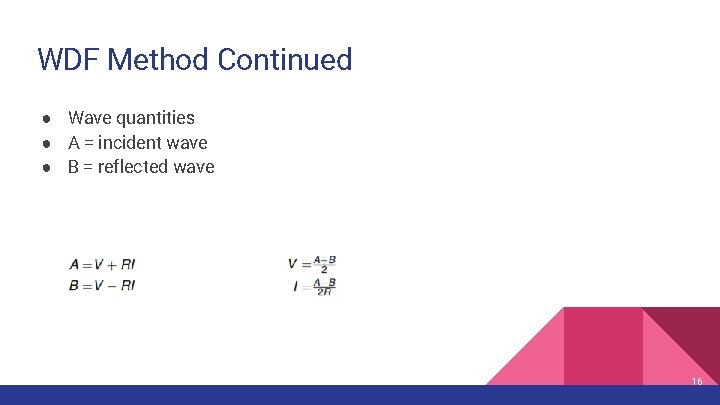

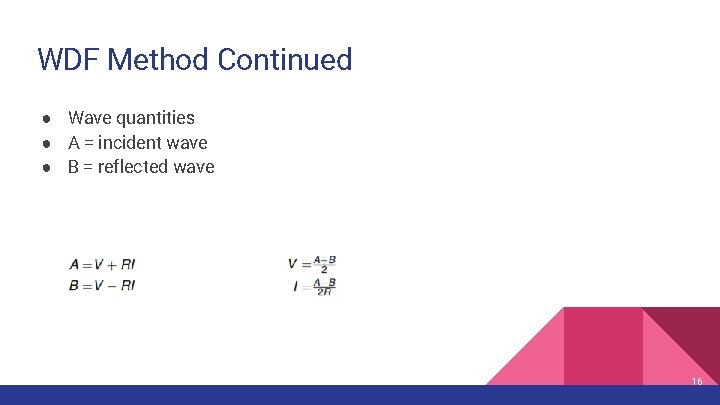

WDF Method Continued ● Wave quantities ● A = incident wave ● B = reflected wave 16

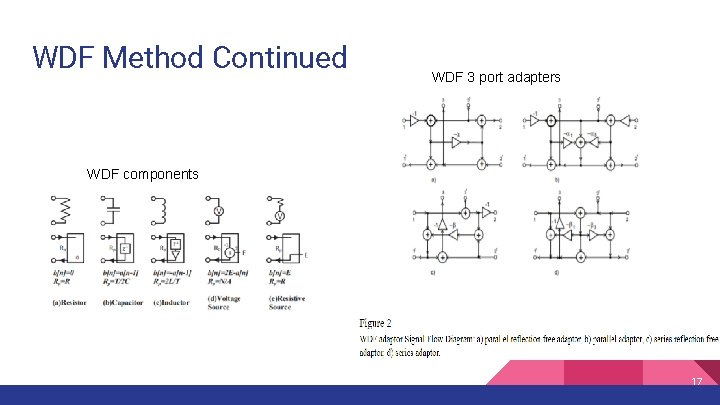

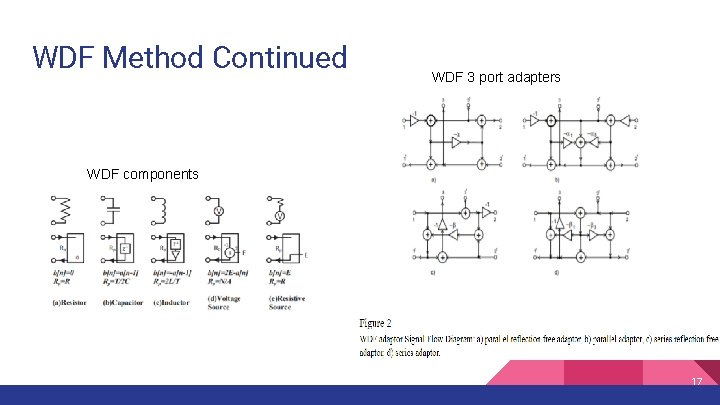

WDF Method Continued WDF 3 port adapters WDF components 17

Preliminary Results ● ● Filter banks design High order bandpass filters Difficult to implement in real-time Not a sufficient method 18

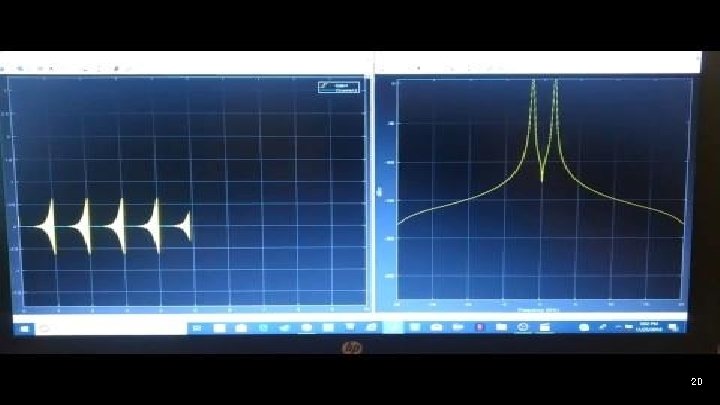

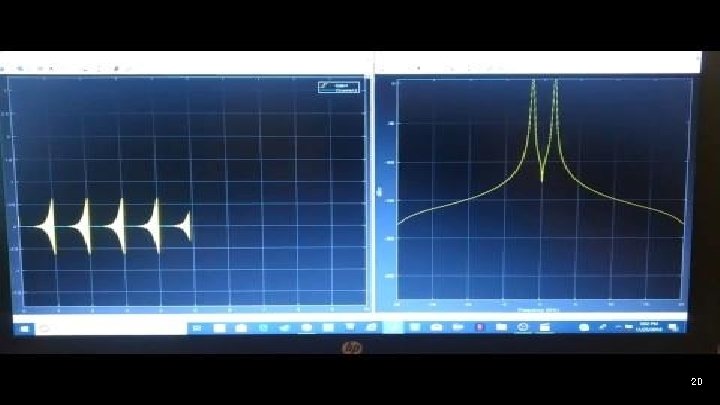

Preliminary Results ● Simulated a RC High Pass Filter ● Time Domain results using chirp signal (left) ● Frequency Domain results (right) 19

20

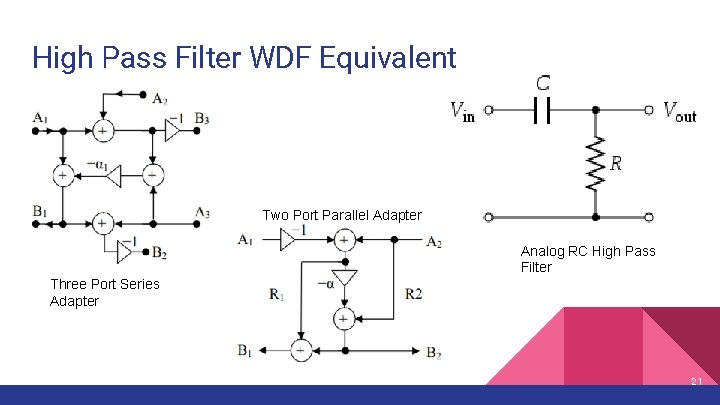

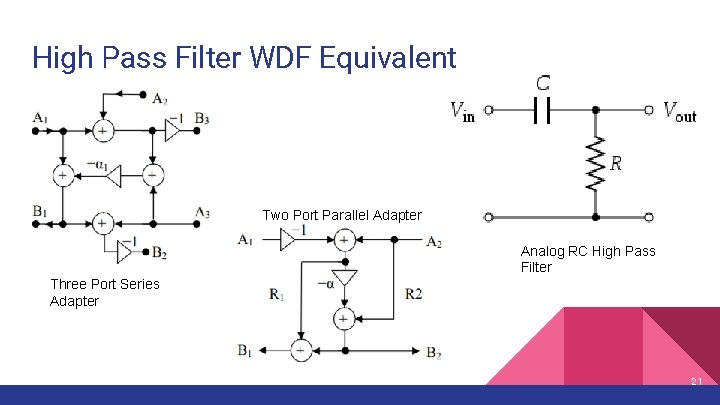

High Pass Filter WDF Equivalent Two Port Parallel Adapter Analog RC High Pass Filter Three Port Series Adapter 21

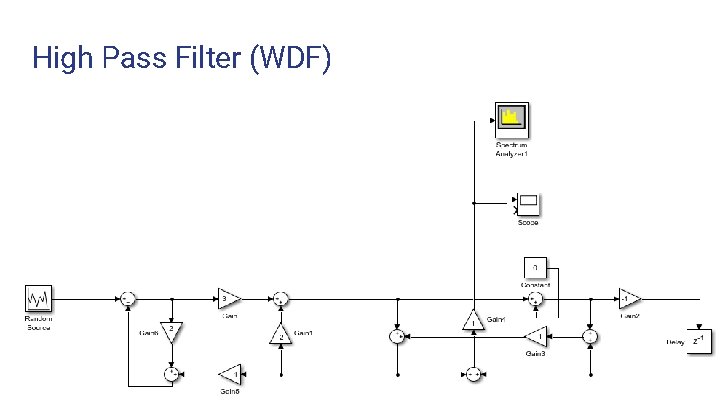

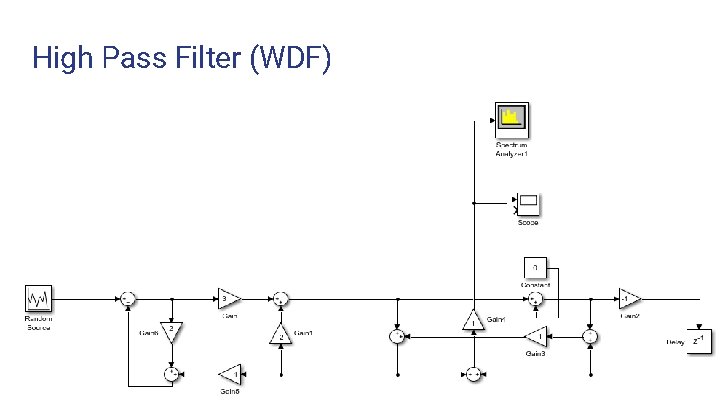

High Pass Filter (WDF) 22

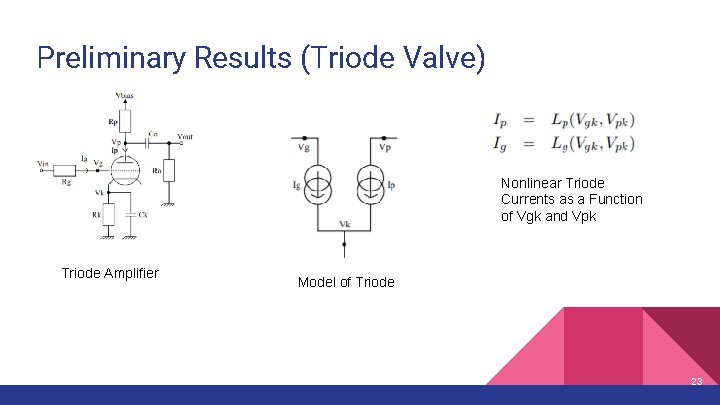

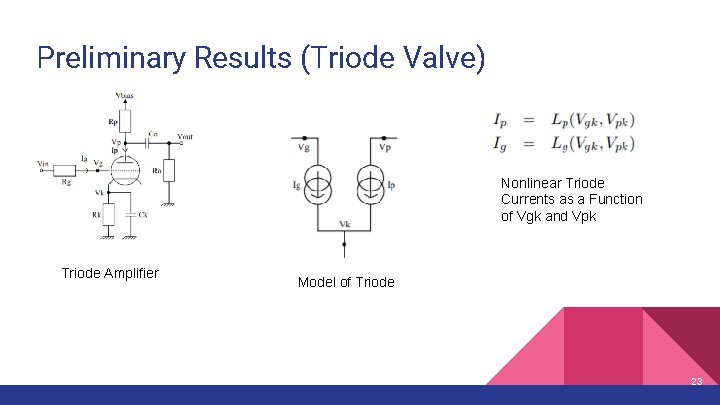

Preliminary Results (Triode Valve) Nonlinear Triode Currents as a Function of Vgk and Vpk Triode Amplifier Model of Triode 23

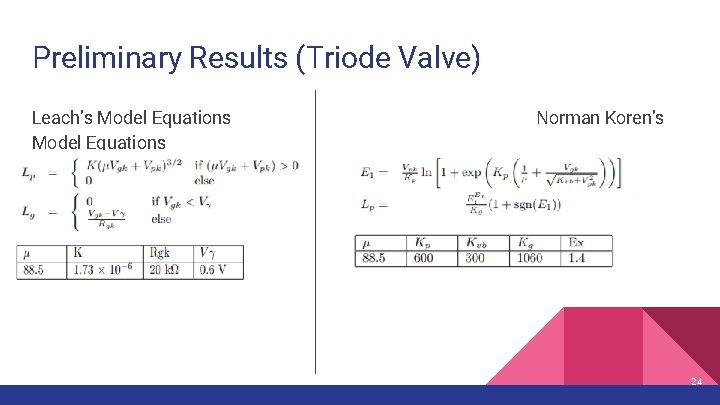

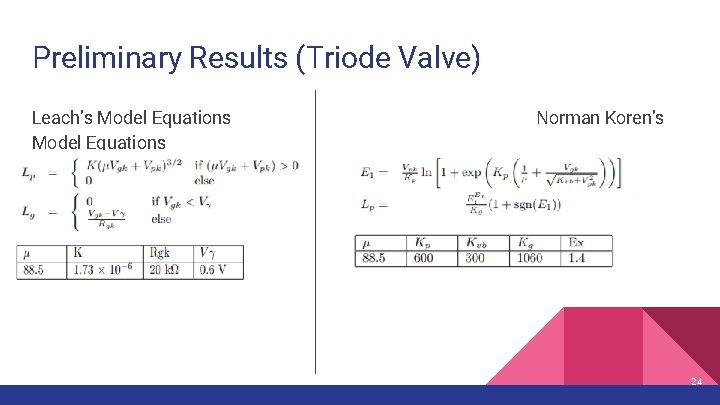

Preliminary Results (Triode Valve) Leach’s Model Equations Norman Koren’s 24

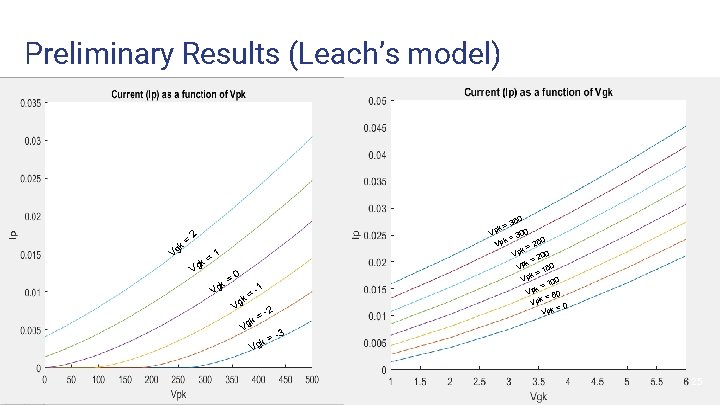

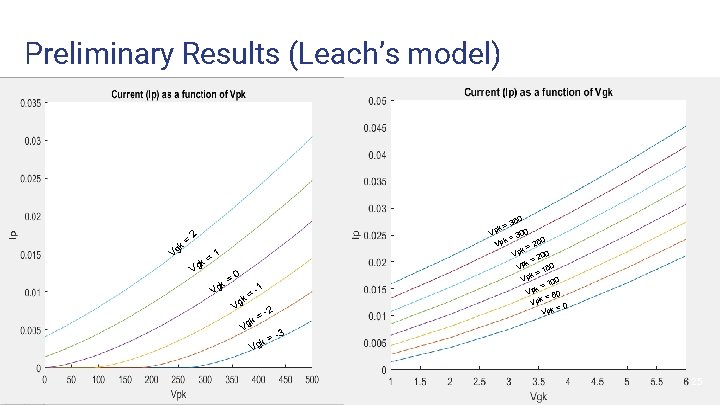

Preliminary Results (Leach’s model) V gk = 350 k= Vp 00 =3 250 Vpk k= p V 200 k= Vp 150 k= Vp 00 =1 Vpk = 50 Vpk =0 Vpk 2 k Vg = 1 k Vg =0 = gk V k Vg -1 2 =- k= Vg -3 25

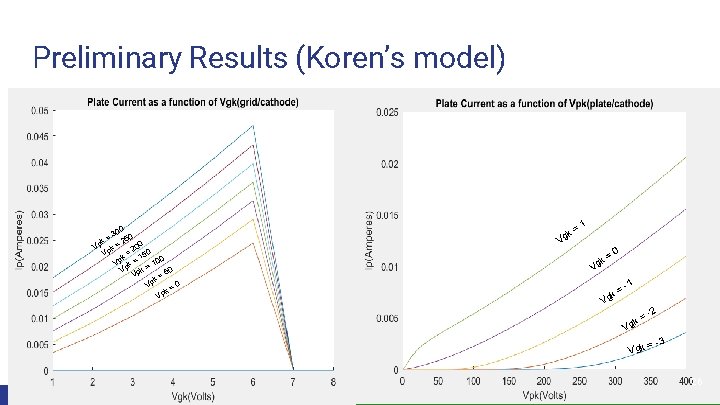

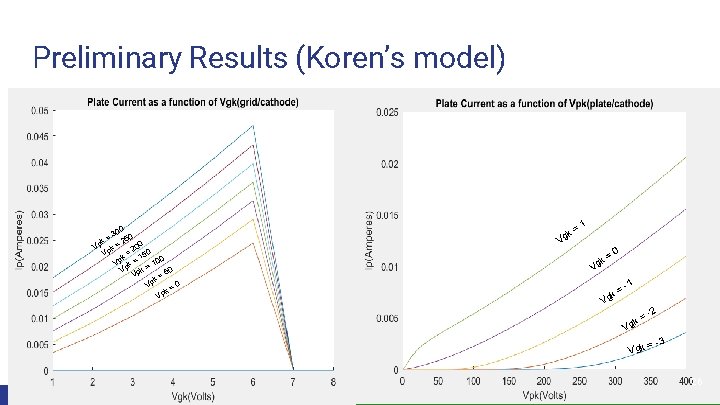

Preliminary Results (Koren’s model) 0 30 0 k = = 25 0 p V pk 20 0 V k = = 15 00 p V pk 1 V pk = 50 V k= 0 Vp k= Vp = gk 1 V =0 k Vg = gk -1 V k= Vg Vgk -2 = -3 26

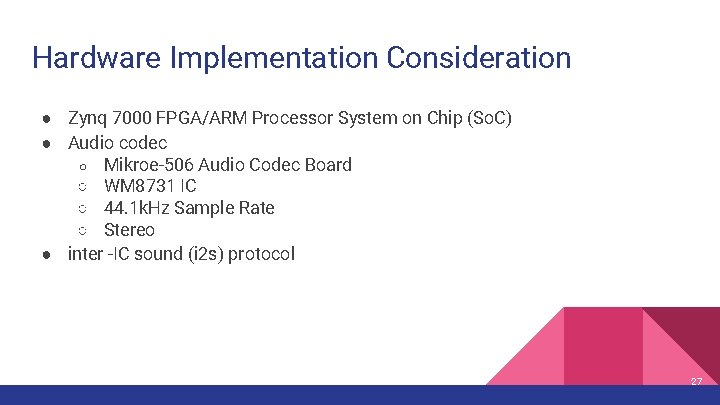

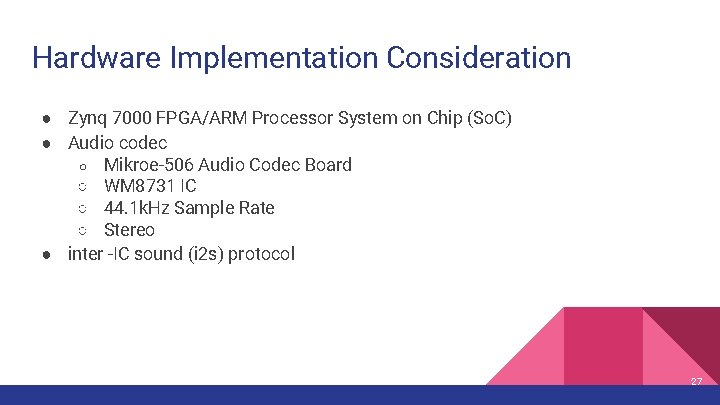

Hardware Implementation Consideration ● Zynq 7000 FPGA/ARM Processor System on Chip (So. C) ● Audio codec ○ Mikroe-506 Audio Codec Board ○ WM 8731 IC ○ 44. 1 k. Hz Sample Rate ○ Stereo ● inter -IC sound (i 2 s) protocol 27

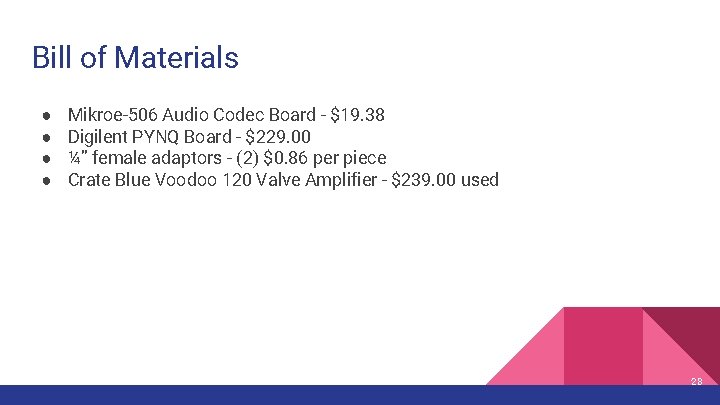

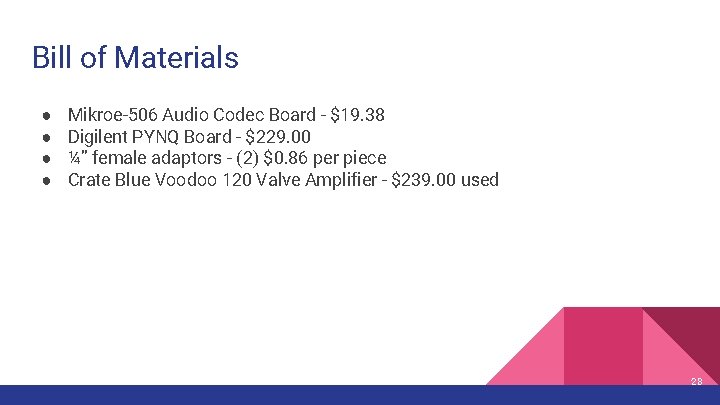

Bill of Materials ● ● Mikroe-506 Audio Codec Board - $19. 38 Digilent PYNQ Board - $229. 00 ¼” female adaptors - (2) $0. 86 per piece Crate Blue Voodoo 120 Valve Amplifier - $239. 00 used 28

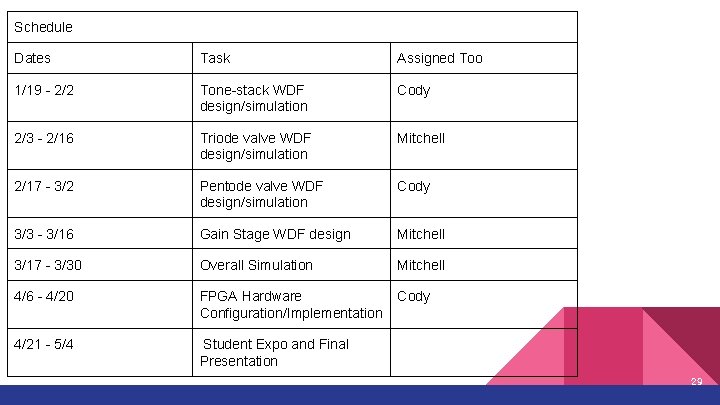

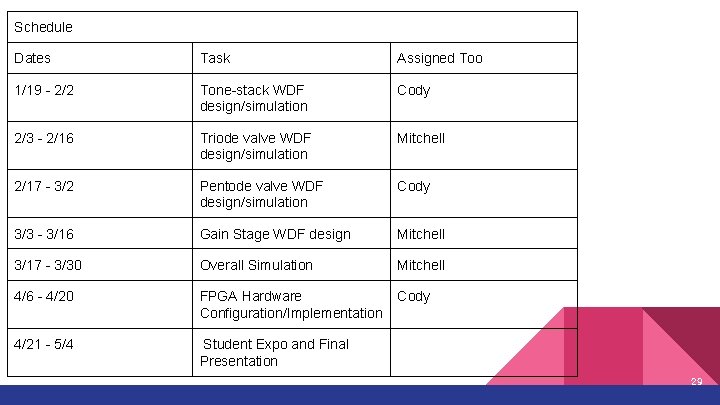

Schedule Dates Task Assigned Too 1/19 - 2/2 Tone-stack WDF design/simulation Cody 2/3 - 2/16 Triode valve WDF design/simulation Mitchell 2/17 - 3/2 Pentode valve WDF design/simulation Cody 3/3 - 3/16 Gain Stage WDF design Mitchell 3/17 - 3/30 Overall Simulation Mitchell 4/6 - 4/20 FPGA Hardware Configuration/Implementation Cody 4/21 - 5/4 Student Expo and Final Presentation 29

Conclusion ● Aims to digitally emulate Analog Circuitry of a valve amplifier using WDF ● Implement on an zynq SOC device ● Utilize i 2 s protocol 30