Digital Logic Design Dr Waseem Ikram Lecture 37

![State Definition of the Elevator Controller State Definition CONSTATE = [DOOR, MOTION, DIR]; WAIT State Definition of the Elevator Controller State Definition CONSTATE = [DOOR, MOTION, DIR]; WAIT](https://slidetodoc.com/presentation_image_h2/79604c94a6120011e010997932e6d61e/image-9.jpg)

- Slides: 23

Digital Logic & Design Dr. Waseem Ikram Lecture 37

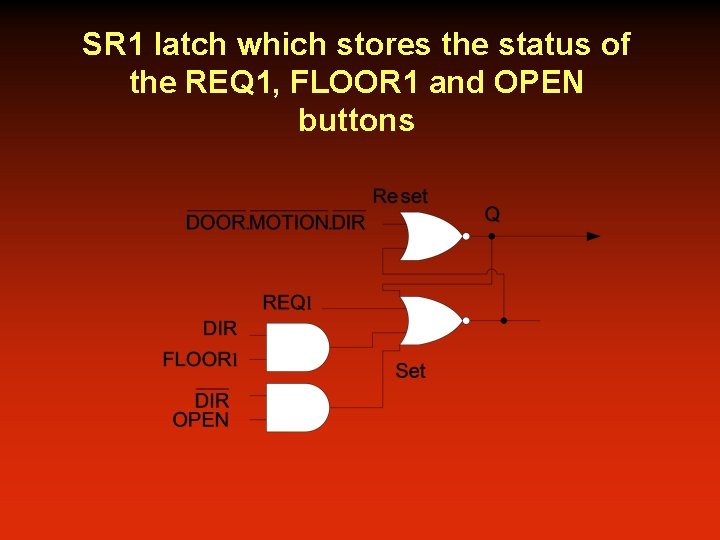

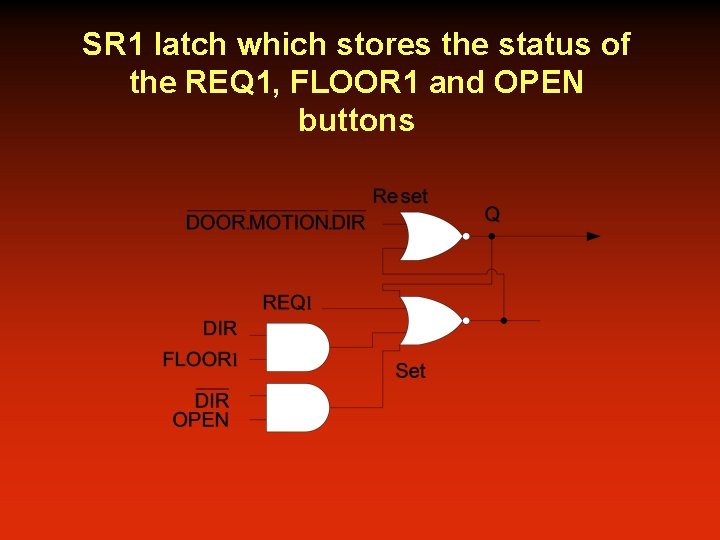

SR 1 latch which stores the status of the REQ 1, FLOOR 1 and OPEN buttons

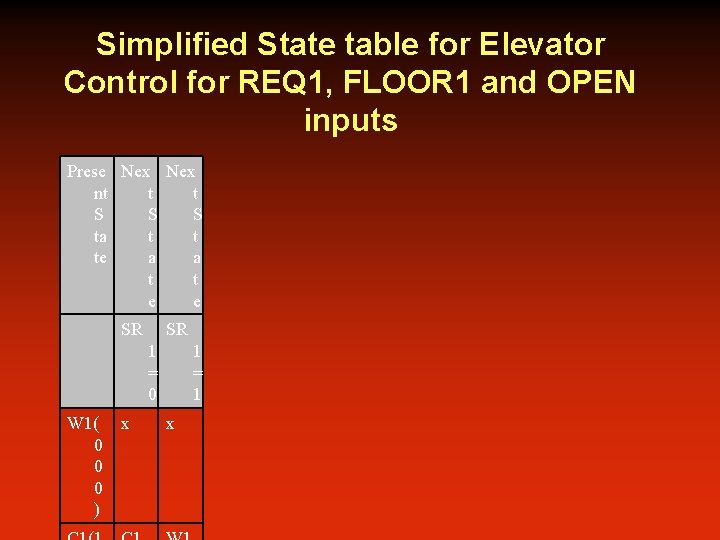

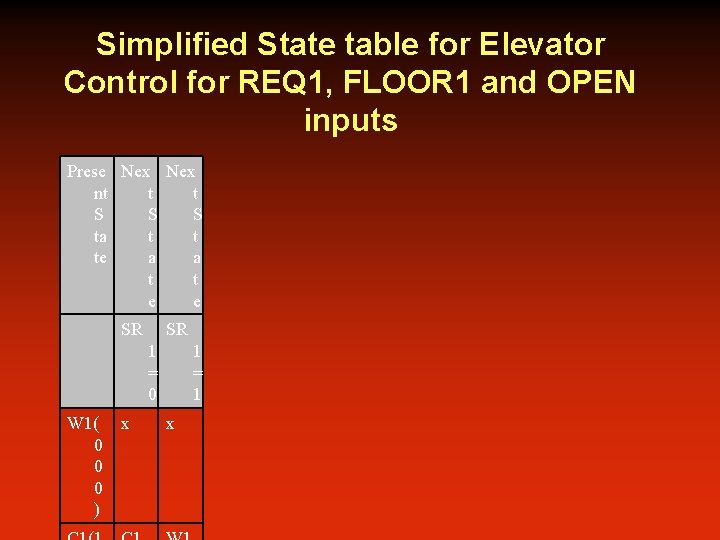

Simplified State table for Elevator Control for REQ 1, FLOOR 1 and OPEN inputs Prese Nex nt t t S S S ta t t te a a t t e e SR SR 1 = 0 W 1( 0 0 0 ) x 1 = 1 x

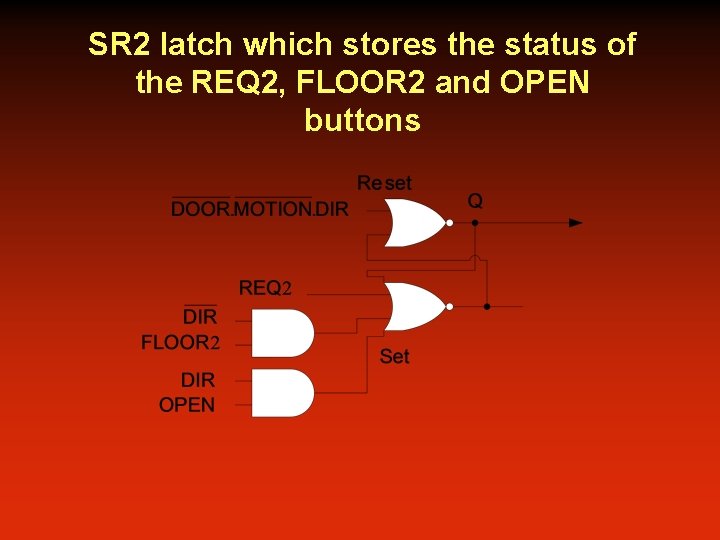

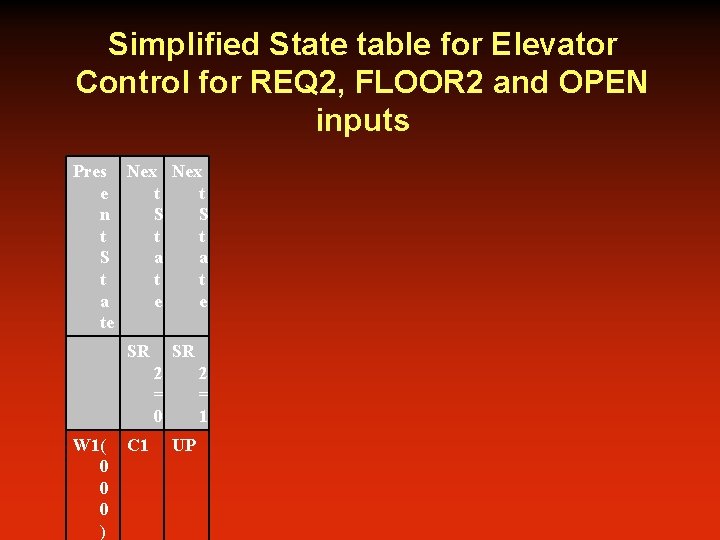

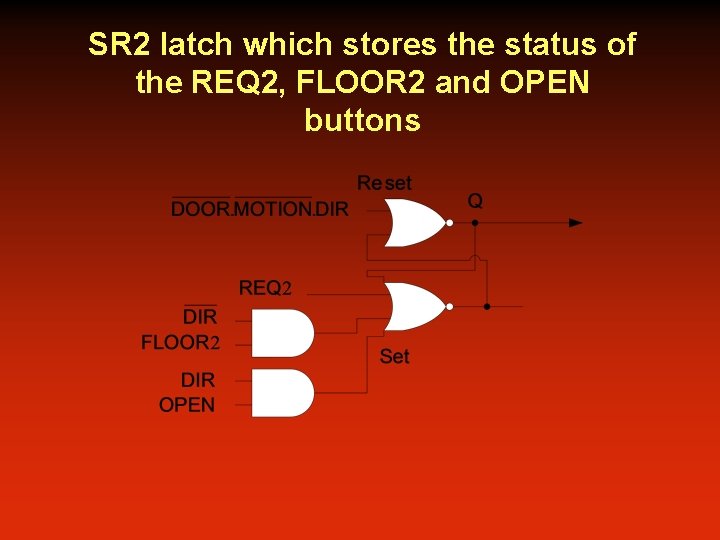

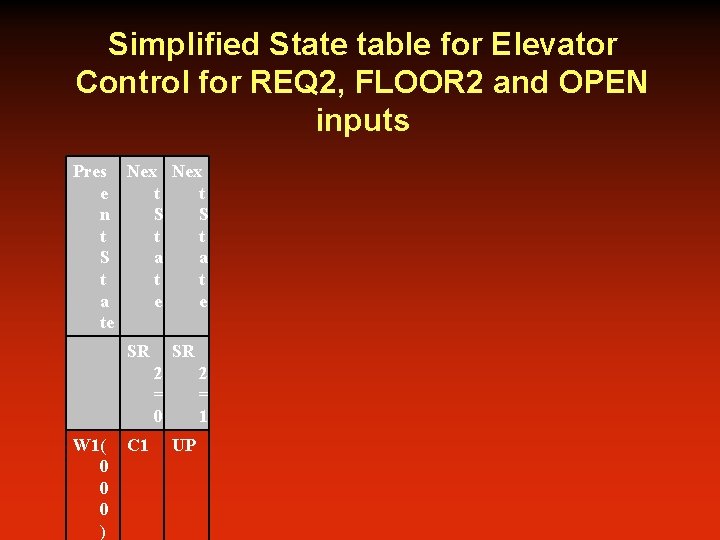

SR 2 latch which stores the status of the REQ 2, FLOOR 2 and OPEN buttons

Simplified State table for Elevator Control for REQ 2, FLOOR 2 and OPEN inputs Pres Nex e t t n S S t t t S a a t t t a e e te SR SR 2 = 0 W 1( 0 0 0 ) C 1 2 = 1 UP

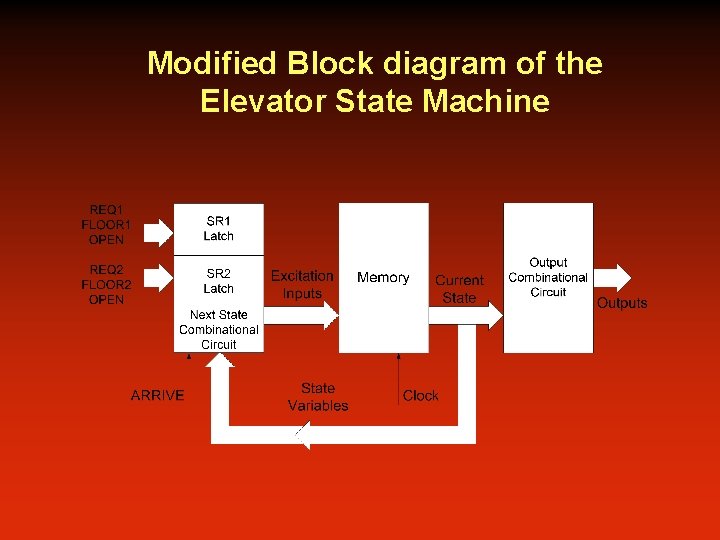

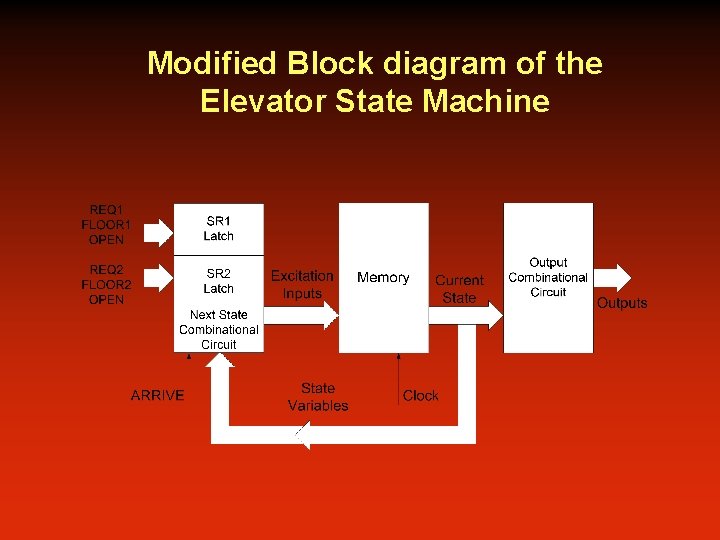

Modified Block diagram of the Elevator State Machine

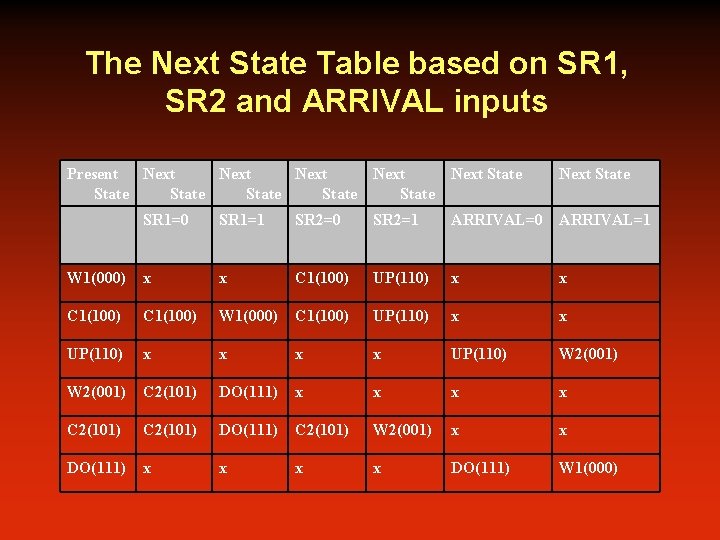

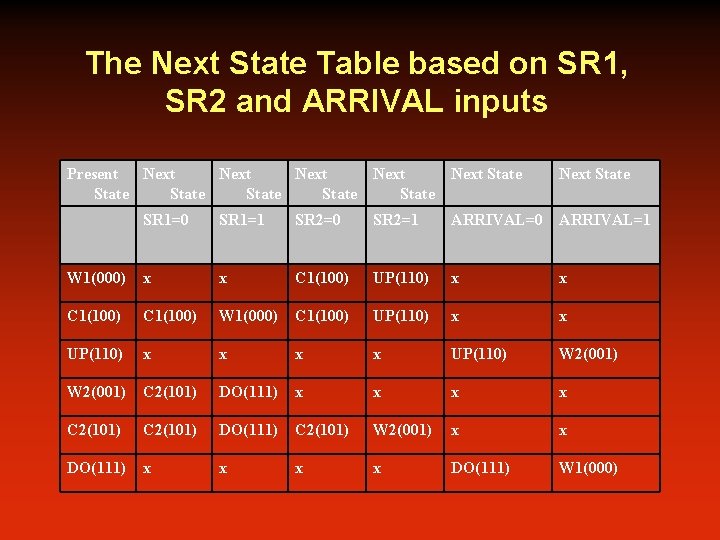

The Next State Table based on SR 1, SR 2 and ARRIVAL inputs Present Next State Next State SR 1=0 SR 1=1 SR 2=0 SR 2=1 ARRIVAL=0 ARRIVAL=1 W 1(000) x x C 1(100) UP(110) x x C 1(100) W 1(000) C 1(100) UP(110) x x x x UP(110) W 2(001) C 2(101) DO(111) x x C 2(101) DO(111) C 2(101) W 2(001) x x DO(111) W 1(000)

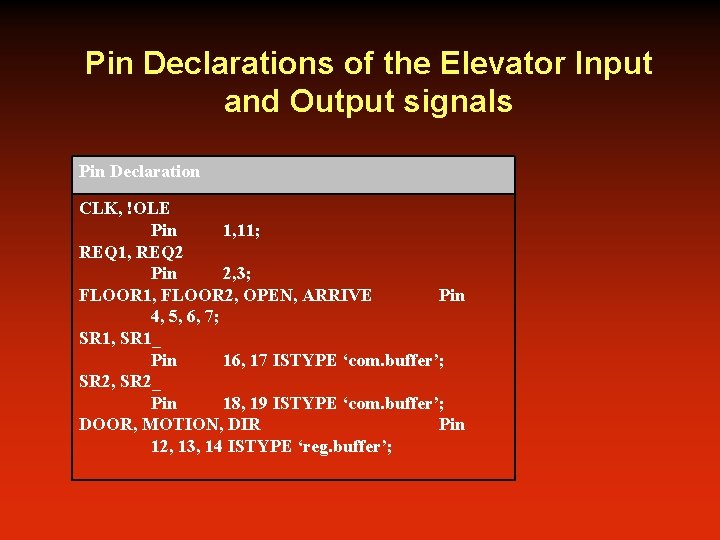

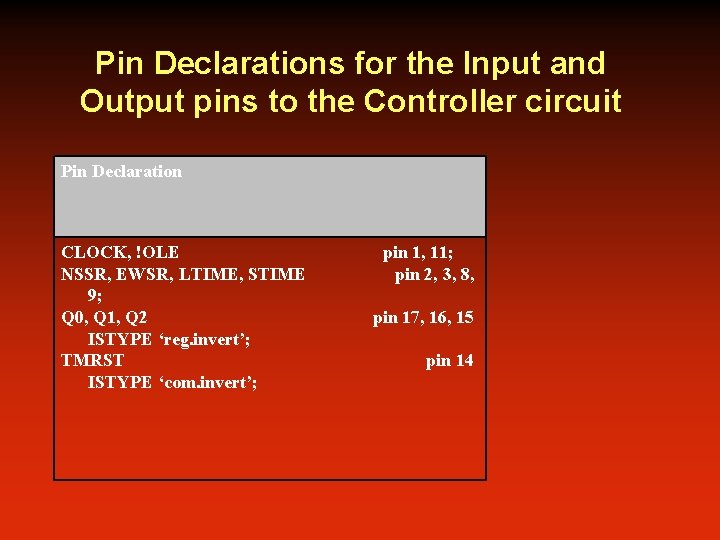

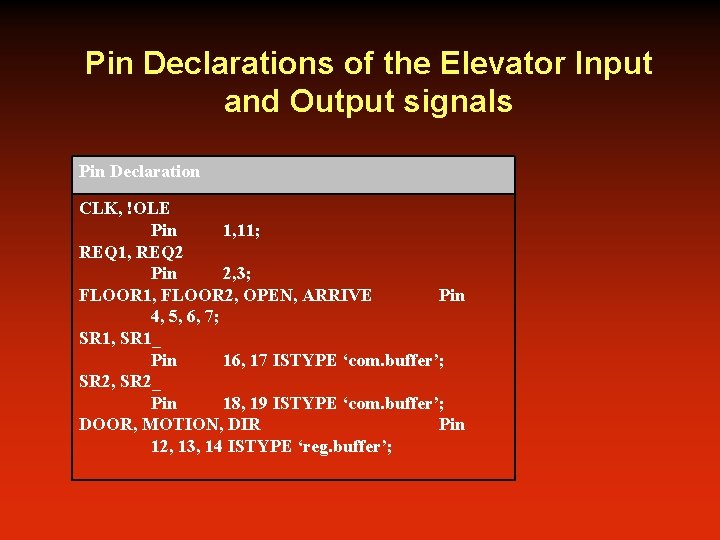

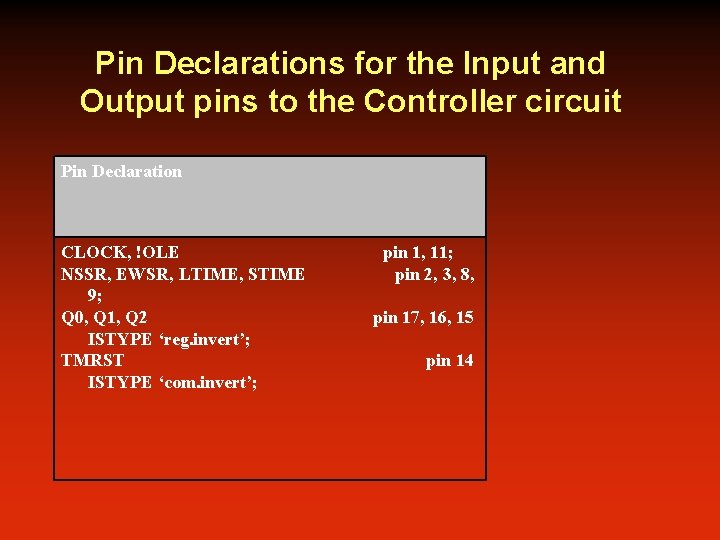

Pin Declarations of the Elevator Input and Output signals Pin Declaration CLK, !OLE Pin 1, 11; REQ 1, REQ 2 Pin 2, 3; FLOOR 1, FLOOR 2, OPEN, ARRIVE Pin 4, 5, 6, 7; SR 1, SR 1_ Pin 16, 17 ISTYPE ‘com. buffer’; SR 2, SR 2_ Pin 18, 19 ISTYPE ‘com. buffer’; DOOR, MOTION, DIR Pin 12, 13, 14 ISTYPE ‘reg. buffer’;

![State Definition of the Elevator Controller State Definition CONSTATE DOOR MOTION DIR WAIT State Definition of the Elevator Controller State Definition CONSTATE = [DOOR, MOTION, DIR]; WAIT](https://slidetodoc.com/presentation_image_h2/79604c94a6120011e010997932e6d61e/image-9.jpg)

State Definition of the Elevator Controller State Definition CONSTATE = [DOOR, MOTION, DIR]; WAIT 1 = ^B 000; CLOSE 1 = ^B 100; UP = ^B 110; WAIT 2 = ^B 001; CLOSE 2 = ^B 101; DOWN = ^B 111;

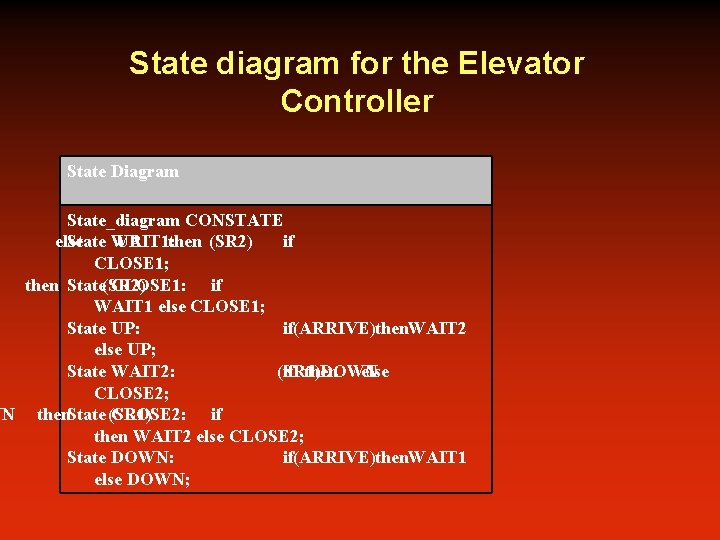

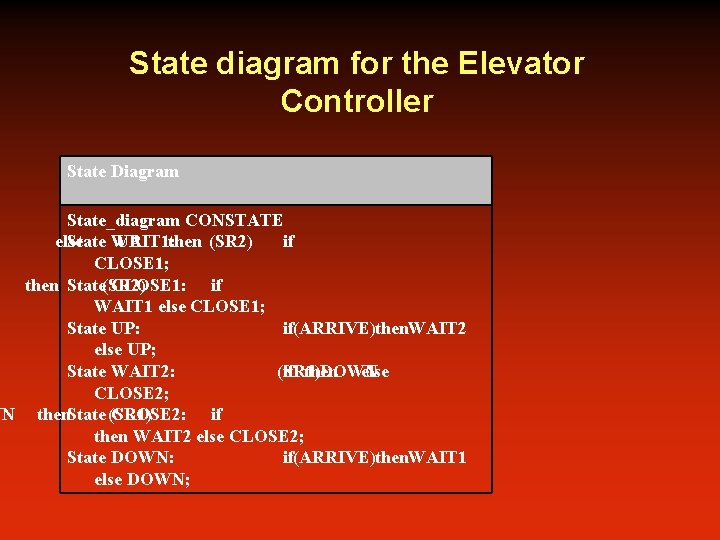

State diagram for the Elevator Controller State Diagram State_diagram CONSTATE else State WAIT 1: UP then (SR 2) if CLOSE 1; then State(SR 2) CLOSE 1: if WAIT 1 else CLOSE 1; State UP: if(ARRIVE)then. WAIT 2 else UP; State WAIT 2: (SR 1) if then DOWN else CLOSE 2; WN then. State (SR 1) CLOSE 2: if then WAIT 2 else CLOSE 2; State DOWN: if(ARRIVE)then. WAIT 1 else DOWN;

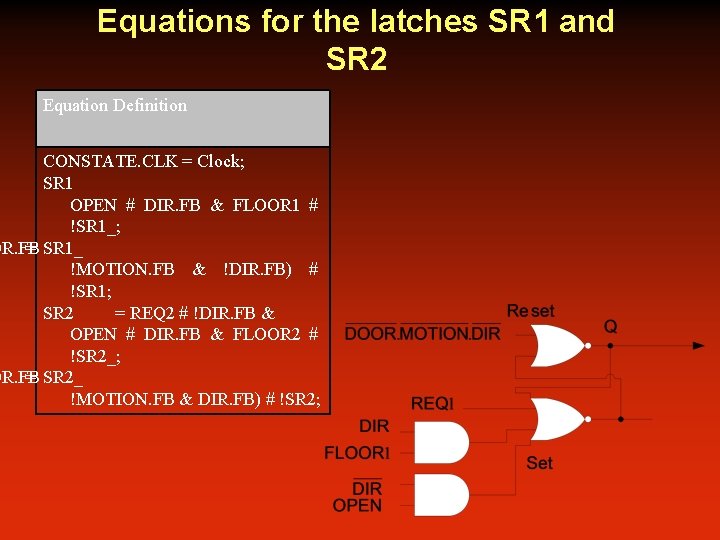

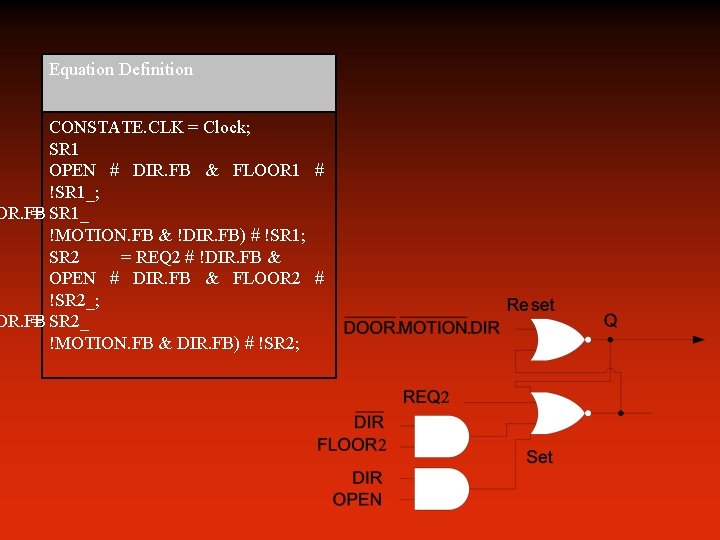

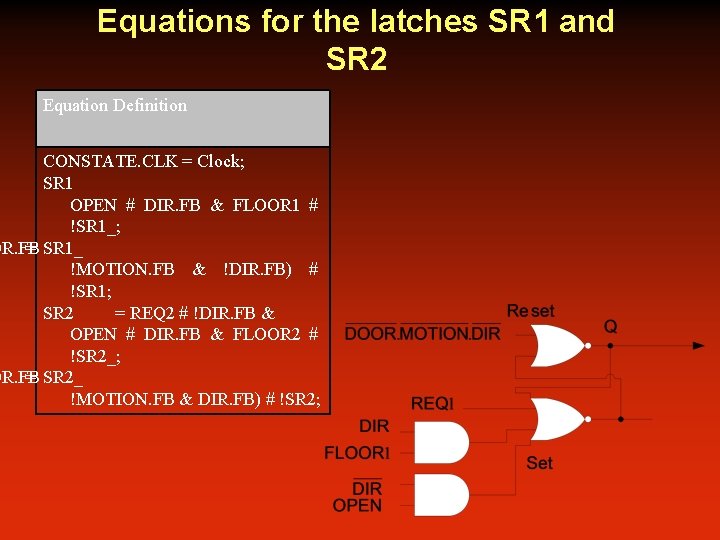

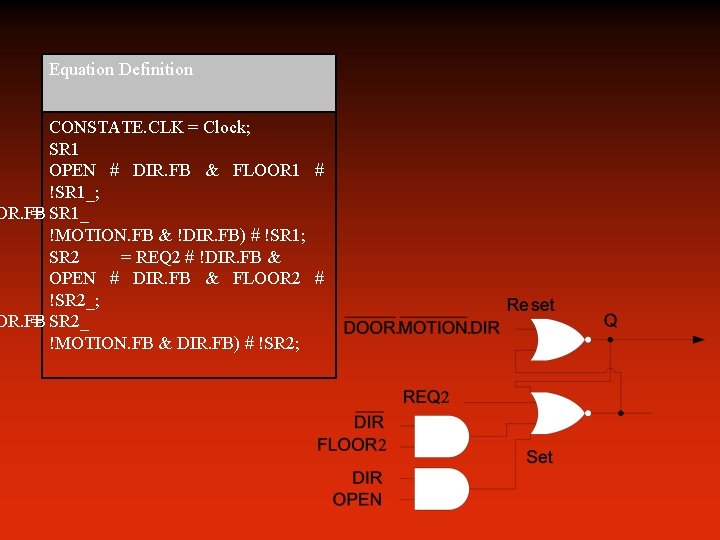

Equations for the latches SR 1 and SR 2 Equation Definition CONSTATE. CLK = Clock; SR 1 OPEN # DIR. FB & FLOOR 1 # !SR 1_; OR. FB = SR 1_ !MOTION. FB & !DIR. FB) # !SR 1; SR 2 = REQ 2 # !DIR. FB & OPEN # DIR. FB & FLOOR 2 # !SR 2_; OR. FB = SR 2_ !MOTION. FB & DIR. FB) # !SR 2;

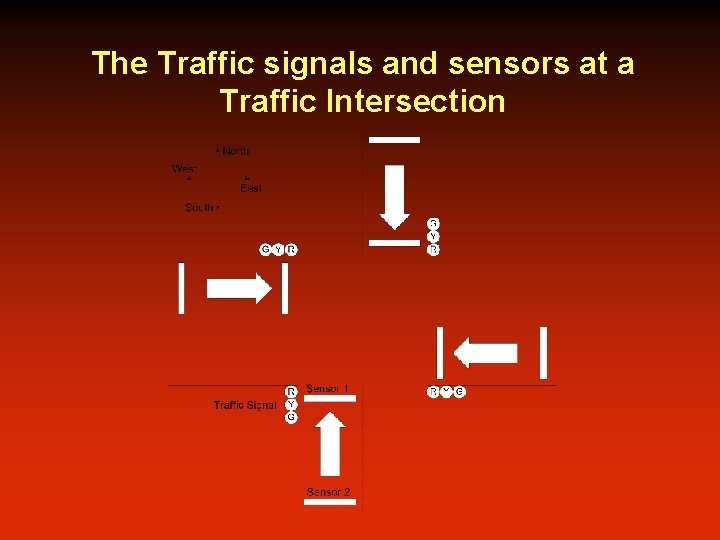

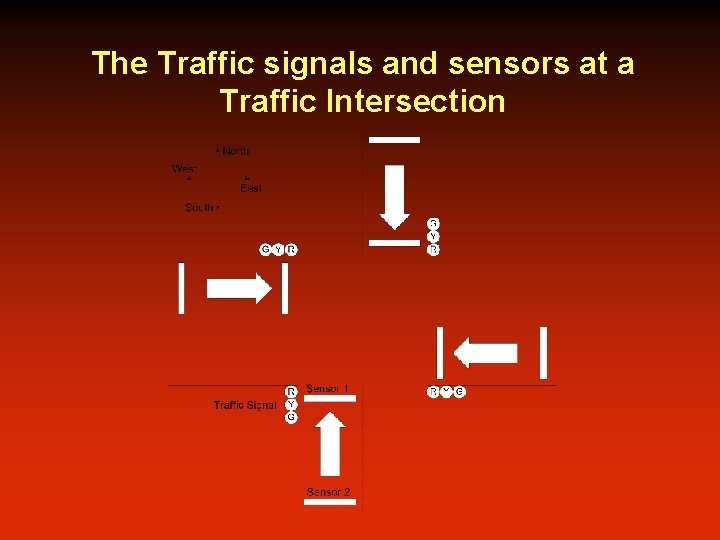

The Traffic signals and sensors at a Traffic Intersection

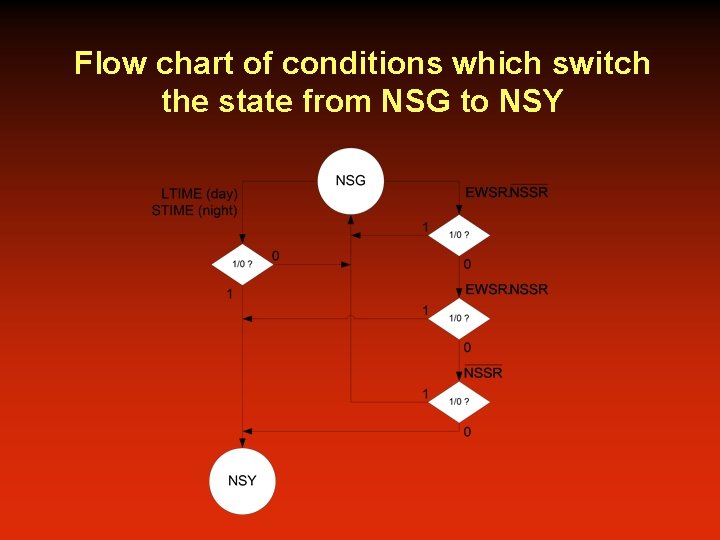

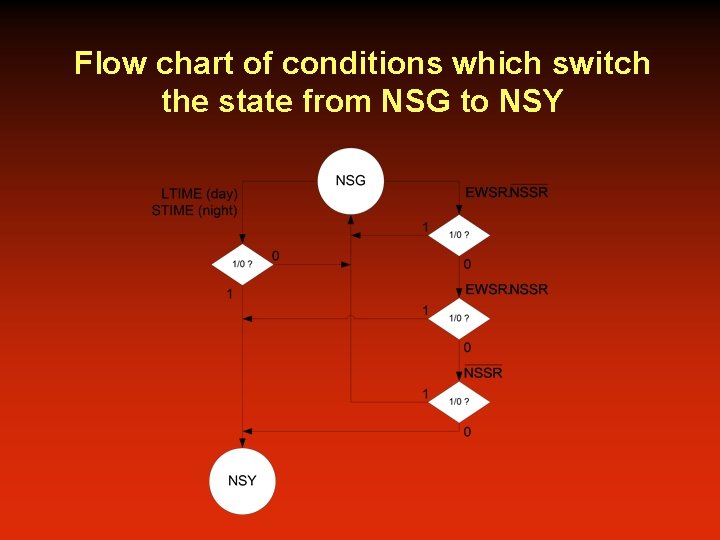

Flow chart of conditions which switch the state from NSG to NSY

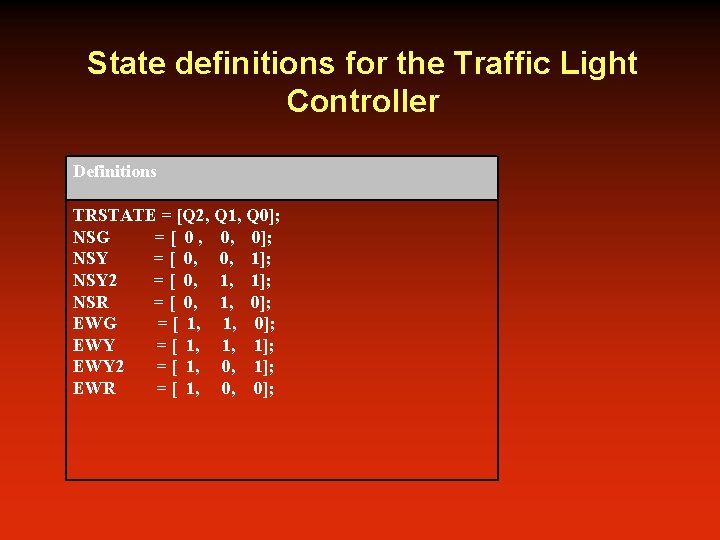

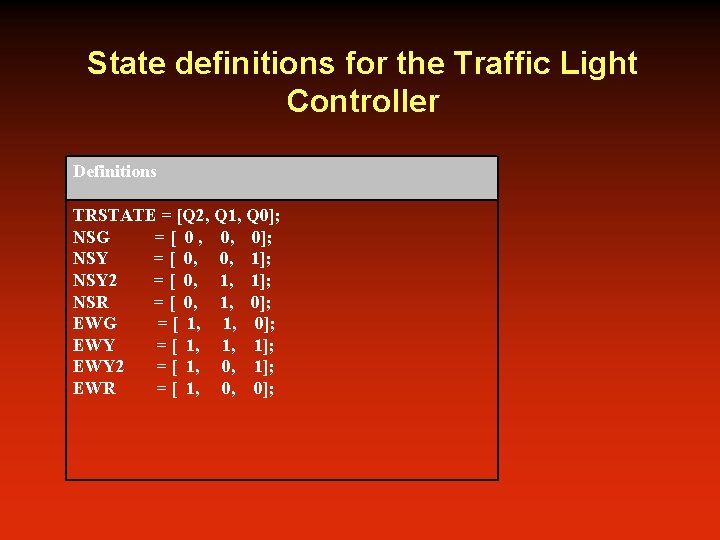

Pin Declarations for the Input and Output pins to the Controller circuit Pin Declaration CLOCK, !OLE NSSR, EWSR, LTIME, STIME 9; Q 0, Q 1, Q 2 ISTYPE ‘reg. invert’; TMRST ISTYPE ‘com. invert’; pin 1, 11; pin 2, 3, 8, pin 17, 16, 15 pin 14

State definitions for the Traffic Light Controller Definitions TRSTATE = [Q 2, Q 1, Q 0]; NSG = [ 0 , 0, 0]; NSY = [ 0, 0, 1]; NSY 2 = [ 0, 1, 1]; NSR = [ 0, 1, 0]; EWG = [ 1, 1, 0]; EWY = [ 1, 1, 1]; EWY 2 = [ 1, 0, 1]; EWR = [ 1, 0, 0];

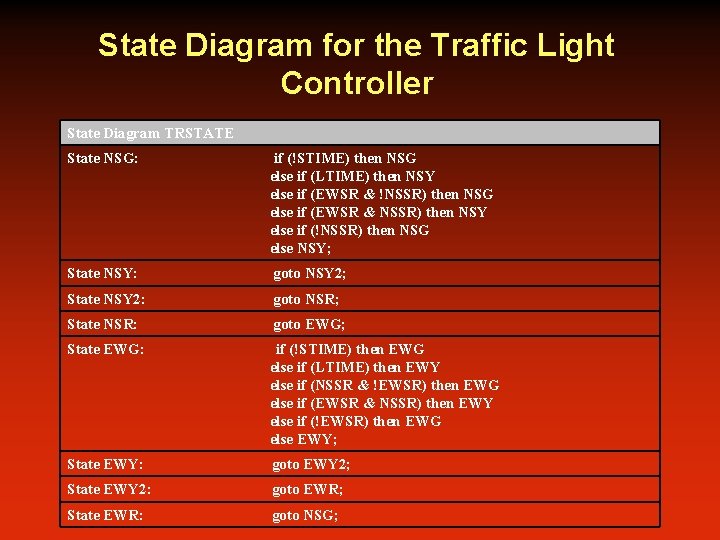

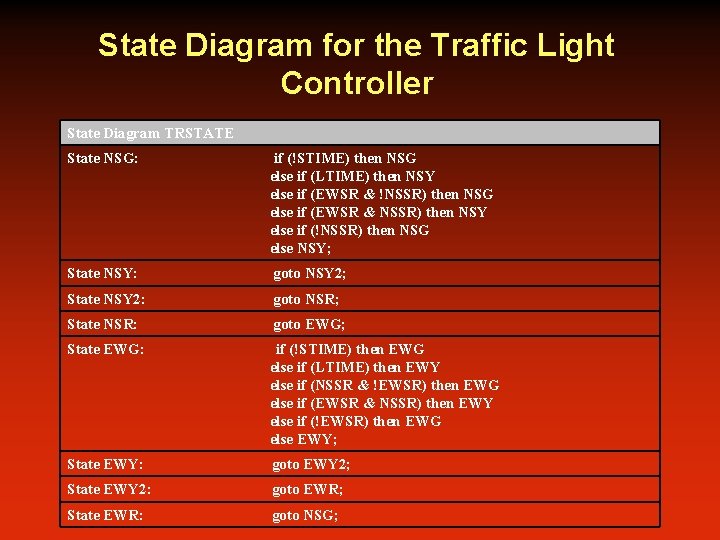

State Diagram for the Traffic Light Controller State Diagram TRSTATE State NSG: if (!STIME) then NSG else if (LTIME) then NSY else if (EWSR & !NSSR) then NSG else if (EWSR & NSSR) then NSY else if (!NSSR) then NSG else NSY; State NSY: goto NSY 2; State NSY 2: goto NSR; State NSR: goto EWG; State EWG: if (!STIME) then EWG else if (LTIME) then EWY else if (NSSR & !EWSR) then EWG else if (EWSR & NSSR) then EWY else if (!EWSR) then EWG else EWY; State EWY: goto EWY 2; State EWY 2: goto EWR; State EWR: goto NSG;

Equation Definition CONSTATE. CLK = Clock; SR 1 OPEN # DIR. FB & FLOOR 1 # !SR 1_; OR. FB = SR 1_ !MOTION. FB & !DIR. FB) # !SR 1; SR 2 = REQ 2 # !DIR. FB & OPEN # DIR. FB & FLOOR 2 # !SR 2_; OR. FB = SR 2_ !MOTION. FB & DIR. FB) # !SR 2;

Recap

Elevator Controller

Elevator Controller PLD Programming

Traffic Light Controller

Traffic Light Controller PLD Programming

Digital Logic Design Lecture 37