Digital Logic Design Dr Waseem Ikram Lecture 13

- Slides: 32

Digital Logic & Design Dr. Waseem Ikram Lecture 13

Recap n n Functions having multiple outputs Comparator Quine-Mc. Cluskey Method (two variations) Odd-Prime Number checker circuit

Odd Prime Number (table 1) Minterm A B C D E 1 0 0 1 3 0 0 0 1 1 5 0 0 1 7 0 0 1 11 0 1 1 13 0 1 17 1 0 0 0 1 19 1 0 0 1 1 23 1 0 1 1 1 29 1 1 1 0 1 31 1 1

Odd Prime Number (table 2) Minterm A B C D E used 1 0 0 1 3 0 0 0 1 1 5 0 0 1 17 1 0 0 0 1 7 0 0 1 11 0 1 1 13 0 1 19 1 0 0 1 1 23 1 0 1 1 1 29 1 1 1 0 1 31 1 1

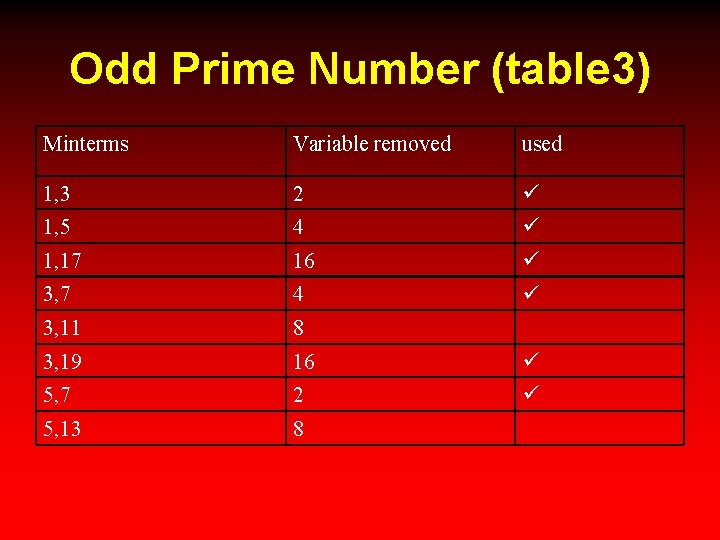

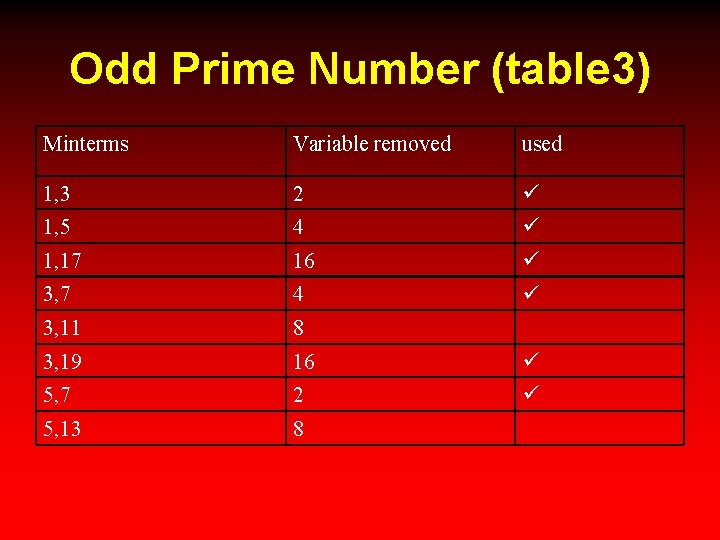

Odd Prime Number (table 3) Minterms Variable removed used 1, 3 2 1, 5 4 1, 17 16 3, 7 4 3, 11 8 3, 19 16 5, 7 2 5, 13 8

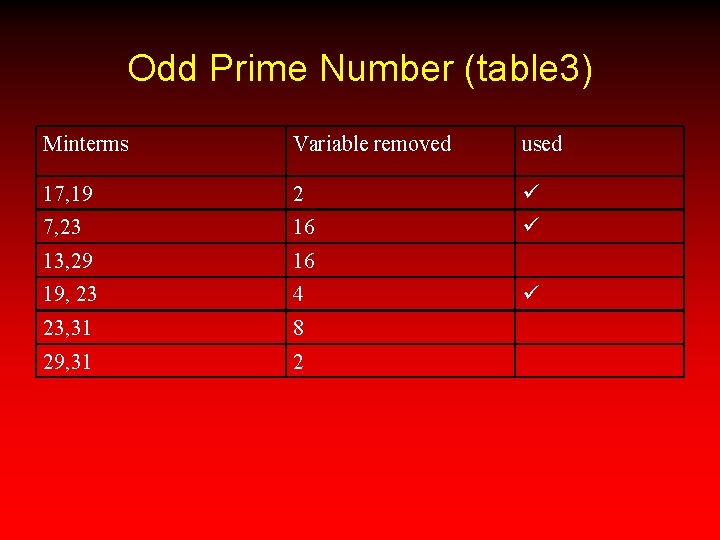

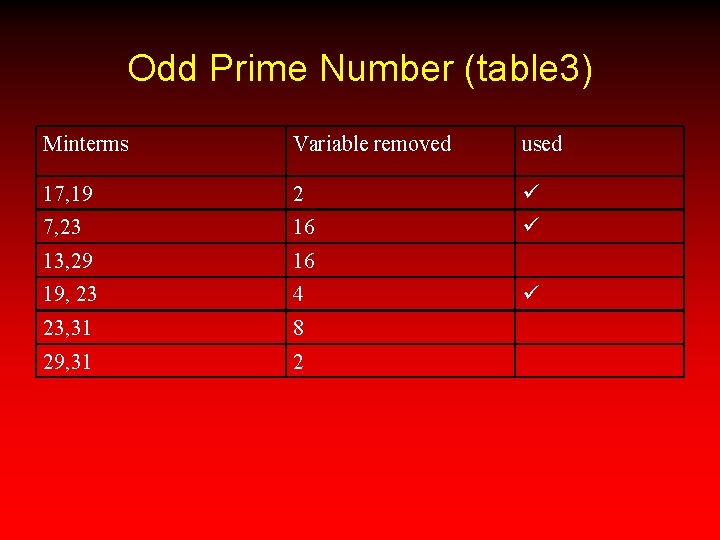

Odd Prime Number (table 3) Minterms Variable removed used 17, 19 2 7, 23 16 13, 29 16 19, 23 4 23, 31 8 29, 31 2

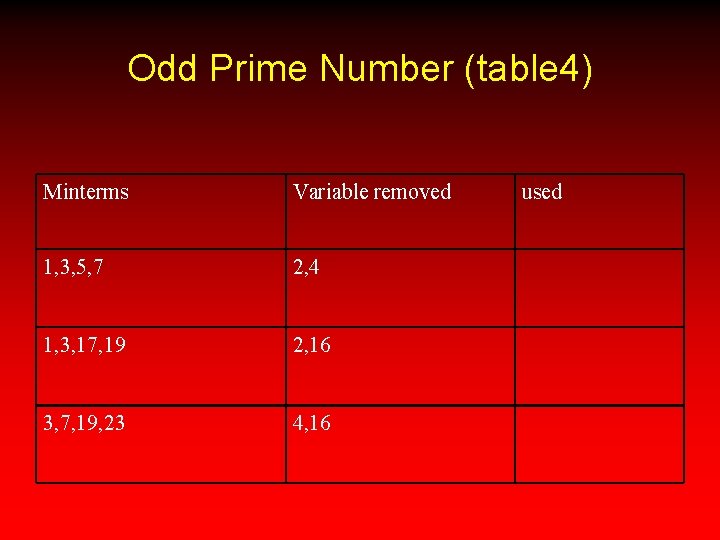

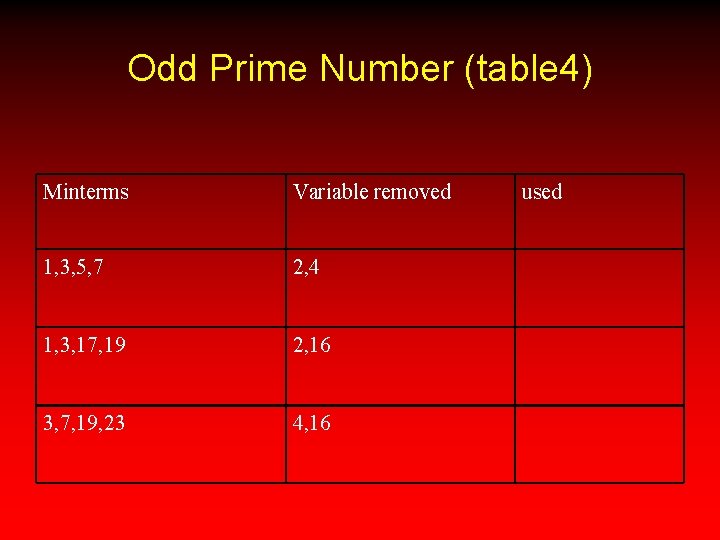

Odd Prime Number (table 4) Minterms Variable removed 1, 3, 5, 7 2, 4 1, 3, 17, 19 2, 16 3, 7, 19, 23 4, 16 used

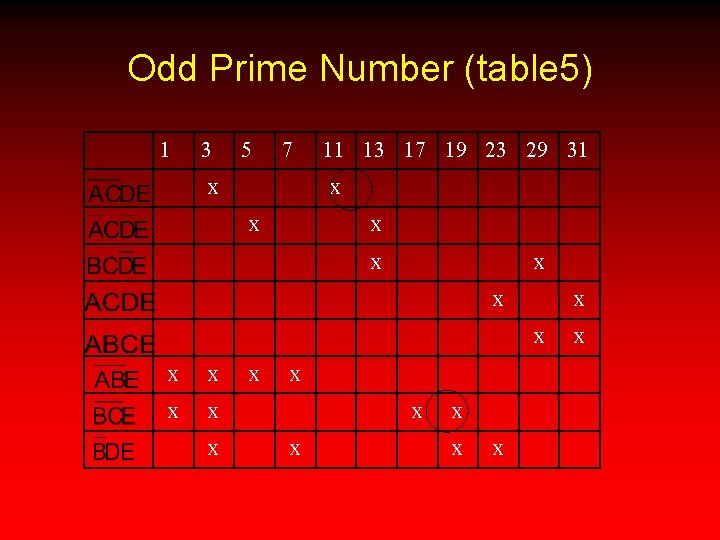

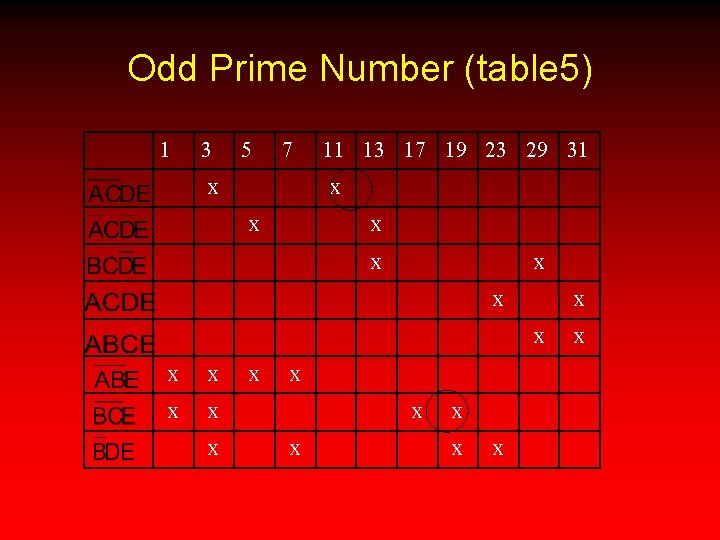

Odd Prime Number (table 5) 1 3 5 7 x 11 13 17 19 23 29 31 x x x x x x

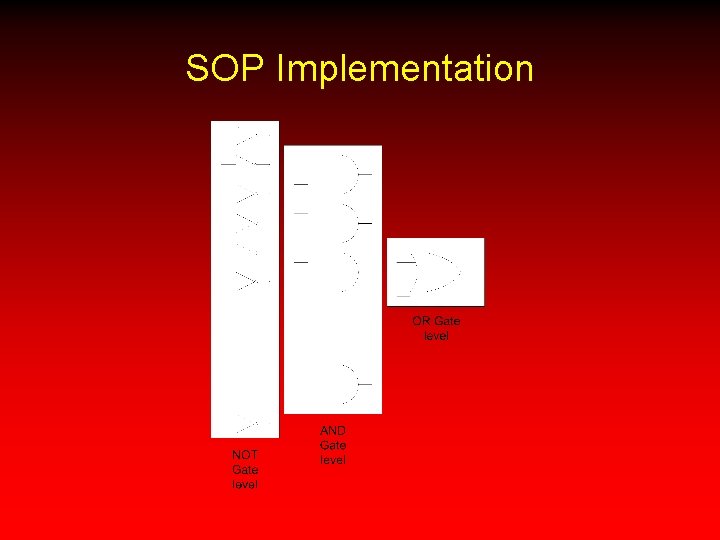

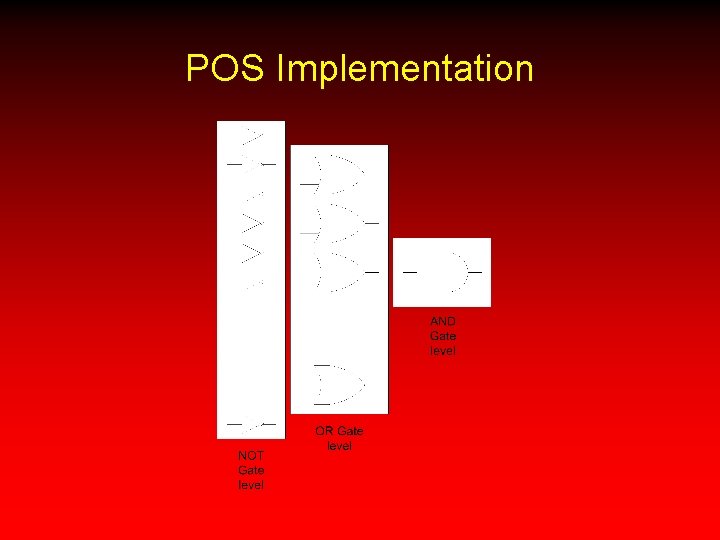

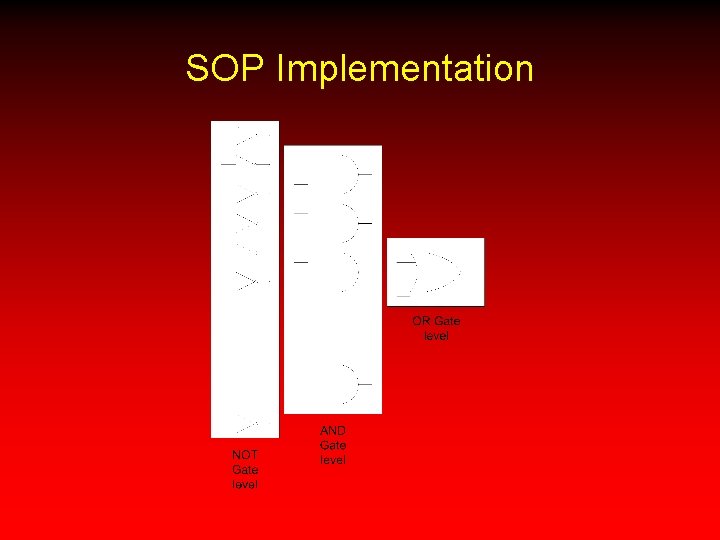

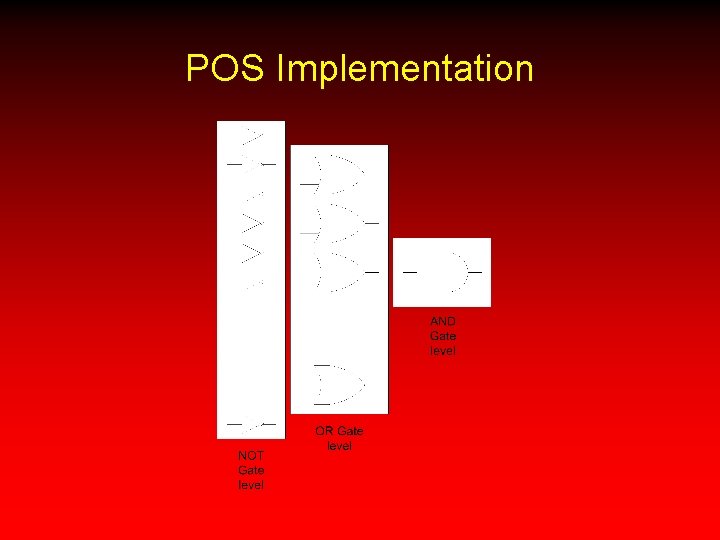

Combinational Logic n n Implementation of SOP using AND-OR Implementation of POS using OR-AND

SOP Implementation

POS Implementation

Design and Implementation of Digital Circuits n n n Function Table Simplification of Expression Implementation

Adjacent 1 s Detector Circuit n SOP Implementation n Directly from function table Simplified implementation Implementation using NAND gates

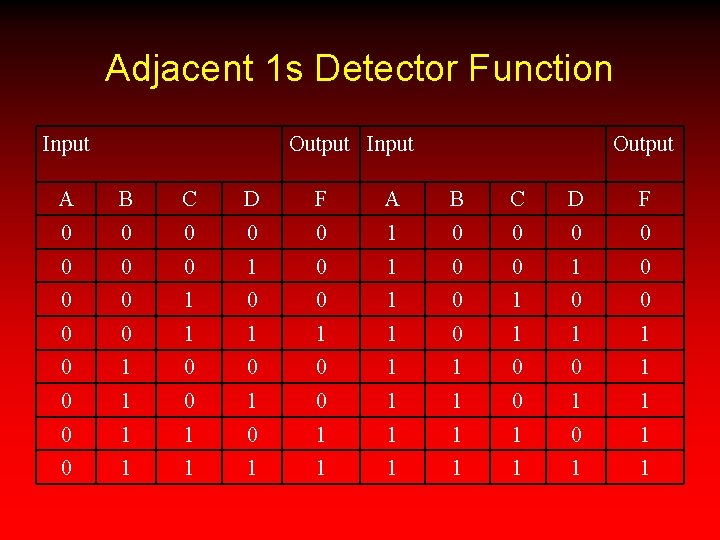

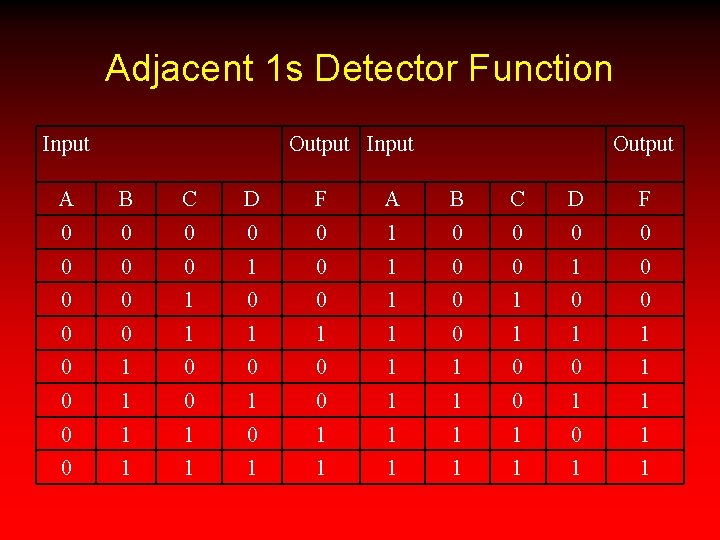

Adjacent 1 s Detector Function Input Output A B C D F 0 0 0 1 0 0 1 0 0 1 1 1 0 0 0 1 1 0 0 1 0 1 1 0 1 1 1 1 1

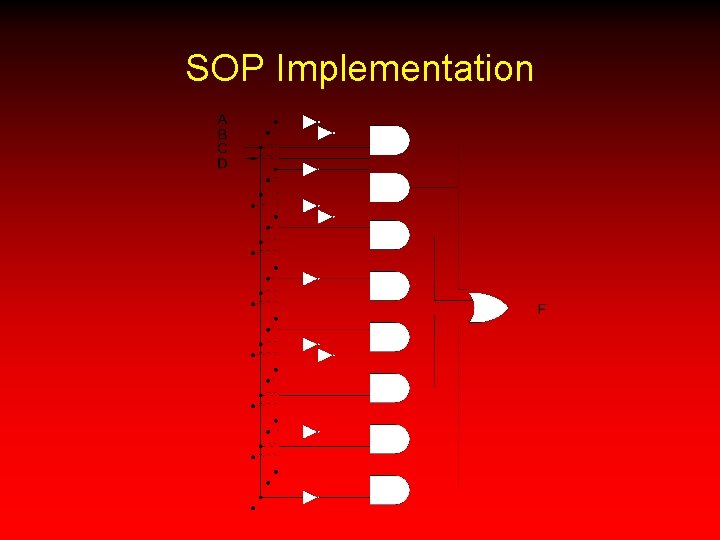

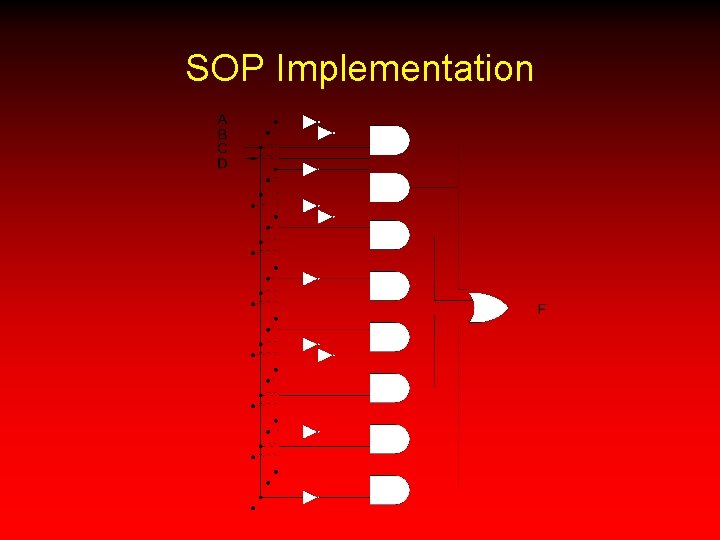

SOP Implementation

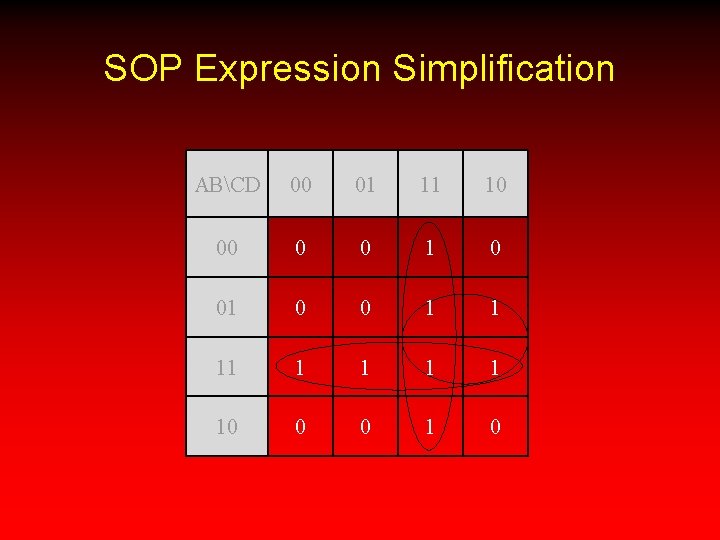

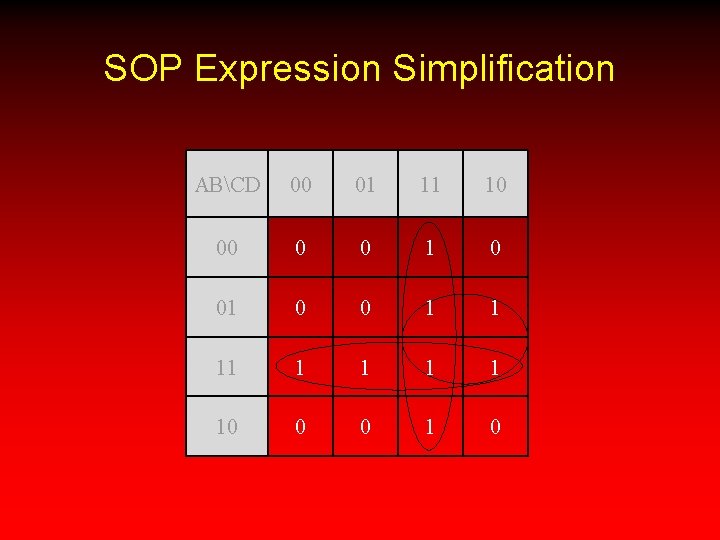

SOP Expression Simplification ABCD 00 01 11 10 00 0 0 1 1 1 1 1 10 0 0 1 0

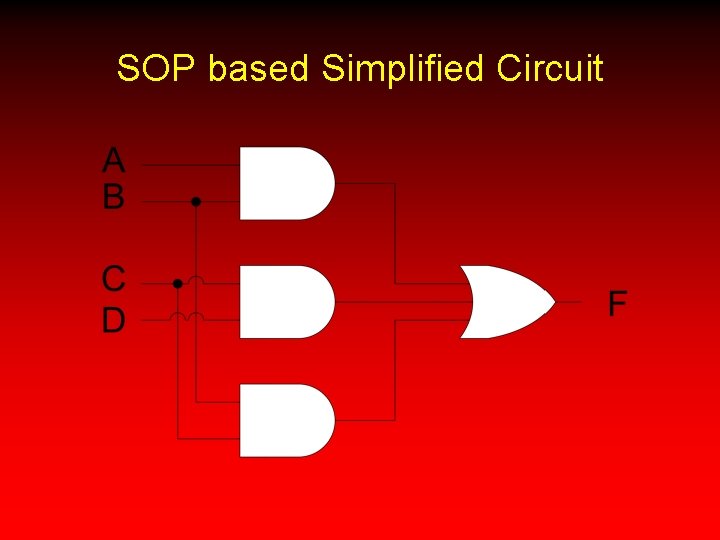

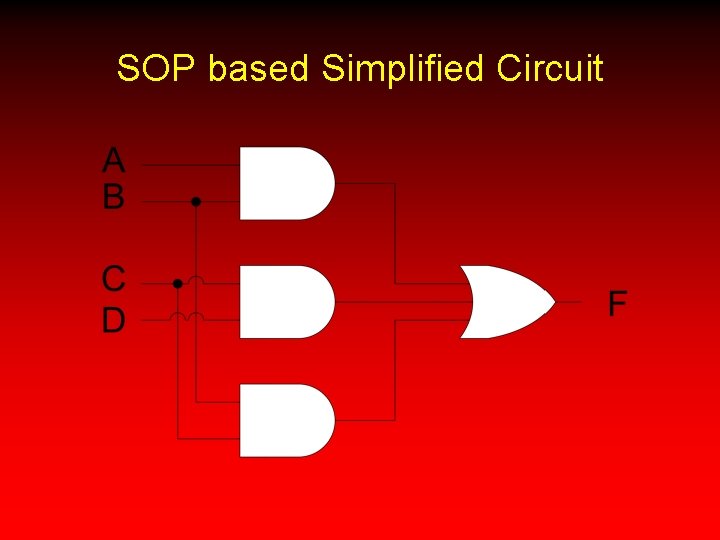

SOP based Simplified Circuit

NAND based Implementation

Adjacent 1 s Detector Circuit n POS Implementation n Directly from function table Simplified Implementation using NOR Gates

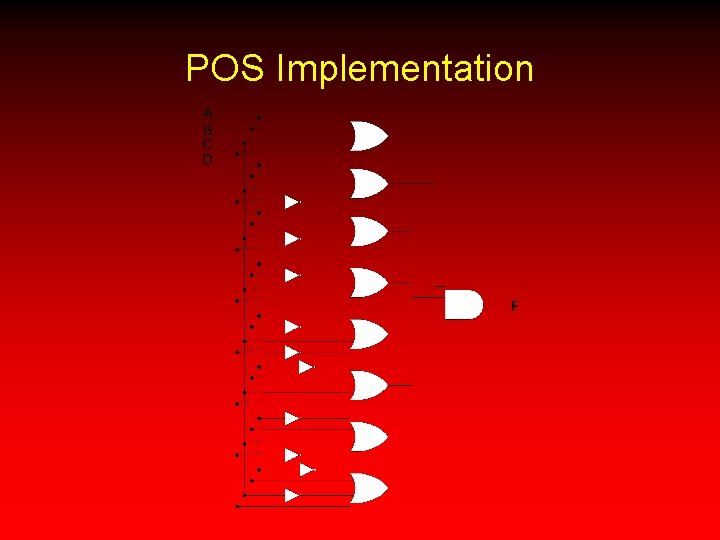

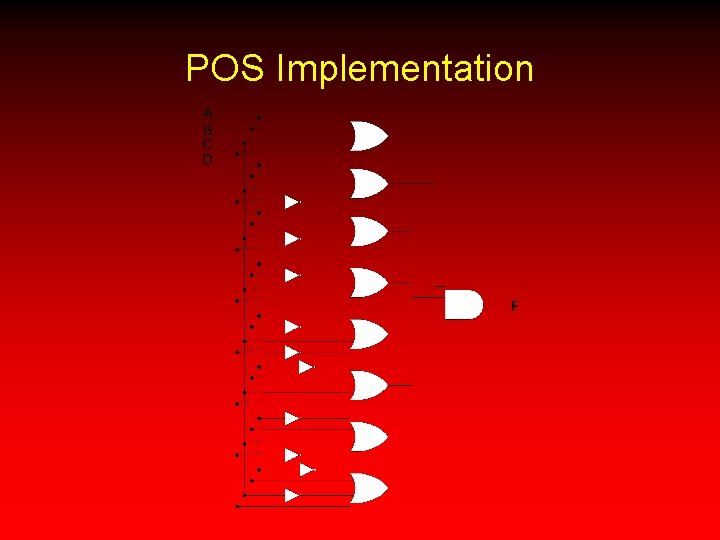

POS Implementation

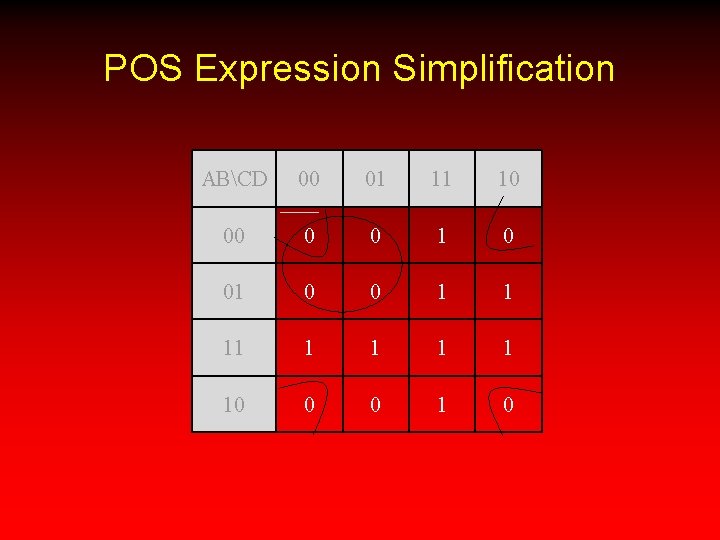

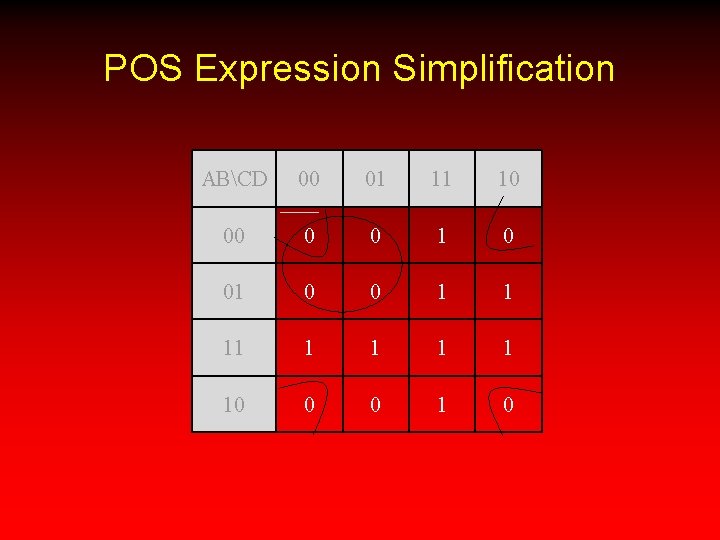

POS Expression Simplification ABCD 00 01 11 10 00 0 0 1 1 1 1 1 10 0 0 1 0

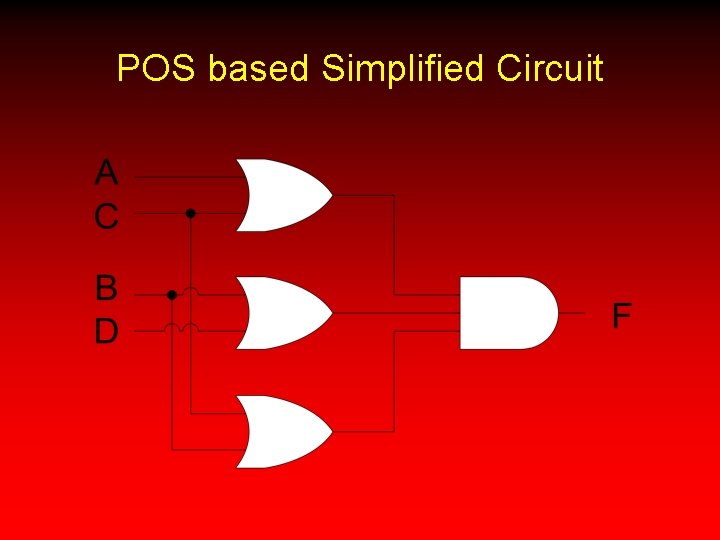

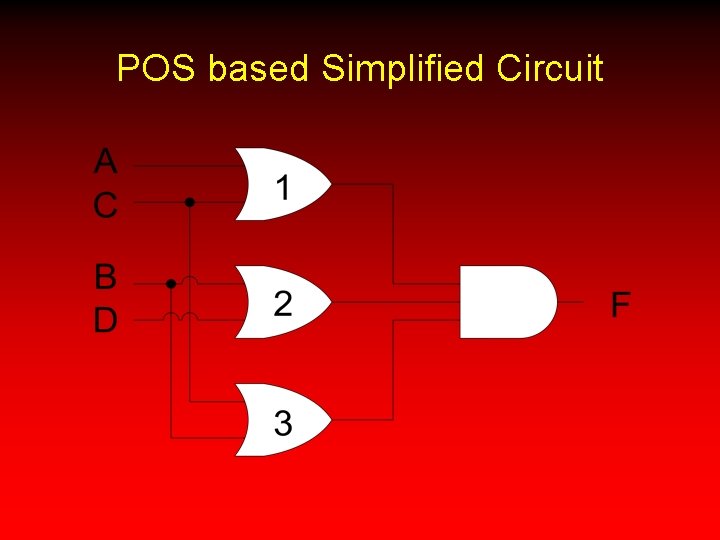

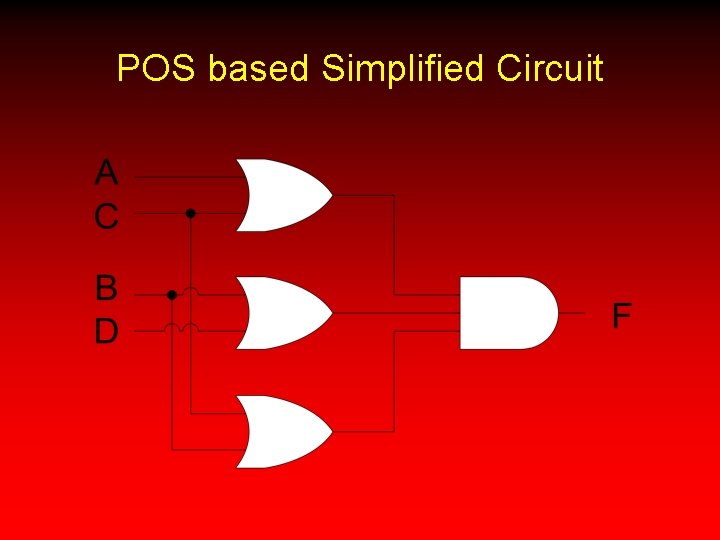

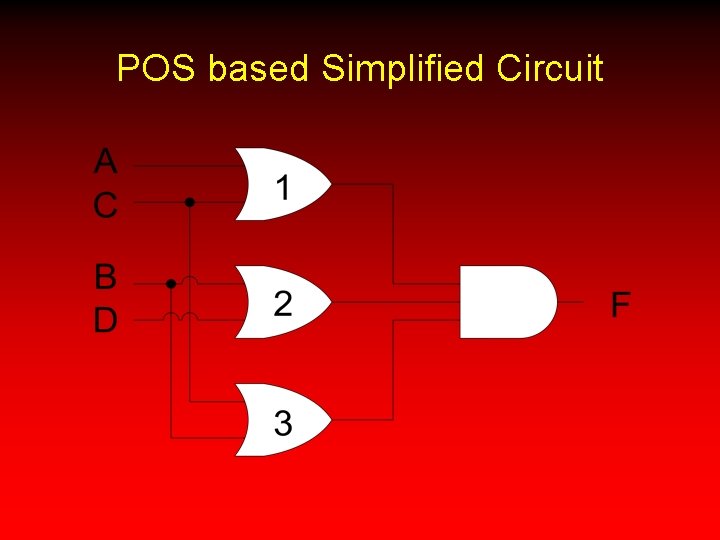

POS based Simplified Circuit

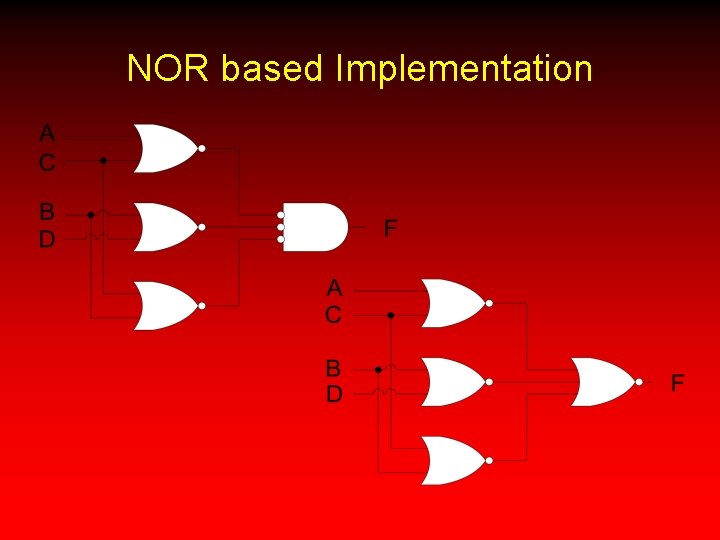

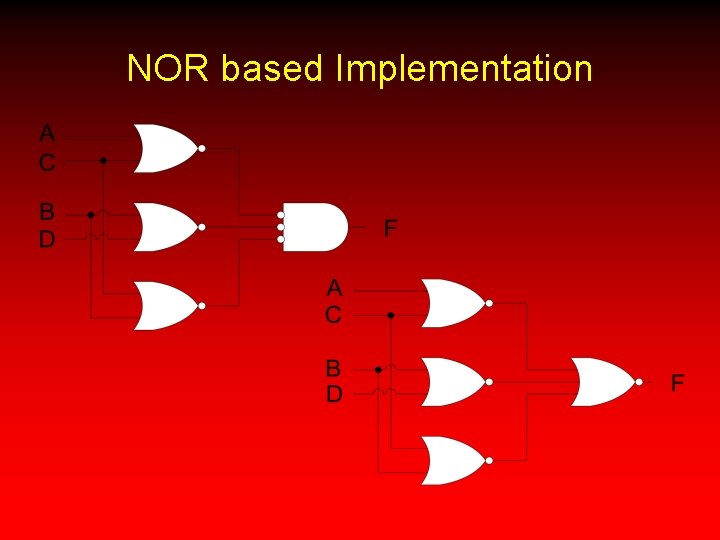

NOR based Implementation

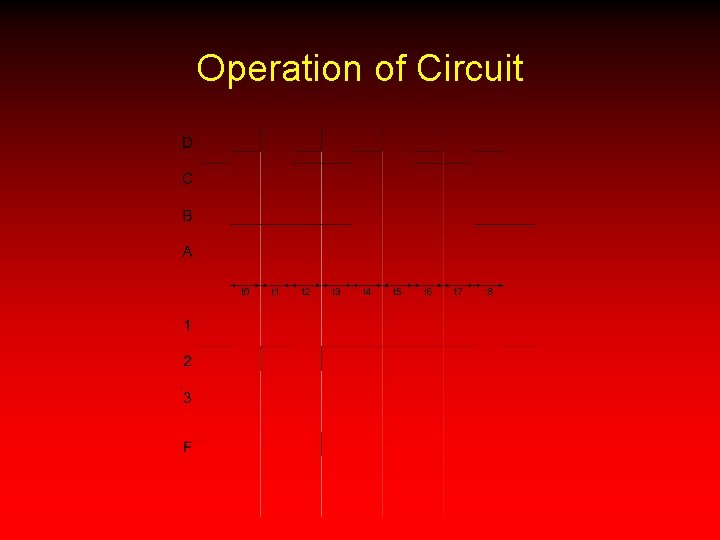

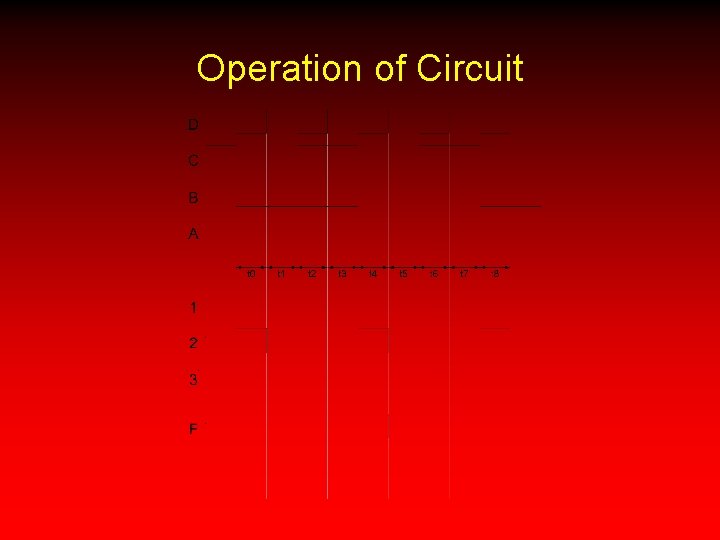

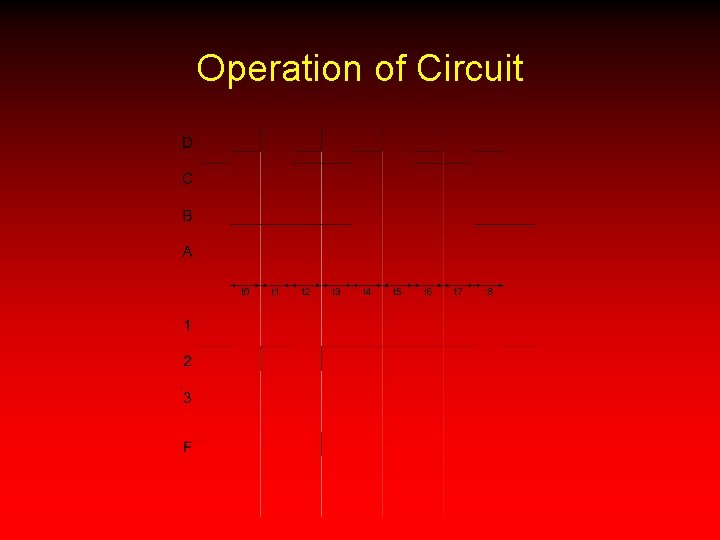

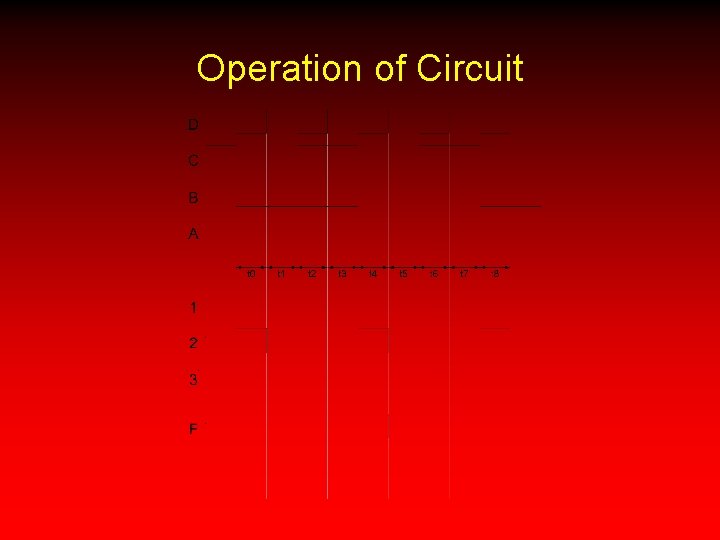

Operation of Circuit n n n Represented through a timing diagram Timing diagram of 8 time intervals Each interval representing a new input

POS based Simplified Circuit

Operation of Circuit

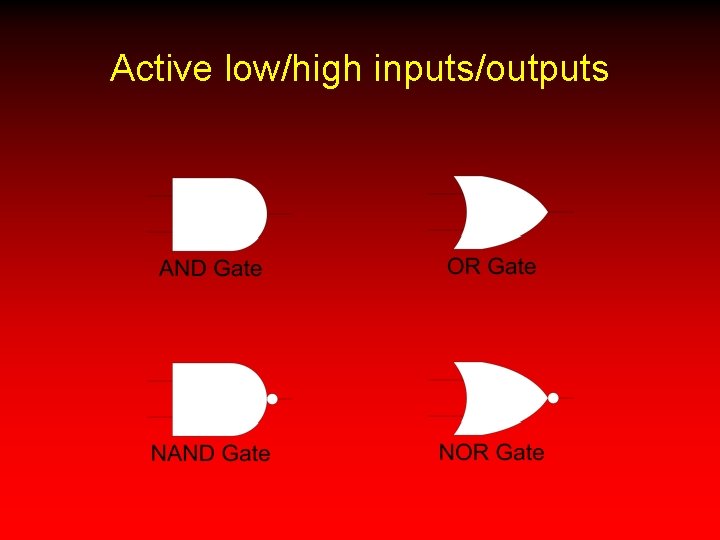

Active low/high inputs/outputs n n Active output state represented by 1 or 0 Active input state represented by 1 or 0 A bubble at output represents active low output A bubble at input represents active low input

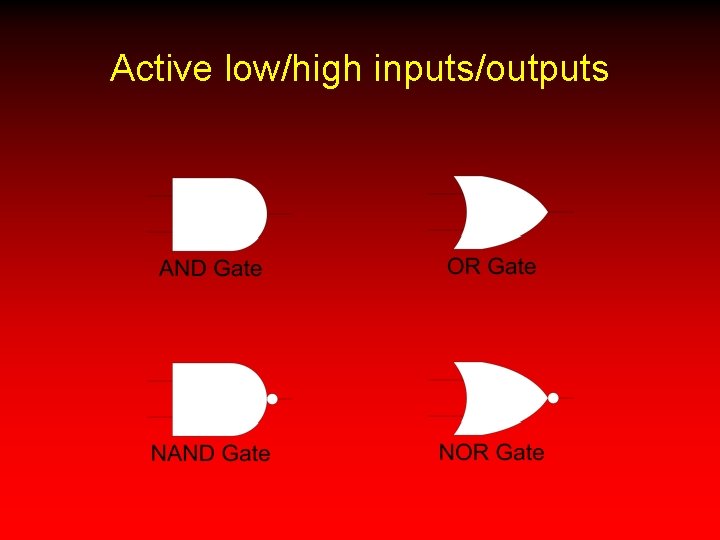

Active low/high inputs/outputs

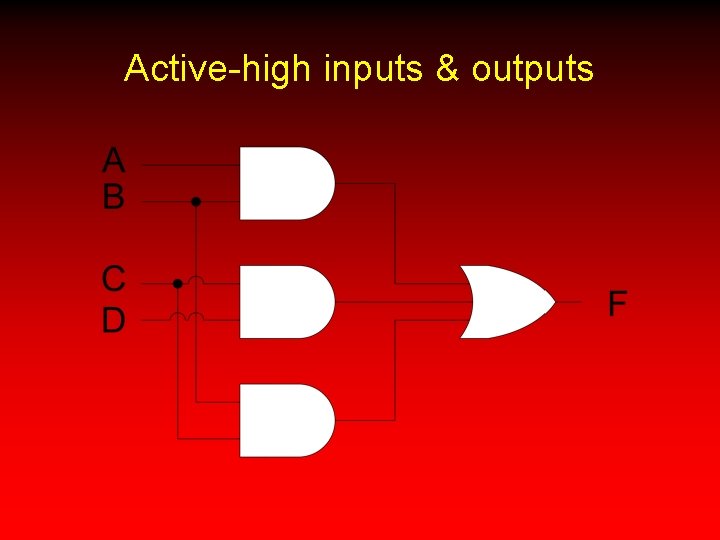

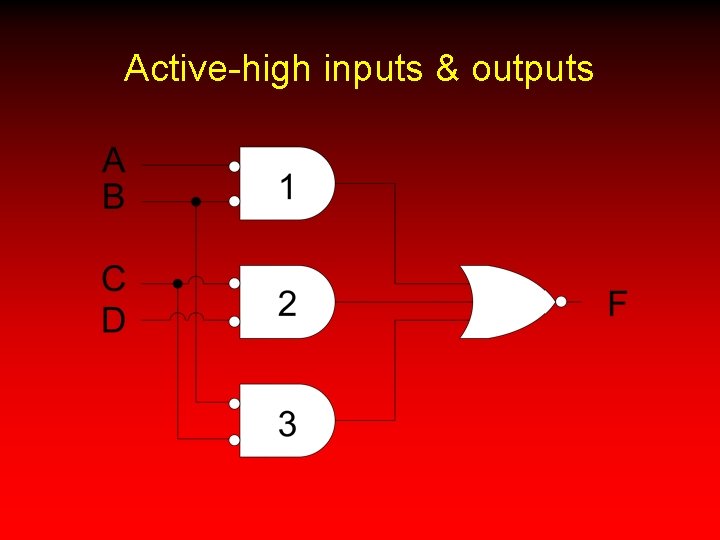

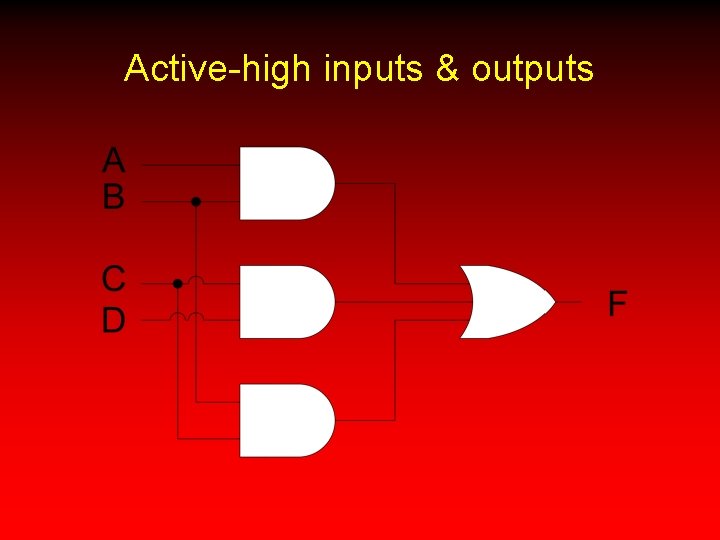

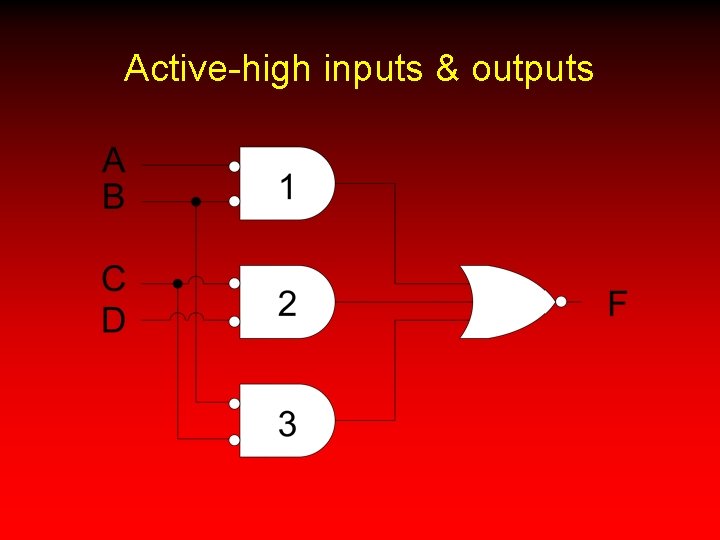

Active-high inputs & outputs

Active-high inputs & outputs

Operation of Circuit

Odd-Parity Generator Circuit n n n Circuit checks the 4 -bit data Generates a parity bit (odd) Data + parity bit add up to odd number of 1 s