Digital Logic Design Combinational Logic Mustafa Kemal Uygurolu

Digital Logic Design Combinational Logic Mustafa Kemal Uyguroğlu

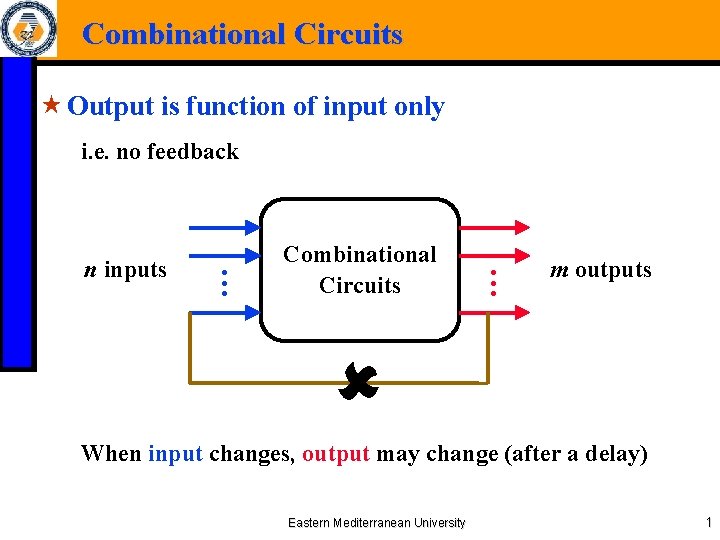

Combinational Circuits « Output is function of input only i. e. no feedback n inputs • • • Combinational Circuits • • • m outputs When input changes, output may change (after a delay) Eastern Mediterranean University 1

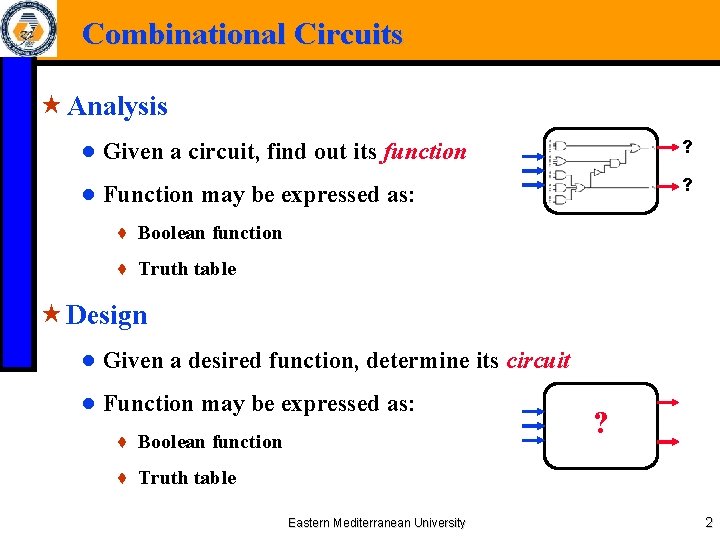

Combinational Circuits « Analysis ● Given a circuit, find out its function ? ● Function may be expressed as: ? ♦ Boolean function ♦ Truth table « Design ● Given a desired function, determine its circuit ● Function may be expressed as: ♦ Boolean function ? ♦ Truth table Eastern Mediterranean University 2

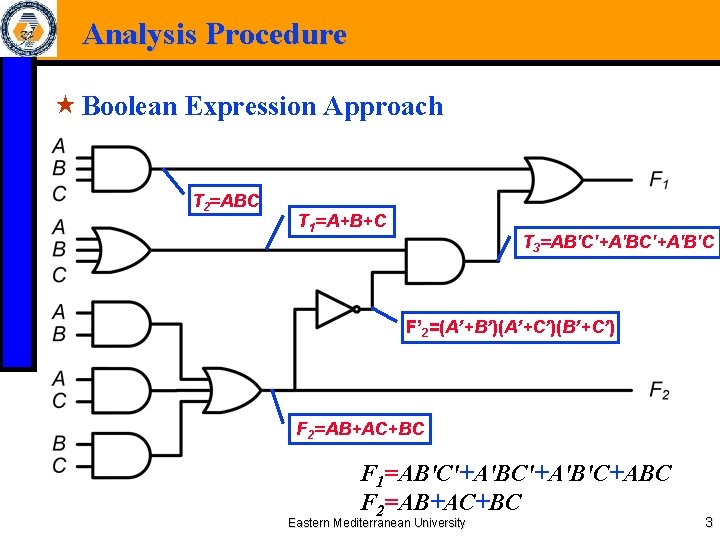

Analysis Procedure « Boolean Expression Approach T 2=ABC T 1=A+B+C T 3=AB'C'+A'B'C F’ 2=(A’+B’)(A’+C’)(B’+C’) F 2=AB+AC+BC F 1=AB'C'+A'B'C+ABC F 2=AB+AC+BC Eastern Mediterranean University 3

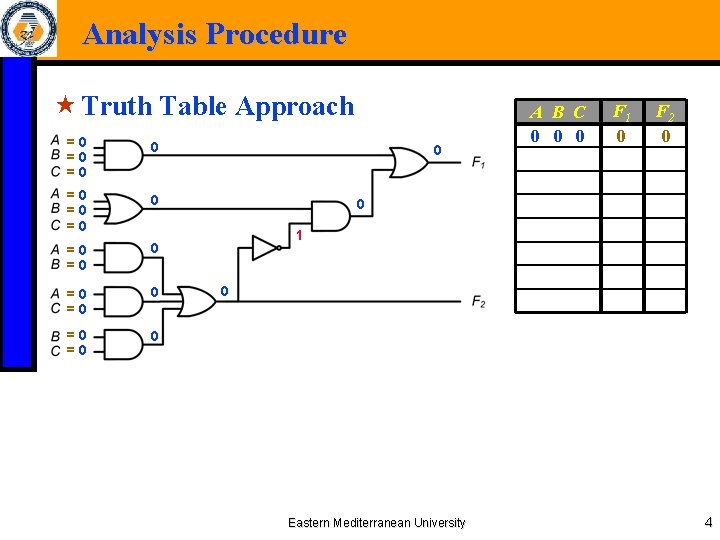

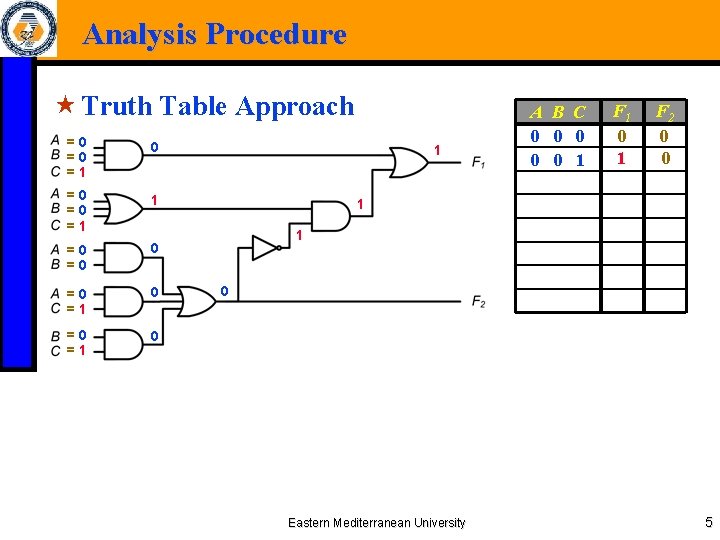

Analysis Procedure « Truth Table Approach =0 =0 =0 0 =0 =0 0 0 A B C 0 0 0 F 1 0 F 2 0 0 1 0 Eastern Mediterranean University 4

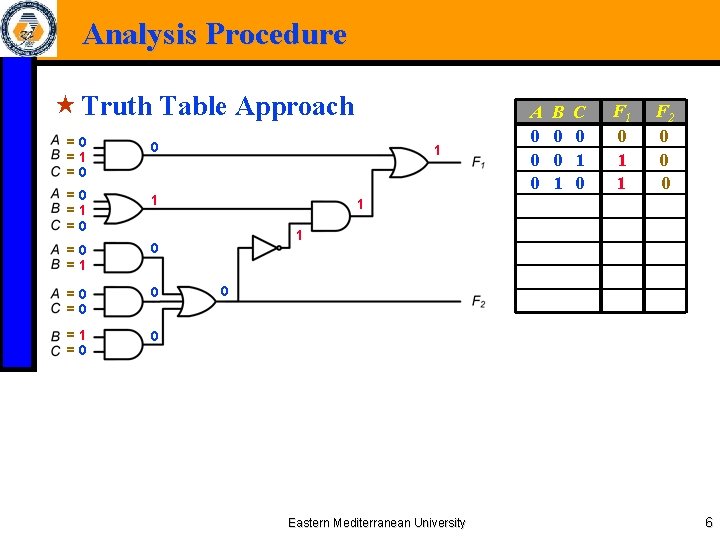

Analysis Procedure « Truth Table Approach =0 =0 =1 0 =0 =0 =1 1 =0 =0 =1 0 1 A B C 0 0 0 1 F 1 0 1 F 2 0 0 1 1 0 Eastern Mediterranean University 5

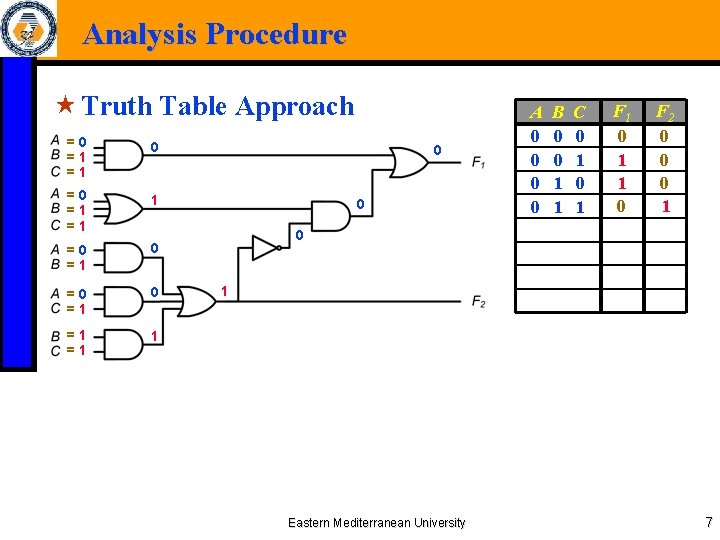

Analysis Procedure « Truth Table Approach =0 =1 =0 0 =0 =1 0 =0 =0 0 =1 =0 0 1 A 0 0 0 B 0 0 1 C 0 1 0 F 1 0 1 1 F 2 0 0 0 1 1 0 Eastern Mediterranean University 6

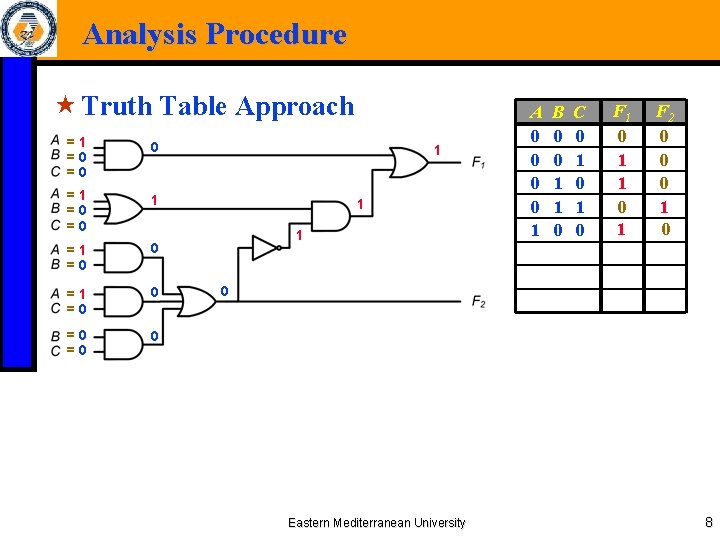

Analysis Procedure « Truth Table Approach =0 =1 =1 0 =0 =1 =1 1 =0 =1 =1 1 0 0 A 0 0 B 0 0 1 1 C 0 1 F 1 0 1 1 0 F 2 0 0 0 1 Eastern Mediterranean University 7

Analysis Procedure « Truth Table Approach =1 =0 =0 0 =1 =0 =0 1 =1 =0 0 =0 =0 0 1 1 1 A 0 0 1 B 0 0 1 1 0 C 0 1 0 F 1 0 1 F 2 0 0 0 1 0 0 Eastern Mediterranean University 8

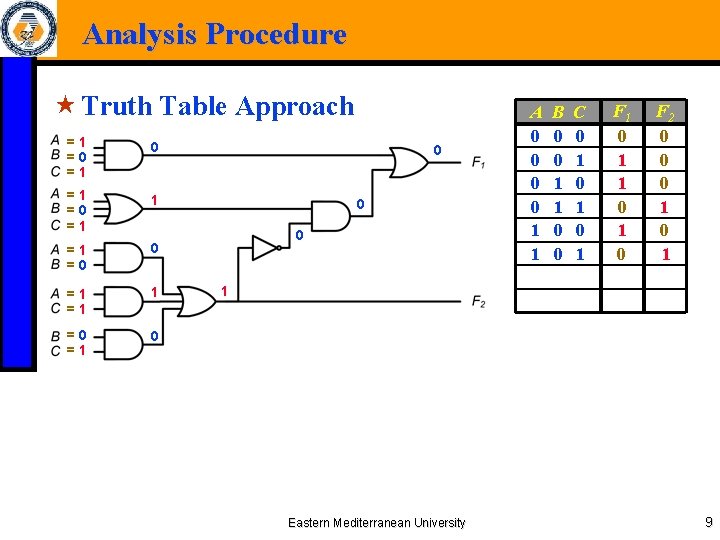

Analysis Procedure « Truth Table Approach =1 =0 =1 1 =1 =0 0 =1 =1 1 =0 =1 0 0 A 0 0 1 1 B 0 0 1 1 0 0 C 0 1 0 1 F 1 0 1 0 F 2 0 0 0 1 1 Eastern Mediterranean University 9

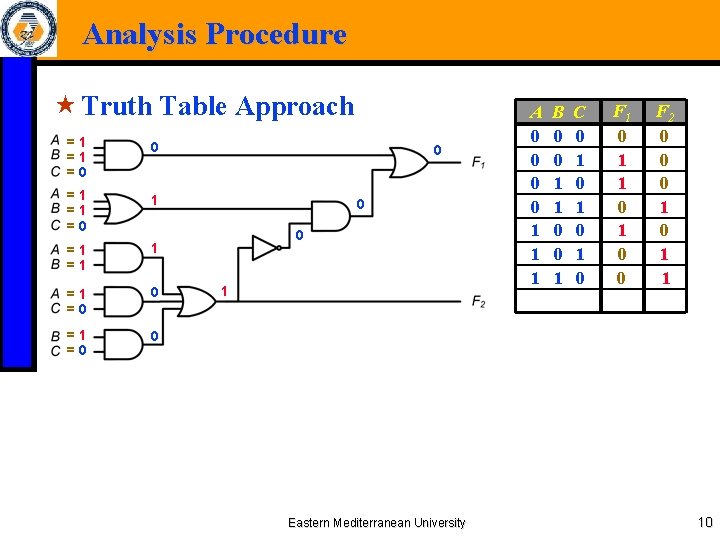

Analysis Procedure « Truth Table Approach =1 =1 =0 0 =1 =1 =0 1 =1 =1 =0 0 0 1 Eastern Mediterranean University A 0 0 1 1 1 B 0 0 1 1 0 0 1 C 0 1 0 1 0 F 1 0 1 0 0 F 2 0 0 0 1 1 10

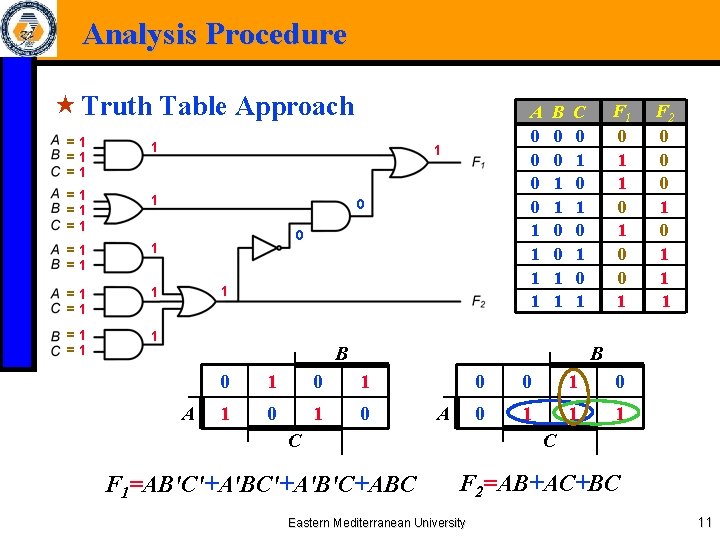

Analysis Procedure « Truth Table Approach =1 =1 =1 1 =1 =1 1 A 0 0 1 1 1 0 0 1 B 0 0 1 1 B A F 1 0 1 0 0 1 C 0 1 0 1 F 2 0 0 0 1 1 1 B 0 1 1 0 A C F 1=AB'C'+A'B'C+ABC 0 0 1 1 1 C F 2=AB+AC+BC Eastern Mediterranean University 11

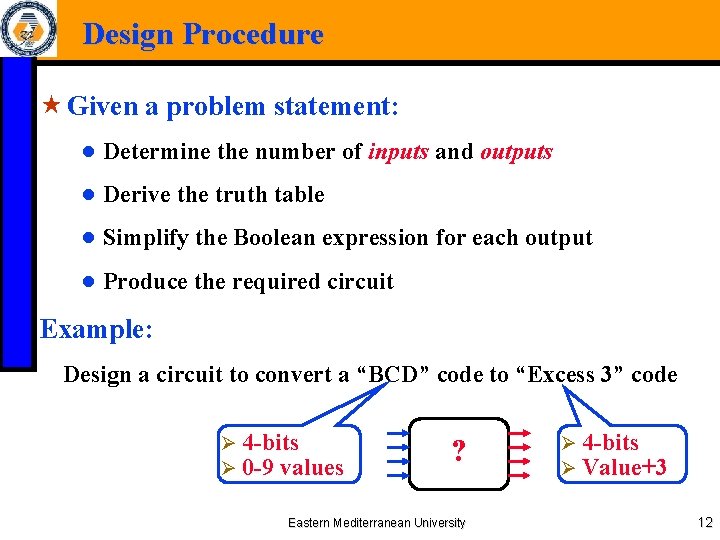

Design Procedure « Given a problem statement: ● Determine the number of inputs and outputs ● Derive the truth table ● Simplify the Boolean expression for each output ● Produce the required circuit Example: Design a circuit to convert a “BCD” code to “Excess 3” code Ø 4 -bits Ø 0 -9 values ? Eastern Mediterranean University Ø 4 -bits Ø Value+3 12

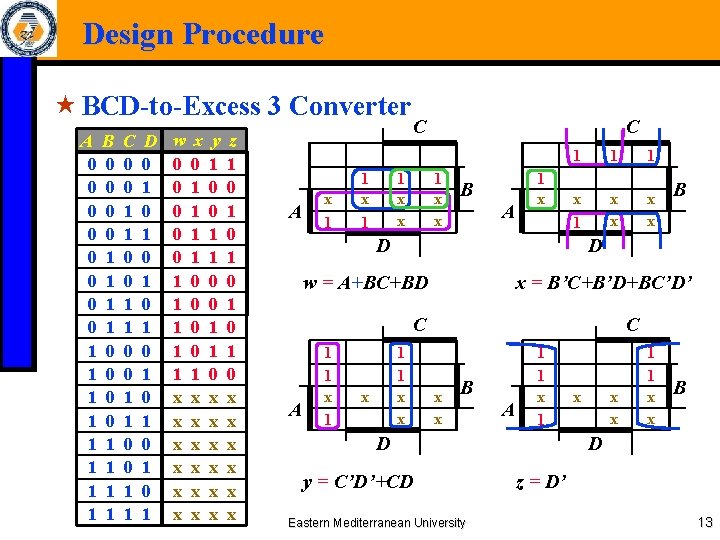

Design Procedure « BCD-to-Excess 3 Converter A 0 0 0 0 1 1 1 1 B 0 0 0 0 1 1 1 1 C 0 0 1 1 D 0 1 0 1 w 0 0 0 1 1 1 x x x x 0 1 1 0 0 1 x x x y 1 0 0 1 1 0 x x x z 1 0 1 0 1 0 x x x A x 1 1 x 1 C 1 x x B A 1 x 1 1 1 x x x x D D w = A+BC+BD x = B’C+B’D+BC’D’ C A 1 1 x 1 1 1 x x x B C x x B A 1 1 x 1 D y = C’D’+CD Eastern Mediterranean University x x x 1 1 x x B D z = D’ 13

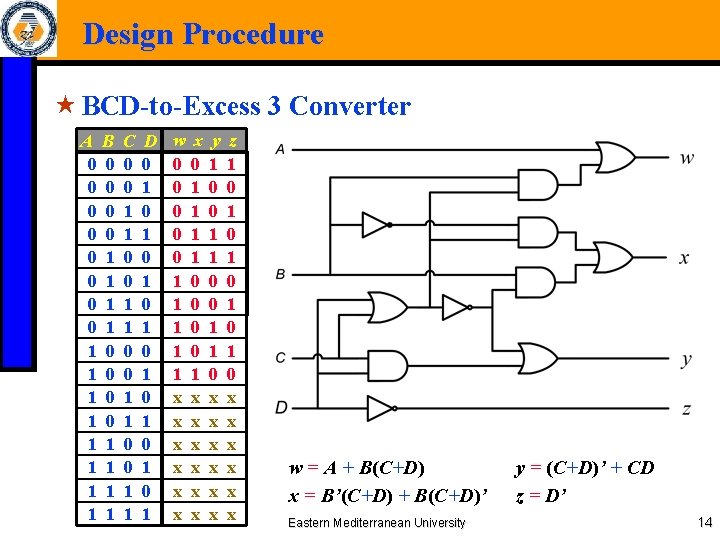

Design Procedure « BCD-to-Excess 3 Converter A 0 0 0 0 1 1 1 1 B 0 0 0 0 1 1 1 1 C 0 0 1 1 D 0 1 0 1 w 0 0 0 1 1 1 x x x x 0 1 1 0 0 1 x x x y 1 0 0 1 1 0 x x x z 1 0 1 0 1 0 x x x w = A + B(C+D) x = B’(C+D) + B(C+D)’ Eastern Mediterranean University y = (C+D)’ + CD z = D’ 14

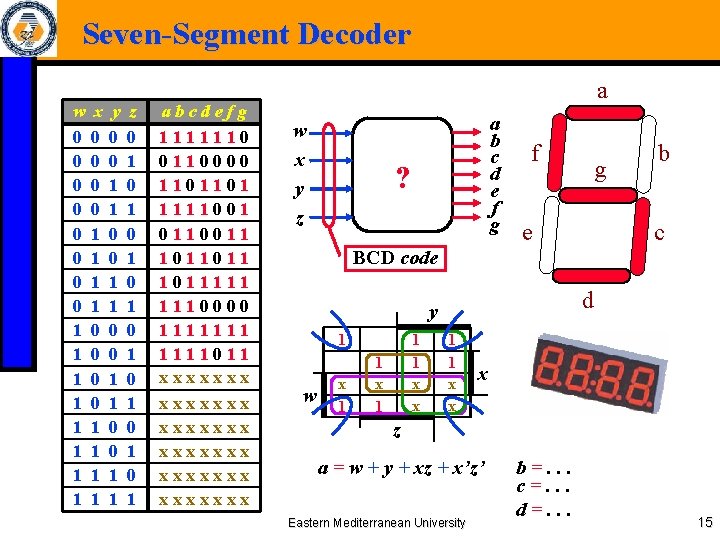

Seven-Segment Decoder w 0 0 0 0 1 1 1 1 x 0 0 0 0 1 1 1 1 y 0 0 1 1 z 0 1 0 1 abcdefg 1111110 0110000 1101101 1111001 0110011 1011111 1110000 1111111011 xxxxxxx xxxxxxx a w x y z a b c d e f g ? f g e b c BCD code d y 1 w x 1 1 1 x x x z a = w + y + xz + x’z’ Eastern Mediterranean University b=. . . c=. . . d=. . . 15

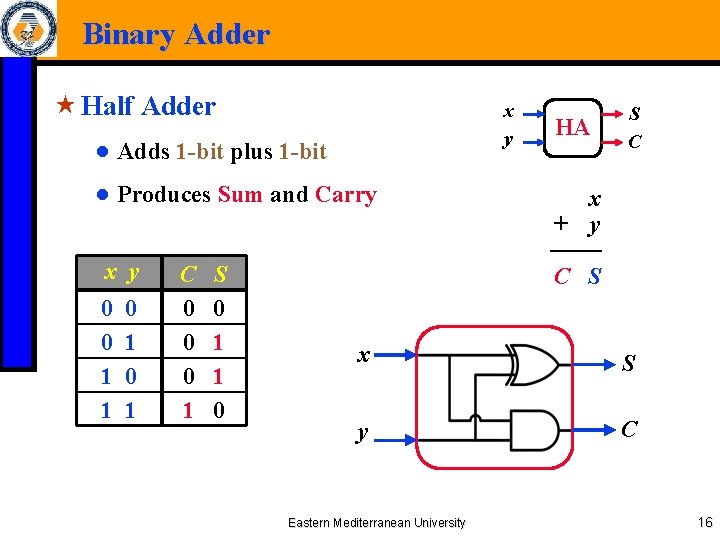

Binary Adder « Half Adder x y ● Adds 1 -bit plus 1 -bit ● Produces Sum and Carry x y 0 0 1 1 0 1 C 0 0 0 1 S 0 1 1 0 HA S C x + y ─── C S x S y C Eastern Mediterranean University 16

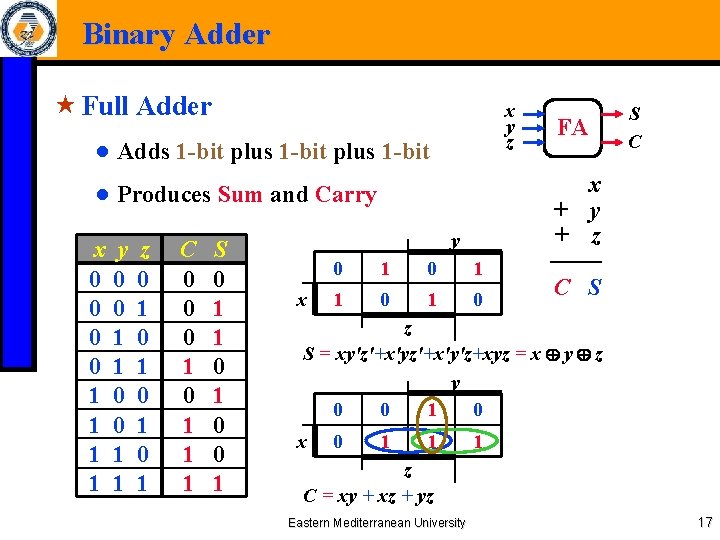

Binary Adder « Full Adder x y z ● Adds 1 -bit plus 1 -bit ● Produces Sum and Carry x y 0 0 0 1 0 1 1 1 1 z 0 1 0 1 C 0 0 0 1 1 1 S 0 1 1 0 0 1 y x 0 1 1 0 FA S C x + y + z ─── C S z S = xy'z'+x'y'z+xyz = x y z y 0 0 1 0 x 0 1 1 1 z C = xy + xz + yz Eastern Mediterranean University 17

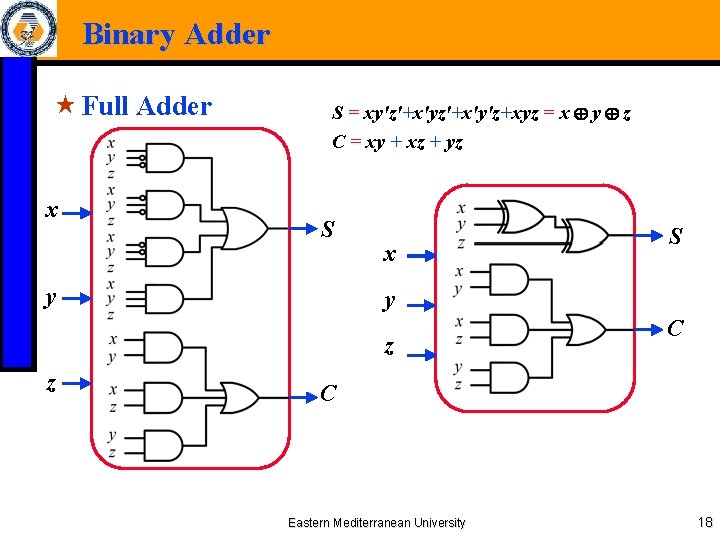

Binary Adder « Full Adder x S = xy'z'+x'y'z+xyz = x y z C = xy + xz + yz S y x y z z S C C Eastern Mediterranean University 18

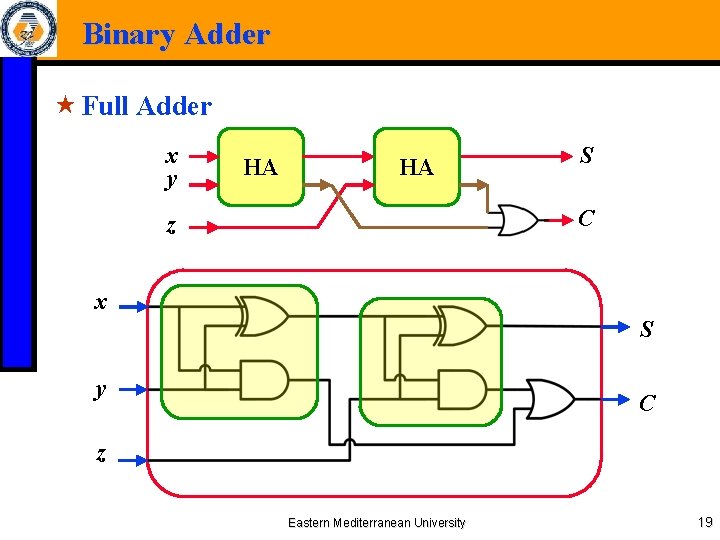

Binary Adder « Full Adder x y HA HA S C z x S y C z Eastern Mediterranean University 19

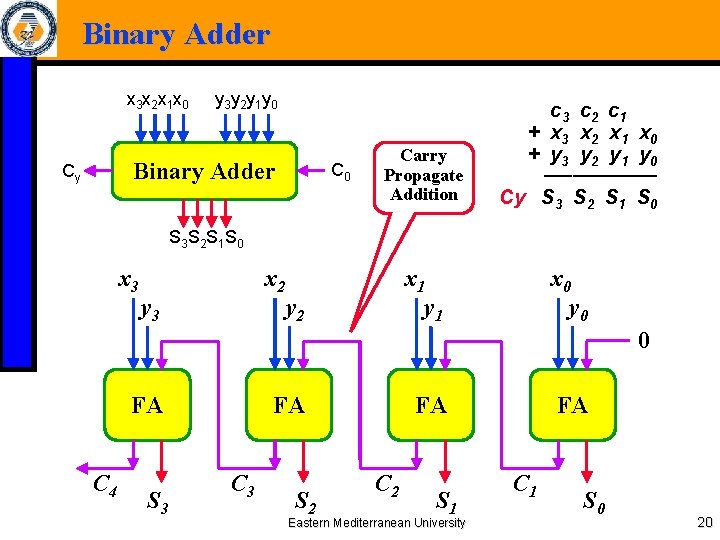

Binary Adder x 3 x 2 x 1 x 0 y 3 y 2 y 1 y 0 Binary Adder Cy C 0 Carry Propagate Addition c 3 c 2 c 1. + x 3 x 2 x 1 x 0 + y 3 y 2 y 1 y 0 ──── Cy S 3 S 2 S 1 S 0 S 3 S 2 S 1 S 0 x 3 x 2 y 3 x 1 y 2 x 0 y 0 0 FA C 4 S 3 FA C 3 S 2 FA C 2 S 1 Eastern Mediterranean University FA C 1 S 0 20

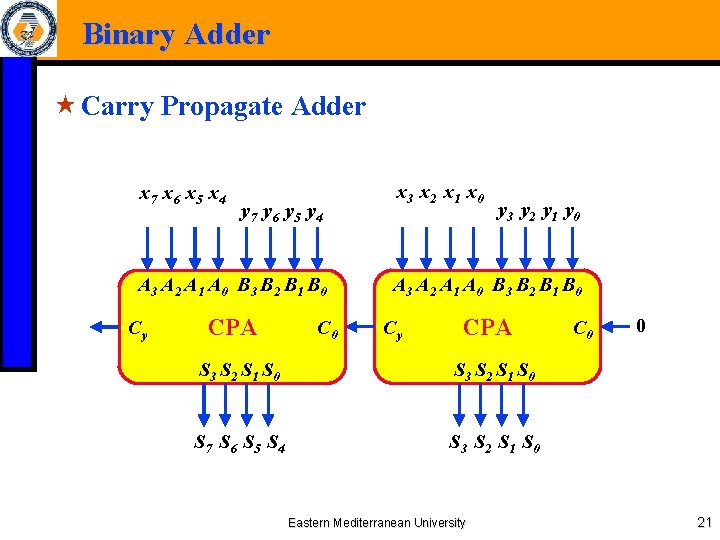

Binary Adder « Carry Propagate Adder x 7 x 6 x 5 x 4 y 7 y 6 y 5 y 4 A 3 A 2 A 1 A 0 B 3 B 2 B 1 B 0 Cy CPA C 0 x 3 x 2 x 1 x 0 y 3 y 2 y 1 y 0 A 3 A 2 A 1 A 0 B 3 B 2 B 1 B 0 Cy CPA S 3 S 2 S 1 S 0 S 7 S 6 S 5 S 4 S 3 S 2 S 1 S 0 Eastern Mediterranean University C 0 0 21

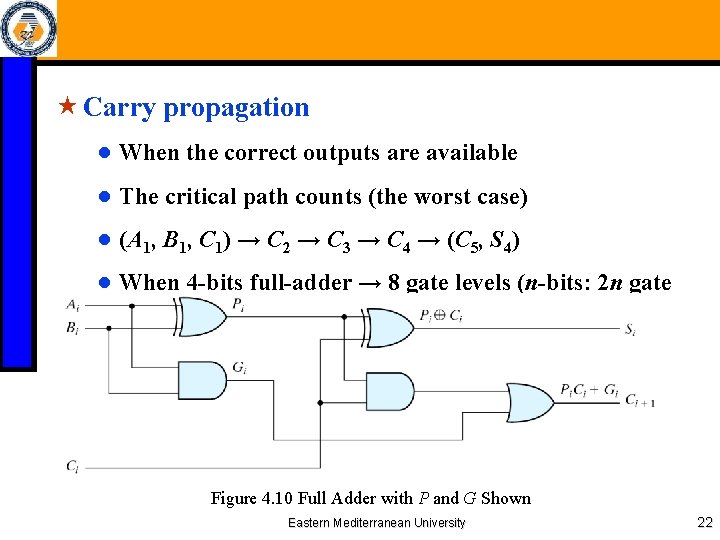

« Carry propagation ● When the correct outputs are available ● The critical path counts (the worst case) ● (A 1, B 1, C 1) → C 2 → C 3 → C 4 → (C 5, S 4) ● When 4 -bits full-adder → 8 gate levels (n-bits: 2 n gate levels) Figure 4. 10 Full Adder with P and G Shown Eastern Mediterranean University 22

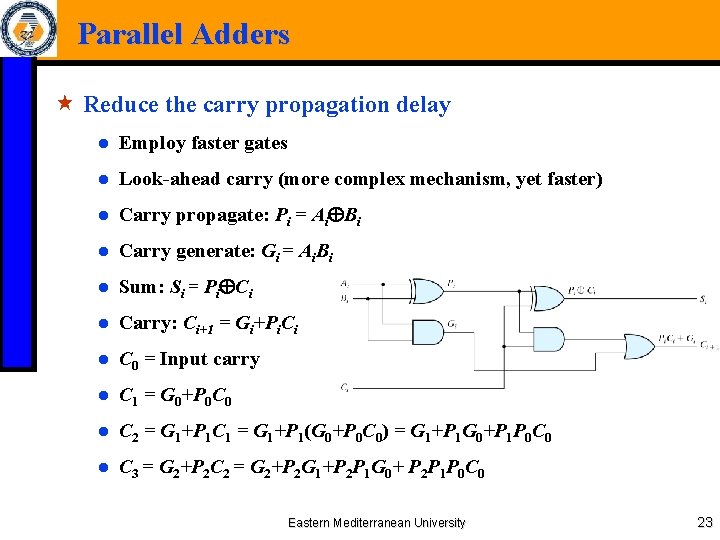

Parallel Adders « Reduce the carry propagation delay ● Employ faster gates ● Look-ahead carry (more complex mechanism, yet faster) ● Carry propagate: Pi = Ai Bi ● Carry generate: Gi = Ai. Bi ● Sum: Si = Pi Ci ● Carry: Ci+1 = Gi+Pi. Ci ● C 0 = Input carry ● C 1 = G 0+P 0 C 0 ● C 2 = G 1+P 1 C 1 = G 1+P 1(G 0+P 0 C 0) = G 1+P 1 G 0+P 1 P 0 C 0 ● C 3 = G 2+P 2 C 2 = G 2+P 2 G 1+P 2 P 1 G 0+ P 2 P 1 P 0 C 0 Eastern Mediterranean University 23

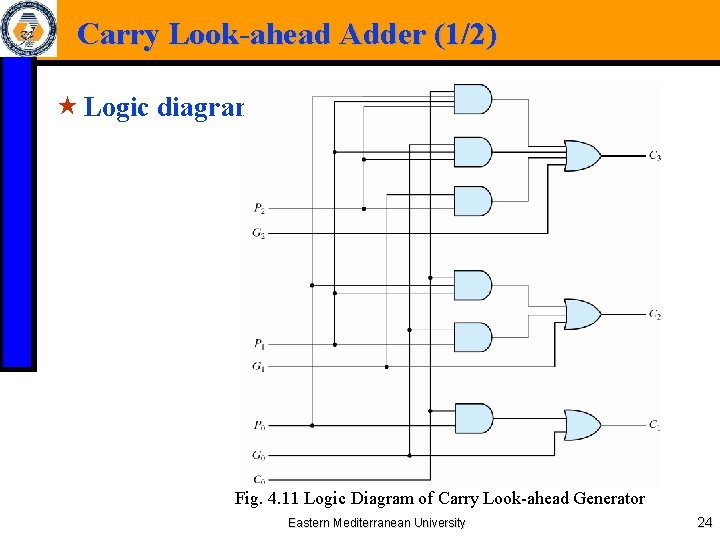

Carry Look-ahead Adder (1/2) « Logic diagram Fig. 4. 11 Logic Diagram of Carry Look-ahead Generator Eastern Mediterranean University 24

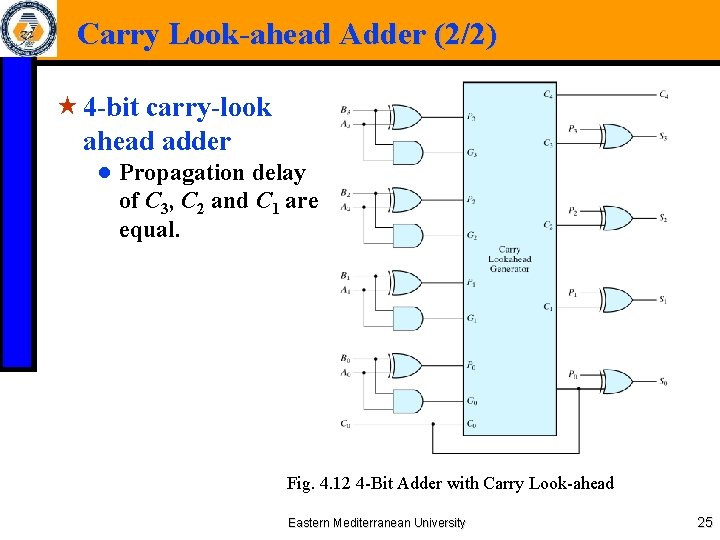

Carry Look-ahead Adder (2/2) « 4 -bit carry-look ahead adder ● Propagation delay of C 3, C 2 and C 1 are equal. Fig. 4. 12 4 -Bit Adder with Carry Look-ahead Eastern Mediterranean University 25

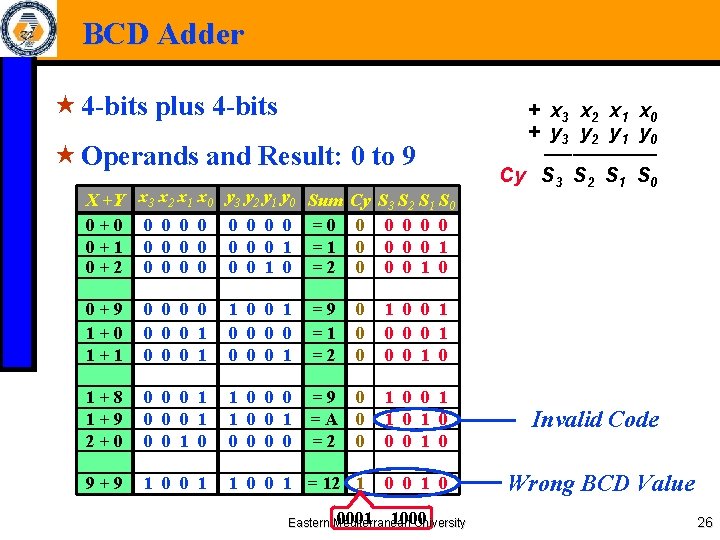

BCD Adder « 4 -bits plus 4 -bits « Operands and Result: 0 to 9 X +Y x 3 x 2 x 1 x 0 0+0 0 0 0+1 0 0 0+2 0 0 y 3 y 2 y 1 y 0 Sum 0 0 =0 0 1 =1 0 0 1 0 =2 0+9 1+0 1+1 0 0 0 0 1 1 0 0 0 0 0 1 =9 =1 =2 1+8 1+9 2+0 0 1 0 0 1 0 0 0 0 9+9 1 0 0 1 Cy 0 0 0 S 3 S 2 S 1 S 0 0 0 0 1 0 0 1 0 =9 0 =A 0 =2 0 1 0 0 1 1 0 0 0 1 = 12 1 0 0001 1000 Eastern Mediterranean University + x 3 x 2 x 1 x 0 + y 3 y 2 y 1 y 0 ──── Cy S 3 S 2 S 1 S 0 Invalid Code Wrong BCD Value 26

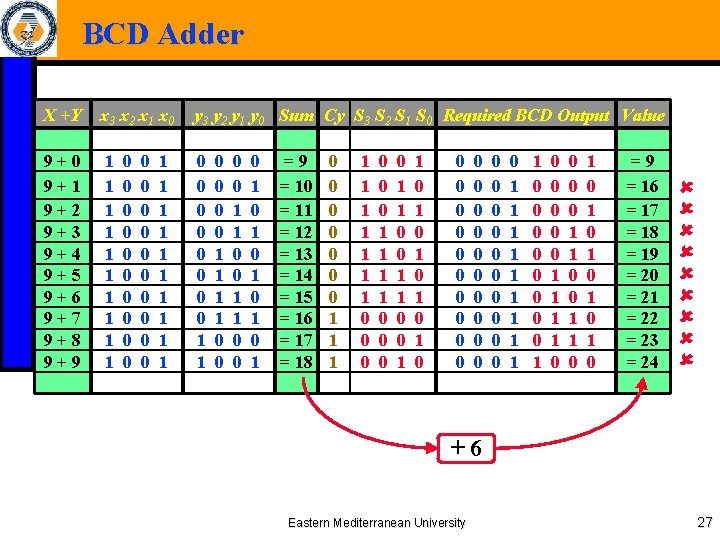

BCD Adder X +Y x 3 x 2 x 1 x 0 y 3 y 2 y 1 y 0 Sum Cy S 3 S 2 S 1 S 0 Required BCD Output Value 9+0 9+1 9+2 9+3 9+4 9+5 9+6 9+7 9+8 9+9 1 1 1 1 1 0 0 0 0 0 0 0 1 1 1 1 1 0 0 1 1 0 0 0 1 0 1 0 1 =9 = 10 = 11 = 12 = 13 = 14 = 15 = 16 = 17 = 18 0 0 0 0 1 1 1 1 1 0 0 0 1 1 0 0 1 1 0 1 0 1 0 0 0 0 0 0 0 0 1 1 1 1 1 0 0 0 0 1 1 0 0 1 1 0 1 0 1 0 =9 = 16 = 17 = 18 = 19 = 20 = 21 = 22 = 23 = 24 +6 Eastern Mediterranean University 27

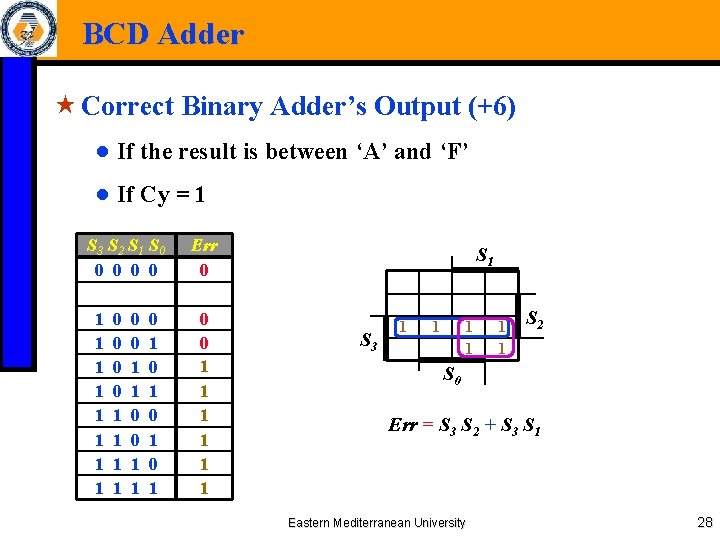

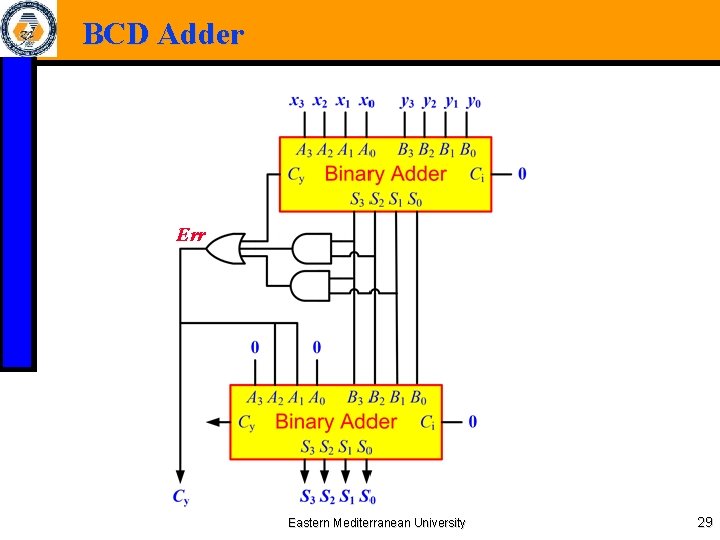

BCD Adder « Correct Binary Adder’s Output (+6) ● If the result is between ‘A’ and ‘F’ ● If Cy = 1 S 3 S 2 S 1 S 0 0 0 1 1 1 1 0 0 1 1 0 1 0 1 Err 0 0 0 1 1 1 S 1 S 3 1 1 1 S 2 S 0 Err = S 3 S 2 + S 3 S 1 Eastern Mediterranean University 28

BCD Adder Err Eastern Mediterranean University 29

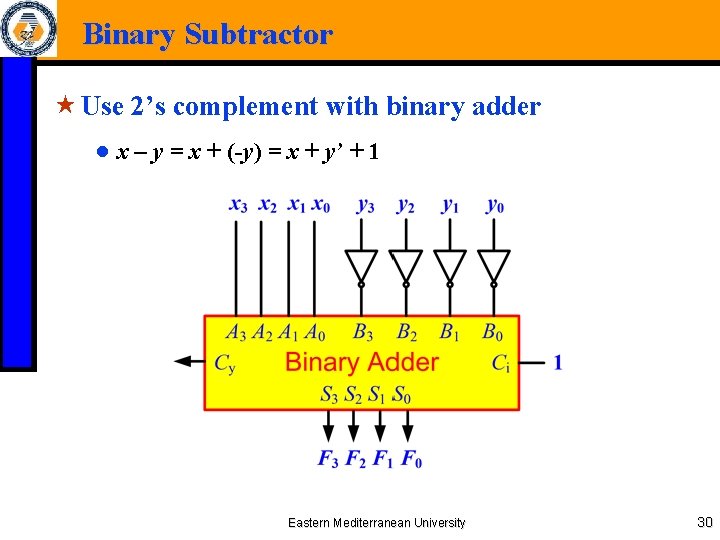

Binary Subtractor « Use 2’s complement with binary adder ● x – y = x + (-y) = x + y’ + 1 Eastern Mediterranean University 30

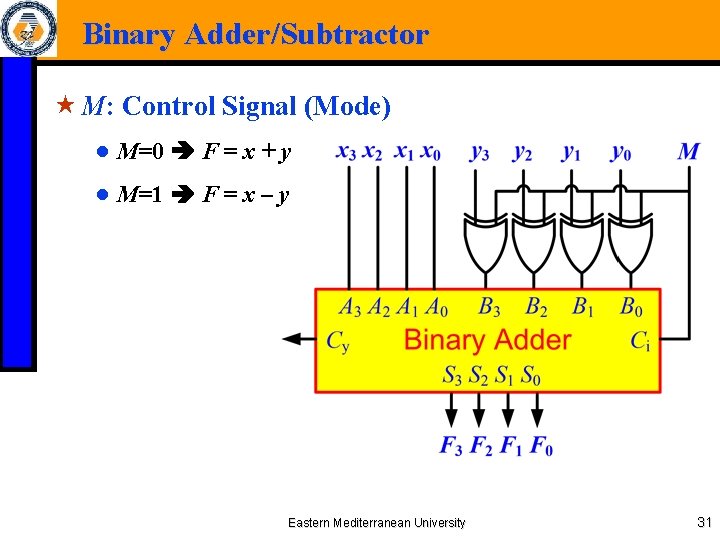

Binary Adder/Subtractor « M: Control Signal (Mode) ● M=0 F = x + y ● M=1 F = x – y Eastern Mediterranean University 31

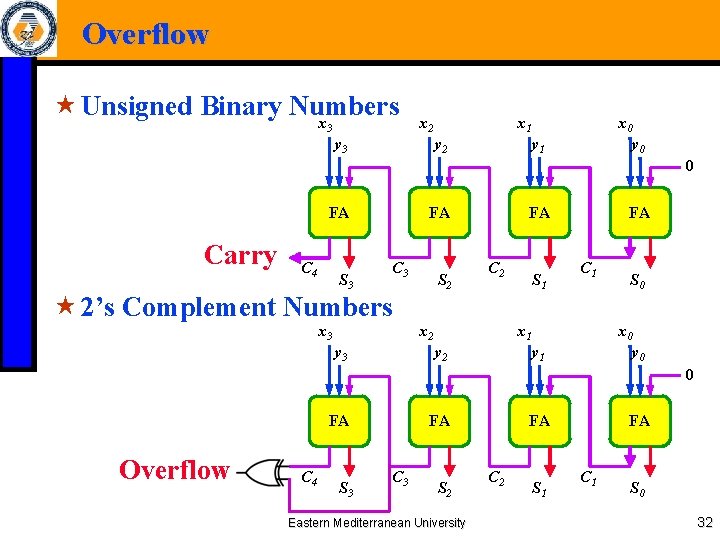

Overflow « Unsigned Binary Numbers x 3 y 3 x 2 x 1 y 2 x 0 y 1 0 FA Carry C 4 S 3 FA C 3 « 2’s Complement Numbers x 3 y 3 S 2 x 2 FA C 2 S 1 x 1 y 2 FA C 1 S 0 x 0 y 1 0 FA Overflow C 4 S 3 FA C 3 S 2 Eastern Mediterranean University FA C 2 S 1 FA C 1 S 0 32

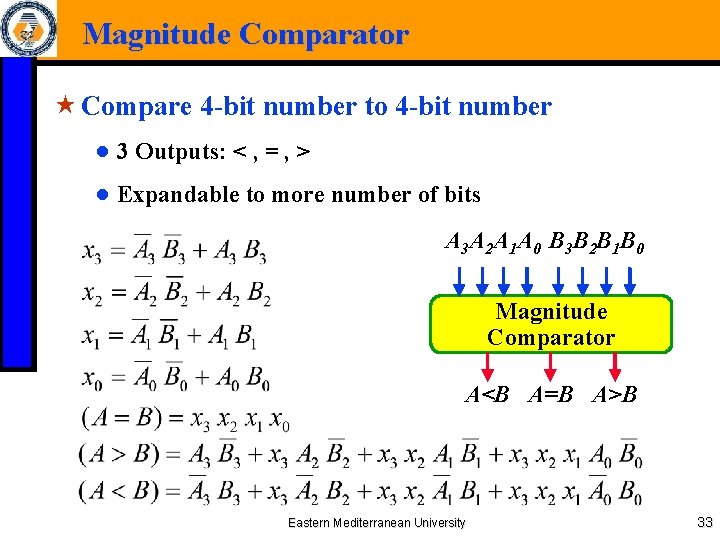

Magnitude Comparator « Compare 4 -bit number to 4 -bit number ● 3 Outputs: < , = , > ● Expandable to more number of bits A 3 A 2 A 1 A 0 B 3 B 2 B 1 B 0 Magnitude Comparator A<B A=B A>B Eastern Mediterranean University 33

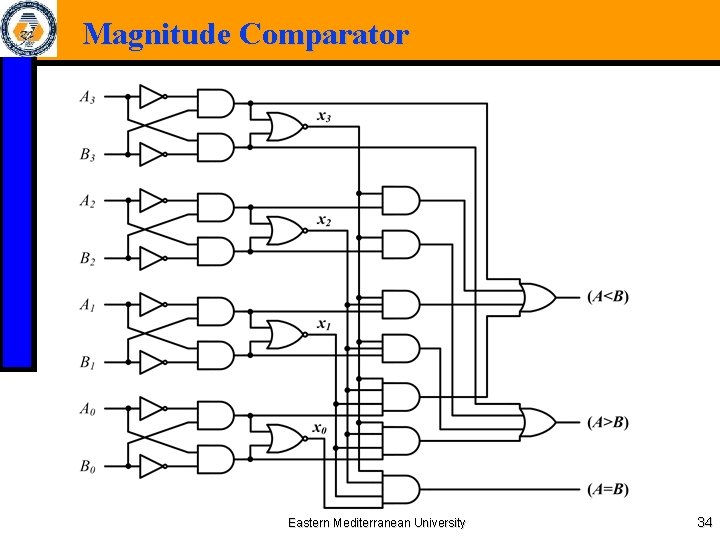

Magnitude Comparator Eastern Mediterranean University 34

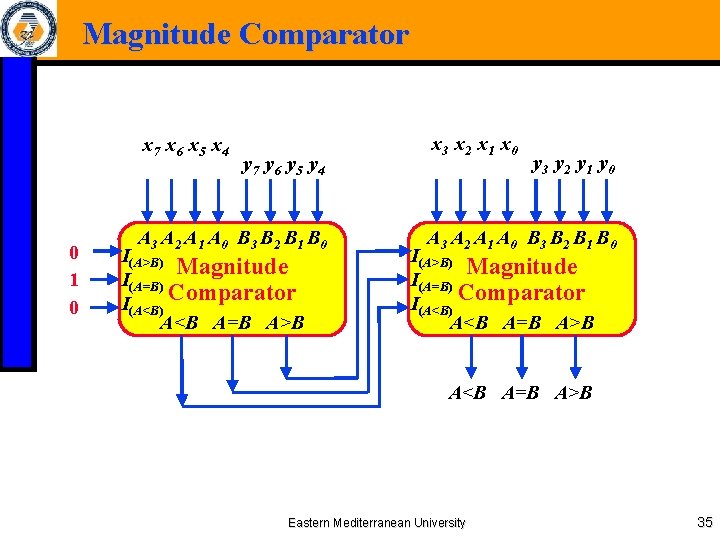

Magnitude Comparator x 7 x 6 x 5 x 4 0 1 0 y 7 y 6 y 5 y 4 A 3 A 2 A 1 A 0 B 3 B 2 B 1 B 0 I(A>B) Magnitude I(A=B) I(A<B) Comparator A<B A=B A>B x 3 x 2 x 1 x 0 y 3 y 2 y 1 y 0 A 3 A 2 A 1 A 0 B 3 B 2 B 1 B 0 I(A>B) Magnitude I(A=B) I(A<B) Comparator A<B A=B A>B Eastern Mediterranean University 35

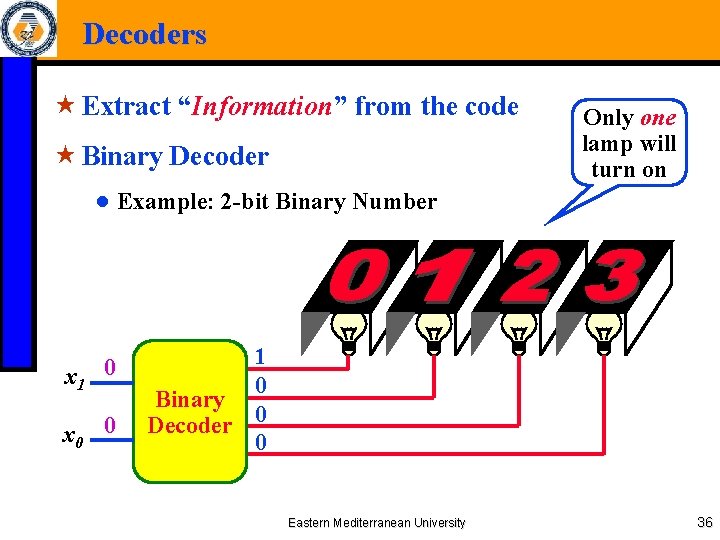

Decoders « Extract “Information” from the code « Binary Decoder Only one lamp will turn on ● Example: 2 -bit Binary Number x 1 0 x 0 0 1 0 Binary Decoder 0 0 Eastern Mediterranean University 36

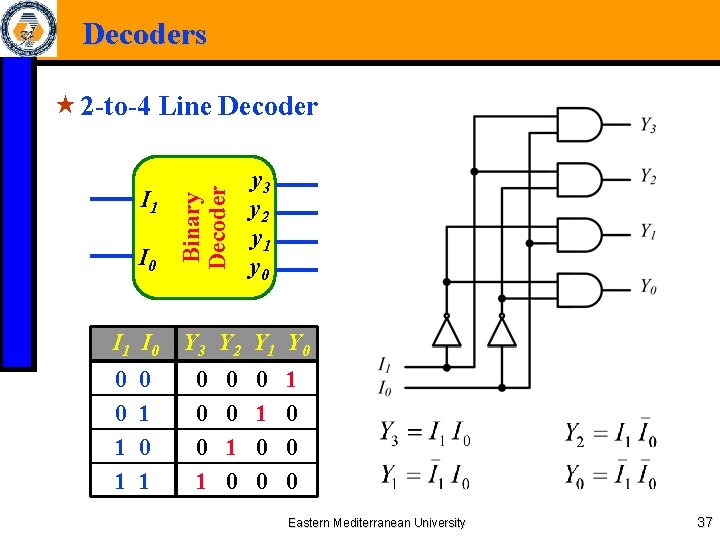

Decoders I 1 I 0 0 0 1 1 0 1 Binary Decoder « 2 -to-4 Line Decoder y 3 y 2 y 1 y 0 Y 3 Y 2 Y 1 Y 0 0 1 0 0 0 Eastern Mediterranean University 37

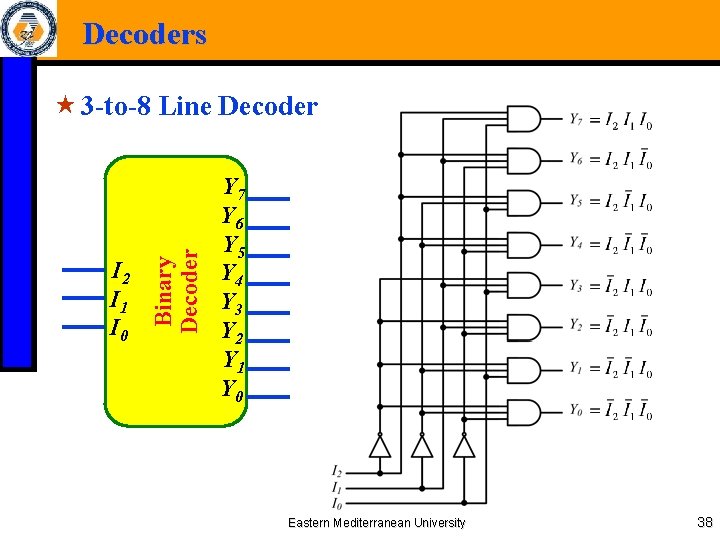

Decoders I 2 I 1 I 0 Binary Decoder « 3 -to-8 Line Decoder Y 7 Y 6 Y 5 Y 4 Y 3 Y 2 Y 1 Y 0 Eastern Mediterranean University 38

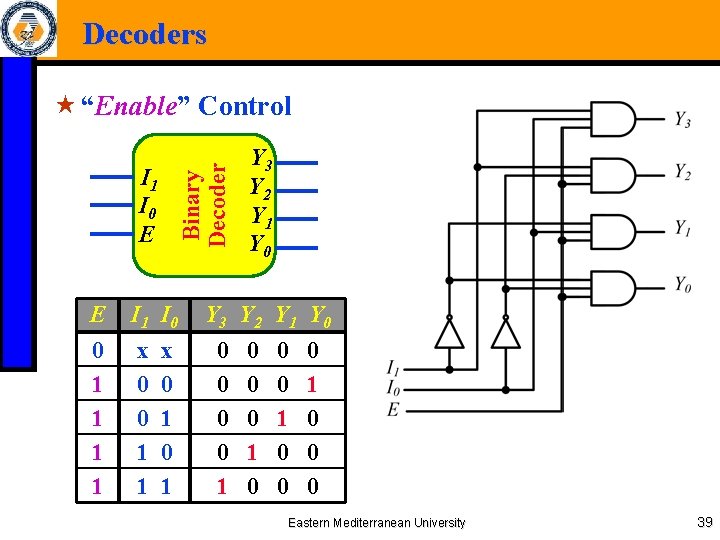

Decoders Binary Decoder « “Enable” Control I 1 I 0 E E I 1 I 0 0 1 1 x 0 1 Y 3 Y 2 Y 1 Y 0 0 0 1 0 0 0 Eastern Mediterranean University 39

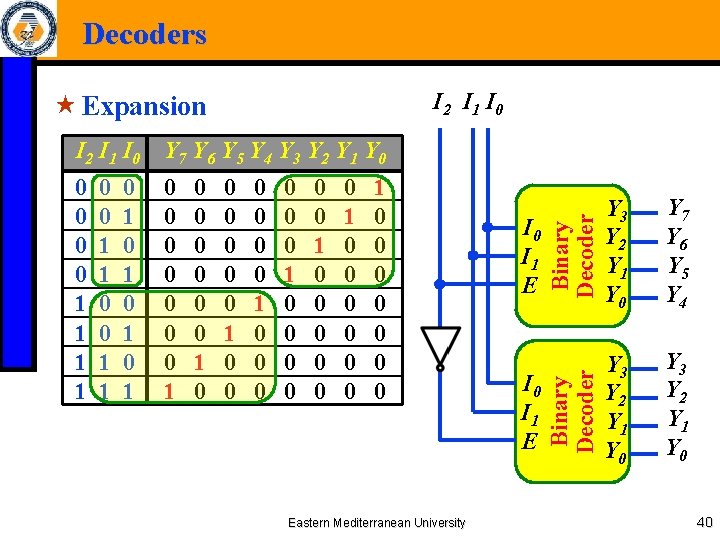

Decoders I 2 I 1 I 0 « Expansion 0 0 1 1 0 1 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 Eastern Mediterranean University I 0 I 1 E Binary Decoder 0 0 1 1 Y 3 Y 2 Y 1 Y 0 Y 7 Y 6 Y 5 Y 4 Binary Decoder I 2 I 1 I 0 Y 7 Y 6 Y 5 Y 4 Y 3 Y 2 Y 1 Y 0 40

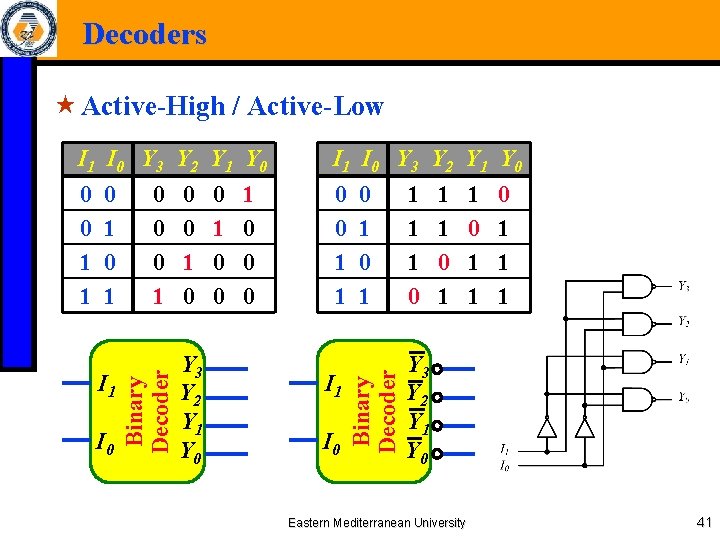

Decoders « Active-High / Active-Low I 1 I 0 Y 3 Y 2 Y 1 Y 0 0 0 1 1 I 0 0 0 1 0 Y 3 Y 2 Y 1 Y 0 0 1 0 0 0 I 1 I 0 0 1 Binary Decoder I 1 0 0 0 1 Binary Decoder 0 1 1 1 1 0 1 1 1 Y 3 Y 2 Y 1 Y 0 Eastern Mediterranean University 41

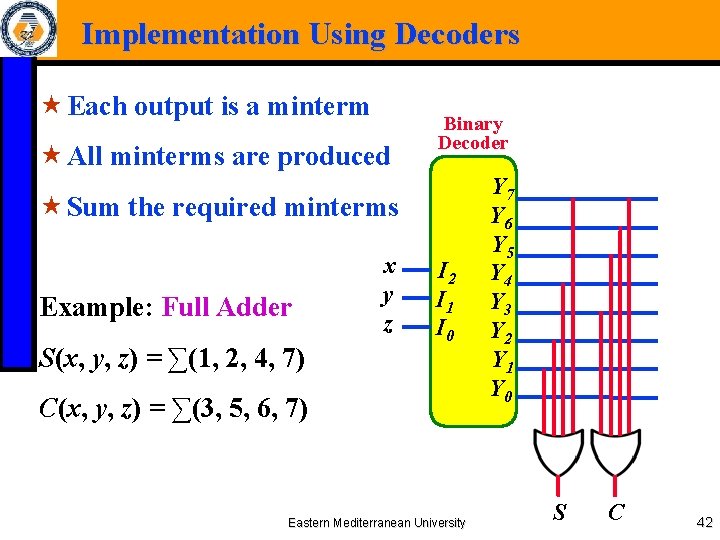

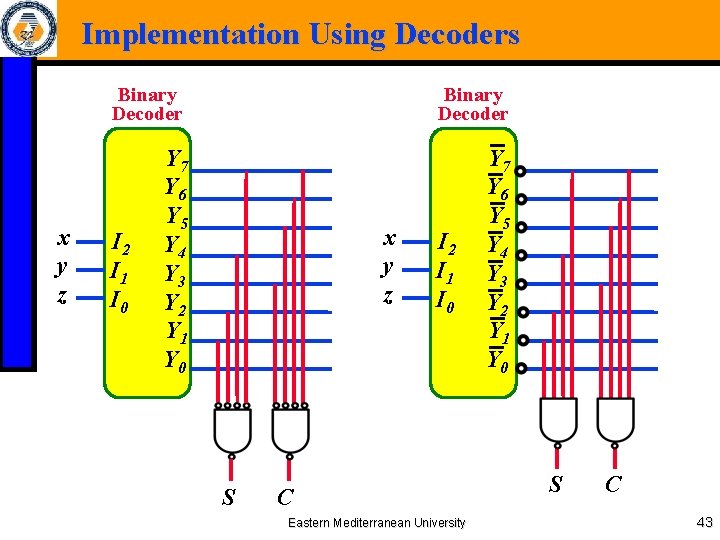

Implementation Using Decoders « Each output is a minterm « All minterms are produced Binary Decoder « Sum the required minterms Example: Full Adder S(x, y, z) = ∑(1, 2, 4, 7) x y z I 2 I 1 I 0 C(x, y, z) = ∑(3, 5, 6, 7) Eastern Mediterranean University Y 7 Y 6 Y 5 Y 4 Y 3 Y 2 Y 1 Y 0 S C 42

Implementation Using Decoders x y z Binary Decoder Y 7 Y 6 Y 5 Y 4 Y 3 Y 2 Y 1 Y 0 I 2 I 1 I 0 x y z S I 2 I 1 I 0 C Eastern Mediterranean University S C 43

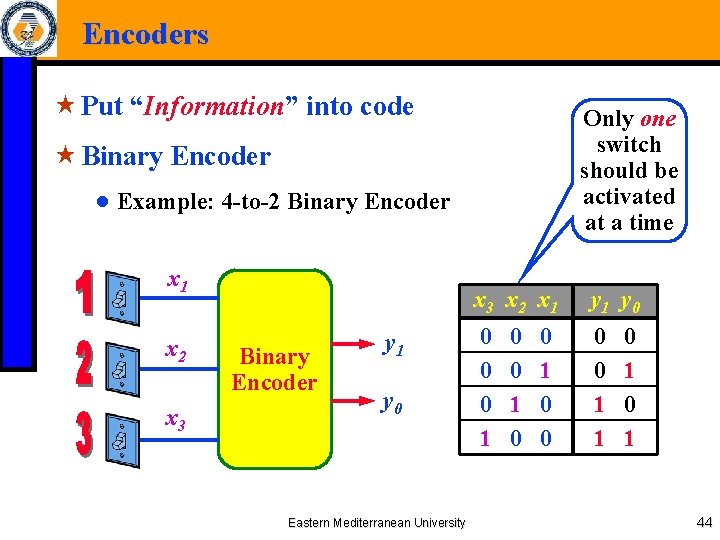

Encoders « Put “Information” into code Only one switch should be activated at a time « Binary Encoder ● Example: 4 -to-2 Binary Encoder x 1 x 2 x 3 Binary Encoder y 1 y 0 Eastern Mediterranean University x 3 x 2 x 1 y 0 0 1 0 0 1 0 1 44

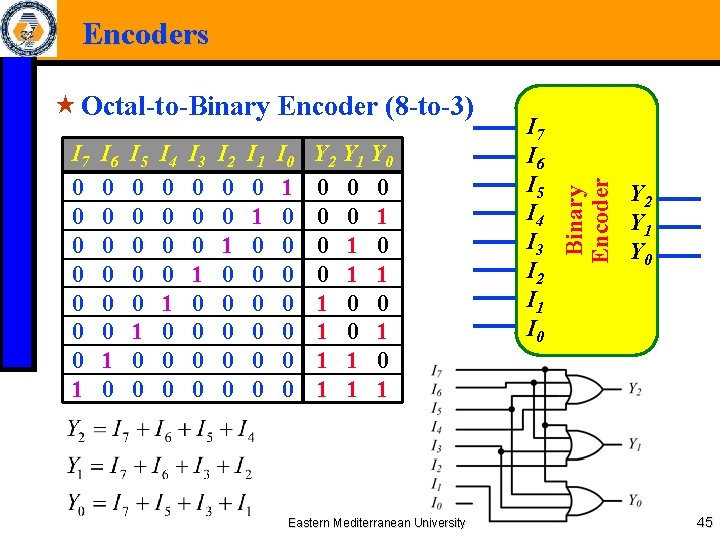

« Octal-to-Binary Encoder (8 -to-3) I 7 0 0 0 0 1 I 6 0 0 0 1 0 I 5 0 0 0 1 0 0 I 4 0 0 1 0 0 0 I 3 0 0 0 1 0 0 I 2 0 0 1 0 0 0 I 1 0 0 0 0 I 0 1 0 0 0 0 Y 2 Y 1 Y 0 0 0 1 1 1 0 0 1 1 1 Eastern Mediterranean University I 7 I 6 I 5 I 4 I 3 I 2 I 1 I 0 Binary Encoders Y 2 Y 1 Y 0 45

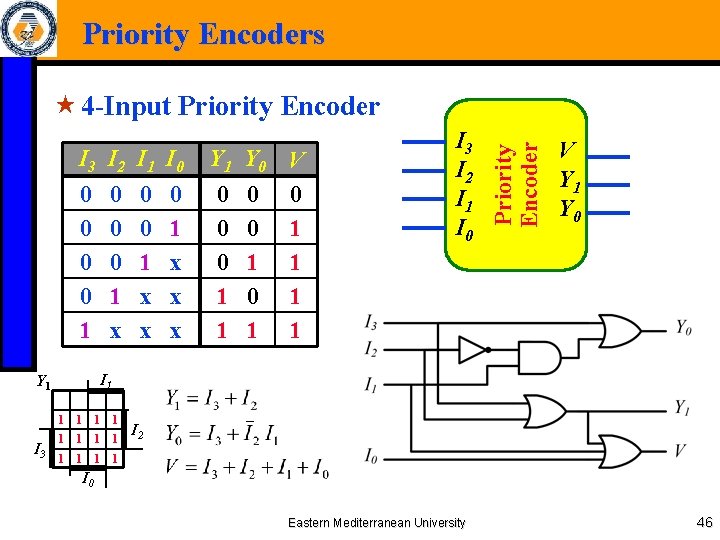

Priority Encoders I 3 I 2 I 1 I 0 0 0 1 x x x V Y 1 Y 0 I 1 Y 1 1 1 I 3 0 0 1 x x Y 1 Y 0 V 0 0 0 1 1 1 0 1 1 I 3 I 2 I 1 I 0 Priority Encoder « 4 -Input Priority Encoder 1 1 I 2 1 1 I 0 Eastern Mediterranean University 46

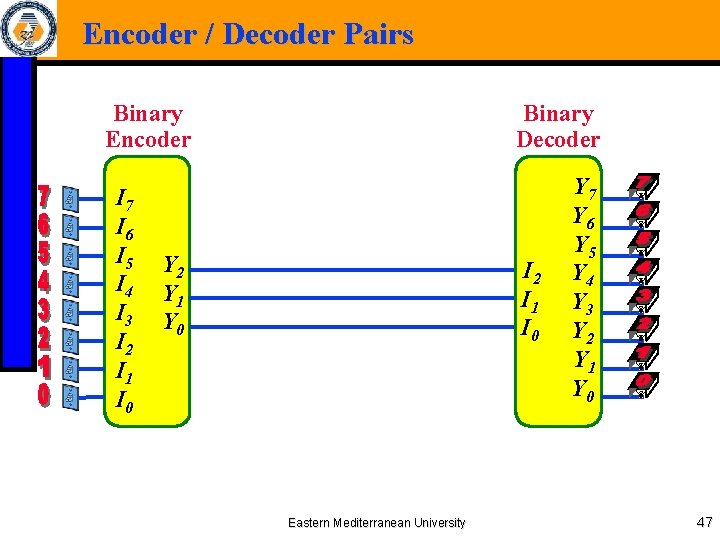

Encoder / Decoder Pairs Binary Encoder I 7 I 6 I 5 I 4 I 3 I 2 I 1 I 0 Binary Decoder Y 2 Y 1 Y 0 I 2 I 1 I 0 Eastern Mediterranean University Y 7 Y 6 Y 5 Y 4 Y 3 Y 2 Y 1 Y 0 47

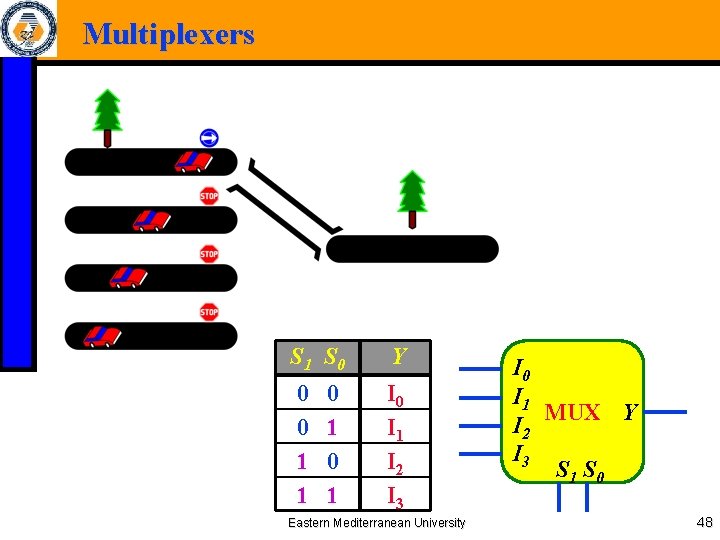

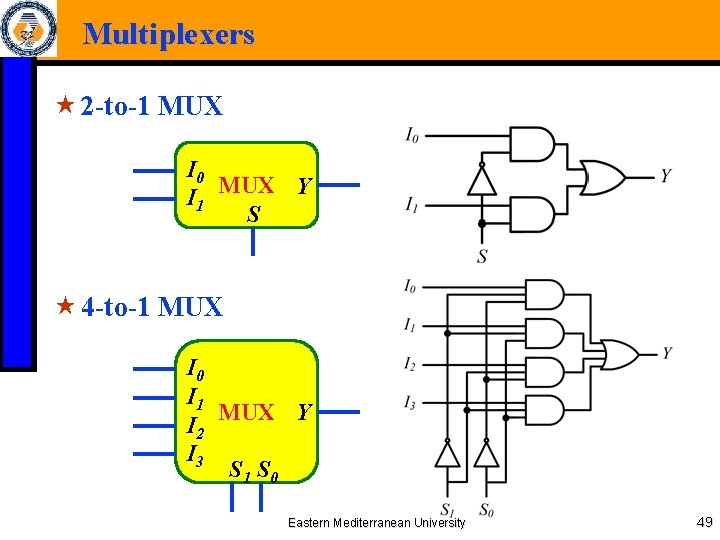

Multiplexers S 1 S 0 Y 0 0 1 1 I 0 I 1 I 2 I 3 0 1 Eastern Mediterranean University I 0 I 1 MUX Y I 2 I 3 S 1 S 0 48

Multiplexers « 2 -to-1 MUX I 0 MUX Y I 1 S « 4 -to-1 MUX I 0 I 1 MUX Y I 2 I 3 S 1 S 0 Eastern Mediterranean University 49

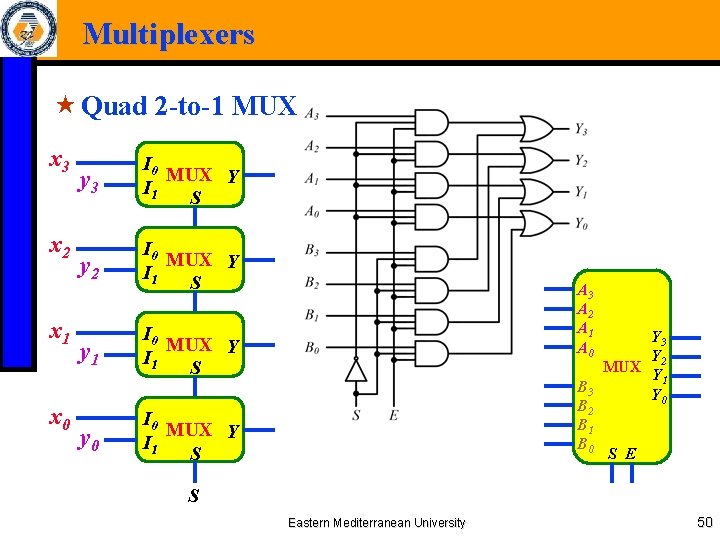

Multiplexers « Quad 2 -to-1 MUX x 3 x 2 x 1 x 0 y 3 I 0 MUX Y I 1 S y 2 I 0 MUX Y I 1 S y 1 I 0 MUX Y I 1 S y 0 I 0 MUX Y I 1 S A 3 A 2 A 1 A 0 Y 3 Y MUX 2 Y 1 B 3 Y 0 B 2 B 1 B 0 S Eastern Mediterranean University 50

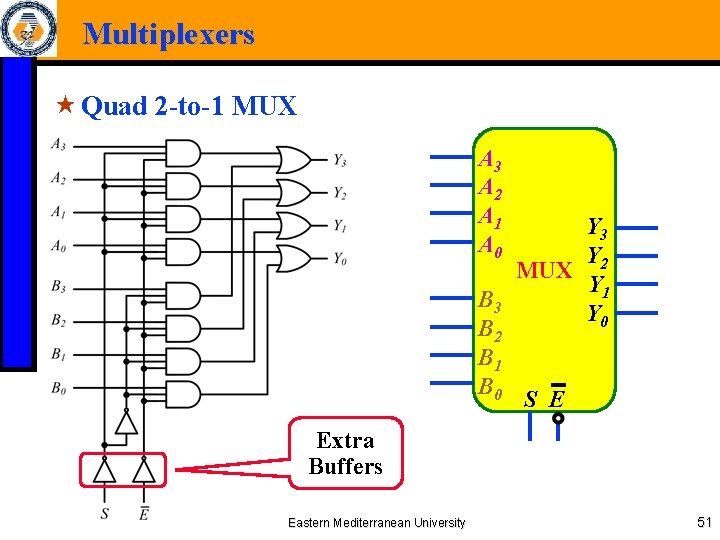

Multiplexers « Quad 2 -to-1 MUX A 3 A 2 A 1 A 0 Y 3 Y 2 MUX Y 1 B 3 Y 0 B 2 B 1 B 0 S E Extra Buffers Eastern Mediterranean University 51

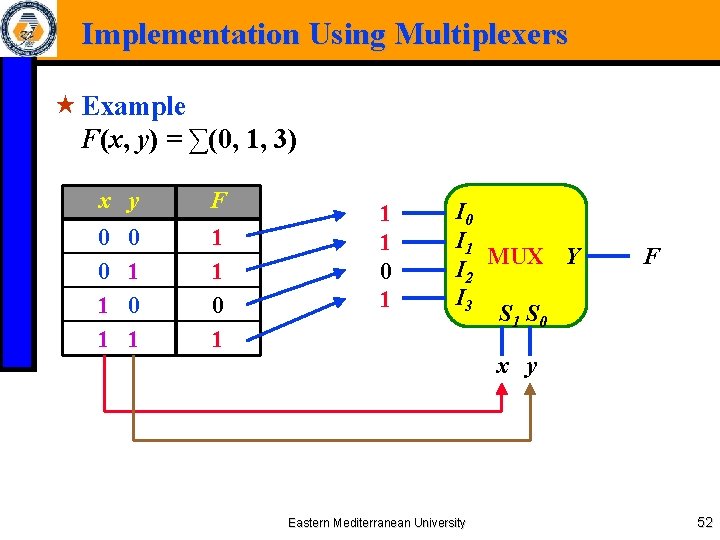

Implementation Using Multiplexers « Example F(x, y) = ∑(0, 1, 3) x y F 0 0 1 1 0 1 0 1 1 1 0 1 I 0 I 1 MUX Y I 2 I 3 S 1 S 0 F x y Eastern Mediterranean University 52

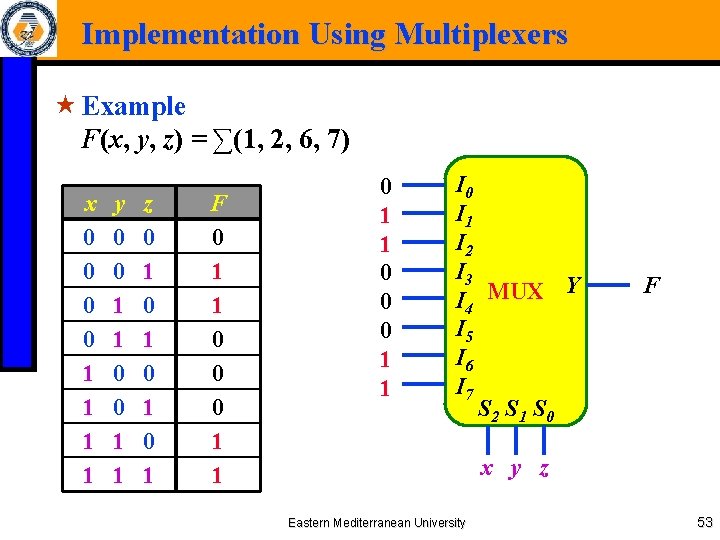

Implementation Using Multiplexers « Example F(x, y, z) = ∑(1, 2, 6, 7) x 0 0 1 1 y 0 0 1 1 z 0 1 0 1 F 0 1 1 0 0 0 1 1 I 0 I 1 I 2 I 3 Y I 4 MUX I 5 I 6 I 7 S 2 S 1 S 0 F x y z Eastern Mediterranean University 53

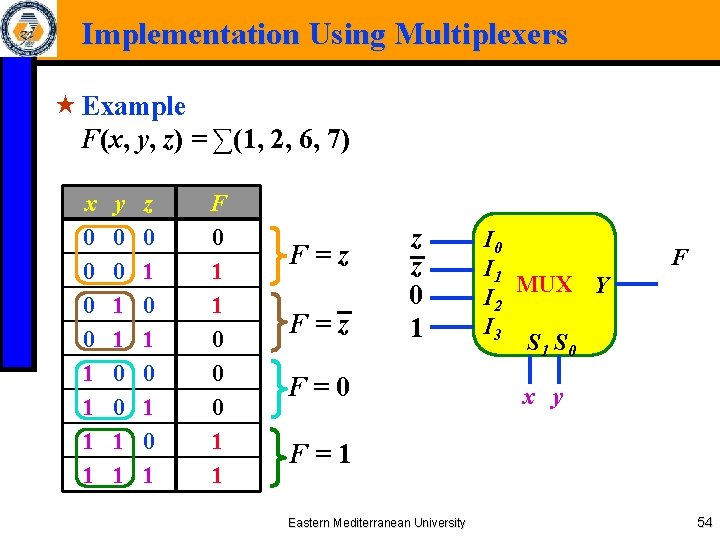

Implementation Using Multiplexers « Example F(x, y, z) = ∑(1, 2, 6, 7) x 0 0 1 1 y 0 0 1 1 z 0 1 0 1 F 0 1 1 0 0 0 1 1 F=z z z 0 1 F=0 I 1 MUX Y I 2 I 3 S 1 S 0 F x y F=1 Eastern Mediterranean University 54

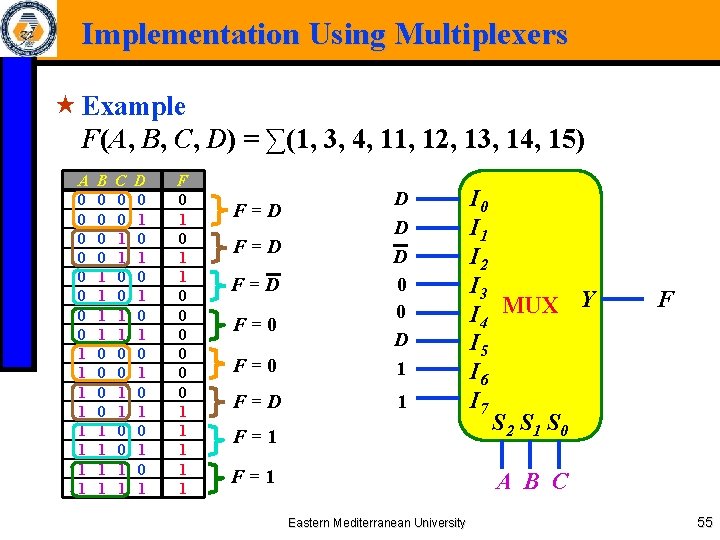

Implementation Using Multiplexers « Example F(A, B, C, D) = ∑(1, 3, 4, 11, 12, 13, 14, 15) A 0 0 0 0 1 1 1 1 B 0 0 0 0 1 1 1 1 C 0 0 1 1 D 0 1 0 1 F 0 1 1 0 0 0 1 1 1 F=1 I 0 I 1 I 2 I 3 Y MUX I 4 I 5 I 6 I 7 S 2 S 1 S 0 F=1 A B C F=0 D D D 0 0 D 1 F=D F=D F=0 Eastern Mediterranean University F 55

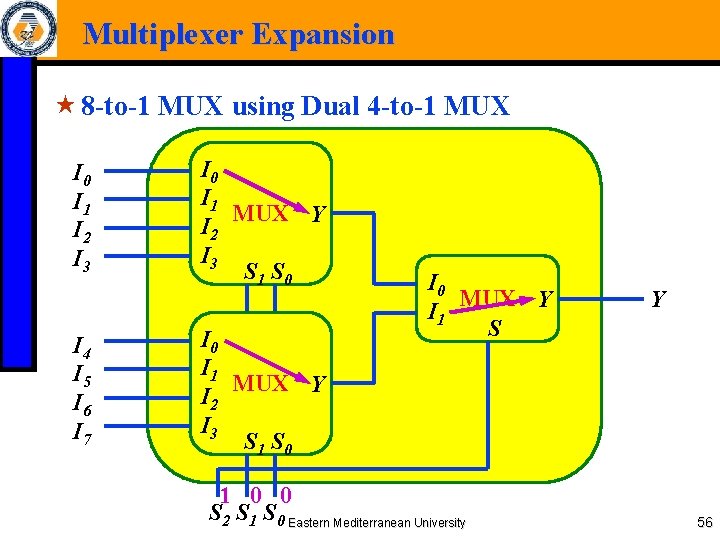

Multiplexer Expansion « 8 -to-1 MUX using Dual 4 -to-1 MUX I 0 I 1 I 2 I 3 I 4 I 5 I 6 I 7 I 0 I 1 MUX Y I 2 I 3 S 1 S 0 I 0 MUX Y I 1 S 1 0 0 S 2 S 1 S 0 Eastern Mediterranean University Y 56

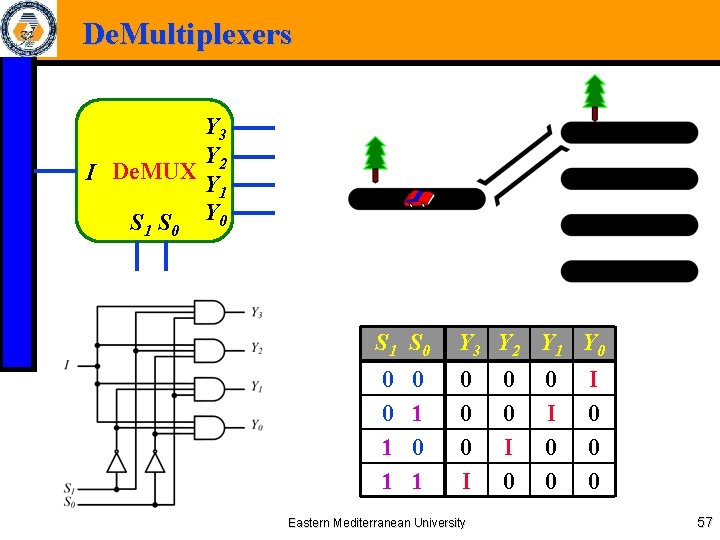

De. Multiplexers Y 3 Y 2 I De. MUX Y 1 S S Y 0 1 0 S 1 S 0 Y 3 Y 2 Y 1 Y 0 0 0 1 1 0 0 0 I 0 1 Eastern Mediterranean University 0 0 I 0 0 0 57

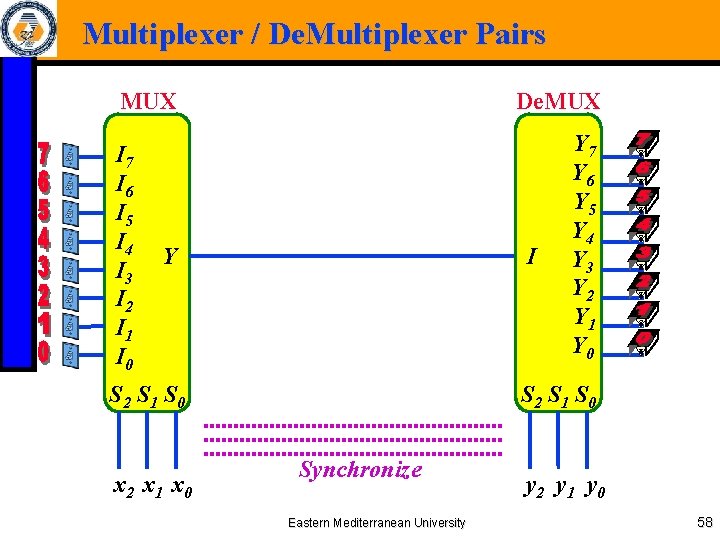

Multiplexer / De. Multiplexer Pairs MUX I 7 I 6 I 5 I 4 I 3 I 2 I 1 I 0 De. MUX Y I S 2 S 1 S 0 x 2 x 1 x 0 Y 7 Y 6 Y 5 Y 4 Y 3 Y 2 Y 1 Y 0 S 2 S 1 S 0 Synchronize Eastern Mediterranean University y 2 y 1 y 0 58

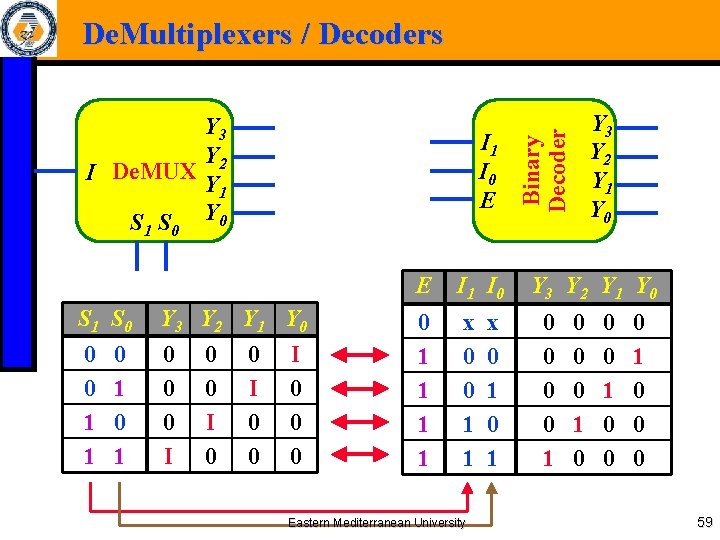

De. Multiplexers / Decoders 1 I 0 E 0 S 1 S 0 Y 3 Y 2 Y 1 Y 0 0 0 1 1 0 0 0 I 0 1 Y 3 Y 2 Y 1 Y 0 Binary Decoder Y 3 Y 2 I De. MUX Y 1 S S Y 0 0 0 I 0 0 0 E I 1 I 0 0 1 1 x 0 0 1 1 Eastern Mediterranean University x 0 1 Y 3 Y 2 Y 1 Y 0 0 0 1 0 0 0 59

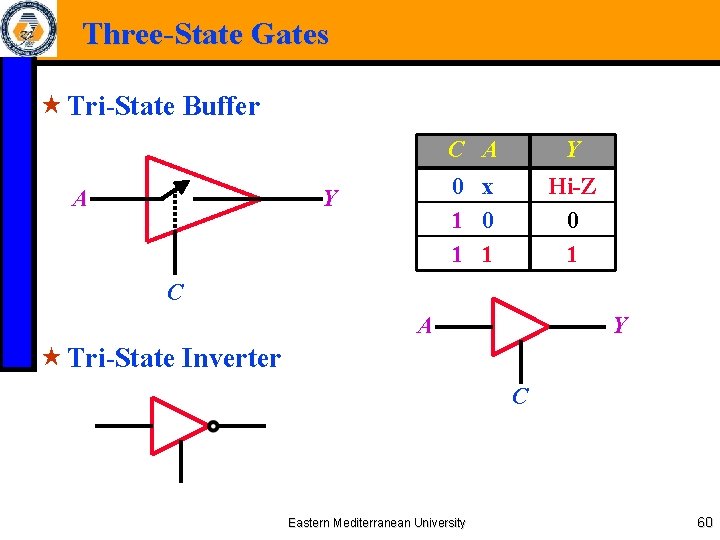

Three-State Gates « Tri-State Buffer A Y C A Y 0 x 1 0 1 1 Hi-Z 0 1 C A Y « Tri-State Inverter C Eastern Mediterranean University 60

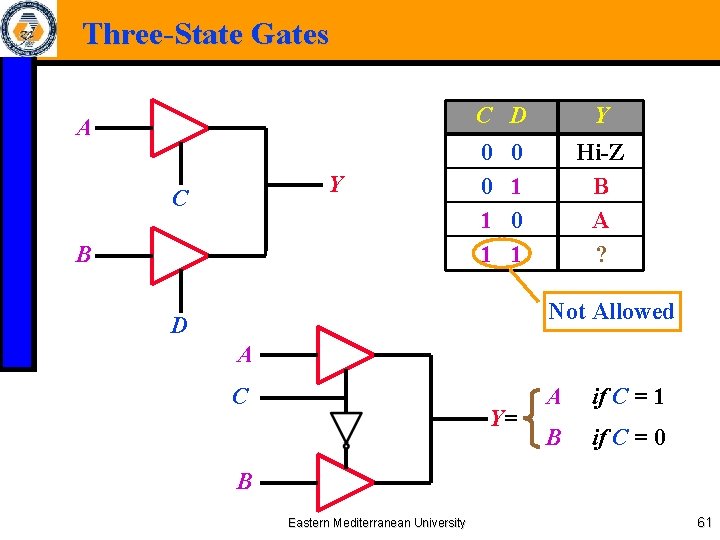

Three-State Gates C D A Y C B 0 0 1 1 Y 0 1 Hi-Z B A ? Not Allowed D A C Y= A if C = 1 B if C = 0 B Eastern Mediterranean University 61

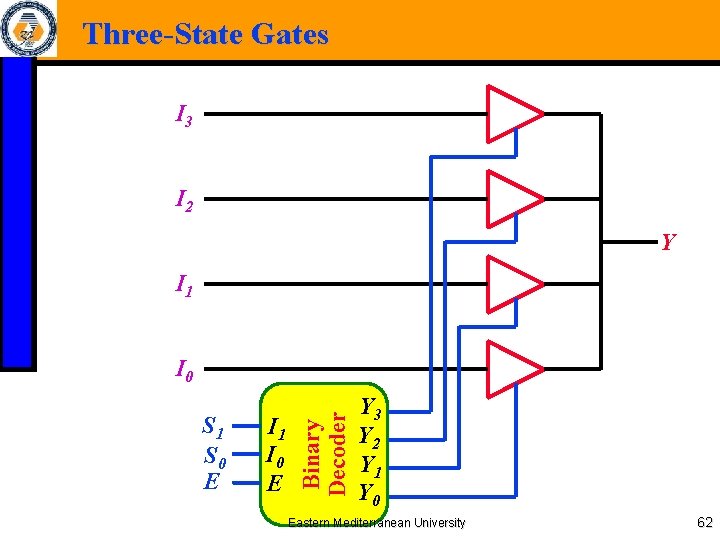

Three-State Gates I 3 I 2 Y I 1 S 0 E I 1 I 0 E Binary Decoder I 0 Y 3 Y 2 Y 1 Y 0 Eastern Mediterranean University 62

- Slides: 63