Digital Integrated Circuits A Design Perspective Jan M

- Slides: 31

Digital Integrated Circuits A Design Perspective Jan M. Rabaey Anantha Chandrakasan Borivoje Nikolic Designing Sequential Logic Circuits November 2002 © Digital Integrated Circuits 2 nd Sequential Circuits

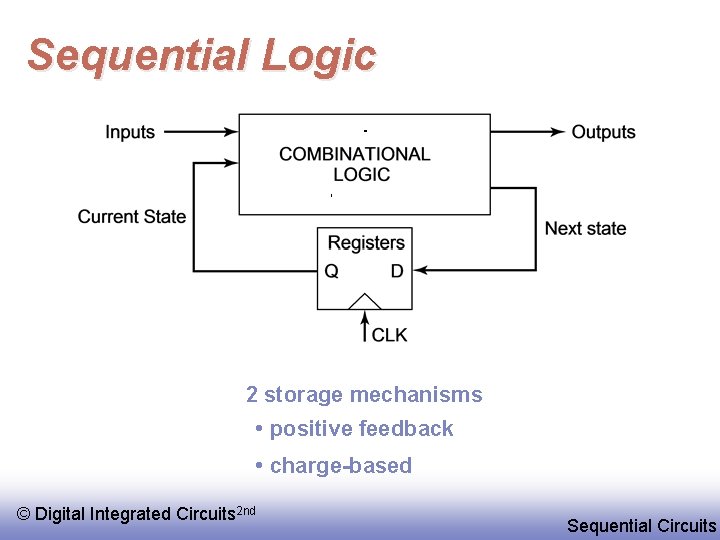

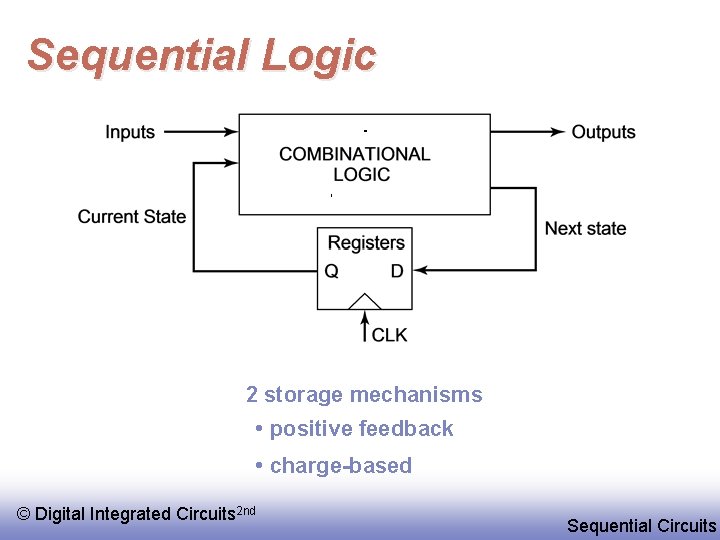

Sequential Logic 2 storage mechanisms • positive feedback • charge-based © Digital Integrated Circuits 2 nd Sequential Circuits

Naming Conventions q In our text: § a latch is level sensitive § a register is edge-triggered q There are many different naming conventions § For instance, many books call edgetriggered elements flip-flops § This leads to confusion however © Digital Integrated Circuits 2 nd Sequential Circuits

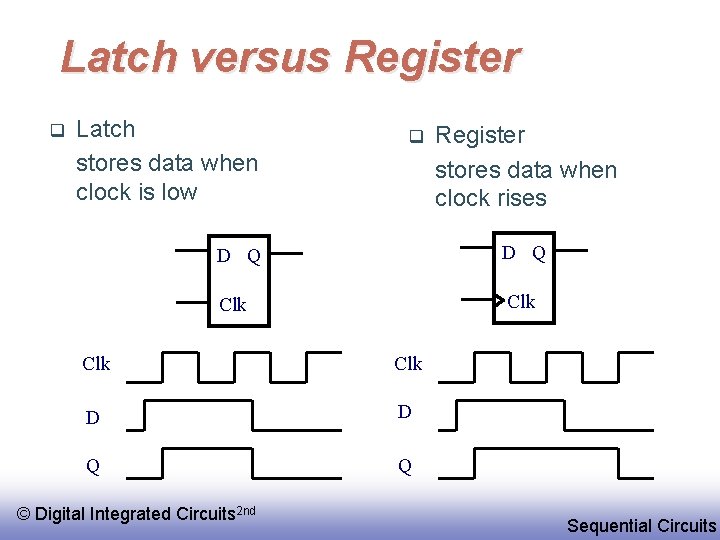

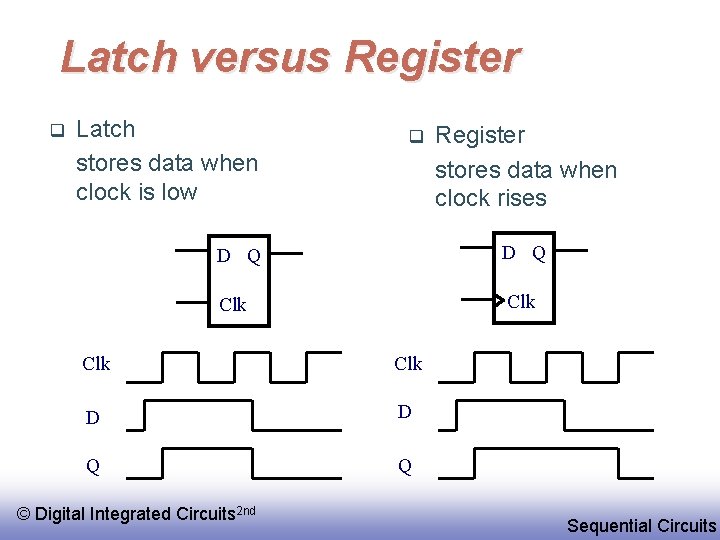

Latch versus Register q Latch stores data when clock is low q Register stores data when clock rises D Q Clk Clk D D Q Q © Digital Integrated Circuits 2 nd Sequential Circuits

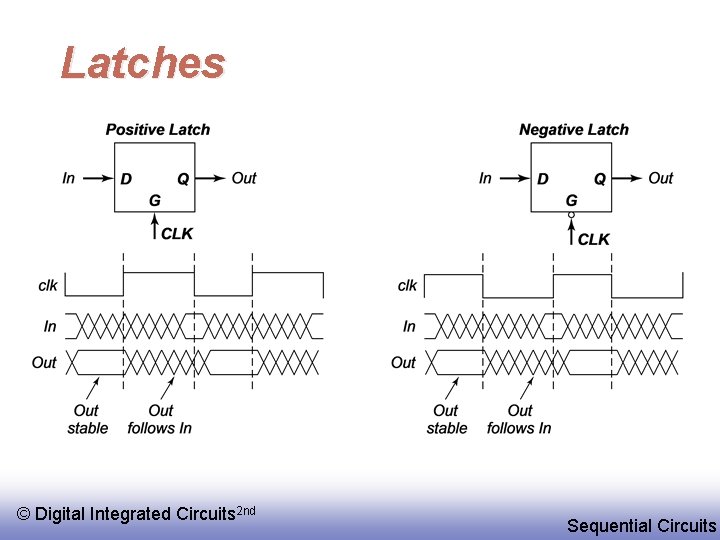

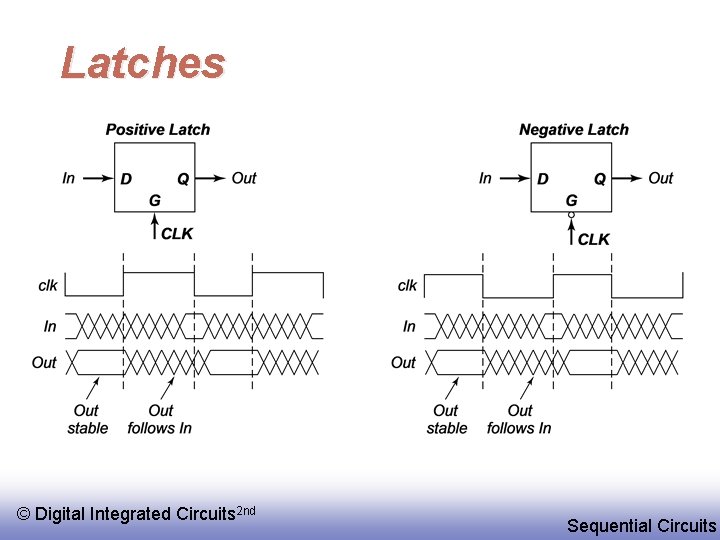

Latches © Digital Integrated Circuits 2 nd Sequential Circuits

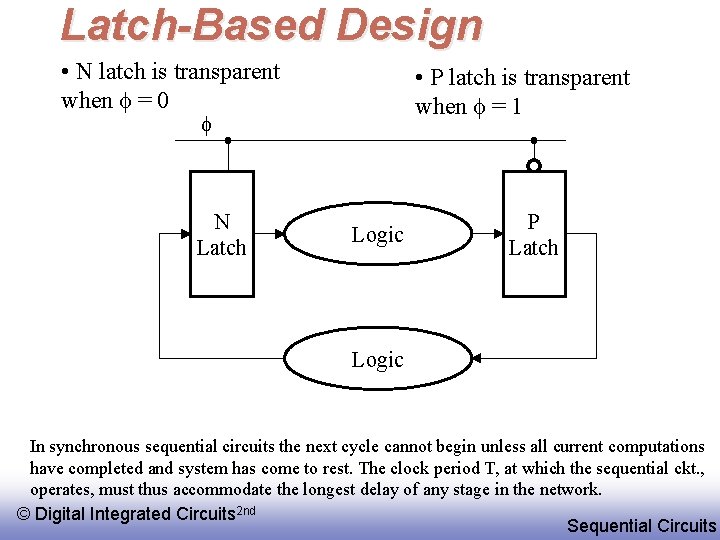

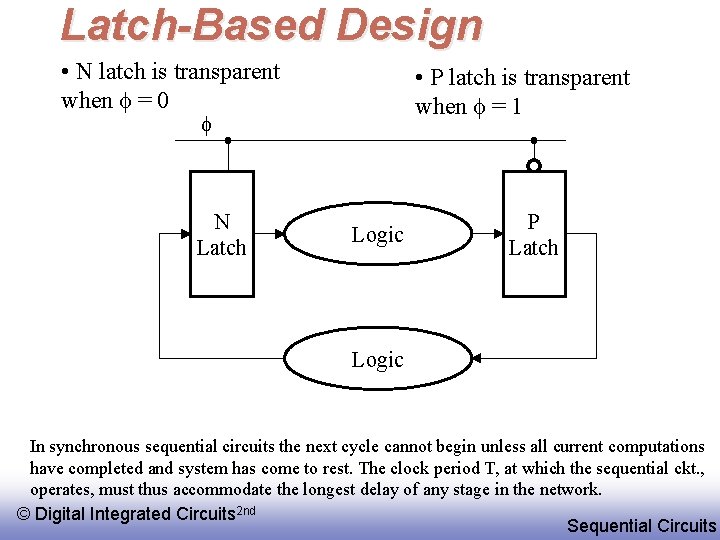

Latch-Based Design • N latch is transparent when f = 0 • P latch is transparent when f = 1 f N Latch Logic P Latch Logic In synchronous sequential circuits the next cycle cannot begin unless all current computations have completed and system has come to rest. The clock period T, at which the sequential ckt. , operates, must thus accommodate the longest delay of any stage in the network. © Digital Integrated Circuits 2 nd Sequential Circuits

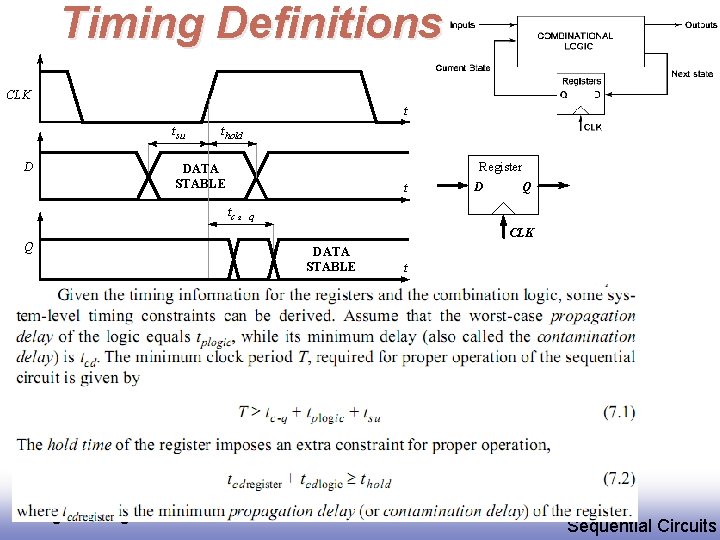

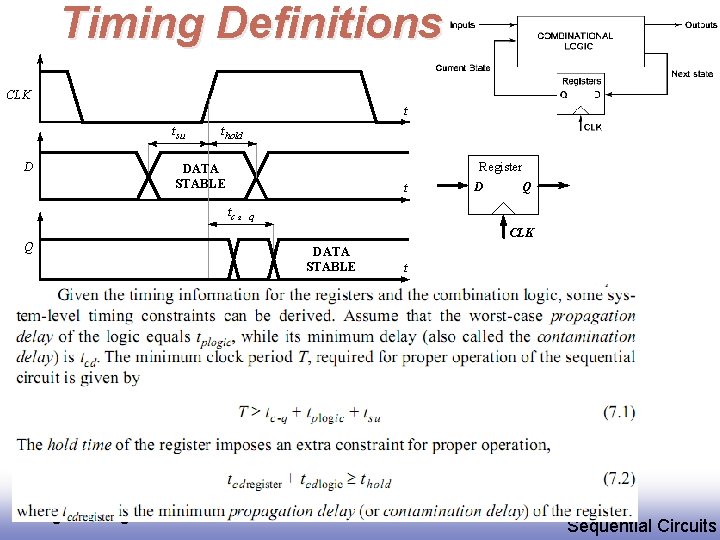

Timing Definitions CLK t tsu D thold Register DATA STABLE t tc 2 D Q q Q © Digital Integrated Circuits 2 nd CLK DATA STABLE t Sequential Circuits

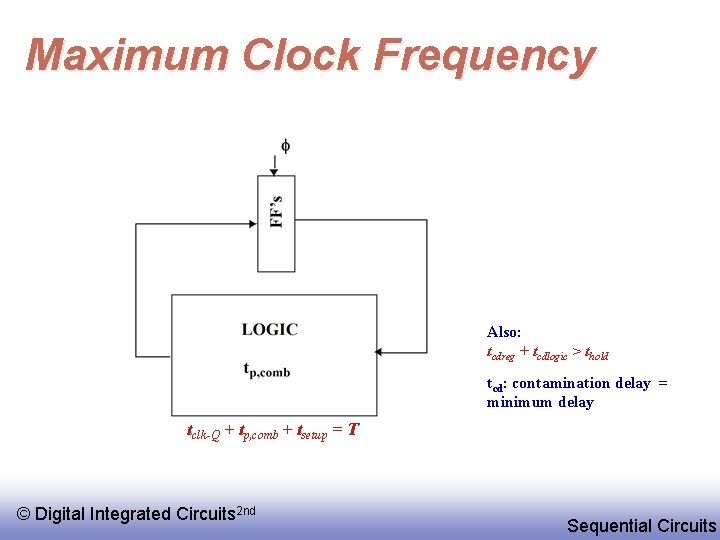

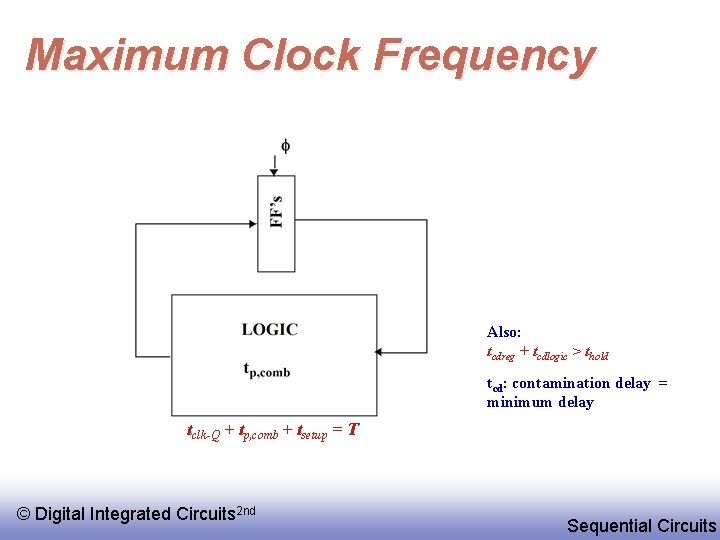

Maximum Clock Frequency Also: tcdreg + tcdlogic > thold tcd: contamination delay = minimum delay tclk-Q + tp, comb + tsetup = T © Digital Integrated Circuits 2 nd Sequential Circuits

Static versus Dynamic Memory -Feedback loop stores data till power is supplied -Data stored on capacitor (needs refreshing) © Digital Integrated Circuits 2 nd Sequential Circuits

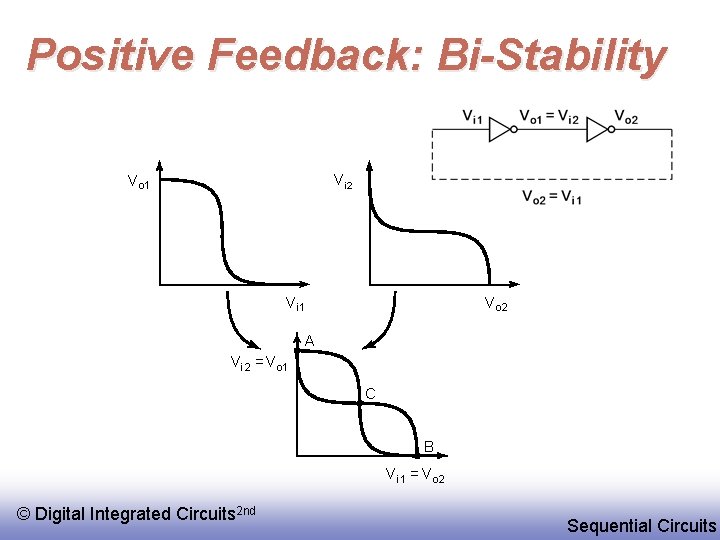

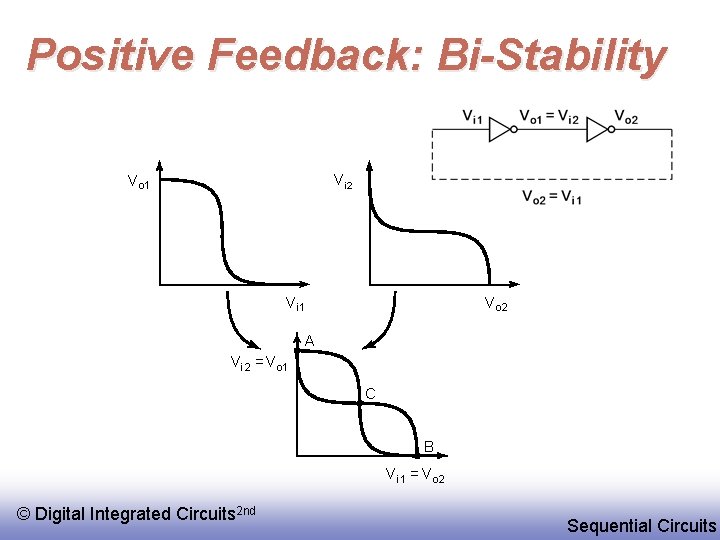

Positive Feedback: Bi-Stability Vi 2 V o 1 V i 1 V o 2 A V i 2 = V o 1 C B V i 1 = V o 2 © Digital Integrated Circuits 2 nd Sequential Circuits

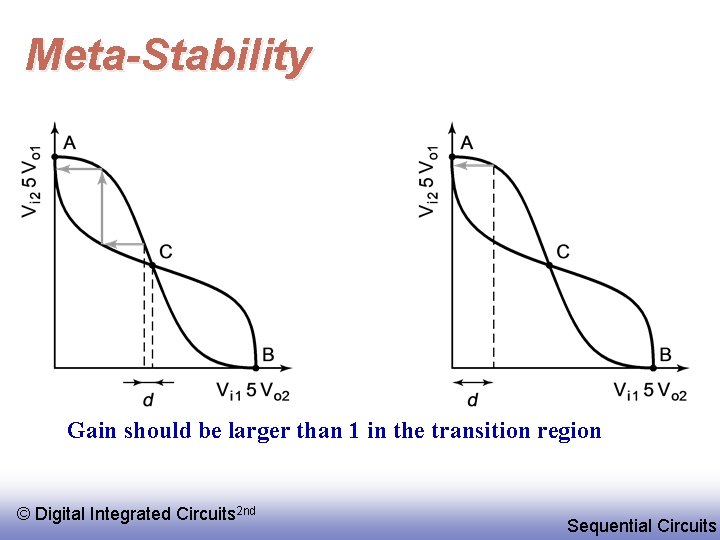

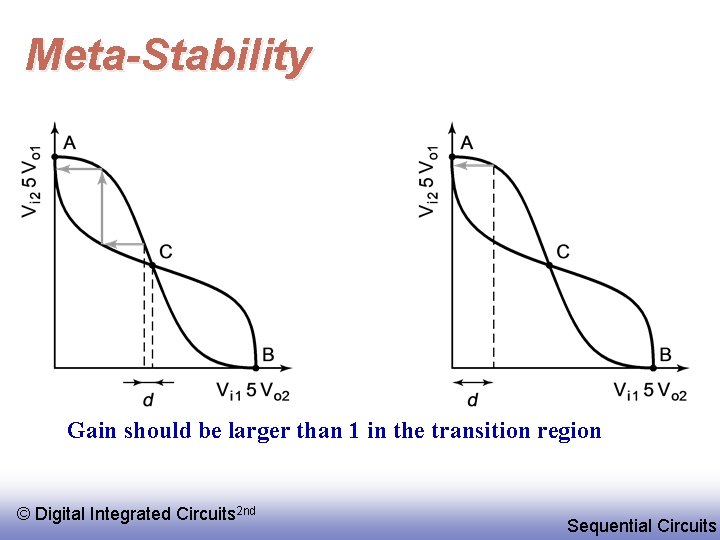

Meta-Stability Gain should be larger than 1 in the transition region © Digital Integrated Circuits 2 nd Sequential Circuits

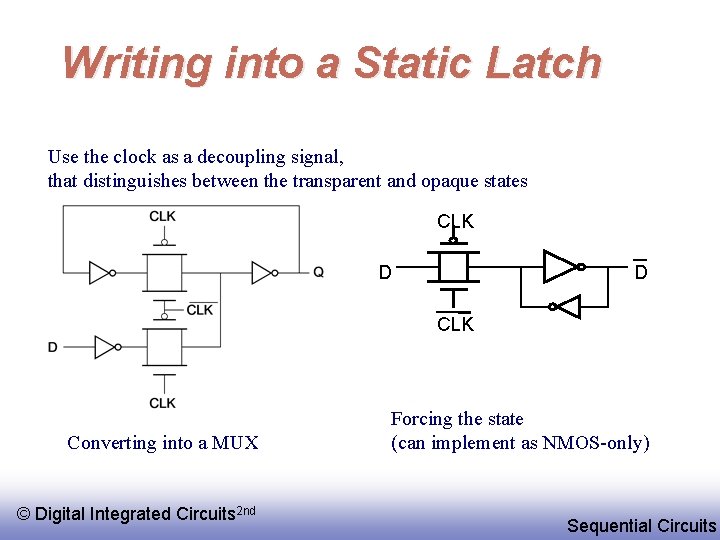

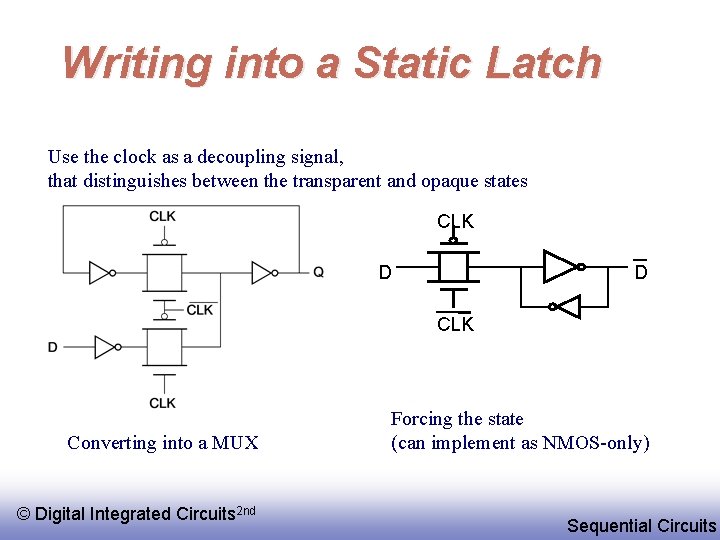

Writing into a Static Latch Use the clock as a decoupling signal, that distinguishes between the transparent and opaque states CLK D D CLK Converting into a MUX © Digital Integrated Circuits 2 nd Forcing the state (can implement as NMOS-only) Sequential Circuits

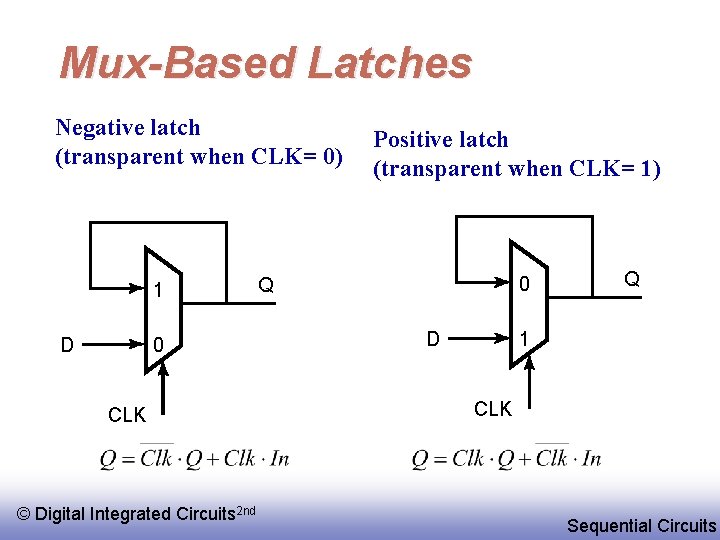

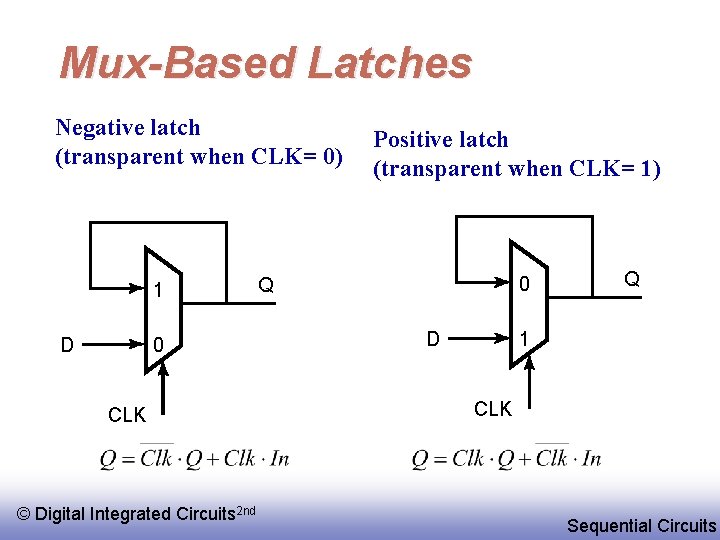

Mux-Based Latches Negative latch (transparent when CLK= 0) 1 D 0 CLK © Digital Integrated Circuits 2 nd Positive latch (transparent when CLK= 1) 0 Q D Q 1 CLK Sequential Circuits

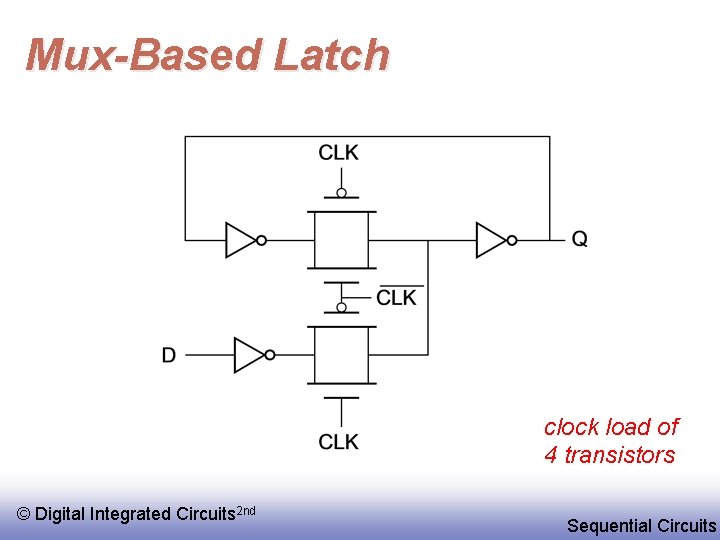

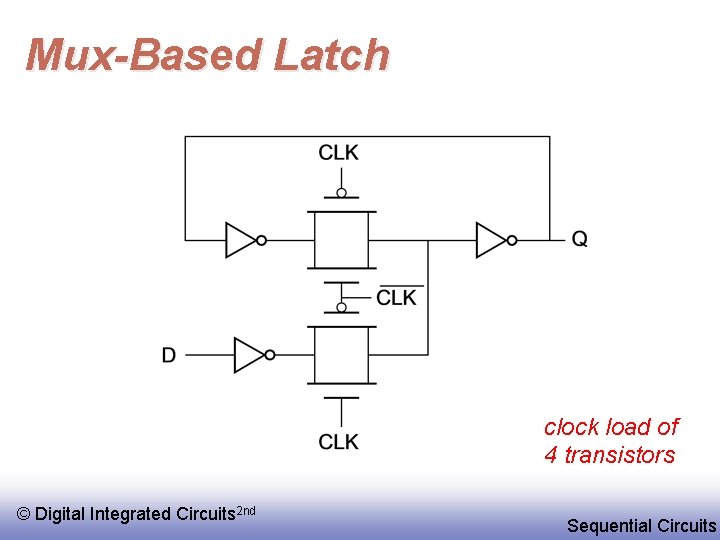

Mux-Based Latch clock load of 4 transistors © Digital Integrated Circuits 2 nd Sequential Circuits

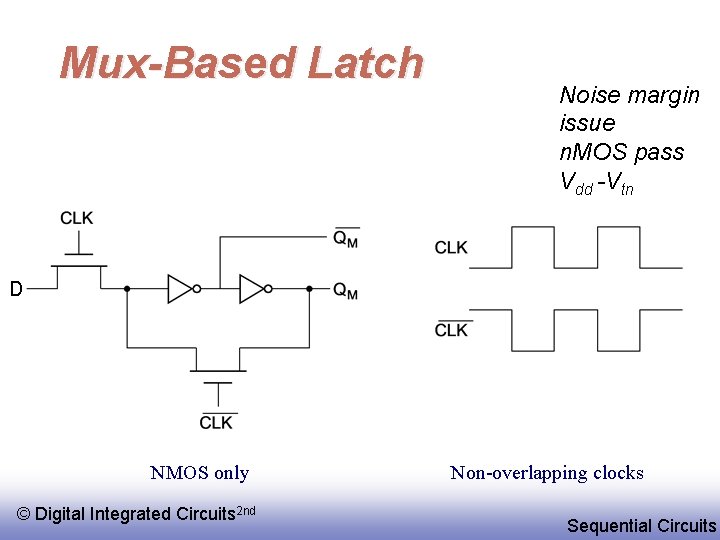

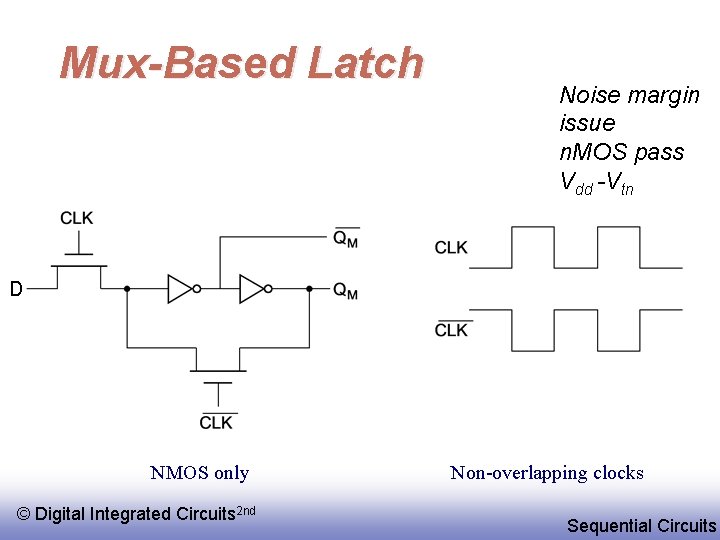

Mux-Based Latch Noise margin issue n. MOS pass Vdd -Vtn D NMOS only © Digital Integrated Circuits 2 nd Non-overlapping clocks Sequential Circuits

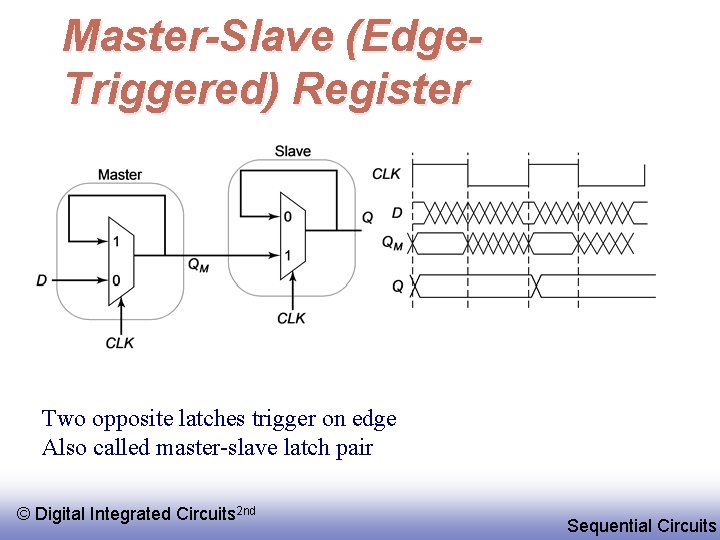

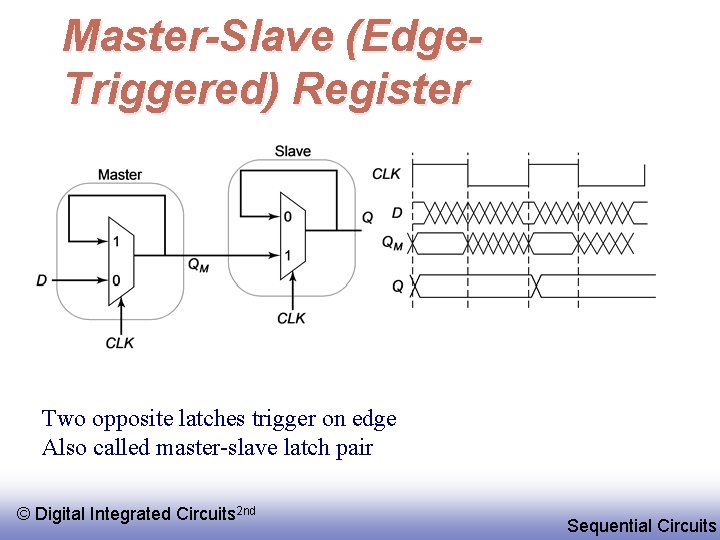

Master-Slave (Edge. Triggered) Register Two opposite latches trigger on edge Also called master-slave latch pair © Digital Integrated Circuits 2 nd Sequential Circuits

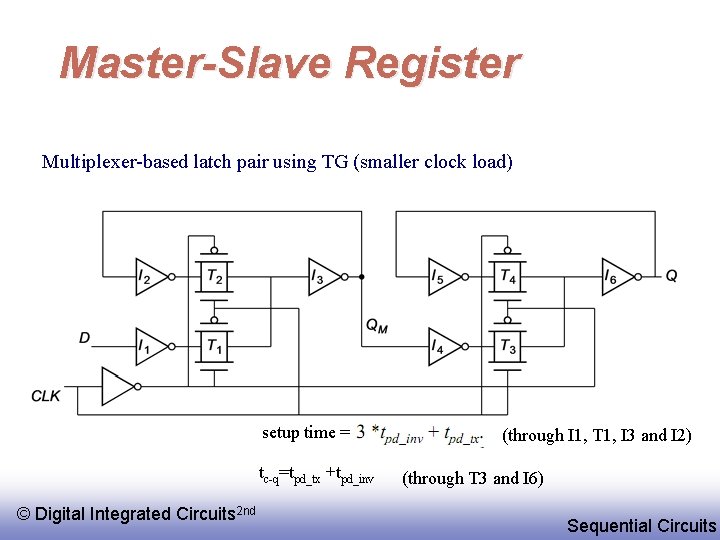

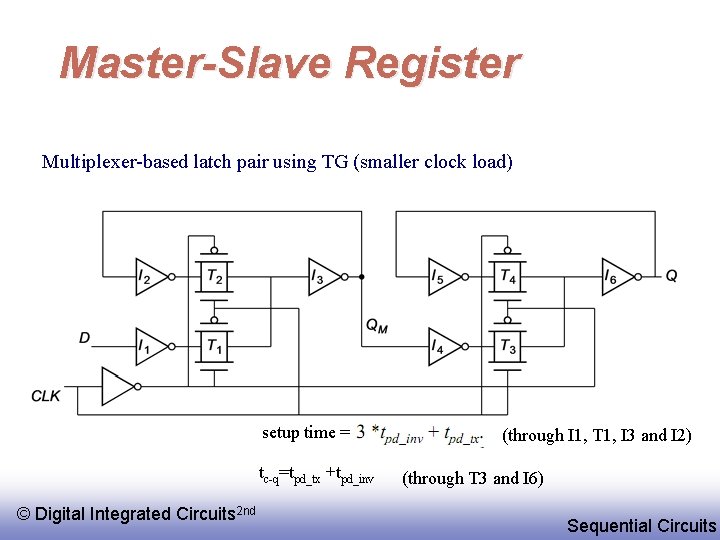

Master-Slave Register Multiplexer-based latch pair using TG (smaller clock load) setup time = tc-q=tpd_tx +tpd_inv © Digital Integrated Circuits 2 nd (through I 1, T 1, I 3 and I 2) (through T 3 and I 6) Sequential Circuits

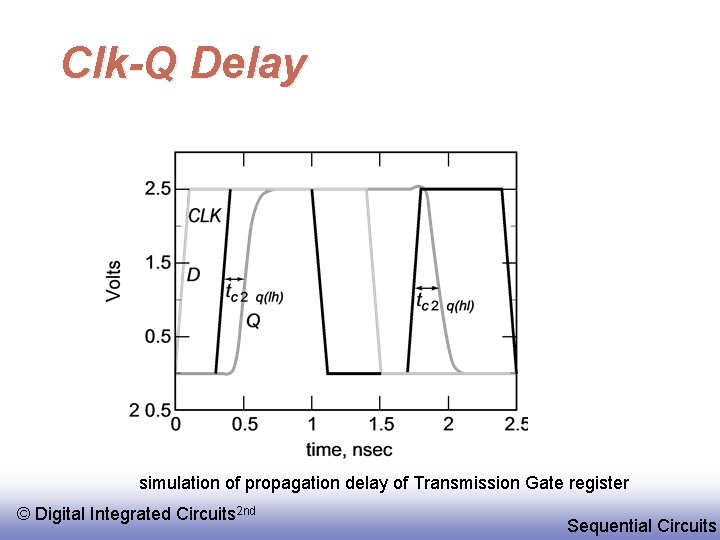

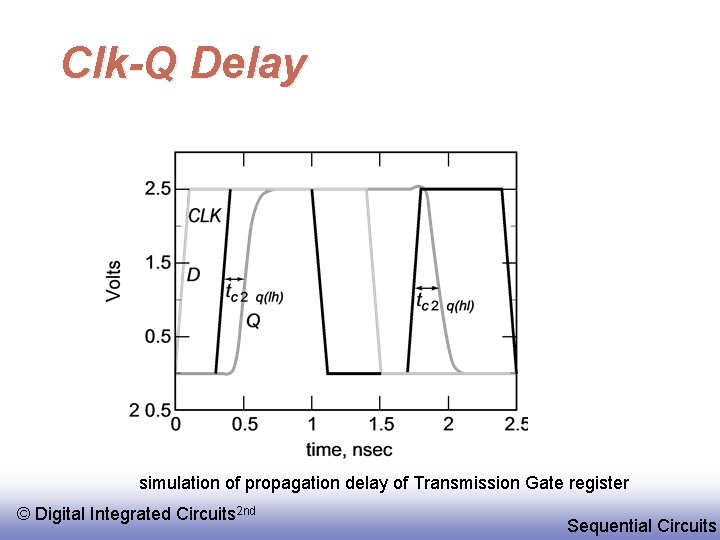

Clk-Q Delay simulation of propagation delay of Transmission Gate register © Digital Integrated Circuits 2 nd Sequential Circuits

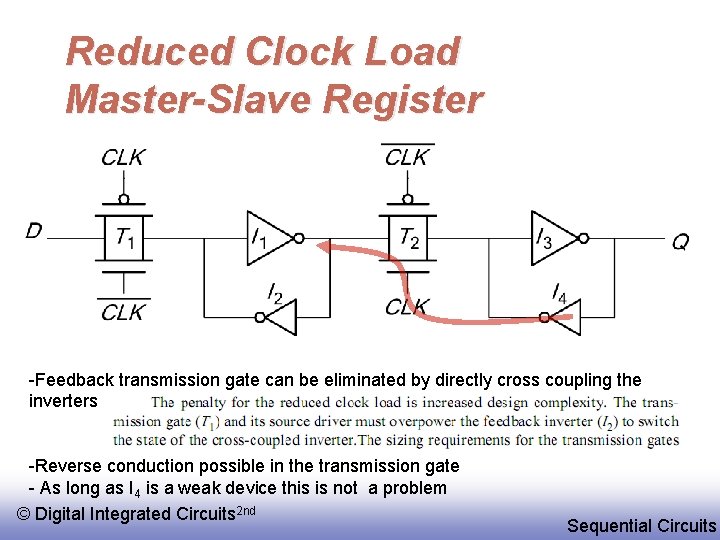

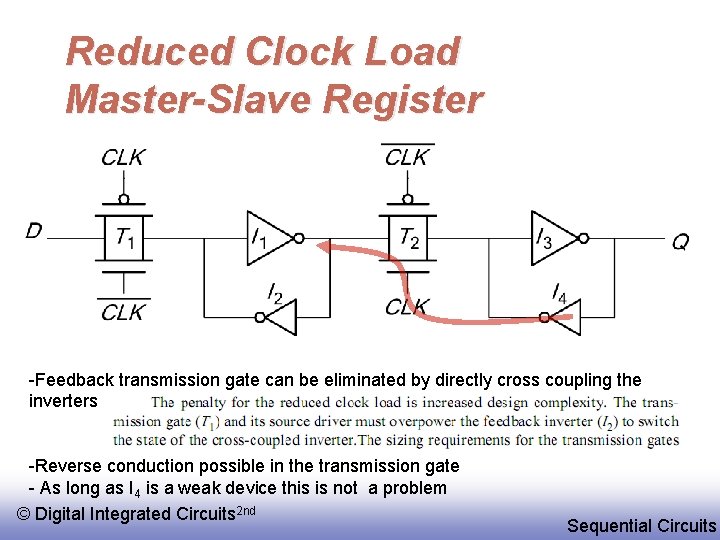

Reduced Clock Load Master-Slave Register -Feedback transmission gate can be eliminated by directly cross coupling the inverters -Reverse conduction possible in the transmission gate - As long as I 4 is a weak device this is not a problem © Digital Integrated Circuits 2 nd Sequential Circuits

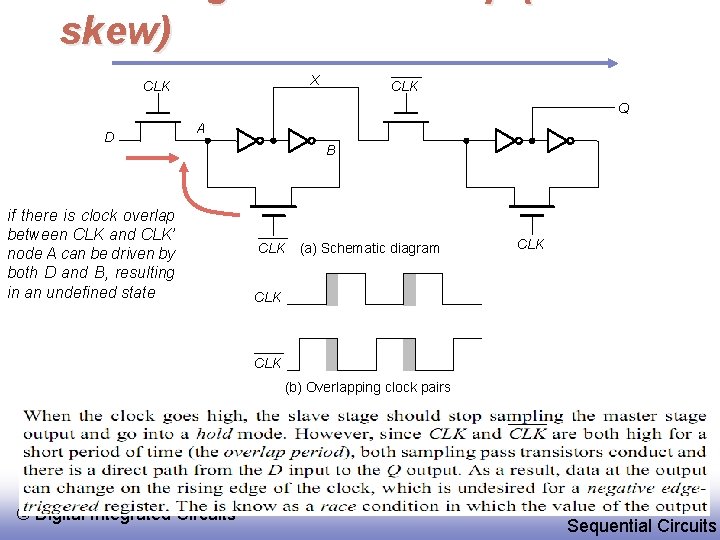

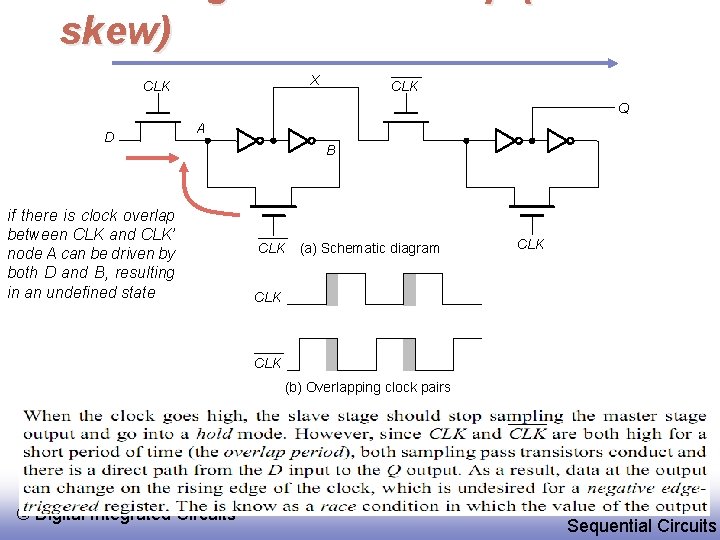

skew) X CLK Q D if there is clock overlap between CLK and CLK’ node A can be driven by both D and B, resulting in an undefined state A B CLK (a) Schematic diagram CLK CLK (b) Overlapping clock pairs © Digital Integrated Circuits 2 nd Sequential Circuits

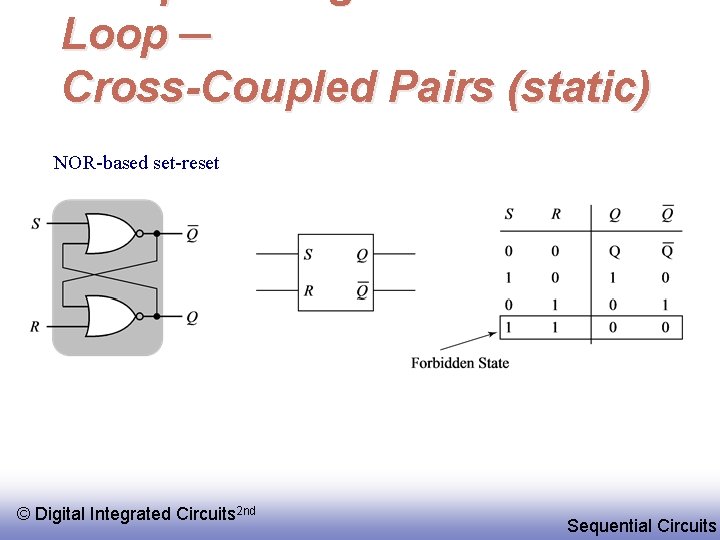

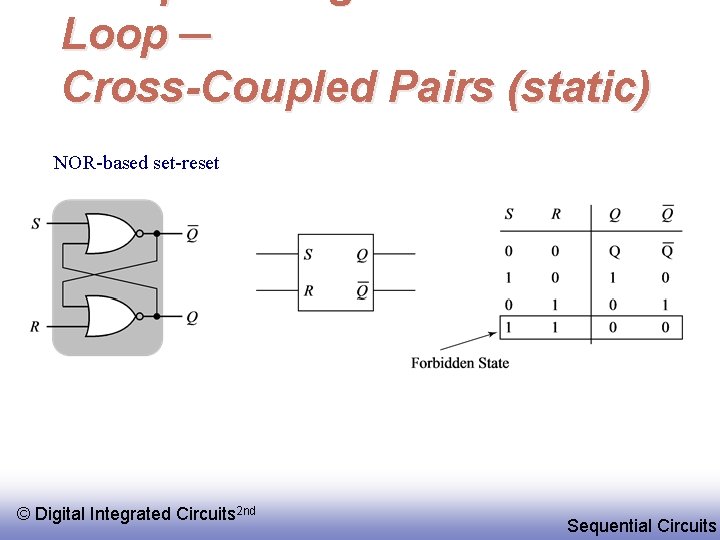

Loop ─ Cross-Coupled Pairs (static) NOR-based set-reset © Digital Integrated Circuits 2 nd Sequential Circuits

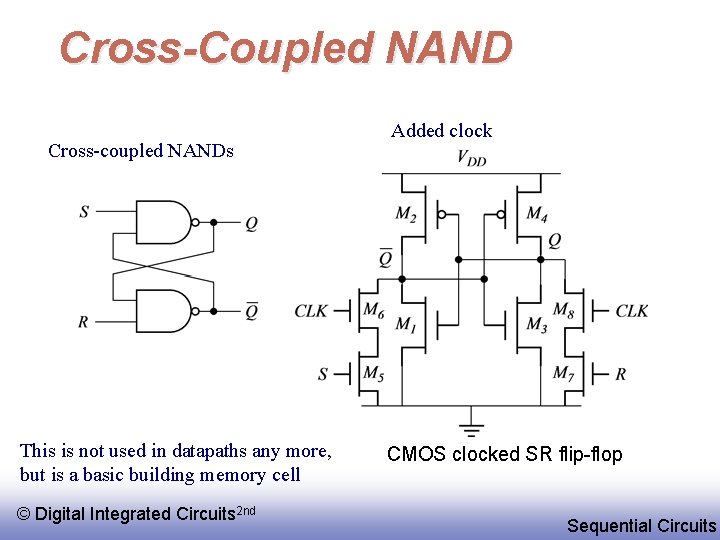

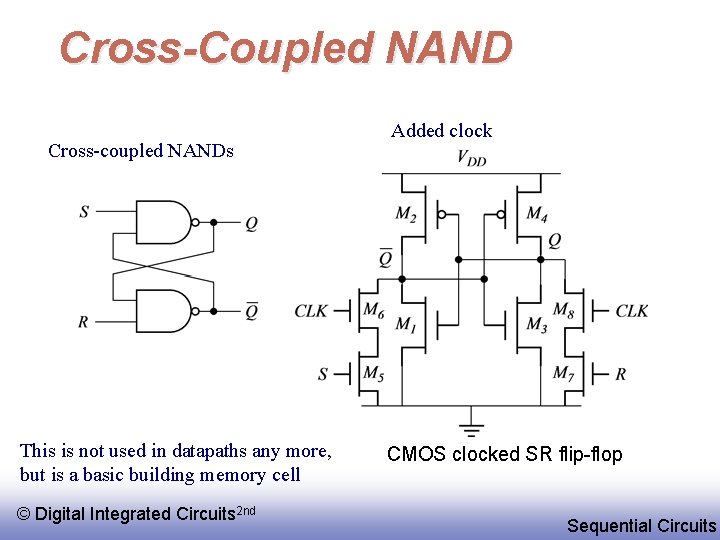

Cross-Coupled NAND Cross-coupled NANDs This is not used in datapaths any more, but is a basic building memory cell © Digital Integrated Circuits 2 nd Added clock CMOS clocked SR flip-flop Sequential Circuits

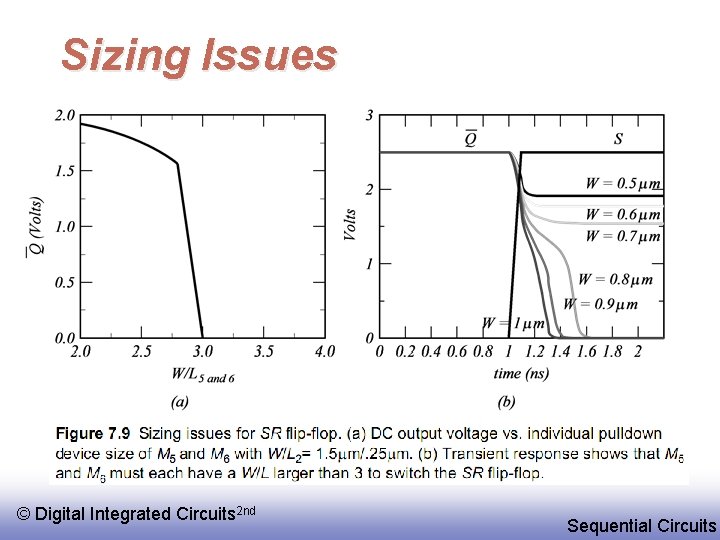

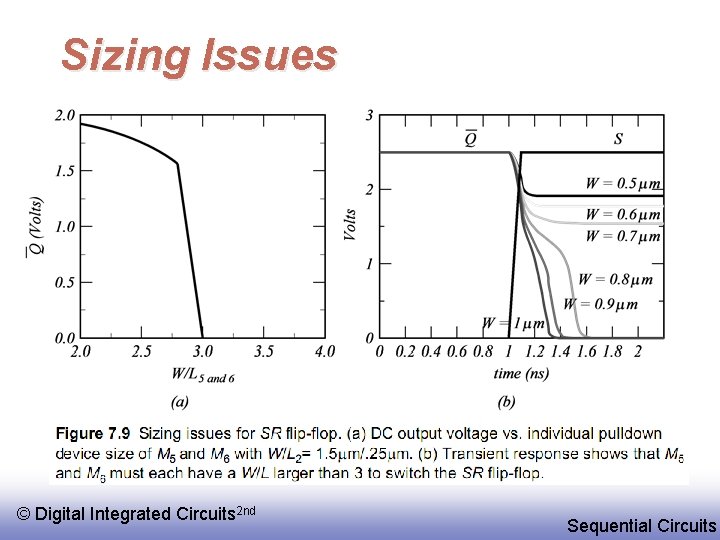

Sizing Issues Output voltage dependence on transistor width © Digital Integrated Circuits 2 nd Transient response Sequential Circuits

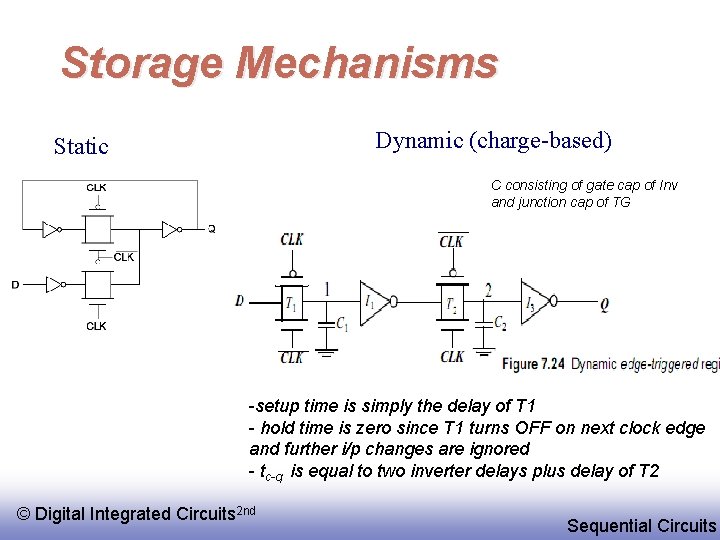

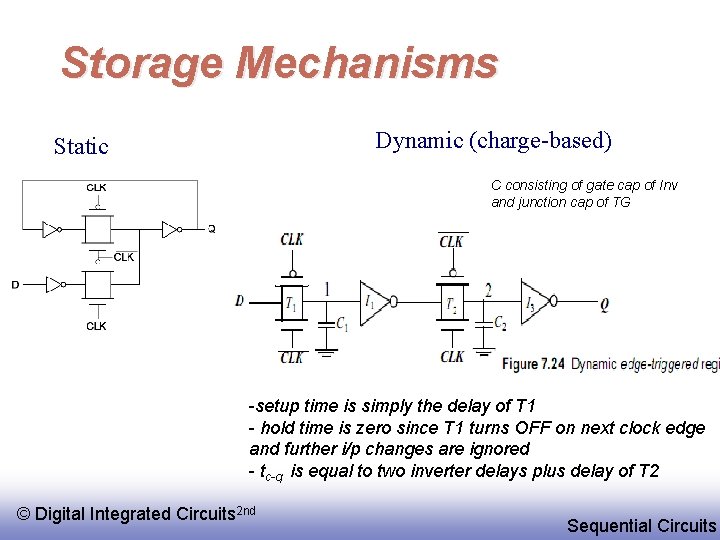

Storage Mechanisms Dynamic (charge-based) Static C consisting of gate cap of Inv and junction cap of TG -setup time is simply the delay of T 1 - hold time is zero since T 1 turns OFF on next clock edge and further i/p changes are ignored - tc-q is equal to two inverter delays plus delay of T 2 © Digital Integrated Circuits 2 nd Sequential Circuits

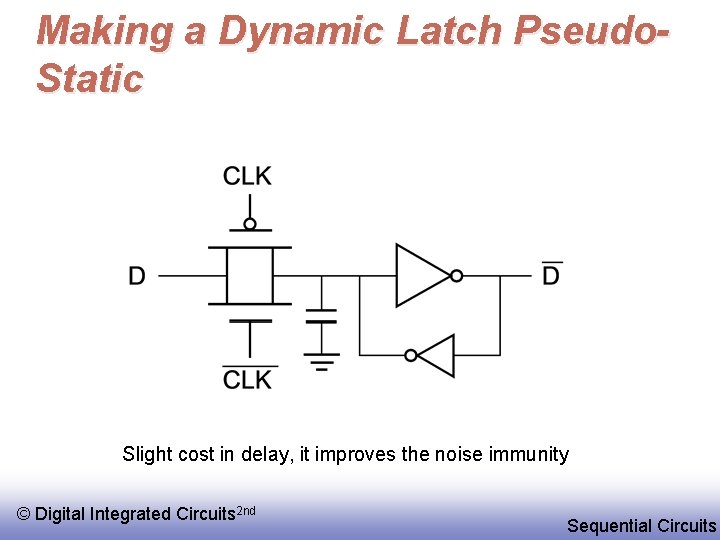

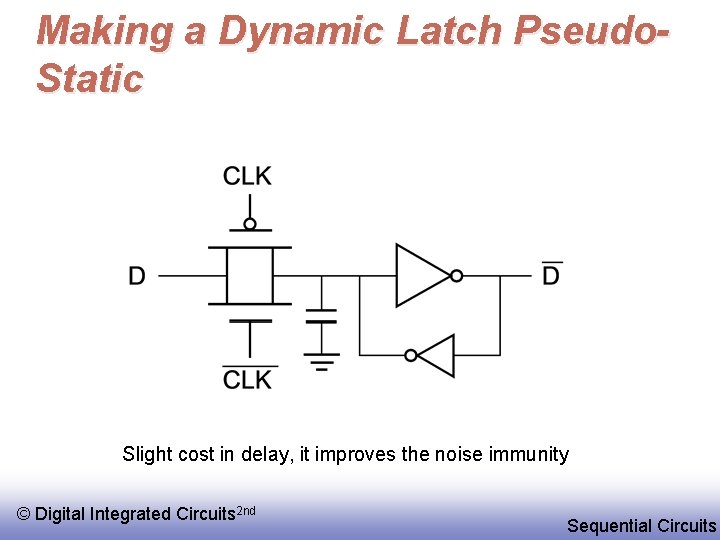

Making a Dynamic Latch Pseudo. Static Slight cost in delay, it improves the noise immunity © Digital Integrated Circuits 2 nd Sequential Circuits

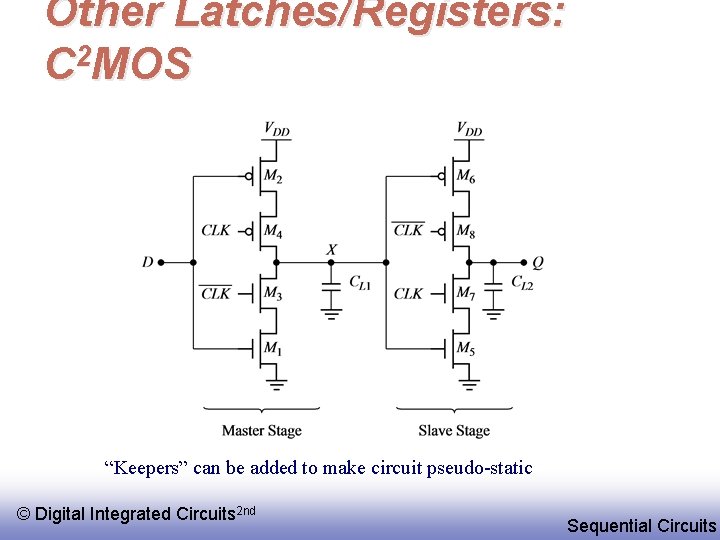

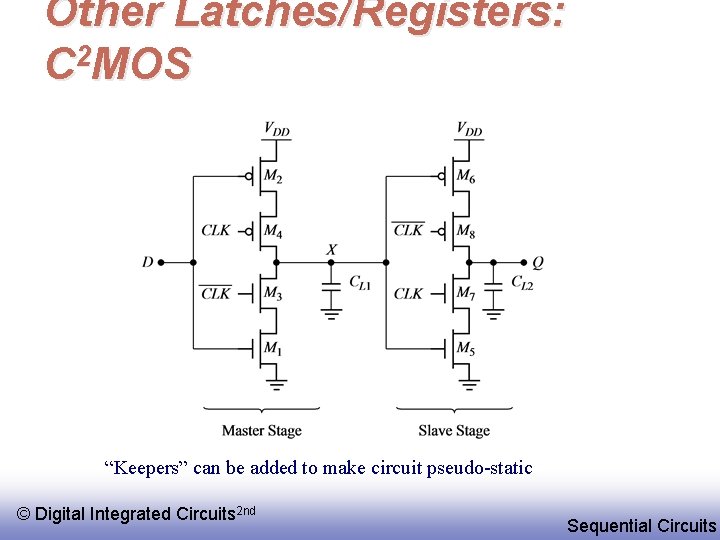

Other Latches/Registers: C 2 MOS “Keepers” can be added to make circuit pseudo-static © Digital Integrated Circuits 2 nd Sequential Circuits

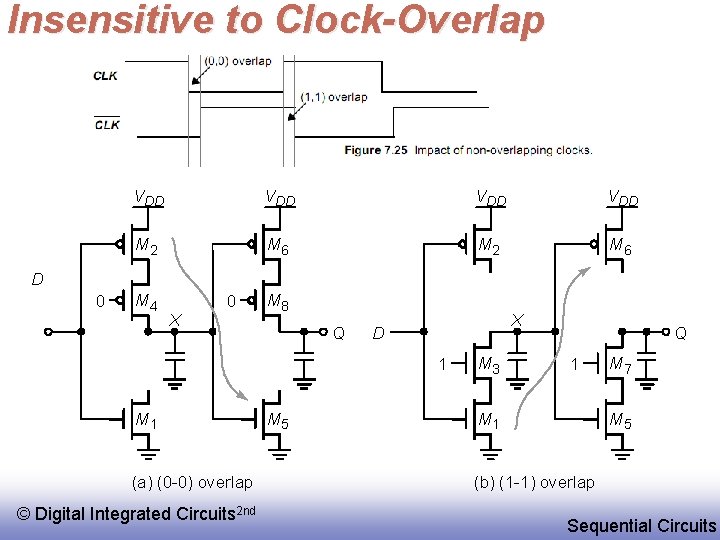

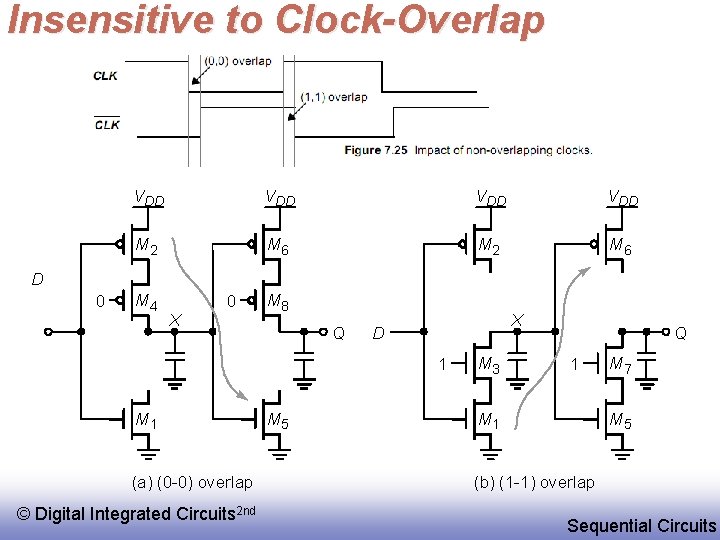

Insensitive to Clock-Overlap VDD VDD M 2 M 6 D 0 M 4 0 X M 8 Q X D 1 M 1 (a) (0 -0) overlap © Digital Integrated Circuits 2 nd M 5 M 3 Q 1 M 7 M 5 (b) (1 -1) overlap Sequential Circuits

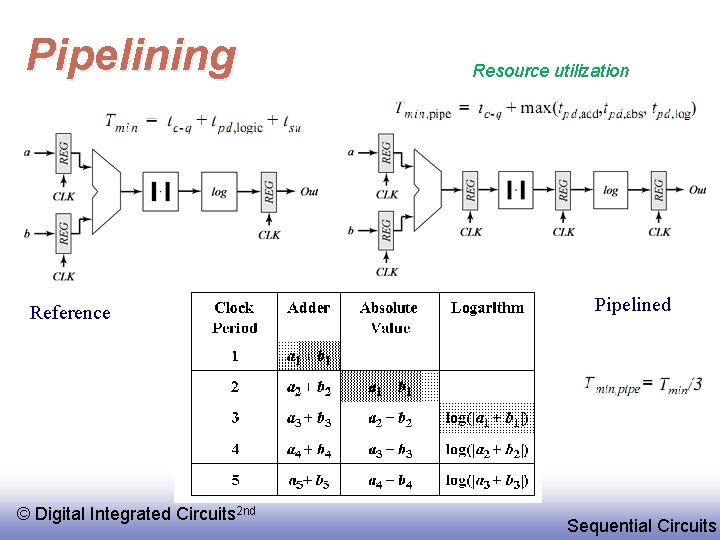

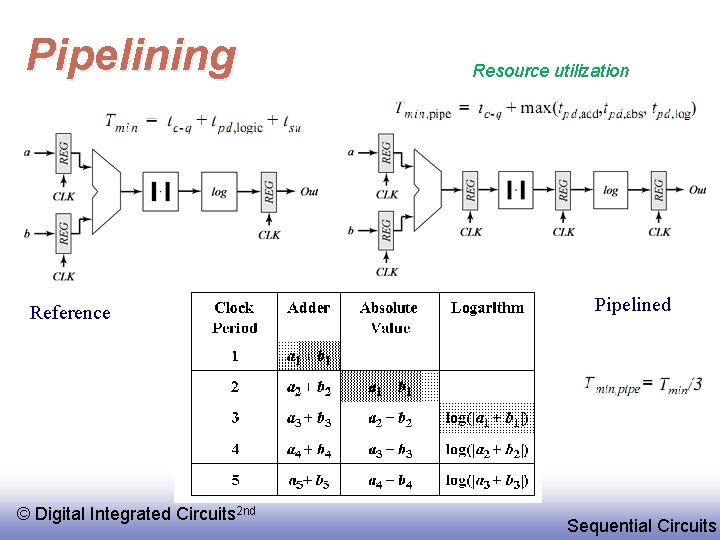

Pipelining Reference © Digital Integrated Circuits 2 nd Resource utilization Pipelined Sequential Circuits

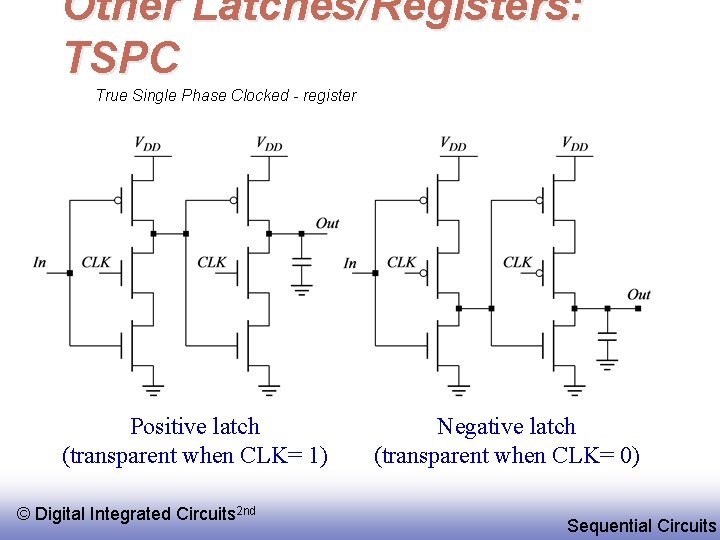

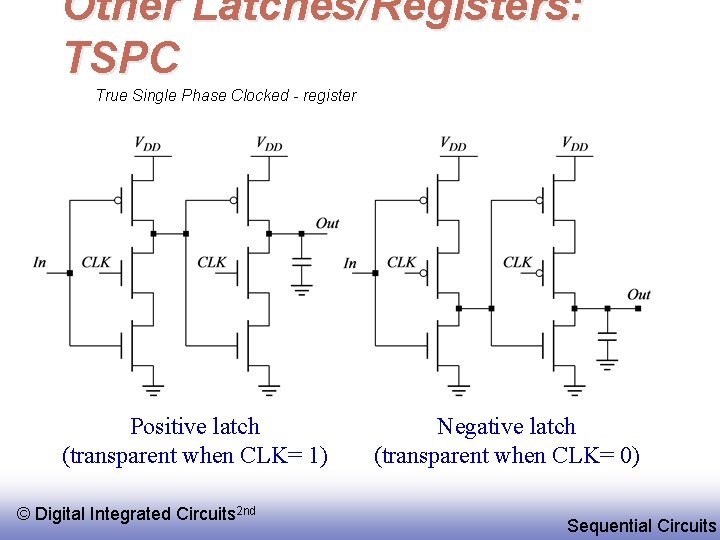

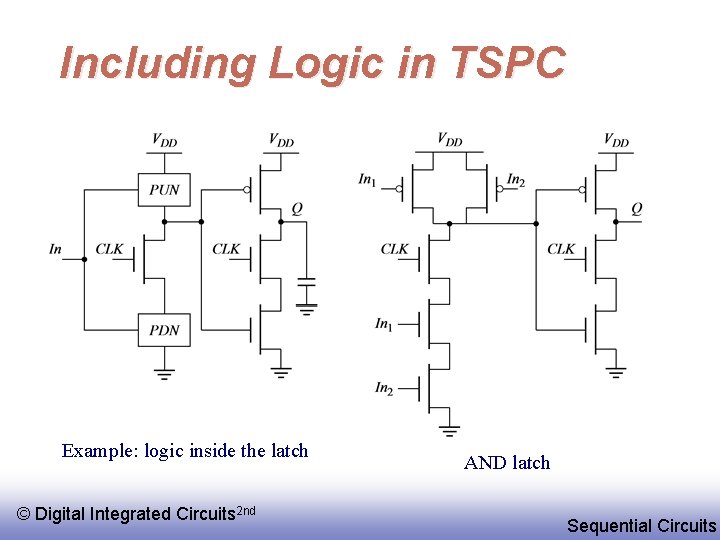

Other Latches/Registers: TSPC True Single Phase Clocked - register Positive latch (transparent when CLK= 1) © Digital Integrated Circuits 2 nd Negative latch (transparent when CLK= 0) Sequential Circuits

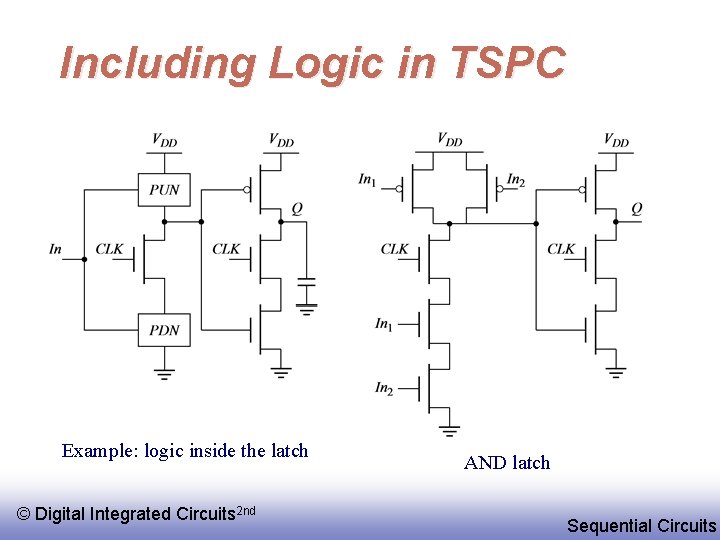

Including Logic in TSPC Example: logic inside the latch © Digital Integrated Circuits 2 nd AND latch Sequential Circuits

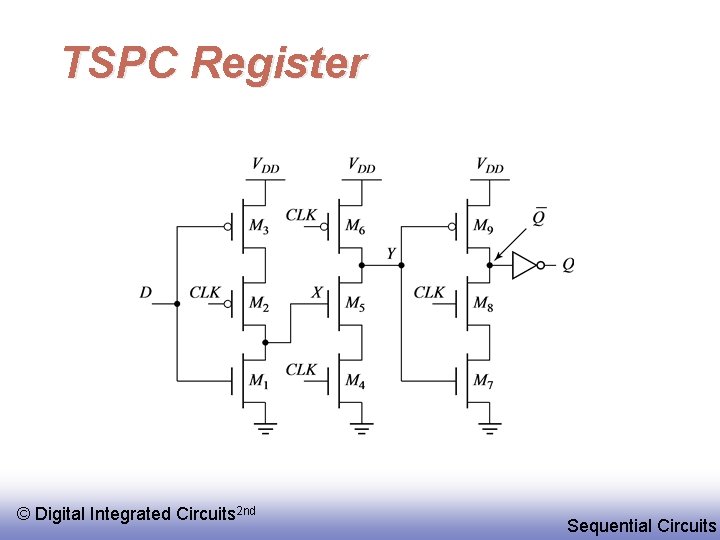

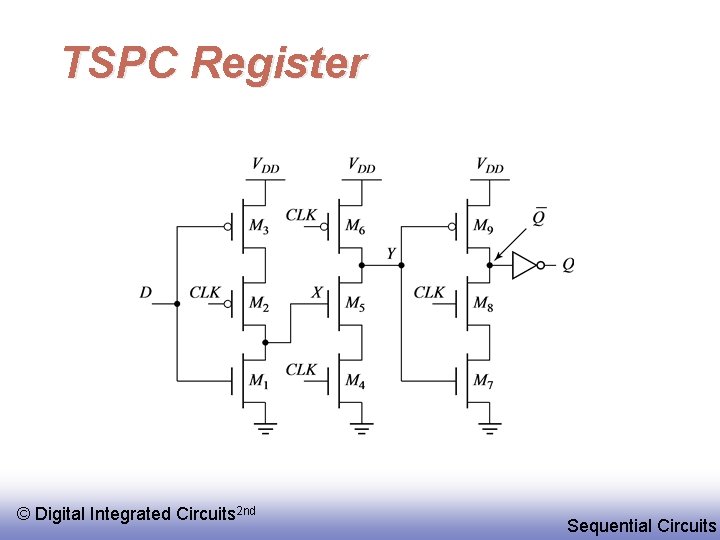

TSPC Register © Digital Integrated Circuits 2 nd Sequential Circuits