Digital Electronics II Chapter 7 Combinational Logic ABEL

Digital Electronics II Chapter 7 Combinational Logic ABEL

GAL 22 V 10 • Contains 12 dedicated inputs and 10 I/O’s • 28 pin PLCC or 24 pin DIP packages • Also available in Low power (3. 3 V) as well as ISP • Contains OLMC’s (Output Logic Macro cells) in combinational mode • 10 Available OLMC – 2 have 8 product terms ; 2 have 10 product terms – 2 have 12 product terms ; 2 have 14 product terms ; and 2 have 16 product terms

GAL 22 V 10 Array • Programmable array is organized as 22 input lines and compliments crossing 132 product term lines • At each of the 5808 intersections there is a programmable cell • A single line represents the product term line in the diagram 7 -8 on page 369 • Actually 44 lines to each AND gate, so each product term line consists of 44 AND gate inputs, one for each input line and its compliment

Gal 22 V 10 Array continued • The OLMC has a capacity for eight product terms that can be used in SOP function • One product term is reserved for the tristate control, one is used for reset function in registered mode for all the OLMC’s • And the last OLMC is a global function because it is common to all OLMC’s

GAL 16 V 8 • Contains 8 dedicated inputs and 8 I/O’s • Available in either 20 pin DIP or 20 pin PLCC package

OLMC of GAL 16 V 8 • Designed to be programmed in one of 3 modes to emulate most of the existing PAL’s • PAL Emulation: Simple mode, Complex mode, and registered mode • Simple and complex mode are associated only with combinational outputs Simple mode: OLMC are configured as dedicated active combinational outputs or as dedicated inputs (limited to 6). 3 Configurations for simple are: Combinational w/ feedback to AND Dedicated input

OLMC of GAL 16 V 8 • Complex mode configured in 2 ways: – Combinational output – Combinational I/O • Produce up to 7 product terms in SOP form

ABEL • Advanced Boolean Expression Language • Allows logic designs to be implemented in programmable logic devices • Requires ABEL software, a computer, a programmer, and an interface cable • Logic Design Entry; Design Simulation; and Logic Synthesis make up ABEL

Logic Design Entry • ABEL provides 3 different text based formats for describing and entering a logic design from the computer keyboard: equations, truth tables, and state diagrams – Equation and truth table formats are used for combinational logic design – State diagram format can be used for sequential logic design

Design Simulation • Once a logic circuit has been entered, its operation can be simulated using test vectors to make sure there are no design errors – Test Vector lists a sample of input values and the corresponding output values – Software then tests the logic design to make sure it works as expected

Logic Synthesis • Software process of converting a circuit description in the form of equations, truth tables, or state diagrams to a standard JEDEC file is called synthesis

Boolean Operations • • • Comprised or NOT, AND, OR, and EX-OR NOT = ! AND = & OR = # XOR = $ So A’B’ + A’B’C + (A+C’) would equate to: !A&!B # !A&!B&C # (A#!C);

Assigning groups in ABEL • Multiple inputs and outputs may be grouped as a set using brackets in order to simplify an equation • A = [A 3, A 2, A 1, A 0]; • Would equate the group of inputs A 3, A 2, A 1, A 0 into A

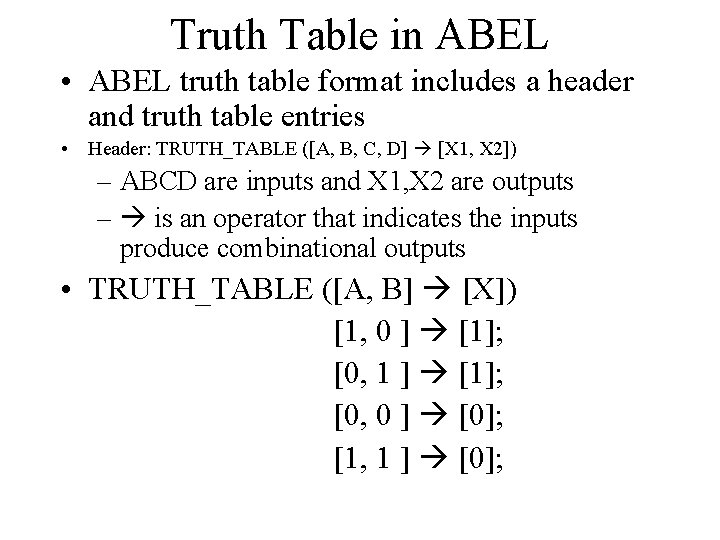

Truth Table in ABEL • ABEL truth table format includes a header and truth table entries • Header: TRUTH_TABLE ([A, B, C, D] [X 1, X 2]) – ABCD are inputs and X 1, X 2 are outputs – is an operator that indicates the inputs produce combinational outputs • TRUTH_TABLE ([A, B] [X]) [1, 0 ] [1]; [0, 1 ] [1]; [0, 0 ] [0]; [1, 1 ] [0];

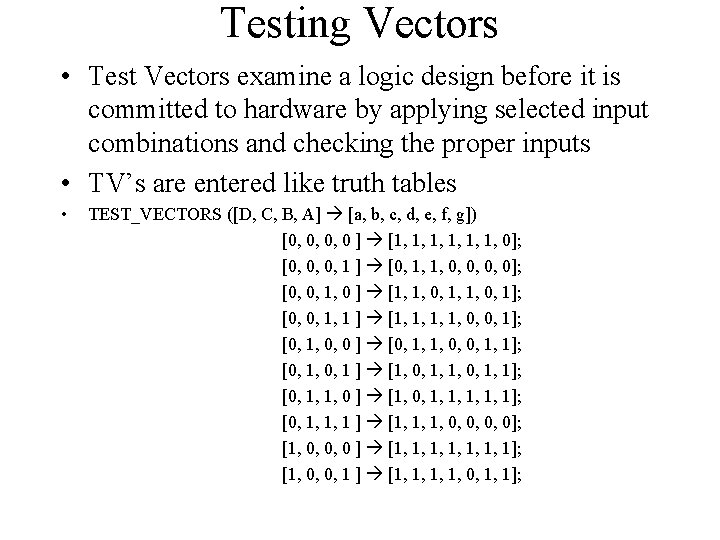

Testing Vectors • Test Vectors examine a logic design before it is committed to hardware by applying selected input combinations and checking the proper inputs • TV’s are entered like truth tables • TEST_VECTORS ([D, C, B, A] [a, b, c, d, e, f, g]) [0, 0, 0, 0 ] [1, 1, 1, 0]; [0, 0, 0, 1 ] [0, 1, 1, 0, 0]; [0, 0, 1, 0 ] [1, 1, 0, 1]; [0, 0, 1, 1 ] [1, 1, 0, 0, 1]; [0, 1, 0, 0 ] [0, 1, 1, 0, 0, 1, 1]; [0, 1, 0, 1 ] [1, 0, 1, 1]; [0, 1, 1, 0 ] [1, 0, 1, 1, 1]; [0, 1, 1, 1 ] [1, 1, 1, 0, 0]; [1, 0, 0, 0 ] [1, 1, 1, 1]; [1, 0, 0, 1 ] [1, 1, 0, 1, 1];

ABEL input file • The ABEL source file creates three basic sections following the module: declarations, logic descriptions, and test vectors • Declarations includes device declarations, pin declarations, and set declarations • Device declaration: decoder device ‘P 22 V 10’ • Pin declaration: A 0, A 1, A 2, A 3, PIN 1, 2, 3, 4; • Logic Descriptions are equations and truth tables • Test Vectors

Documentation File • Provides a hard copy of all the equations and a JEDEC file • The JEDEC file is what is sent to the programmer to program the SPLD • The JEDEC file is a cell or fuse map of all the programming that has been tested and completed

- Slides: 17