Digital Electronics Chapter 7 Memory and Programmable Logic

Digital Electronics

Chapter 7 Memory and Programmable Logic

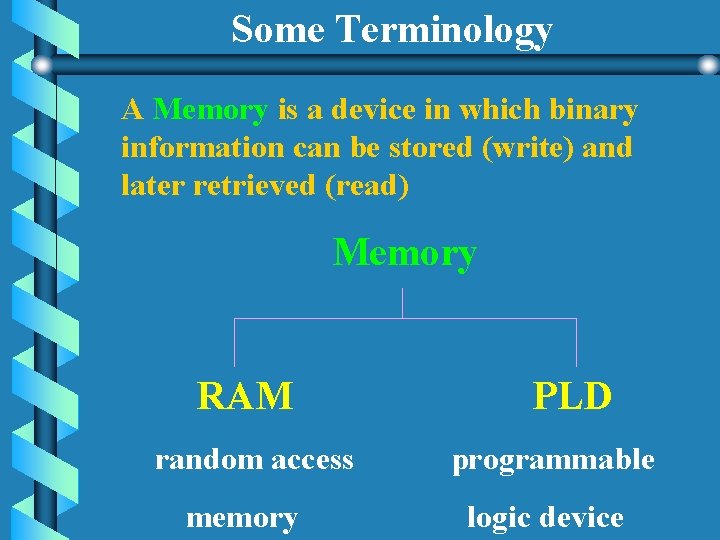

Some Terminology A Memory is a device in which binary information can be stored (write) and later retrieved (read) Memory RAM random access memory PLD programmable logic device

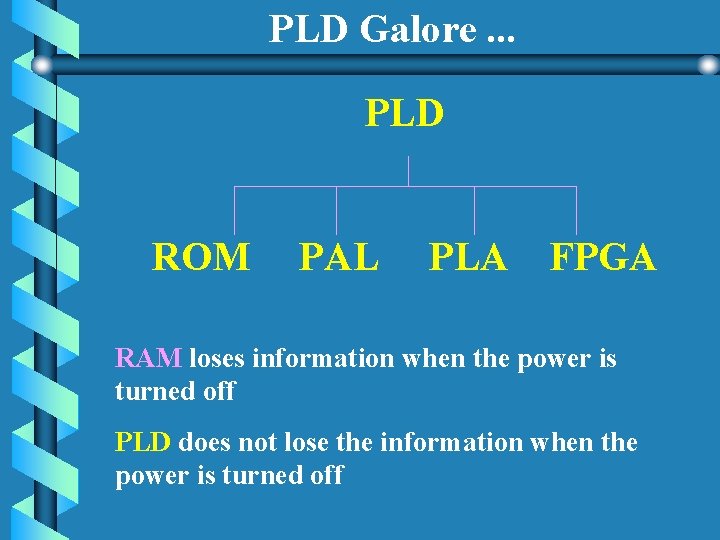

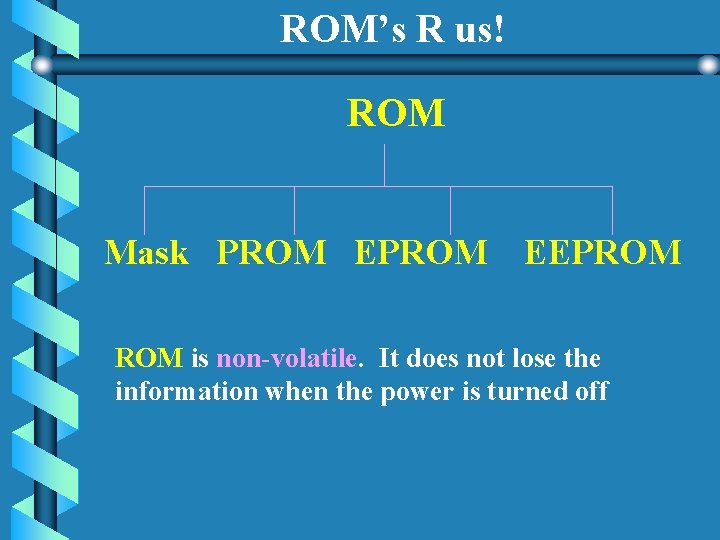

PLD Galore. . . PLD ROM PAL PLA FPGA RAM loses information when the power is turned off PLD does not lose the information when the power is turned off

ROM’s R us! ROM Mask PROM EEPROM is non-volatile. It does not lose the information when the power is turned off

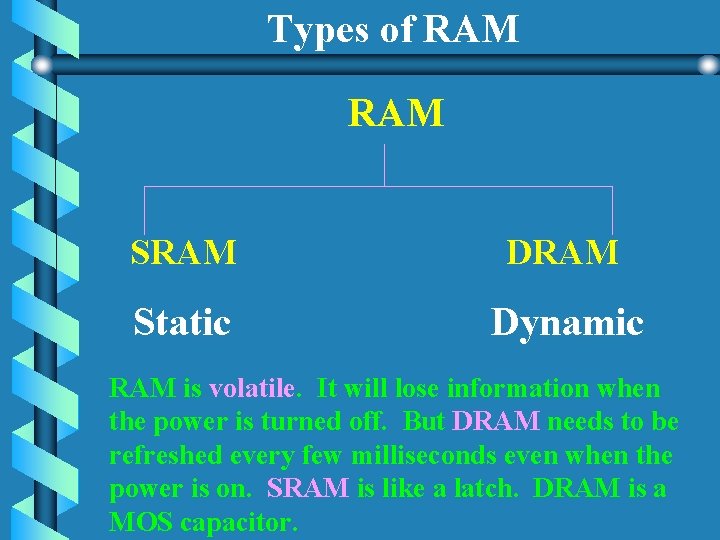

Types of RAM SRAM DRAM Static Dynamic RAM is volatile. It will lose information when the power is turned off. But DRAM needs to be refreshed every few milliseconds even when the power is on. SRAM is like a latch. DRAM is a MOS capacitor.

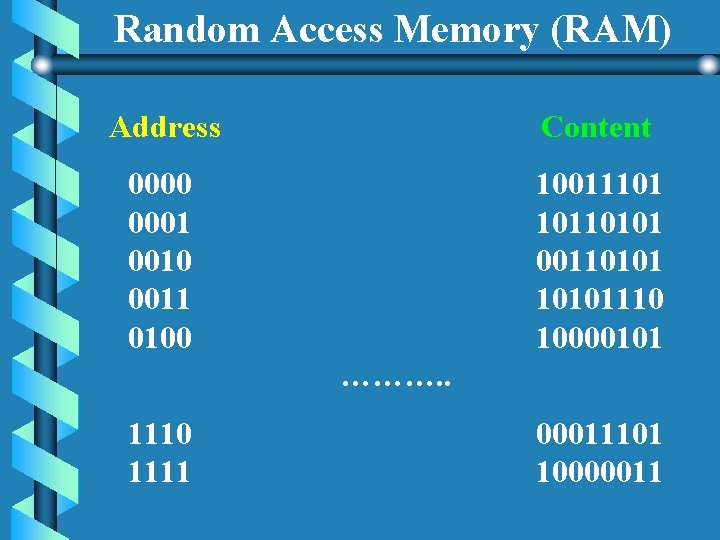

Random Access Memory (RAM) Address Content 0000 0001 0010 0011 0100 10011101 10110101 00110101110 10000101 ………. . 1110 1111 00011101 10000011

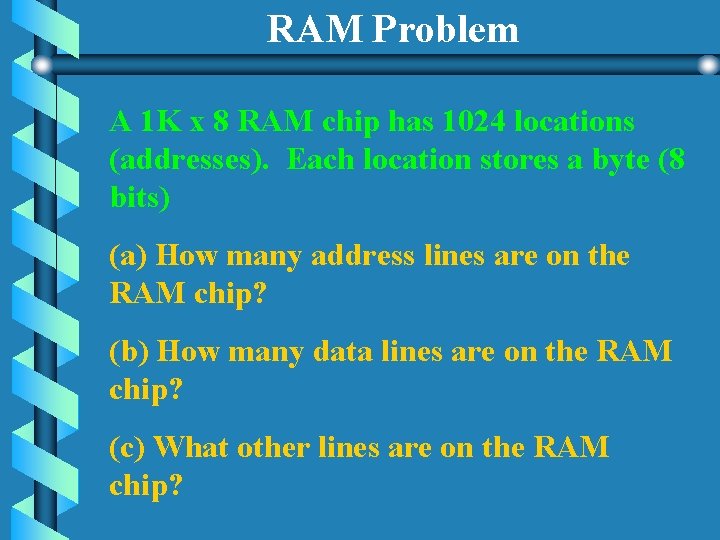

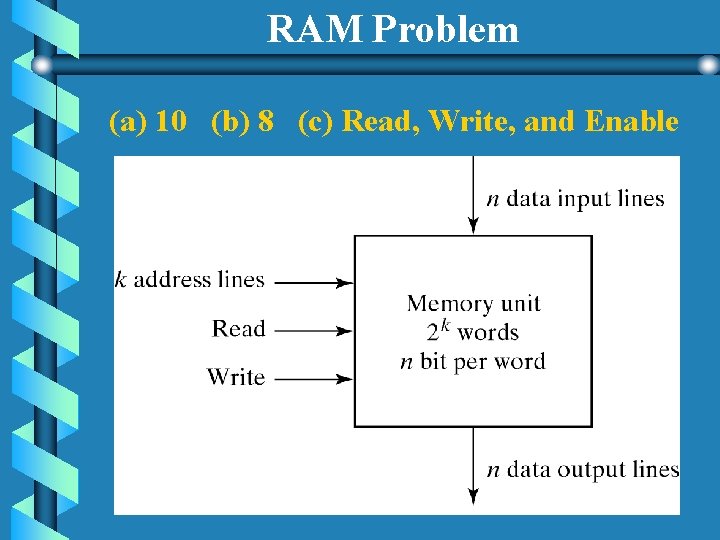

RAM Problem A 1 K x 8 RAM chip has 1024 locations (addresses). Each location stores a byte (8 bits) (a) How many address lines are on the RAM chip? (b) How many data lines are on the RAM chip? (c) What other lines are on the RAM chip?

RAM Problem (a) 10 (b) 8 (c) Read, Write, and Enable

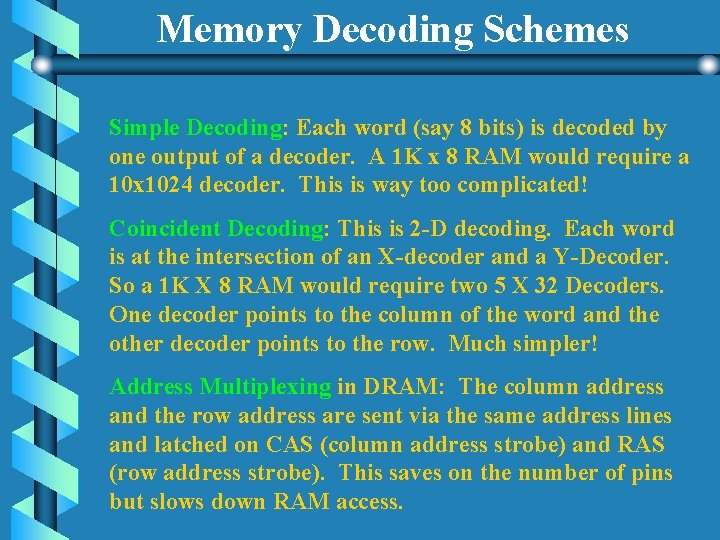

Memory Decoding Schemes Simple Decoding: Each word (say 8 bits) is decoded by one output of a decoder. A 1 K x 8 RAM would require a 10 x 1024 decoder. This is way too complicated! Coincident Decoding: This is 2 -D decoding. Each word is at the intersection of an X-decoder and a Y-Decoder. So a 1 K X 8 RAM would require two 5 X 32 Decoders. One decoder points to the column of the word and the other decoder points to the row. Much simpler! Address Multiplexing in DRAM: The column address and the row address are sent via the same address lines and latched on CAS (column address strobe) and RAS (row address strobe). This saves on the number of pins but slows down RAM access.

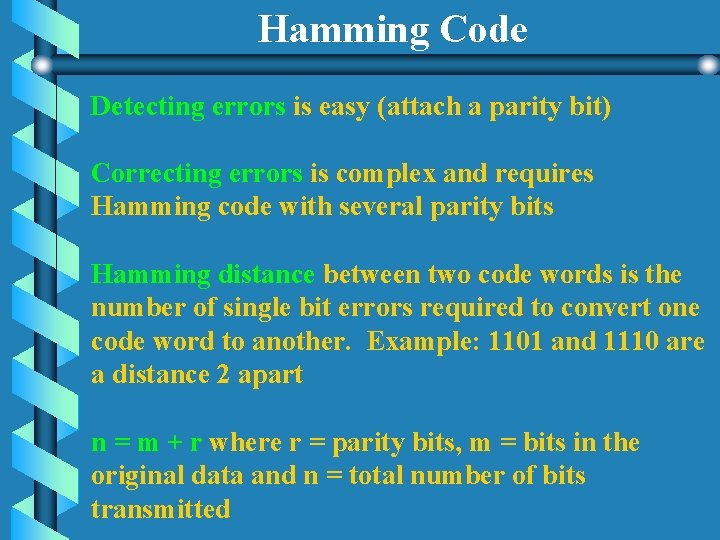

Hamming Code Detecting errors is easy (attach a parity bit) Correcting errors is complex and requires Hamming code with several parity bits Hamming distance between two code words is the number of single bit errors required to convert one code word to another. Example: 1101 and 1110 are a distance 2 apart n = m + r where r = parity bits, m = bits in the original data and n = total number of bits transmitted

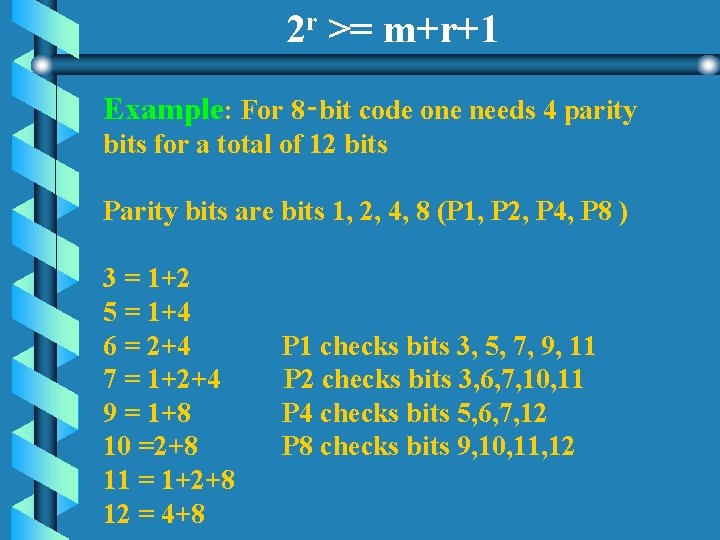

2 r >= m+r+1 Example: For 8‑bit code one needs 4 parity bits for a total of 12 bits Parity bits are bits 1, 2, 4, 8 (P 1, P 2, P 4, P 8 ) 3 = 1+2 5 = 1+4 6 = 2+4 7 = 1+2+4 9 = 1+8 10 =2+8 11 = 1+2+8 12 = 4+8 P 1 checks bits 3, 5, 7, 9, 11 P 2 checks bits 3, 6, 7, 10, 11 P 4 checks bits 5, 6, 7, 12 P 8 checks bits 9, 10, 11, 12

Problemo du Jour. . . Example We need to send 11101001. What 12 -bit Hamming word should we send?

Solution de Problemo du Jour … 101111001001

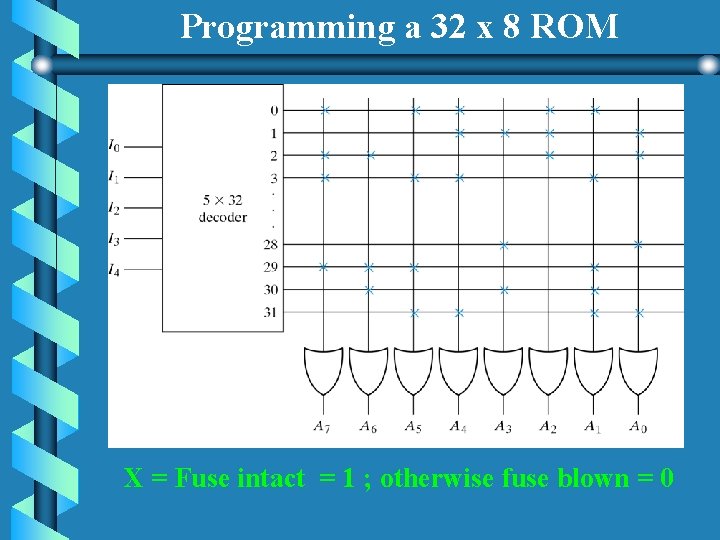

Programming a 32 x 8 ROM X = Fuse intact = 1 ; otherwise fuse blown = 0

Programming a 32 x 8 ROM Example: What are the contents of memory location 11101?

Solution to 32 x 8 ROM Address location 11110 = 30 whose contents are 01001010 Practice: Address 11100 has 00001001

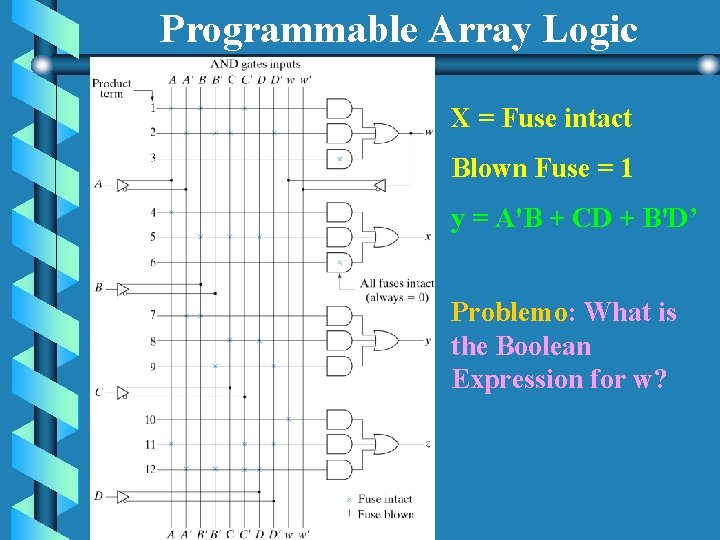

Programmable Array Logic X = Fuse intact Blown Fuse = 1 y = A'B + CD + B'D’ Problemo: What is the Boolean Expression for w?

Solution. . . w = ABC' + A'B'CD'

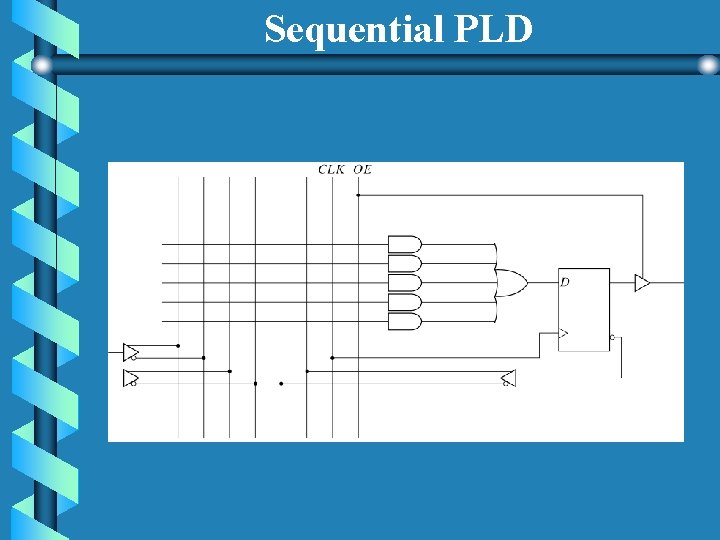

Sequential PLD

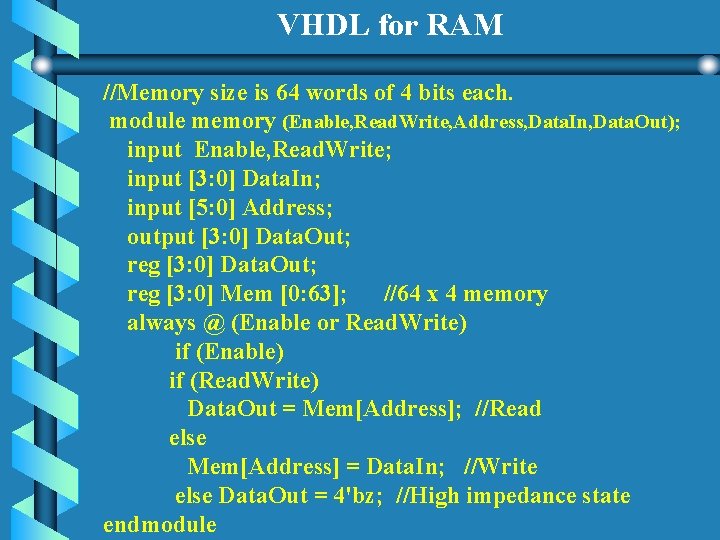

VHDL for RAM //Memory size is 64 words of 4 bits each. module memory (Enable, Read. Write, Address, Data. In, Data. Out); input Enable, Read. Write; input [3: 0] Data. In; input [5: 0] Address; output [3: 0] Data. Out; reg [3: 0] Mem [0: 63]; //64 x 4 memory always @ (Enable or Read. Write) if (Enable) if (Read. Write) Data. Out = Mem[Address]; //Read else Mem[Address] = Data. In; //Write else Data. Out = 4'bz; //High impedance state endmodule

That’s All Folks!

- Slides: 22