Digital Design Through Verilog Introduction 1 Chips Everywhere

- Slides: 19

Digital Design Through Verilog Introduction 1

Chips Everywhere! 2

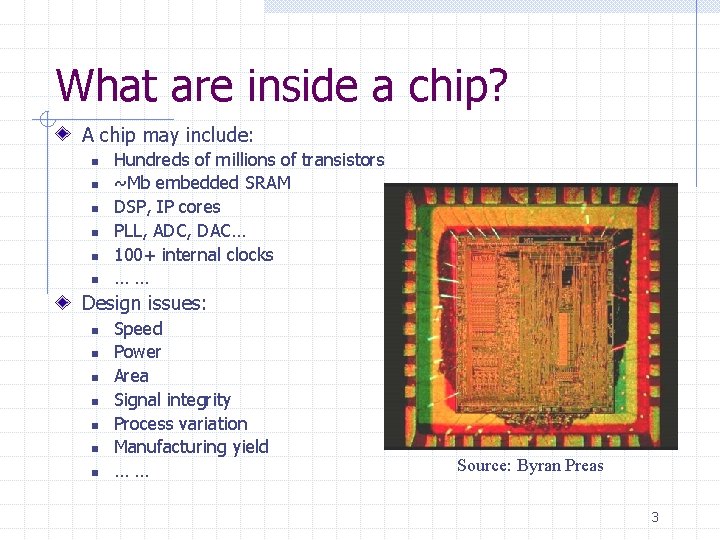

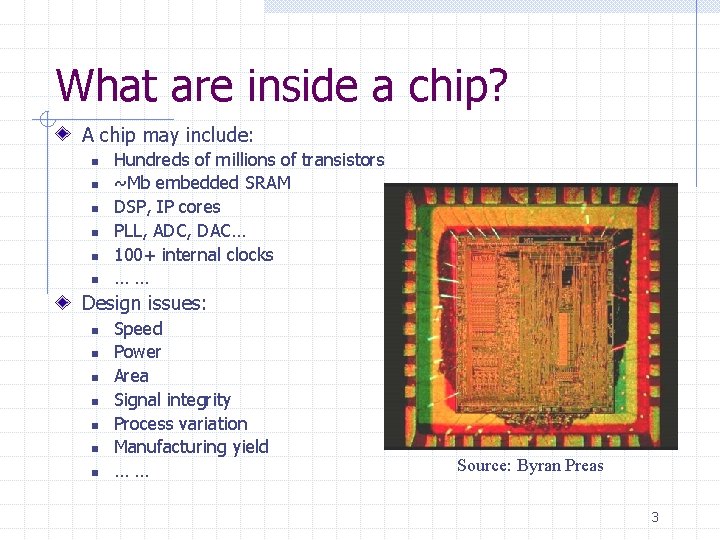

What are inside a chip? A chip may include: n n n Hundreds of millions of transistors ~Mb embedded SRAM DSP, IP cores PLL, ADC, DAC… 100+ internal clocks …… Design issues: n n n n Speed Power Area Signal integrity Process variation Manufacturing yield …… Source: Byran Preas 3

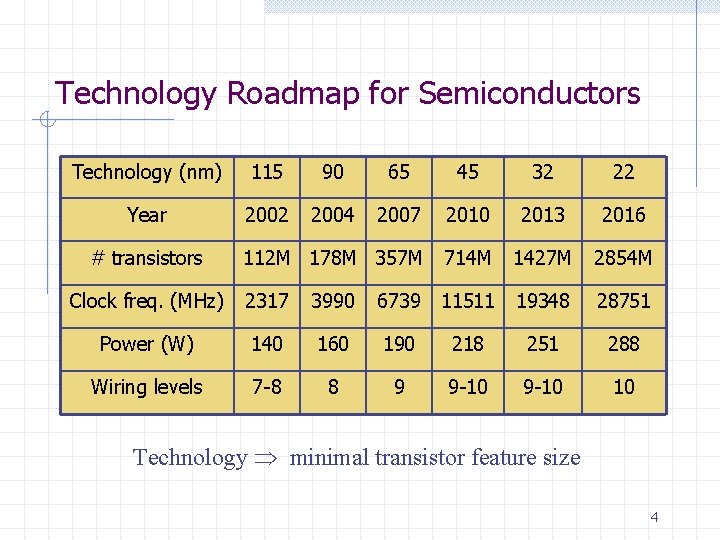

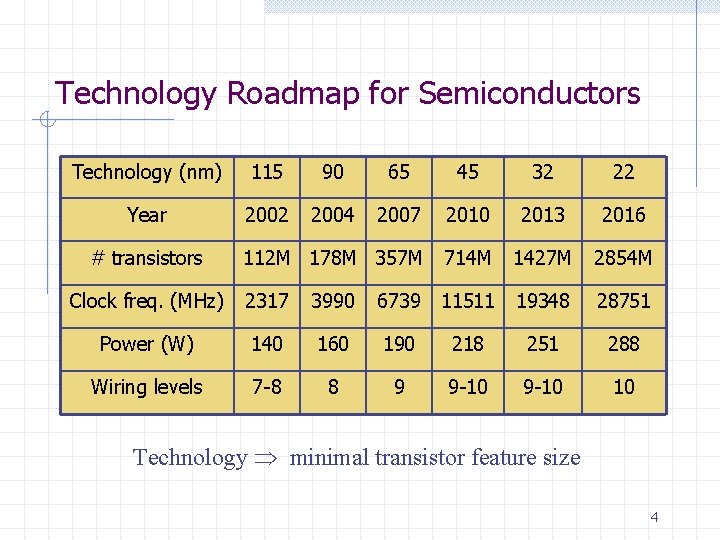

Technology Roadmap for Semiconductors Technology (nm) 115 90 65 45 32 22 Year 2002 2004 2007 2010 2013 2016 112 M 178 M 357 M 714 M 1427 M 2854 M 19348 28751 # transistors Clock freq. (MHz) 2317 3990 6739 11511 Power (W) 140 160 190 218 251 288 Wiring levels 7 -8 8 9 9 -10 10 Technology minimal transistor feature size 4

ELEN 468 Lecture 1 5

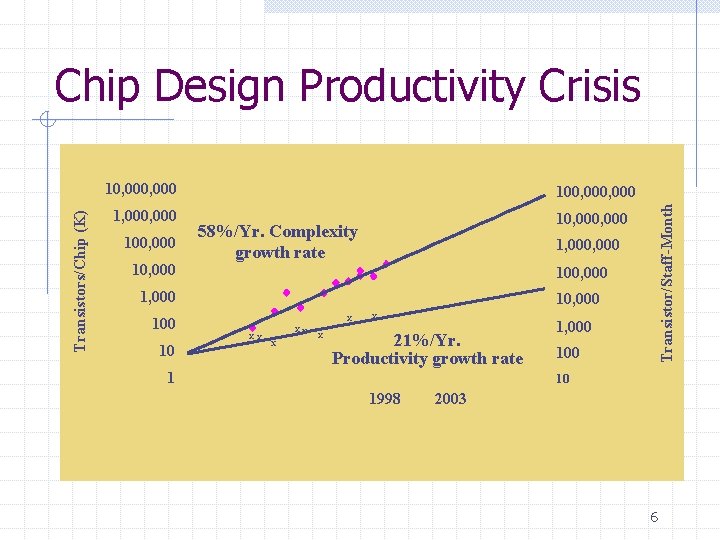

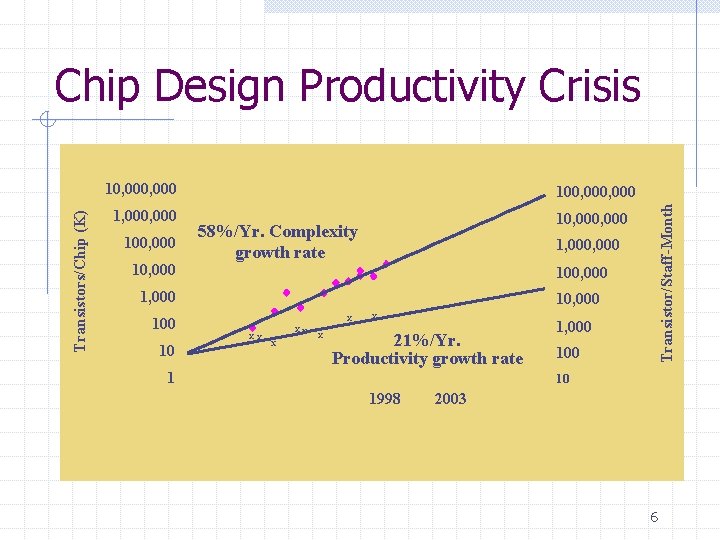

10, 000 100, 000 1, 000, 000 100, 000 10, 000 58%/Yr. Complexity growth rate 1, 000 100, 000 100 10 10, 000 x xx xx x 21%/Yr. Productivity growth rate 1 1, 000 100 Transistor/Staff-Month Transistors/Chip (K) Chip Design Productivity Crisis 10 1998 2003 6

Solutions Apply ECAD tools High level abstraction Learn Verilog ! 7

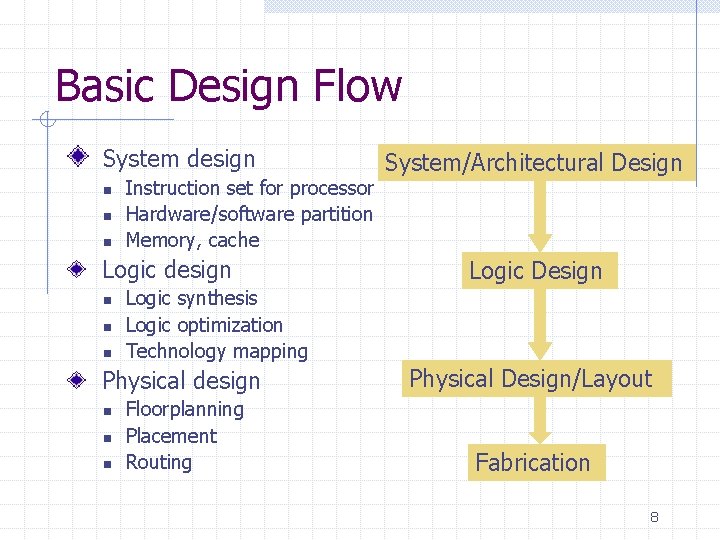

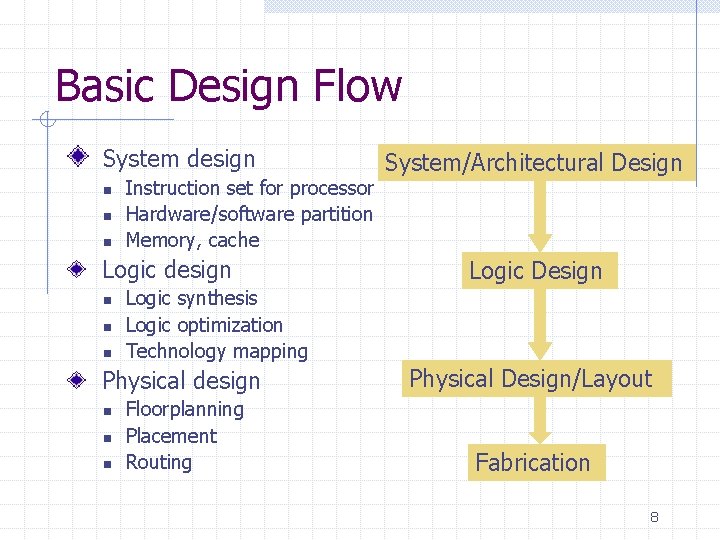

Basic Design Flow System design n Instruction set for processor Hardware/software partition Memory, cache Logic design n System/Architectural Design Logic synthesis Logic optimization Technology mapping Physical design Physical Design/Layout Floorplanning Placement Routing Fabrication n 8

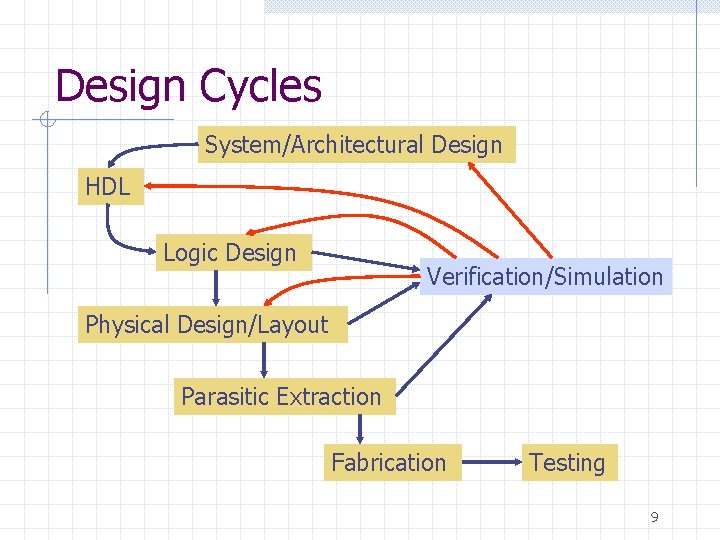

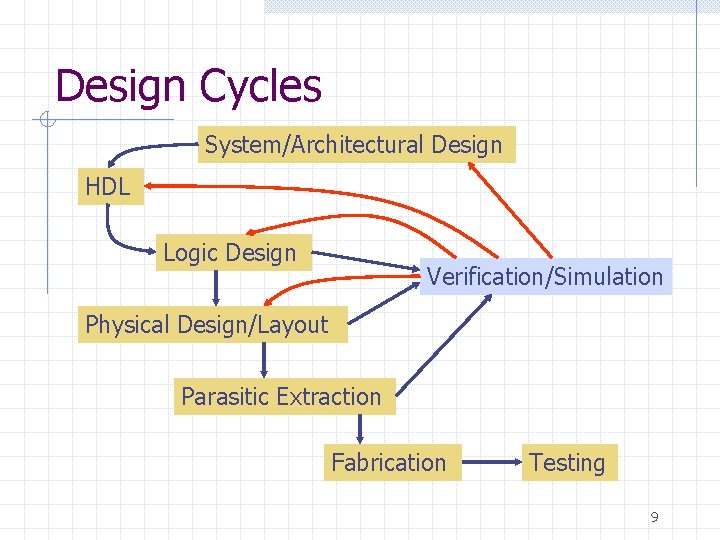

Design Cycles System/Architectural Design HDL Logic Design Verification/Simulation Physical Design/Layout Parasitic Extraction Fabrication Testing 9

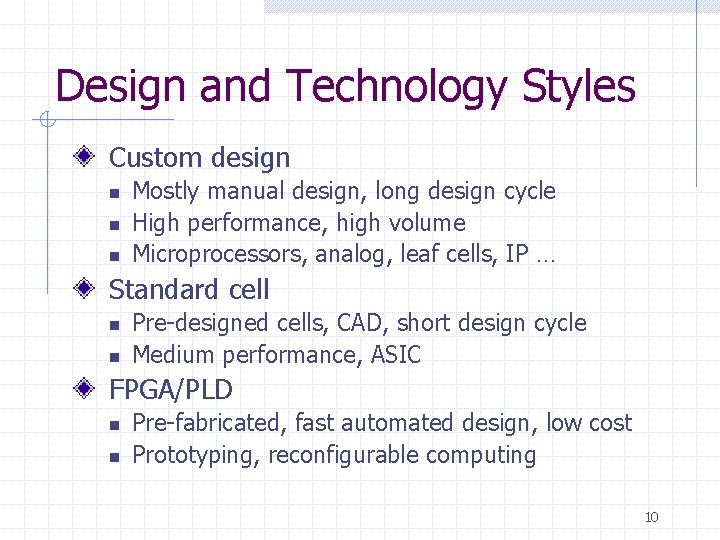

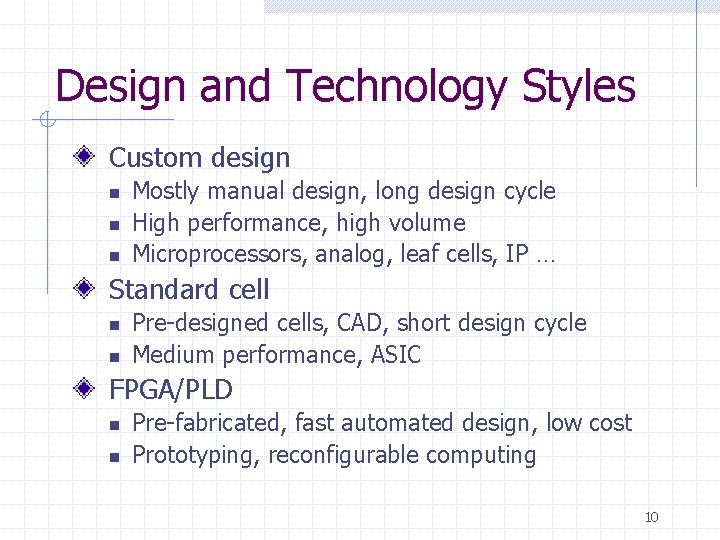

Design and Technology Styles Custom design n Mostly manual design, long design cycle High performance, high volume Microprocessors, analog, leaf cells, IP … Standard cell n n Pre-designed cells, CAD, short design cycle Medium performance, ASIC FPGA/PLD n n Pre-fabricated, fast automated design, low cost Prototyping, reconfigurable computing 10

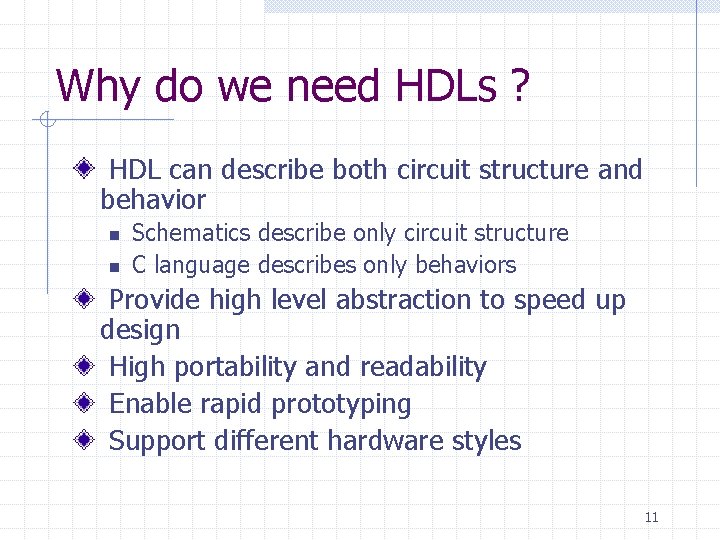

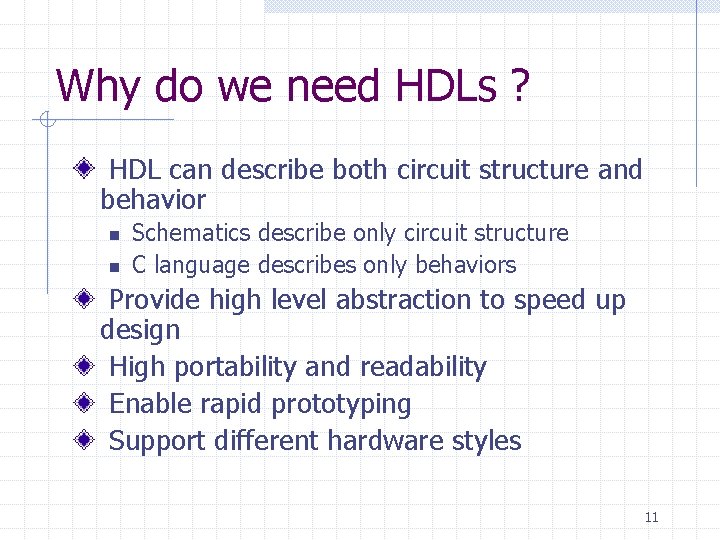

Why do we need HDLs ? HDL can describe both circuit structure and behavior n n Schematics describe only circuit structure C language describes only behaviors Provide high level abstraction to speed up design High portability and readability Enable rapid prototyping Support different hardware styles 11

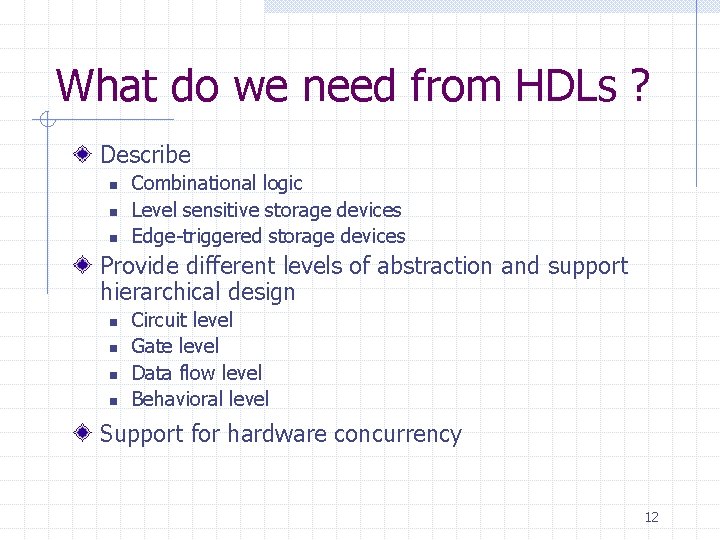

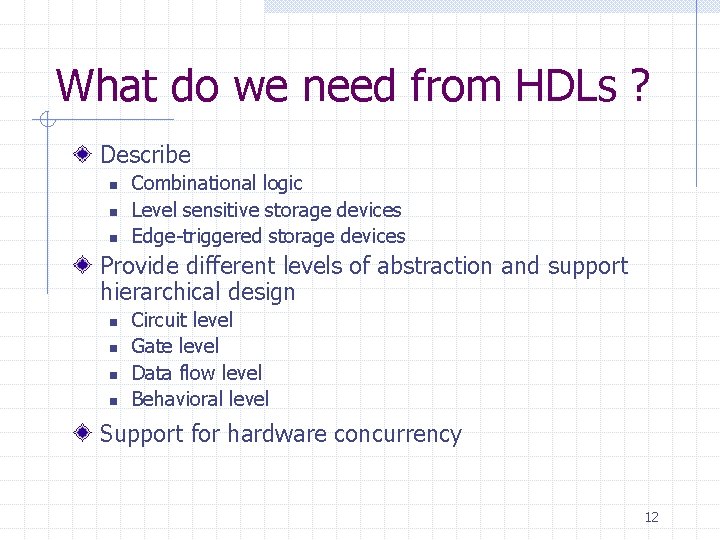

What do we need from HDLs ? Describe n n n Combinational logic Level sensitive storage devices Edge-triggered storage devices Provide different levels of abstraction and support hierarchical design n n Circuit level Gate level Data flow level Behavioral level Support for hardware concurrency 12

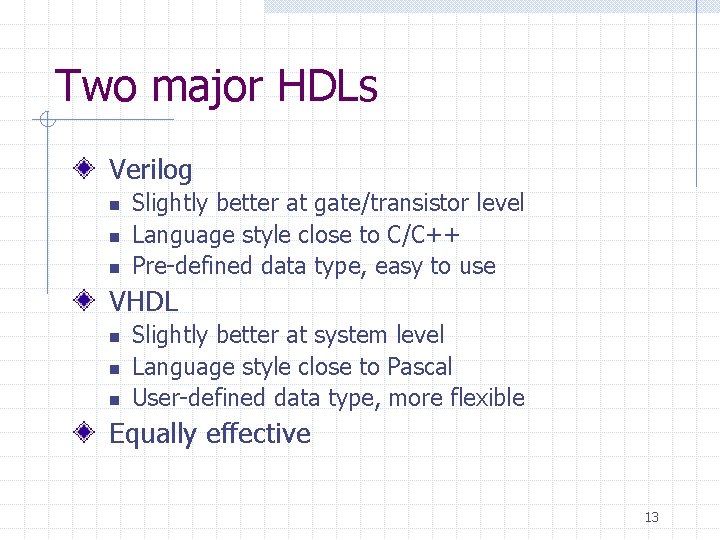

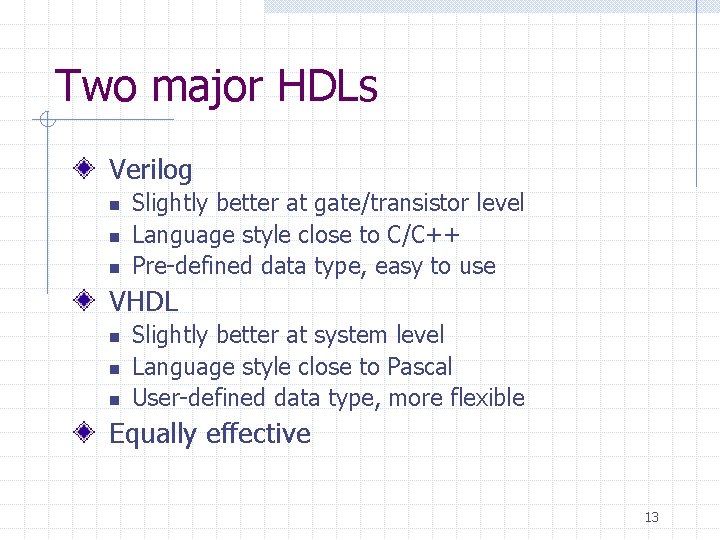

Two major HDLs Verilog n n n Slightly better at gate/transistor level Language style close to C/C++ Pre-defined data type, easy to use VHDL n n n Slightly better at system level Language style close to Pascal User-defined data type, more flexible Equally effective 13

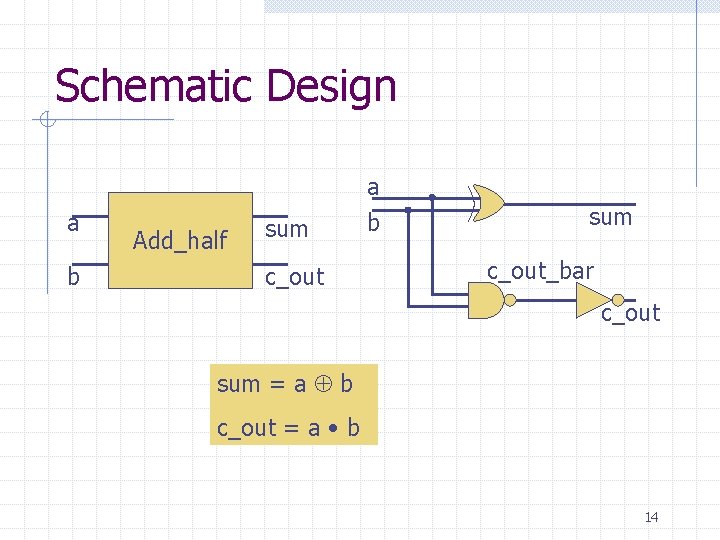

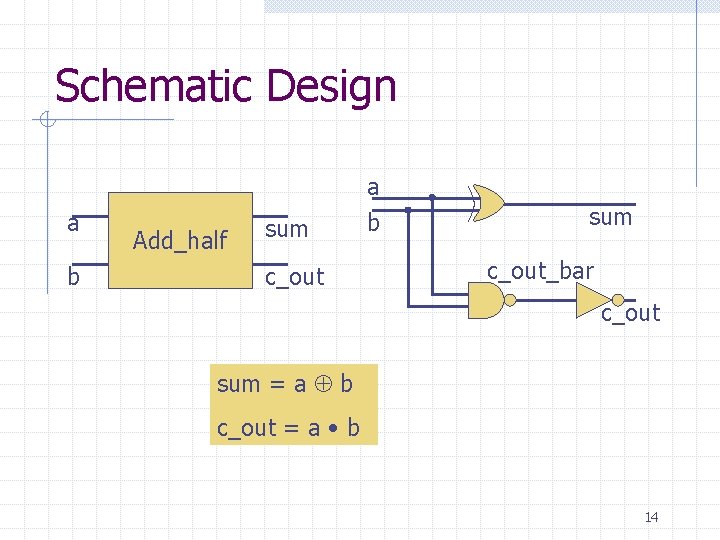

Schematic Design a b Add_half sum c_out a b sum c_out_bar c_out sum = a b c_out = a • b 14

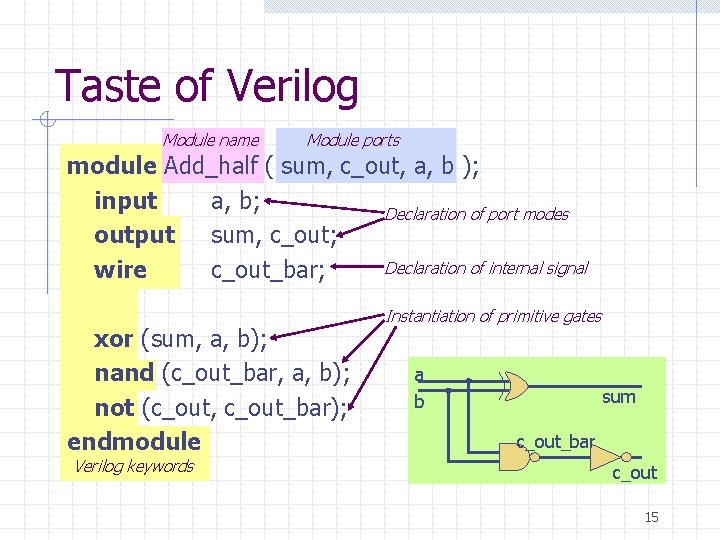

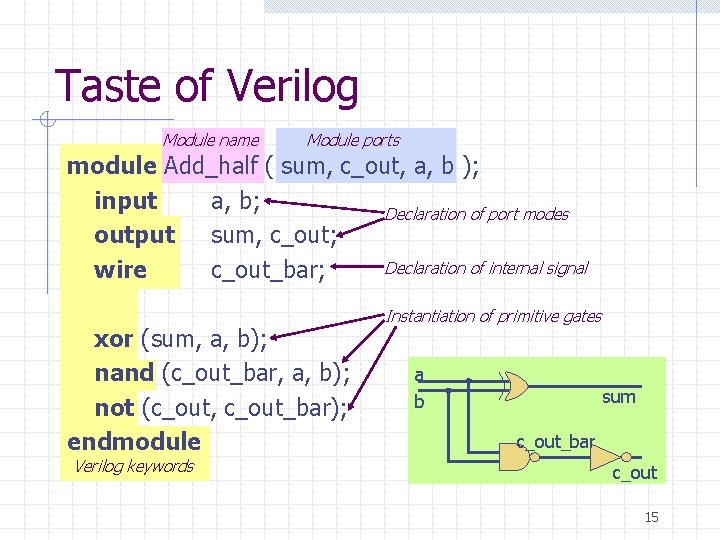

Taste of Verilog Module name Module ports module Add_half ( sum, c_out, a, b ); input a, b; Declaration of port modes output sum, c_out; Declaration of internal signal wire c_out_bar; xor (sum, a, b); nand (c_out_bar, a, b); not (c_out, c_out_bar); endmodule Verilog keywords Instantiation of primitive gates a b sum c_out_bar c_out 15

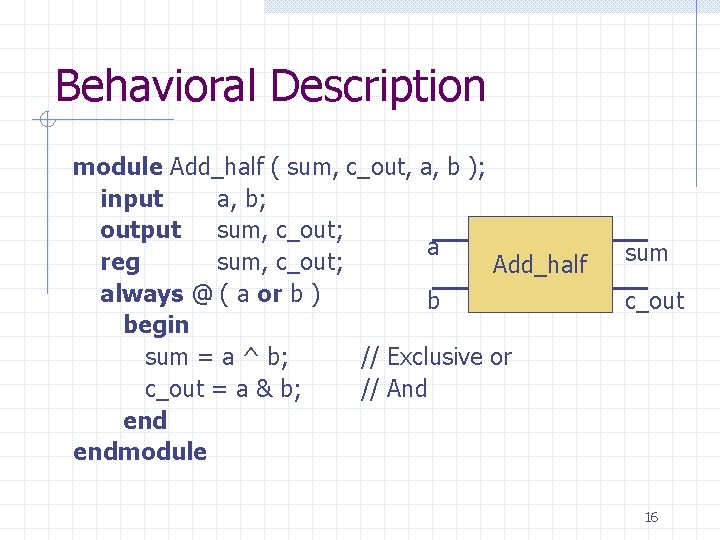

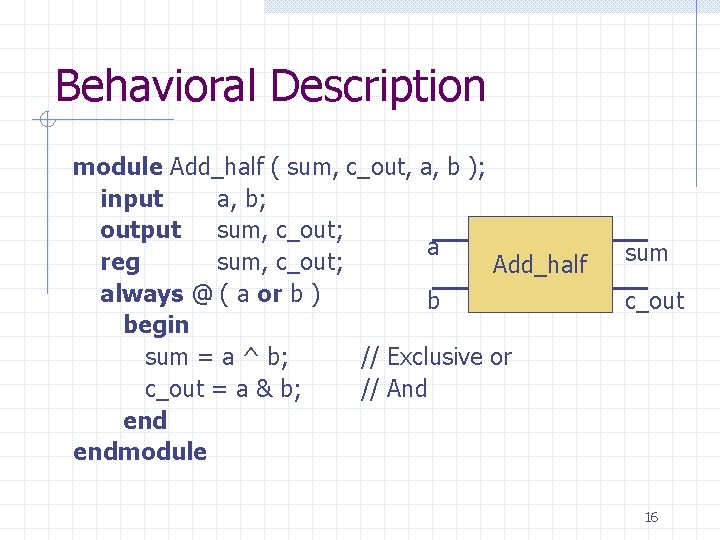

Behavioral Description module Add_half ( sum, c_out, a, b ); input a, b; output sum, c_out; a reg sum, c_out; Add_half always @ ( a or b ) b begin sum = a ^ b; // Exclusive or c_out = a & b; // And endmodule sum c_out 16

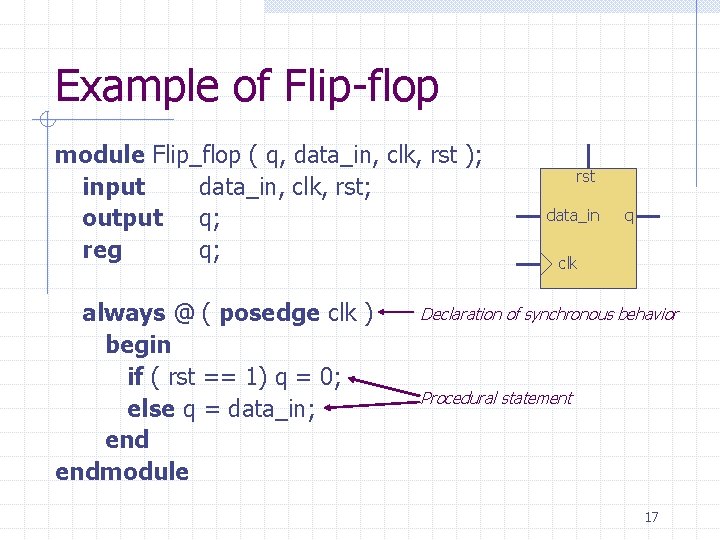

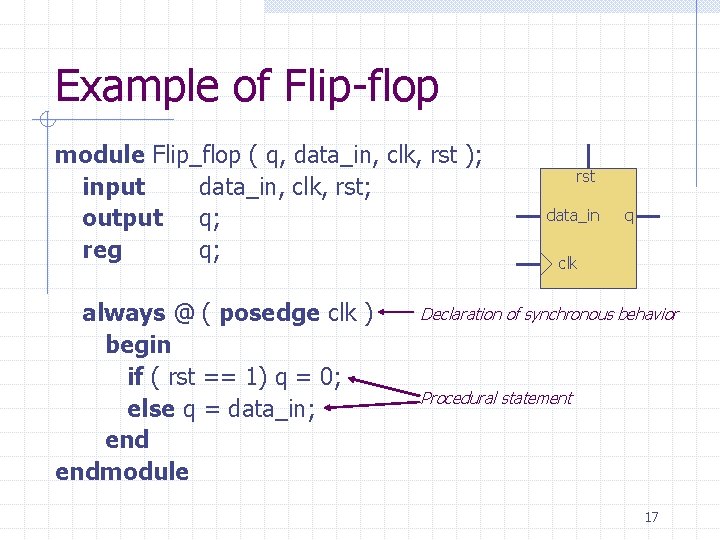

Example of Flip-flop module Flip_flop ( q, data_in, clk, rst ); input data_in, clk, rst; output q; reg q; always @ ( posedge clk ) begin if ( rst == 1) q = 0; else q = data_in; endmodule rst data_in q clk Declaration of synchronous behavior Procedural statement 17

Text Books 18

Conclusion VLSI Chips Chip design flow Chip design styles Why do we need HDLs ? What do we need from HDLs ? Examples of Verilog HDL 19