Digital Design Programmable Processors Chapter 8 Programmable Processors

Digital Design – Programmable Processors Chapter 8 Programmable Processors

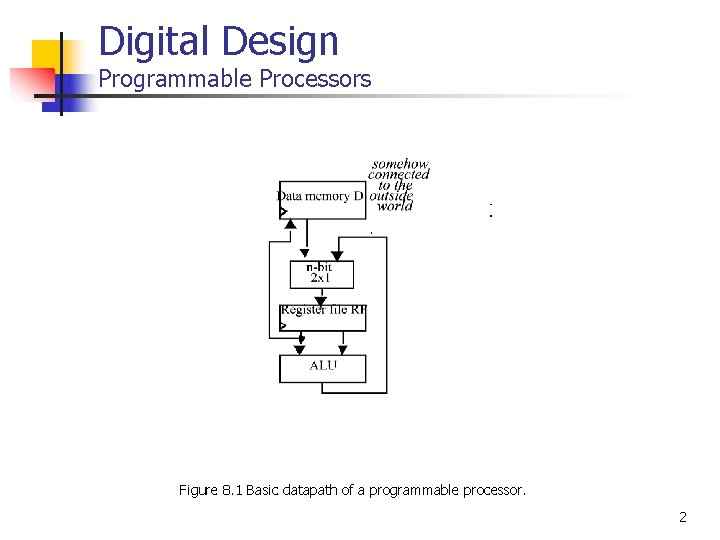

Digital Design Programmable Processors Figure 8. 1 Basic datapath of a programmable processor. 2

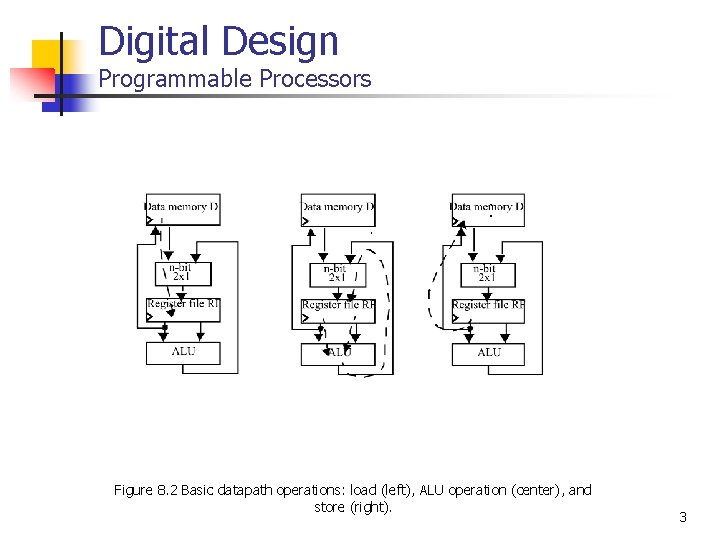

Digital Design Programmable Processors Figure 8. 2 Basic datapath operations: load (left), ALU operation (center), and store (right). 3

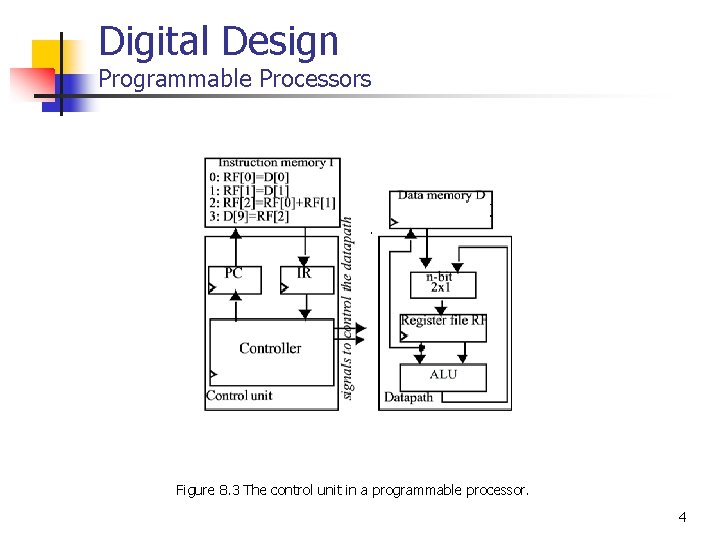

Digital Design Programmable Processors Figure 8. 3 The control unit in a programmable processor. 4

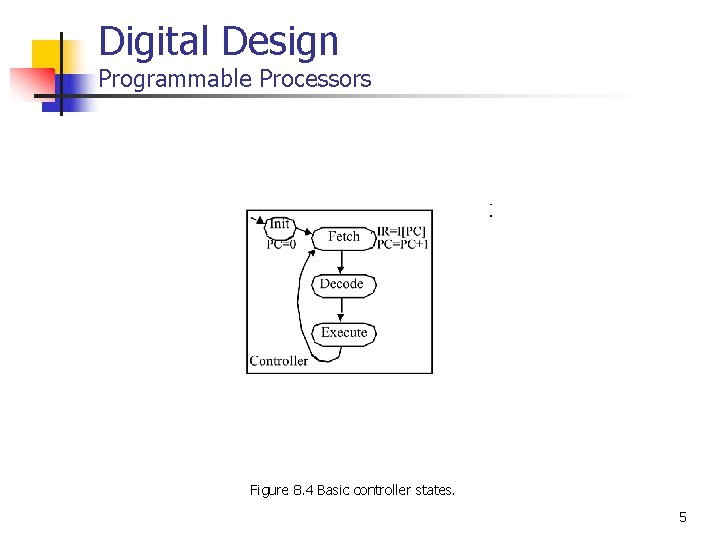

Digital Design Programmable Processors Figure 8. 4 Basic controller states. 5

![Digital Design Programmable Processors Figure 8. 5 A program that computes D[9]=D[0]+D[1], using a Digital Design Programmable Processors Figure 8. 5 A program that computes D[9]=D[0]+D[1], using a](http://slidetodoc.com/presentation_image/bf0a4def62a75ef3aeff4dcaa9081f25/image-6.jpg)

Digital Design Programmable Processors Figure 8. 5 A program that computes D[9]=D[0]+D[1], using a given instruction set. 6

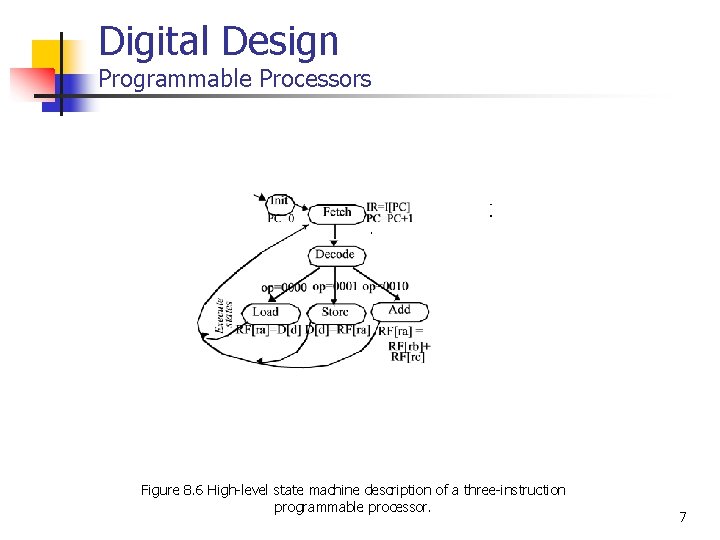

Digital Design Programmable Processors Figure 8. 6 High-level state machine description of a three-instruction programmable processor. 7

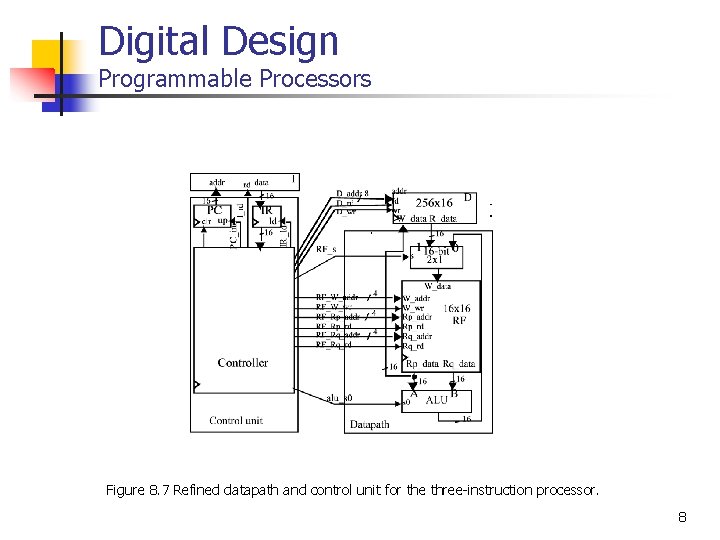

Digital Design Programmable Processors Figure 8. 7 Refined datapath and control unit for the three-instruction processor. 8

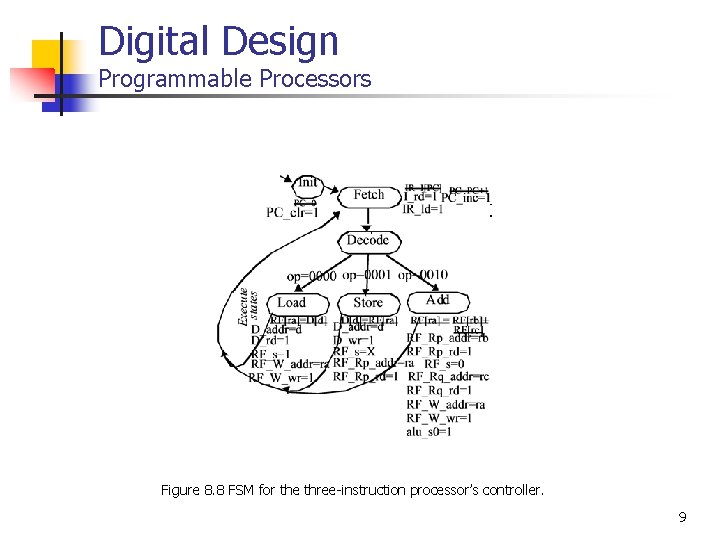

Digital Design Programmable Processors Figure 8. 8 FSM for the three-instruction processor’s controller. 9

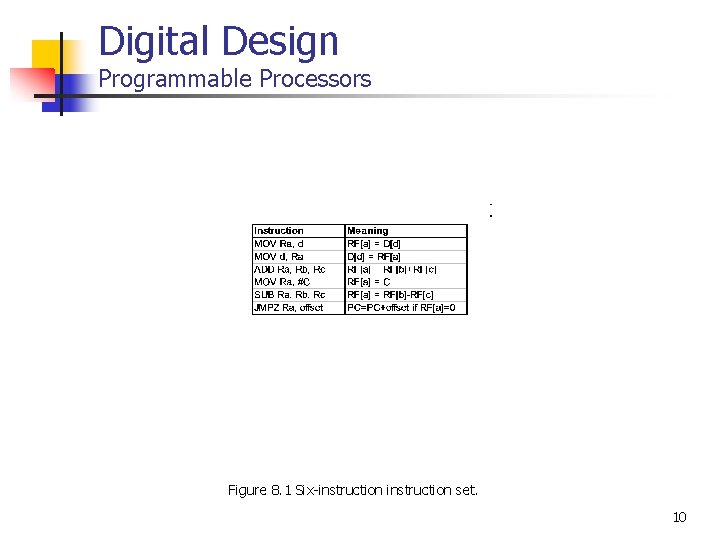

Digital Design Programmable Processors Figure 8. 1 Six-instruction set. 10

Digital Design Programmable Processors Figure 8. 9 Control unit and datapath for the six-instruction processor. 11

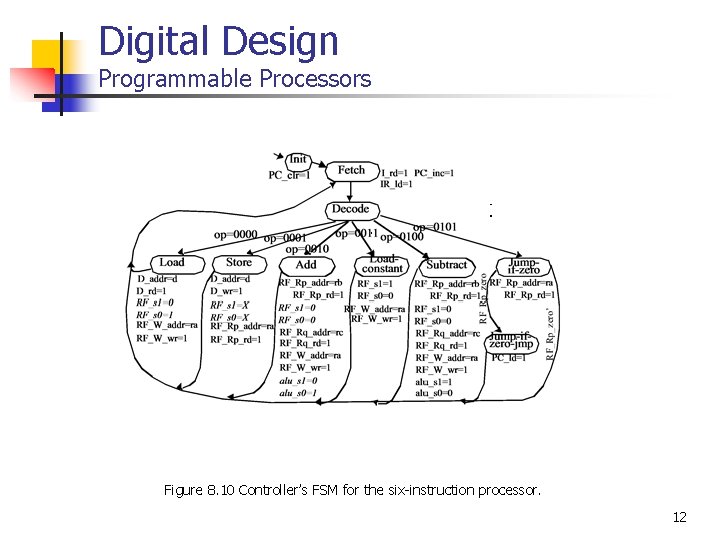

Digital Design Programmable Processors Figure 8. 10 Controller’s FSM for the six-instruction processor. 12

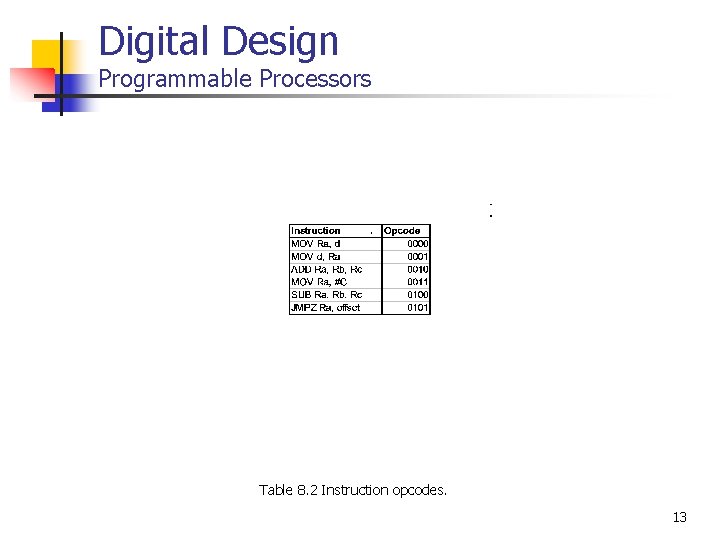

Digital Design Programmable Processors Table 8. 2 Instruction opcodes. 13

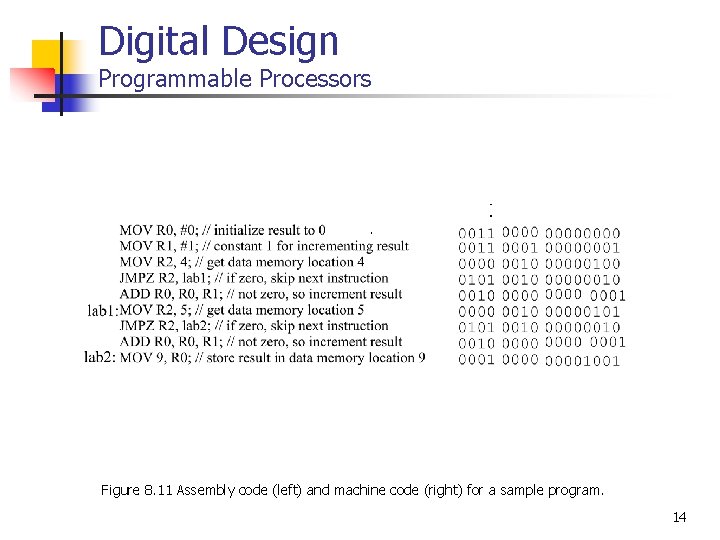

Digital Design Programmable Processors Figure 8. 11 Assembly code (left) and machine code (right) for a sample program. 14

- Slides: 14