Digital Design Module 2 Decoder Amit Kumar AP

- Slides: 20

Digital Design Module 2 Decoder Amit Kumar AP SCSE, GU Greater Noida

OUTLINE Introduction to Decoder • Implementation of 3 to 8 line Decoder • Decoder with enable input • Decoder expansion • Combinational Logic Circuit Implementation using a Decoder •

Decoder: Introduction A decoder has N inputs 2 N outputs A decoder selects one of 2 N outputs by decoding the binary value on the N inputs. The decoder generates all of the minterms of the N input variables. Exactly one output will be active for each combination of the inputs.

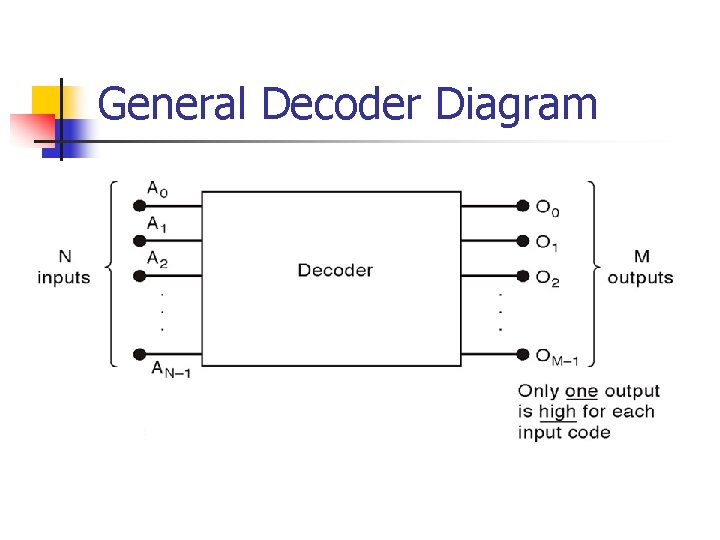

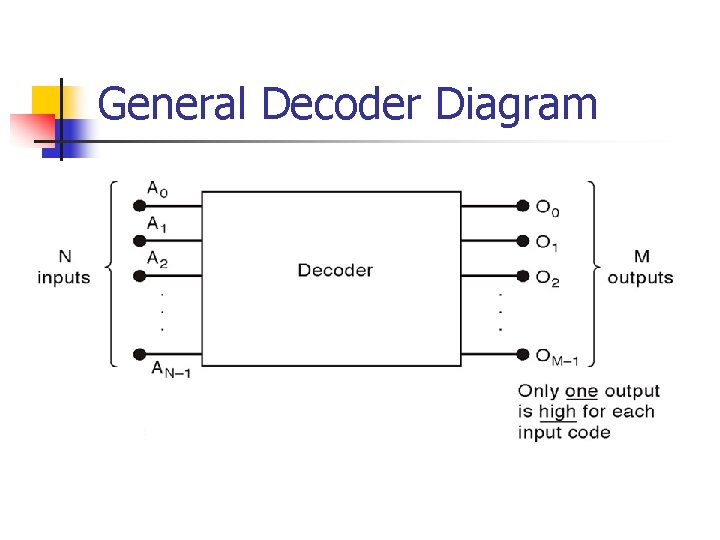

General Decoder Diagram

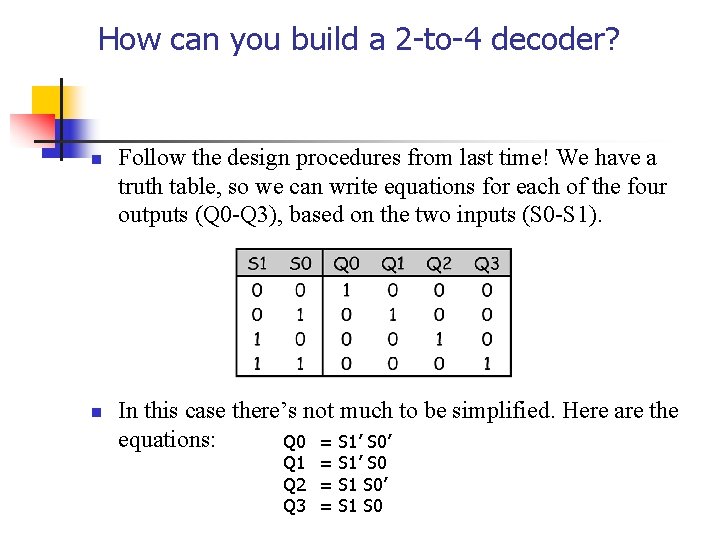

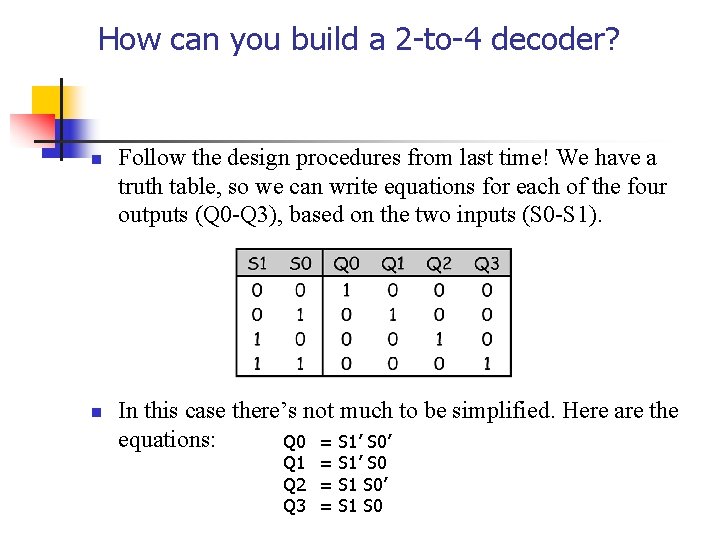

How can you build a 2 -to-4 decoder? n n Follow the design procedures from last time! We have a truth table, so we can write equations for each of the four outputs (Q 0 -Q 3), based on the two inputs (S 0 -S 1). In this case there’s not much to be simplified. Here are the equations: Q 0 = S 1’ S 0’ Q 1 = S 1’ S 0 Q 2 = S 1 S 0’ Q 3 = S 1 S 0

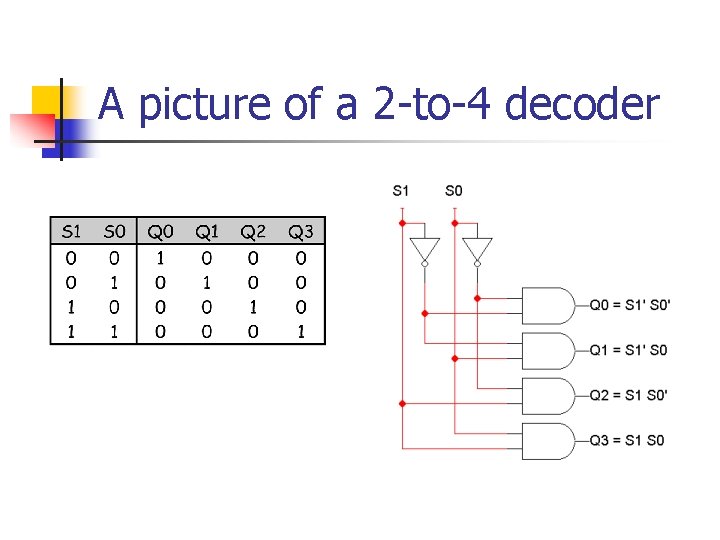

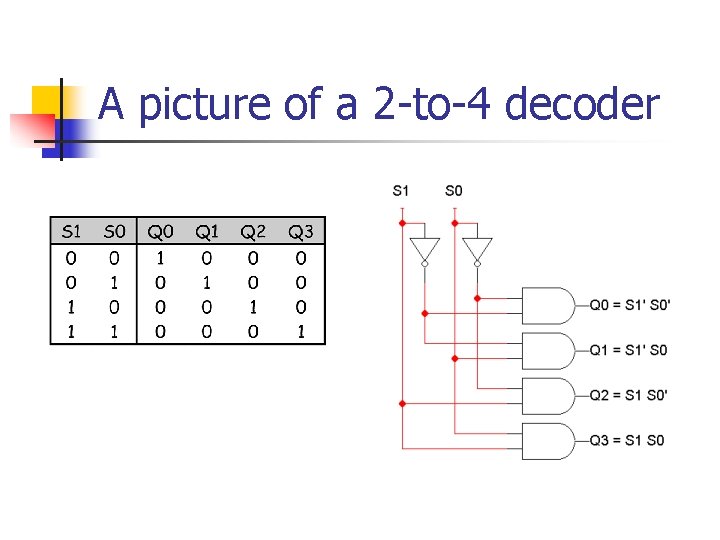

A picture of a 2 -to-4 decoder

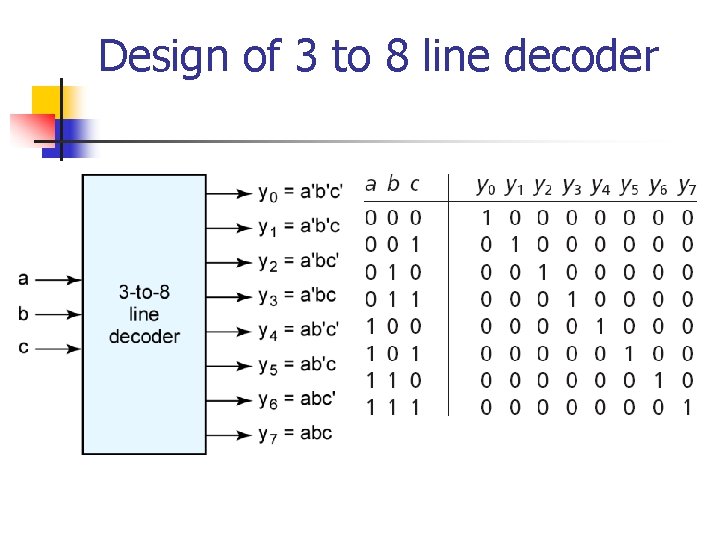

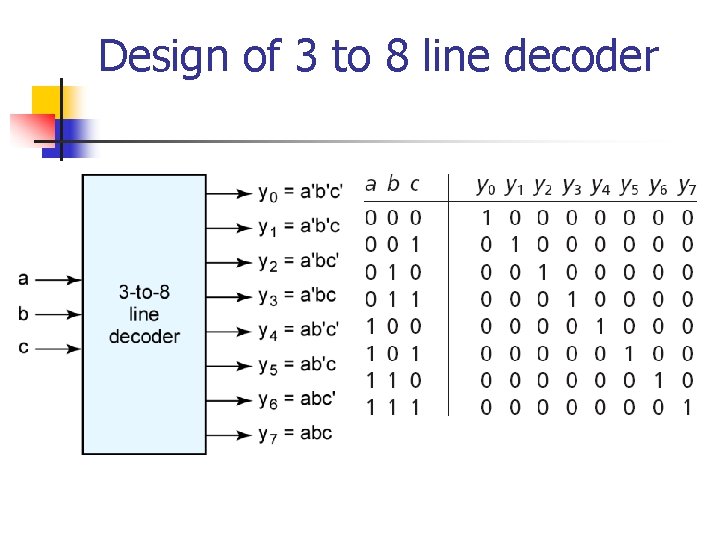

Design of 3 to 8 line decoder

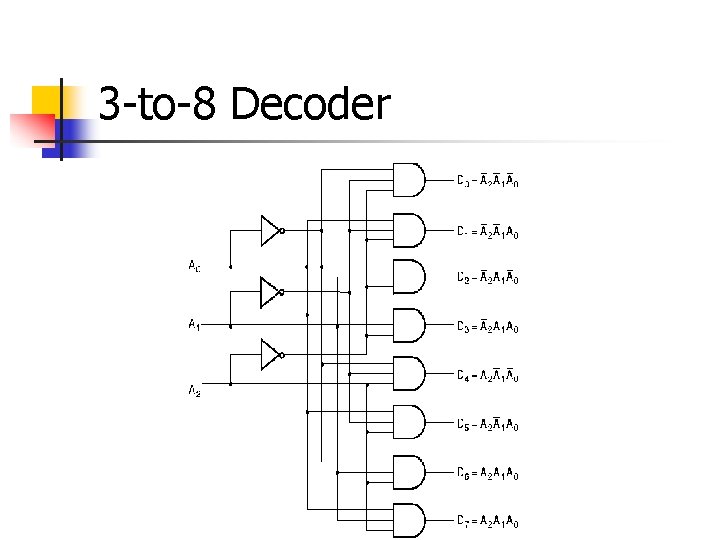

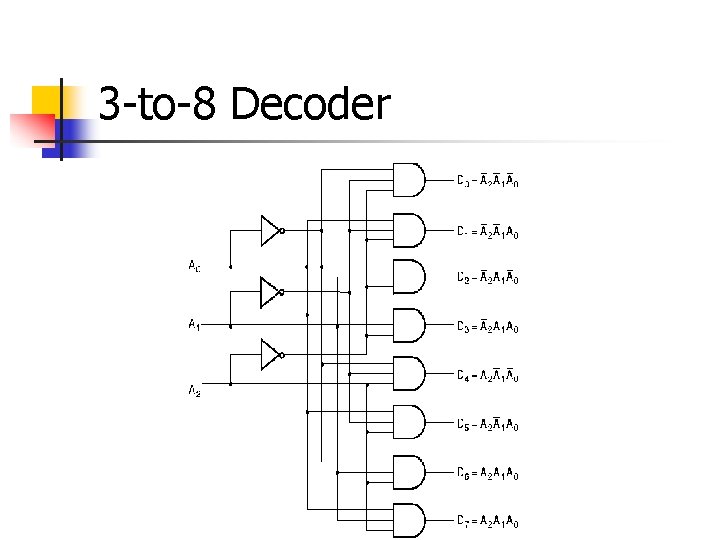

3 -to-8 Decoder

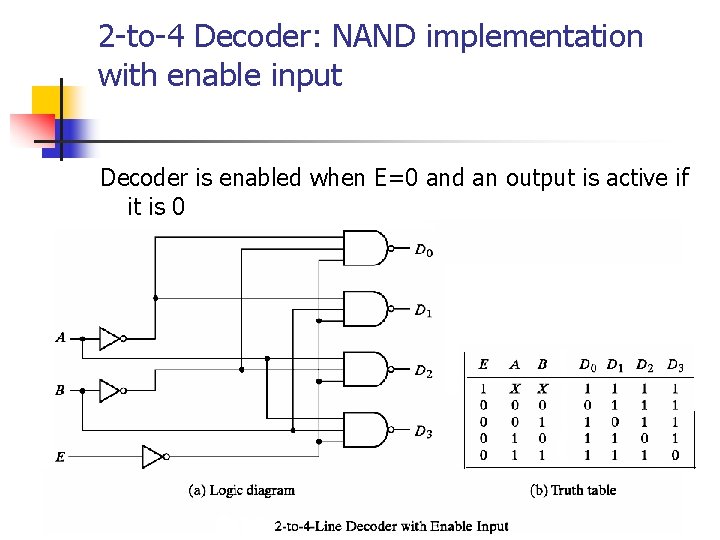

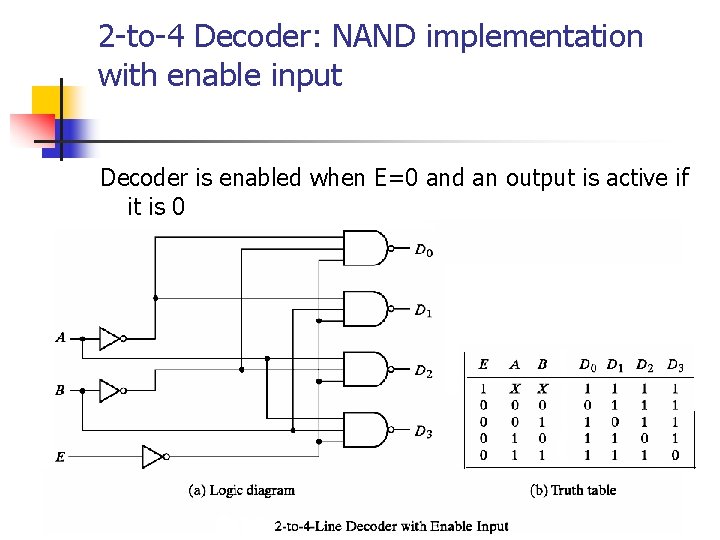

Decoder with enable input n n The circuit operates with complemented outputs and a complement enable input. The decoder is enabled when E is equal to 0. Only one output can be equal to 0 at any given time, all other outputs are equal to 1. The output whose value is equal to 0 represents the minterm selected by inputs A and B The circuit is disabled when E is equal to 1.

2 -to-4 Decoder: NAND implementation with enable input Decoder is enabled when E=0 and an output is active if it is 0

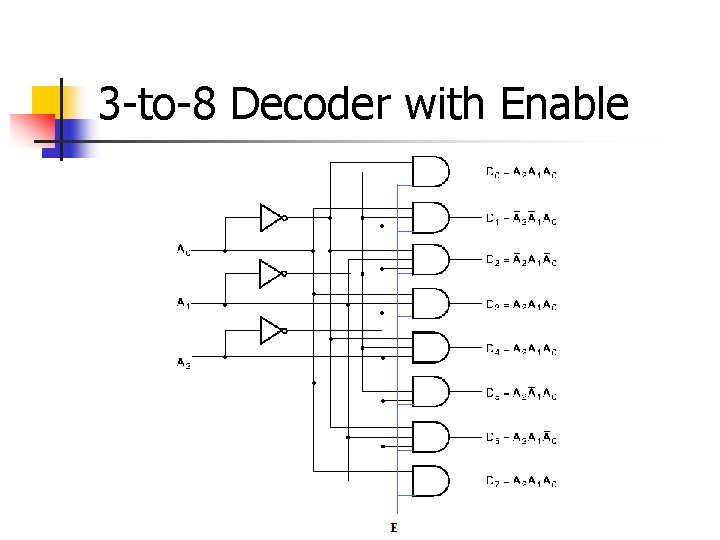

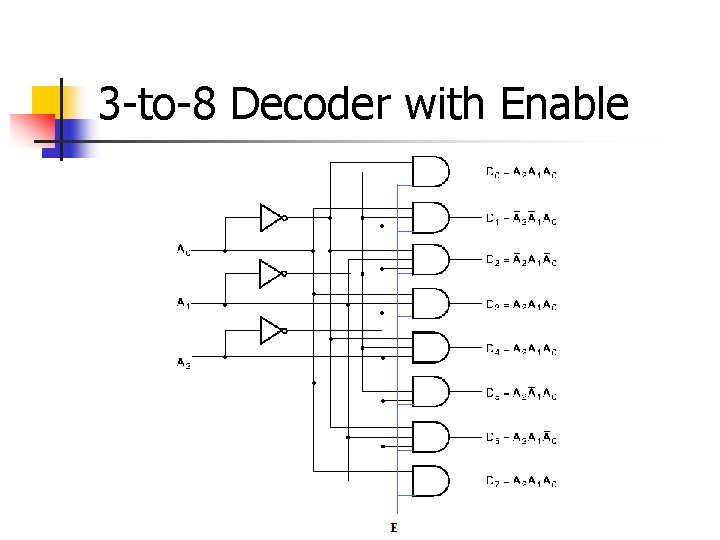

3 -to-8 Decoder with Enable

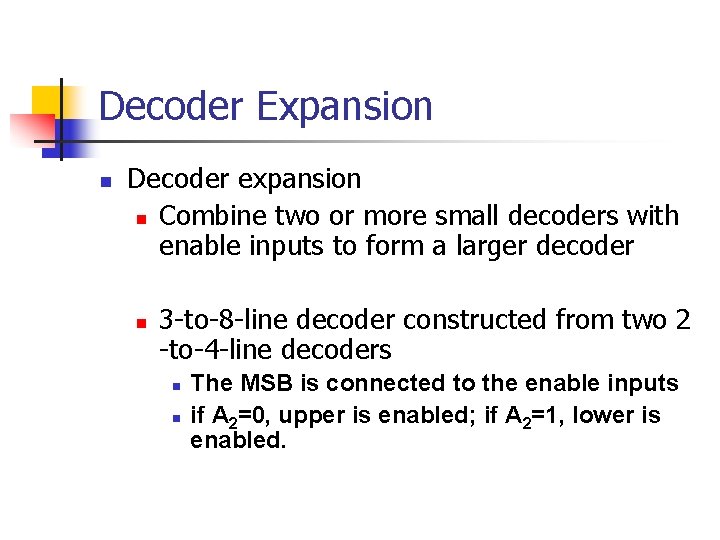

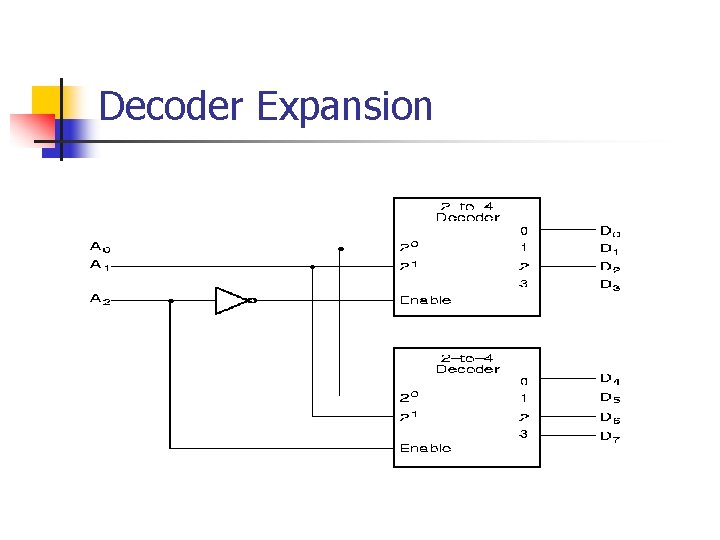

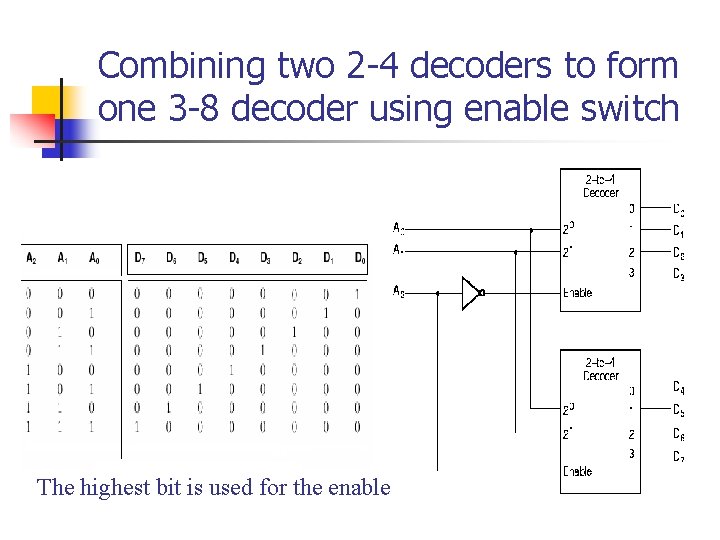

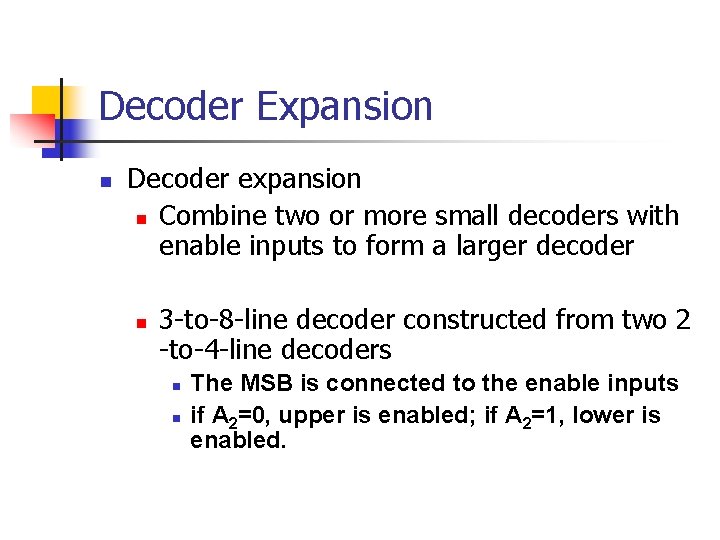

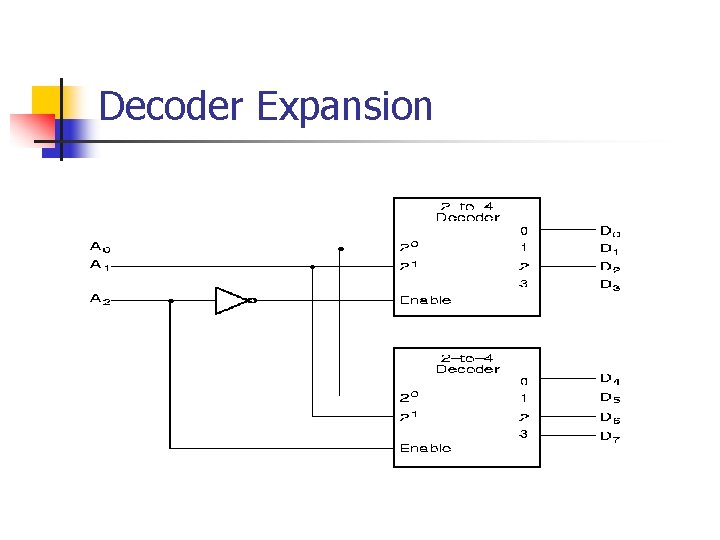

Decoder Expansion n Decoder expansion n Combine two or more small decoders with enable inputs to form a larger decoder n 3 -to-8 -line decoder constructed from two 2 -to-4 -line decoders n n The MSB is connected to the enable inputs if A 2=0, upper is enabled; if A 2=1, lower is enabled.

Decoder Expansion

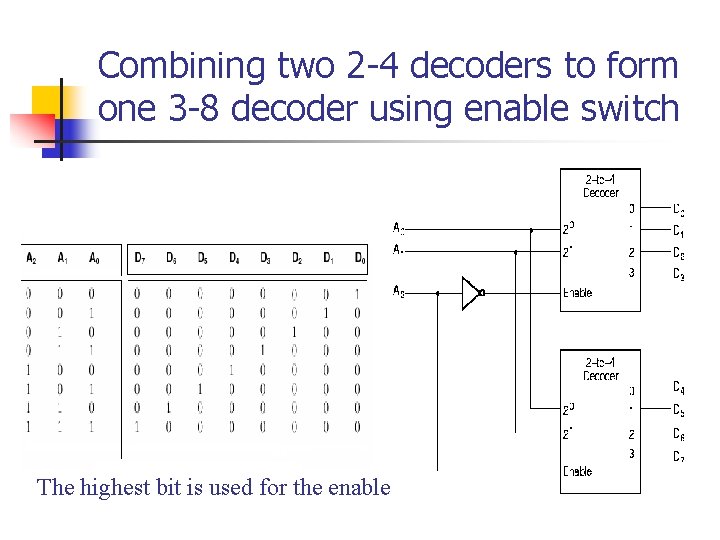

Combining two 2 -4 decoders to form one 3 -8 decoder using enable switch The highest bit is used for the enables

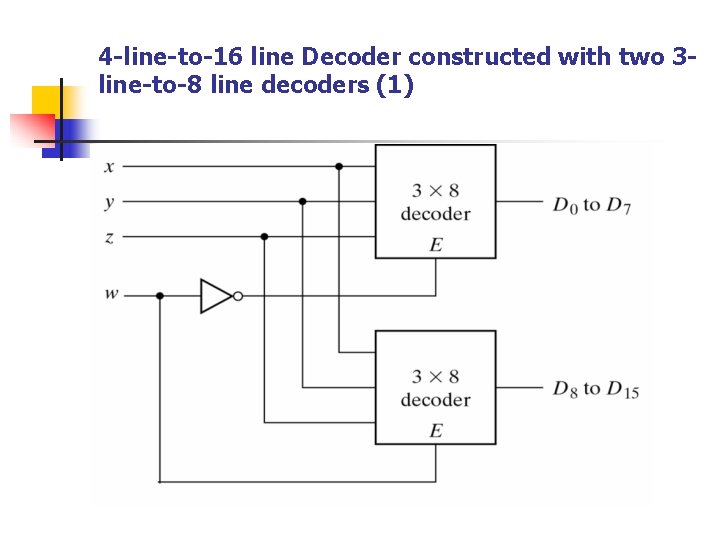

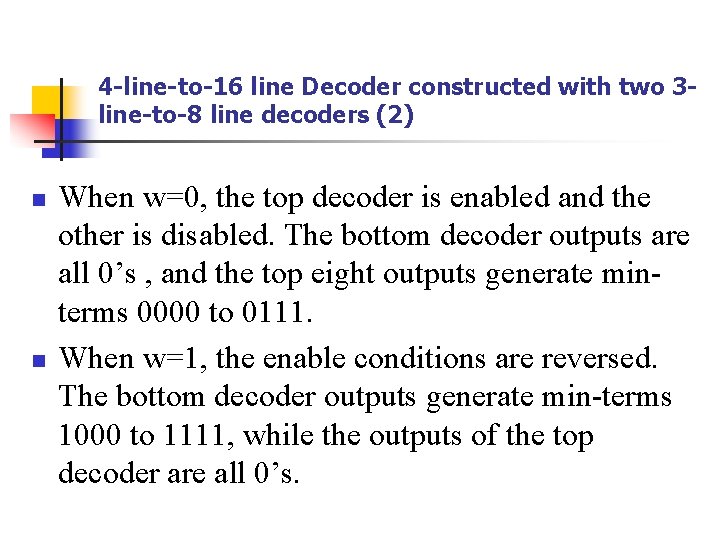

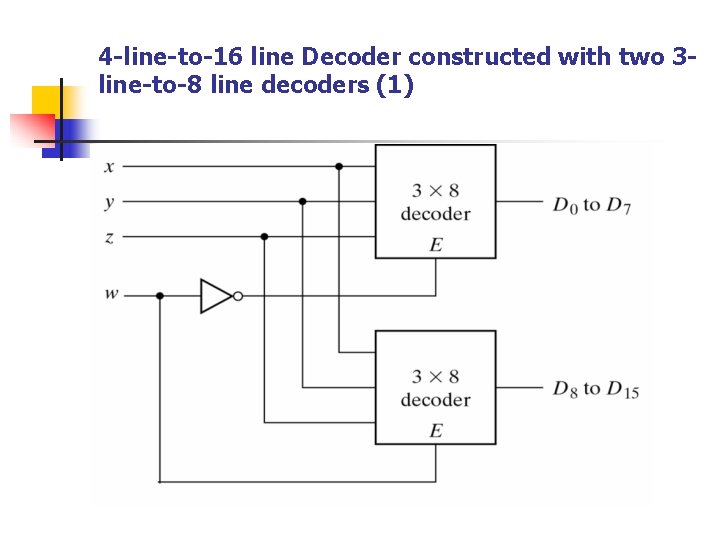

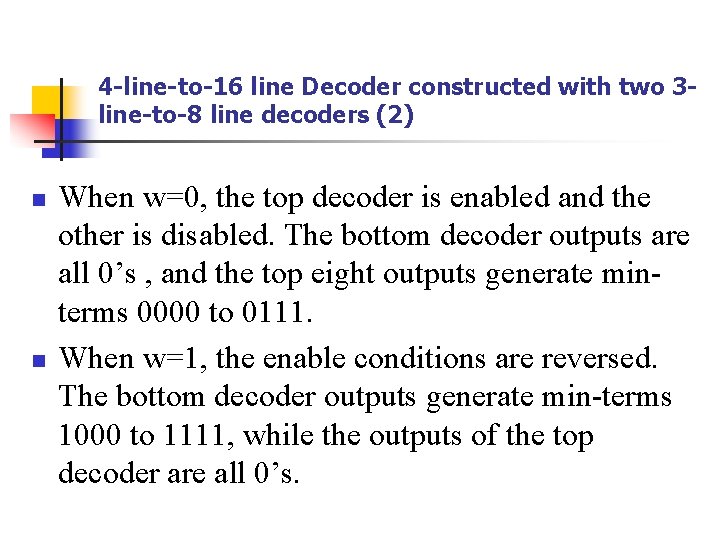

4 -line-to-16 line Decoder constructed with two 3 line-to-8 line decoders (1)

4 -line-to-16 line Decoder constructed with two 3 line-to-8 line decoders (2) n n When w=0, the top decoder is enabled and the other is disabled. The bottom decoder outputs are all 0’s , and the top eight outputs generate minterms 0000 to 0111. When w=1, the enable conditions are reversed. The bottom decoder outputs generate min-terms 1000 to 1111, while the outputs of the top decoder are all 0’s.

Combinational Logic Circuit Implementation using a Decoder n n Any combinational logic circuit with n inputs and m outputs can be implemented with an n-to-2 n-line decoder and m OR gates. Procedure: n Express the given Boolean function in sum of min-terms n Choose a decoder to generate all the min-terms of the input variables. n Select the inputs to each OR gate from the decoder outputs according to the list of min-term for each function.

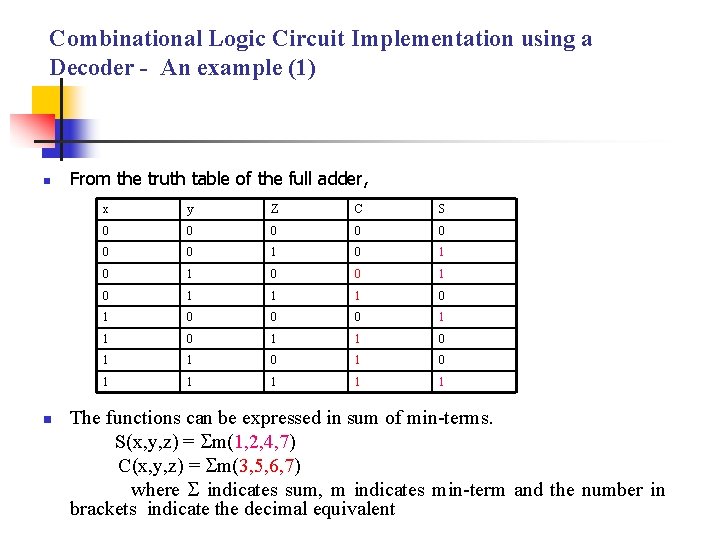

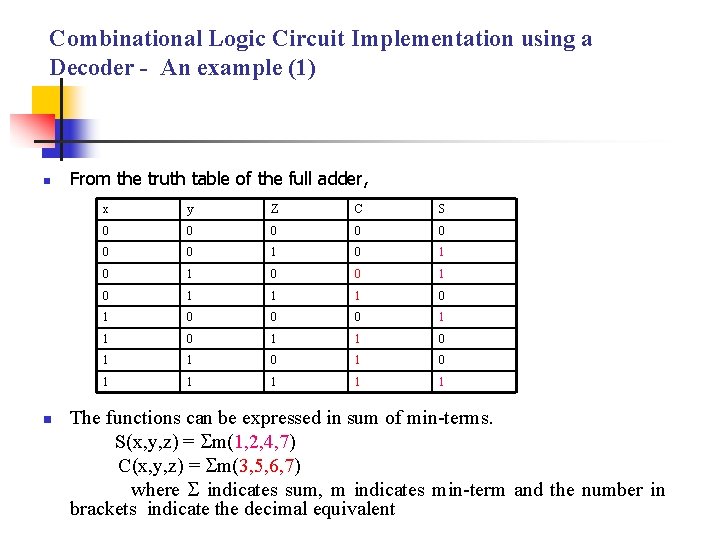

Combinational Logic Circuit Implementation using a Decoder - An example (1) n n From the truth table of the full adder, x y Z C S 0 0 0 0 1 0 1 0 1 1 1 0 0 0 1 1 0 1 1 1 The functions can be expressed in sum of min-terms. S(x, y, z) = m(1, 2, 4, 7) C(x, y, z) = m(3, 5, 6, 7) where indicates sum, m indicates min-term and the number in brackets indicate the decimal equivalent

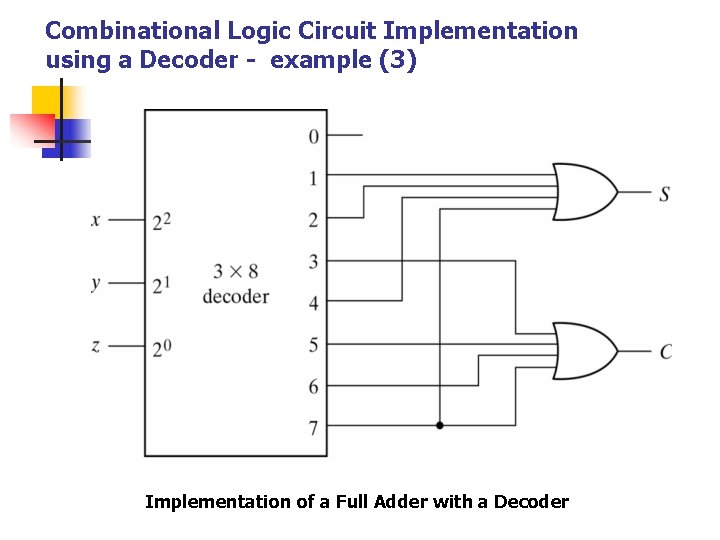

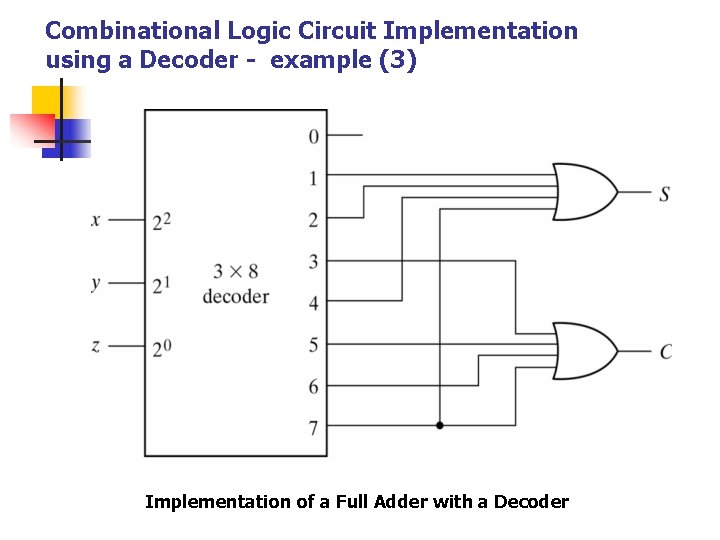

Combinational Logic Circuit Implementation using a Decoder - An example (2) Since there are three inputs and a total of eight minterms, we need a 3 -to-8 line decoder. n The decoder generates the eight min-terms for x, y, z n The OR gate for output S forms the logical sum of min-terms 1, 2, 4, and 7. n The OR gates for output C forms the logical sum of min-terms 3, 5, 6, and 7

Combinational Logic Circuit Implementation using a Decoder - example (3) Implementation of a Full Adder with a Decoder