Digital Design Hardware Description Languages Chapter 9 Hardware

- Slides: 19

Digital Design – Hardware Description Languages Chapter 9 Hardware Description Languages

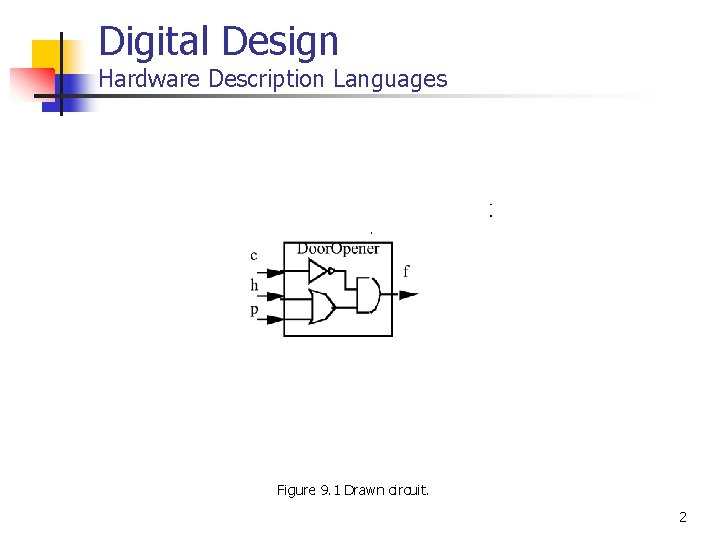

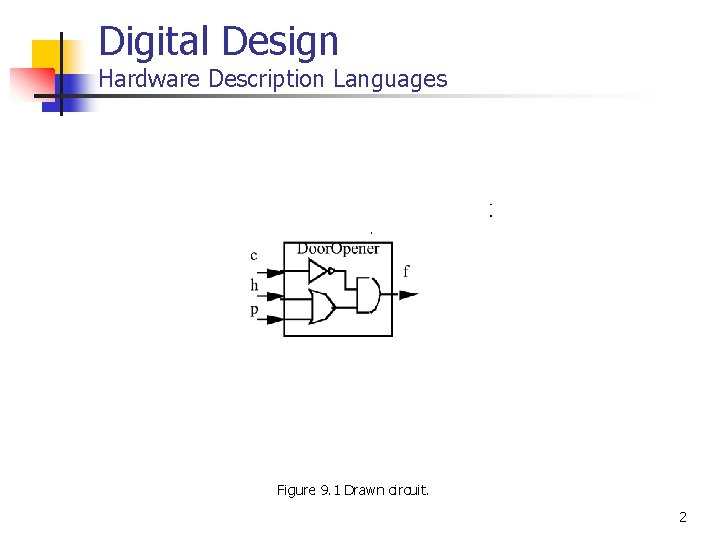

Digital Design Hardware Description Languages Figure 9. 1 Drawn circuit. 2

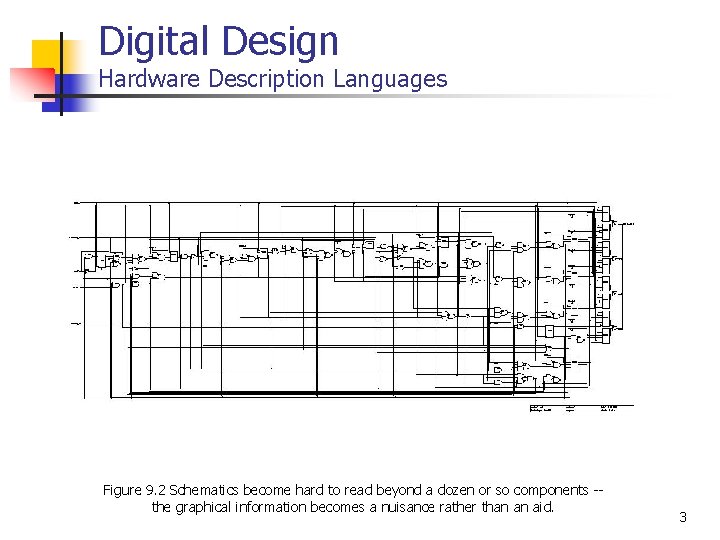

Digital Design Hardware Description Languages Figure 9. 2 Schematics become hard to read beyond a dozen or so components -the graphical information becomes a nuisance rather than an aid. 3

Digital Design Hardware Description Languages Figure 9. 3 Describing a circuit using a textual language rather than a graphical drawing: (a) schematic, (b) textual description in the English language. 4

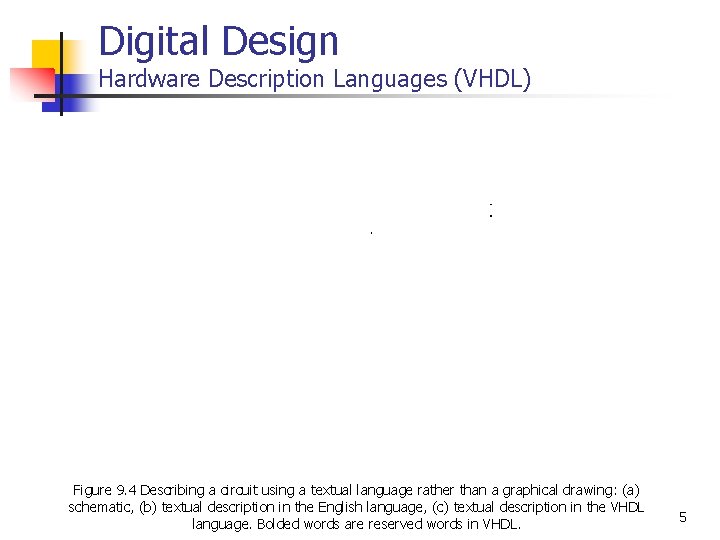

Digital Design Hardware Description Languages (VHDL) Figure 9. 4 Describing a circuit using a textual language rather than a graphical drawing: (a) schematic, (b) textual description in the English language, (c) textual description in the VHDL language. Bolded words are reserved words in VHDL. 5

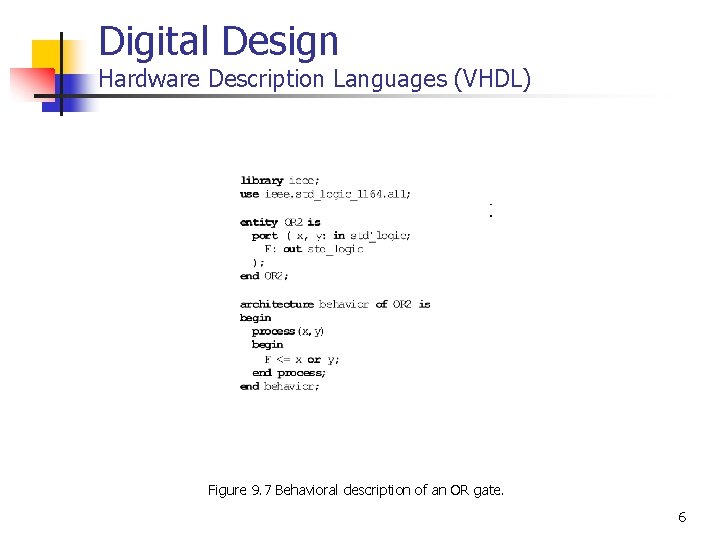

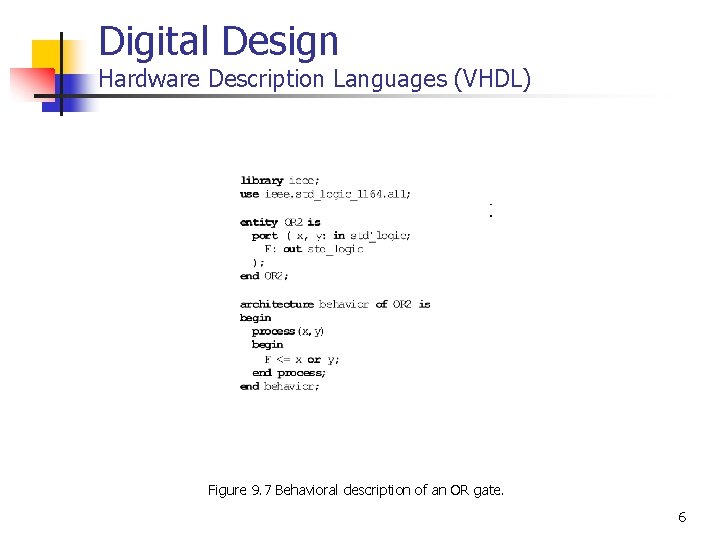

Digital Design Hardware Description Languages (VHDL) Figure 9. 7 Behavioral description of an OR gate. 6

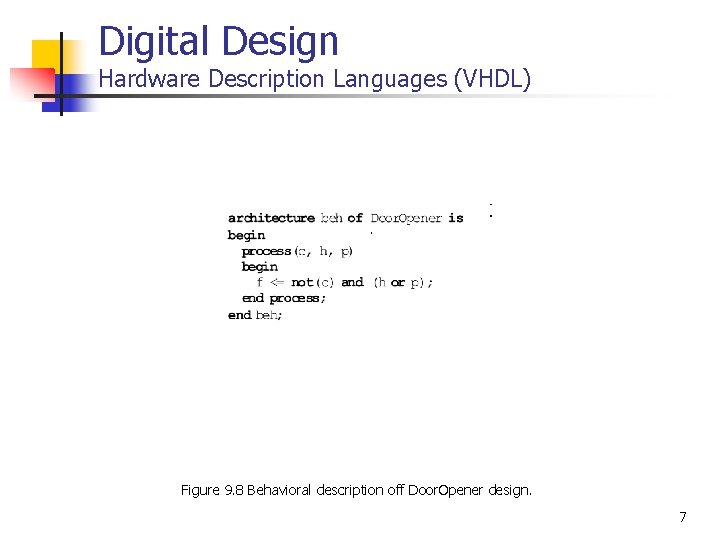

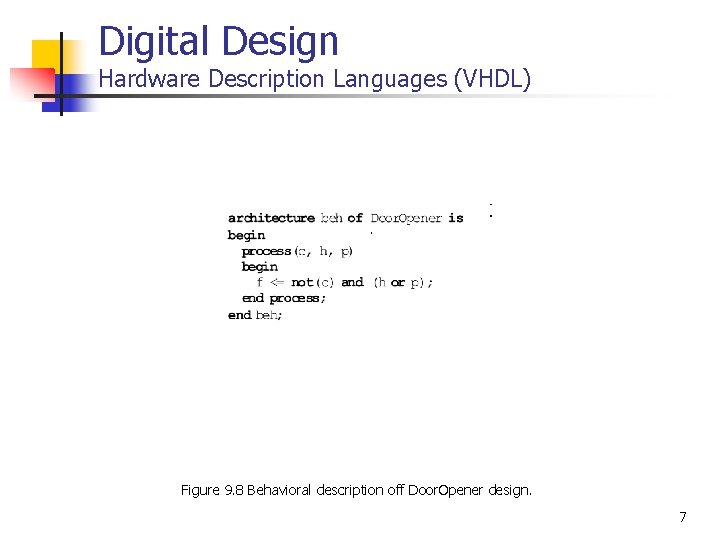

Digital Design Hardware Description Languages (VHDL) Figure 9. 8 Behavioral description off Door. Opener design. 7

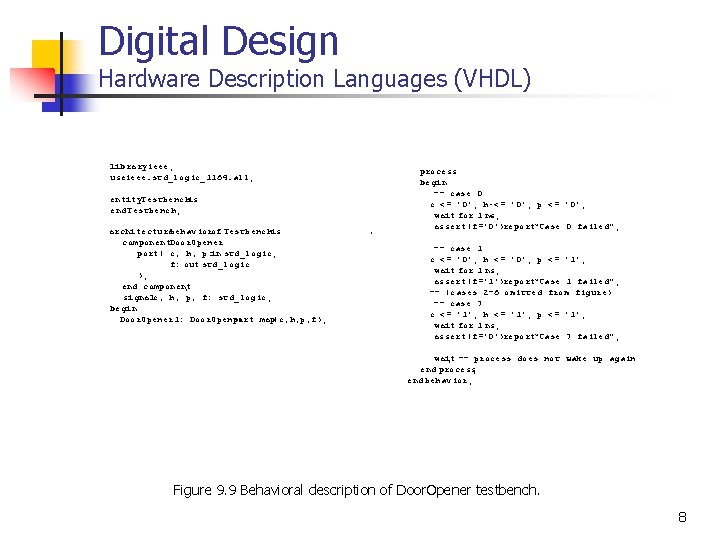

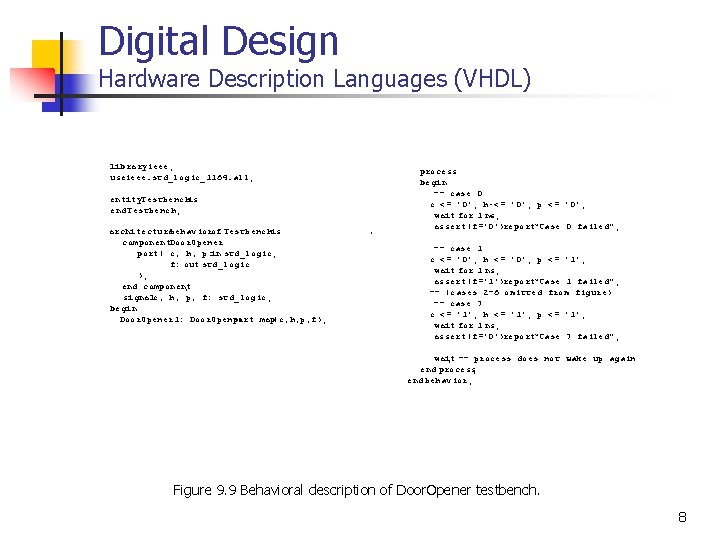

Digital Design Hardware Description Languages (VHDL) libraryieee; useieee. std_logic_1164. all; entity. Testbenchis end Testbench; architecturebehaviorof Testbenchis component. Door. Opener port ( c, h, p: in std_logic; f: out std_logic ); end component ; signalc, h, p, f: std_logic; begin Door. Opener 1: Door. Opener port map(c, h, p, f); process begin -- case 0 c <= ’ 0’; h <= ’ 0’; p <= ’ 0’; wait for 1 ns; assert (f=’ 0’)report“Case 0 failed”; -- case 1 c <= ’ 0’; h <= ’ 0’; p <= ’ 1’; wait for 1 ns; assert (f=’ 1’)report“Case 1 failed”; -- (cases 2 -6 omitted from figure) -- case 7 c <= ’ 1’; h <= ’ 1’; p <= ’ 1’; wait for 1 ns; assert (f=’ 0’)report“Case 7 failed”; wait ; -- process does not wake up again end process ; end behavior; Figure 9. 9 Behavioral description of Door. Opener testbench. 8

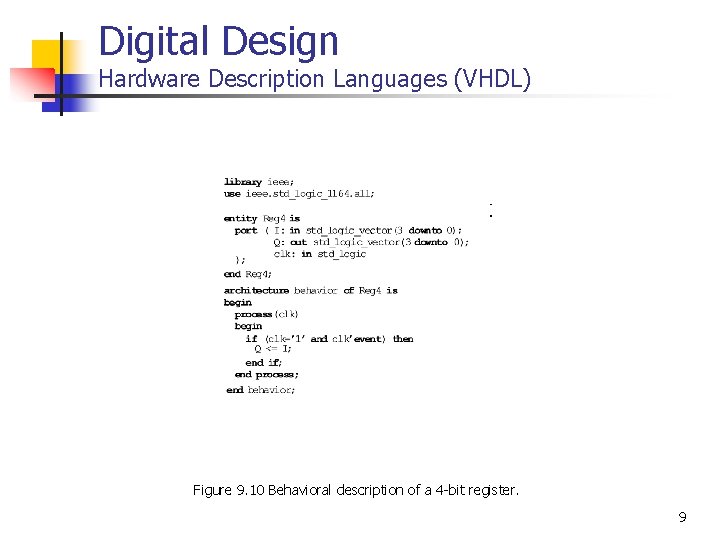

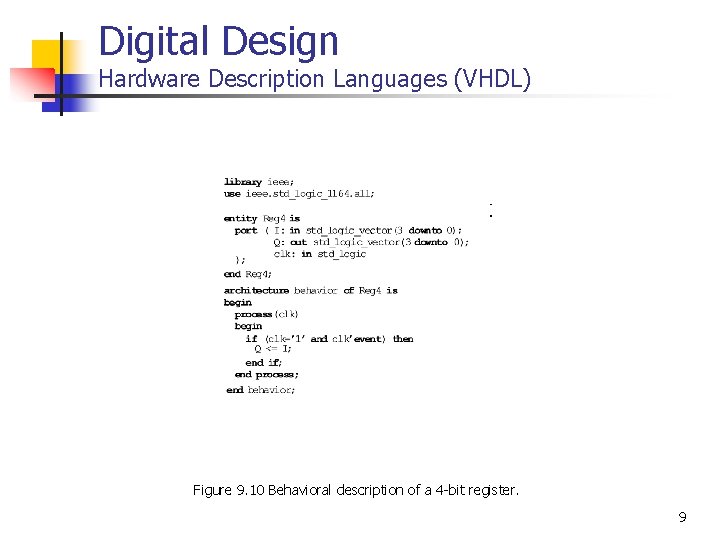

Digital Design Hardware Description Languages (VHDL) Figure 9. 10 Behavioral description of a 4 -bit register. 9

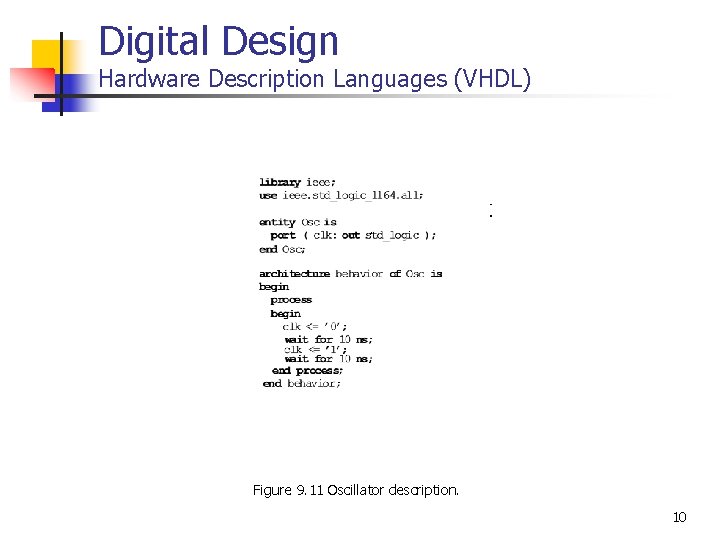

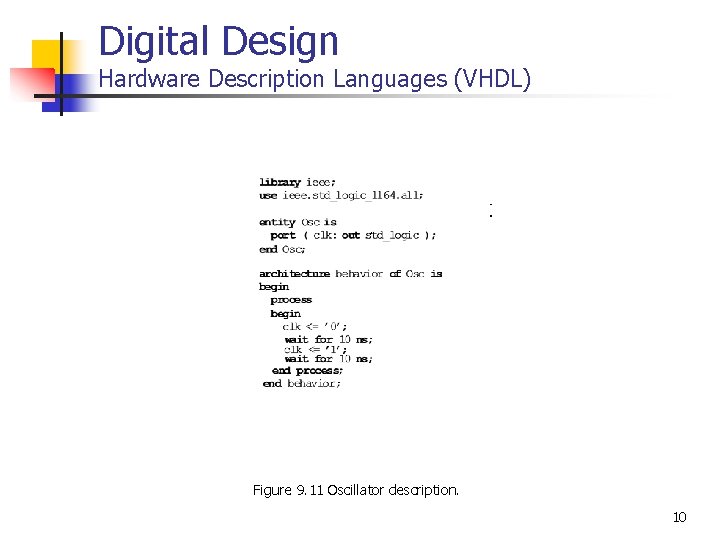

Digital Design Hardware Description Languages (VHDL) Figure 9. 11 Oscillator description. 10

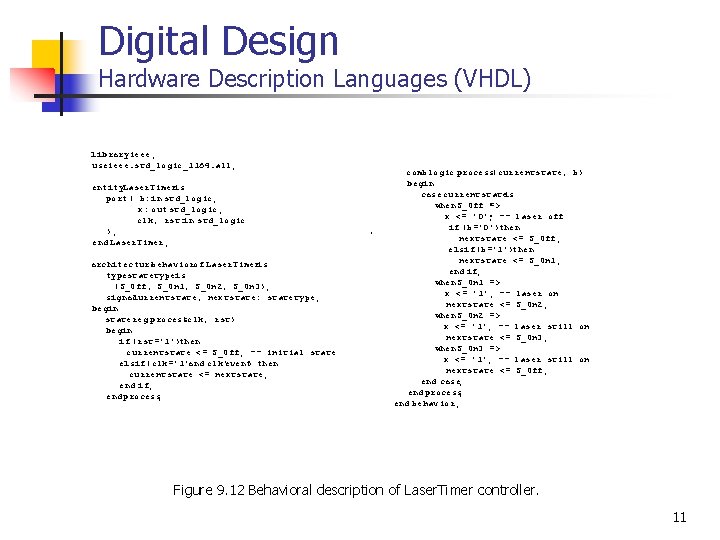

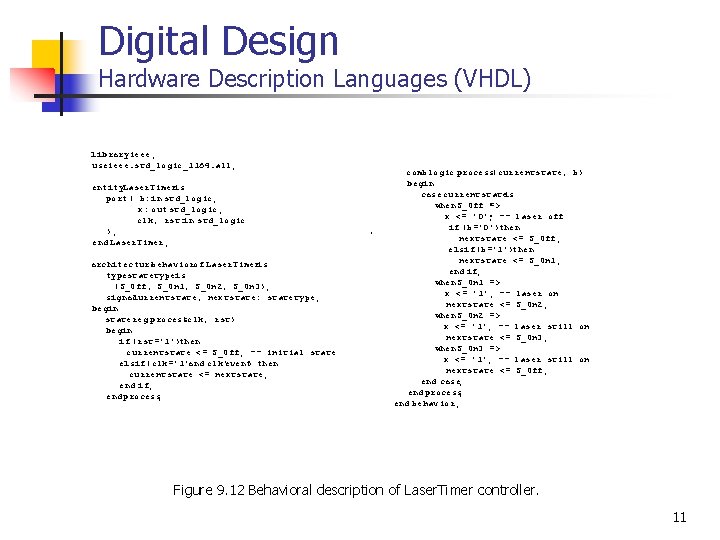

Digital Design Hardware Description Languages (VHDL) libraryieee; useieee. std_logic_1164. all; entity. Laser. Timeris port ( b: in std_logic; x: out std_logic; clk, rst: in std_logic ); end Laser. Timer; architecturebehaviorof Laser. Timeris typestatetypeis (S_Off, S_On 1, S_On 2, S_On 3); signal currentstate, nextstate: statetype; begin statereg: process (clk, rst) begin if (rst=’ 1’)then currentstate <= S_Off; -- initial state elsif (clk=’ 1’and clk’event) then currentstate <= nextstate; end if; end process ; comblogic: process(currentstate, b) begin case currentstateis when S_Off => x <= ’ 0’; -- laser off if (b=’ 0’)then nextstate <= S_Off; elsif (b=’ 1’)then nextstate <= S_On 1; end if; when S_On 1 => x <= ’ 1’; -- laser on nextstate <= S_On 2; when S_On 2 => x <= ’ 1’; -- laser still on nextstate <= S_On 3; when S_On 3 => x <= ’ 1’; -- laser still on nextstate <= S_Off; end case; end process ; end behavior; Figure 9. 12 Behavioral description of Laser. Timer controller. 11

Digital Design Hardware Description Languages (VHDL) Figure 9. 13 Behavioral description of a full-adder. 12

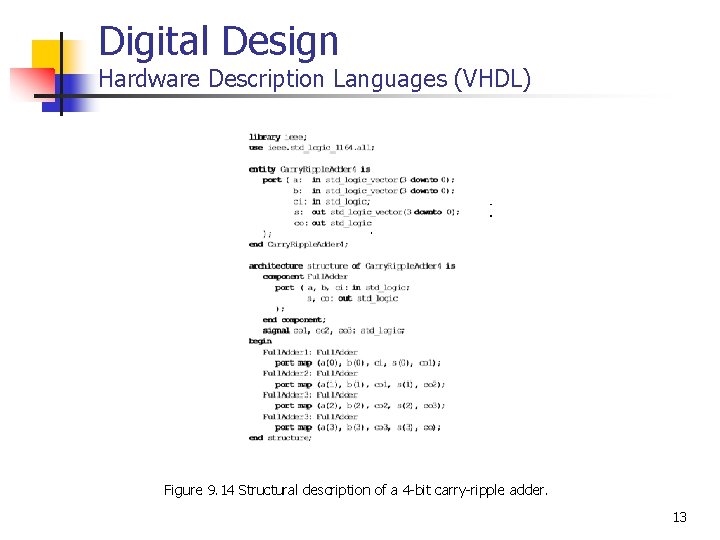

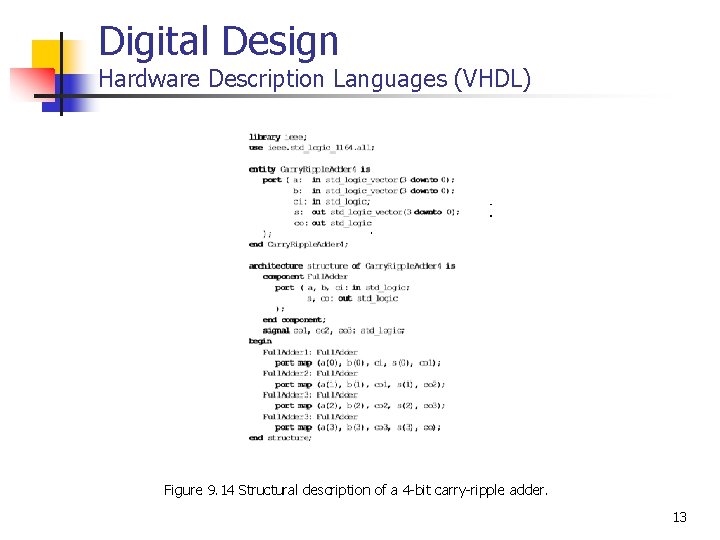

Digital Design Hardware Description Languages (VHDL) Figure 9. 14 Structural description of a 4 -bit carry-ripple adder. 13

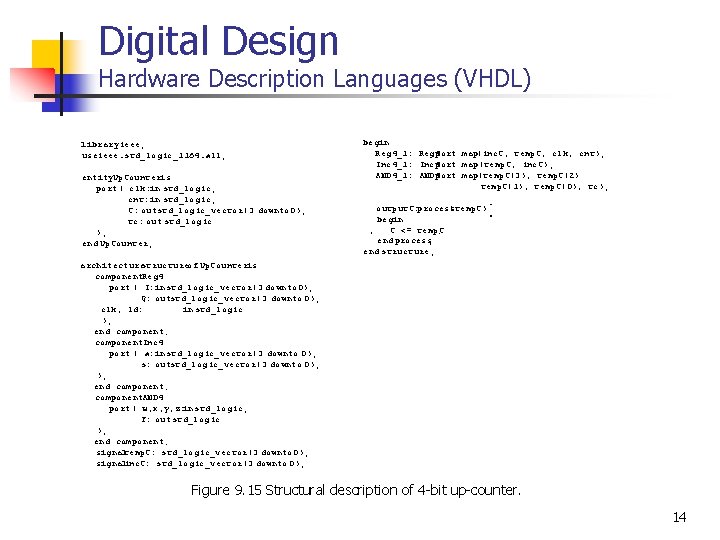

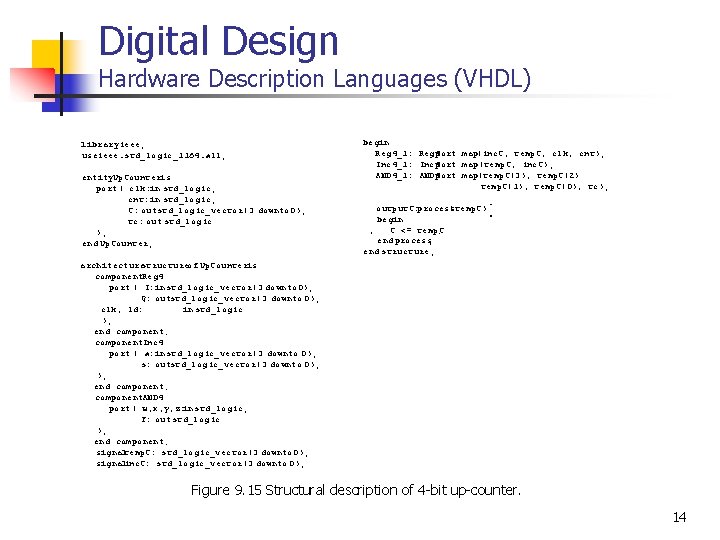

Digital Design Hardware Description Languages (VHDL) libraryieee; useieee. std_logic_1164. all; entity. Up. Counteris port ( clk: in std_logic; cnt: in std_logic; C: outstd_logic_vector(3 downto 0); tc: out std_logic ); end Up. Counter; begin Reg 4_1: Reg 4 port map(inc. C, temp. C, clk, cnt); Inc 4_1: Inc 4 port map(temp. C, inc. C); AND 4_1: AND 4 port map(temp. C(3), temp. C(2) temp. C(1), temp. C(0), tc); output. C: process (temp. C) begin C <= temp. C ; end process ; end structure; architecturestructureof Up. Counteris component. Reg 4 port ( I: instd_logic_vector(3 downto 0); Q: outstd_logic_vector(3 downto 0); clk, ld: in std_logic ); end component; component. Inc 4 port ( a: instd_logic_vector(3 downto 0); s: outstd_logic_vector(3 downto 0); ); end component; component. AND 4 port ( w, x, y, z: in std_logic; F: out std_logic ); end component; signaltemp. C: std_logic_vector(3 downto 0); signalinc. C: std_logic_vector(3 downto 0); Figure 9. 15 Structural description of 4 -bit up-counter. 14

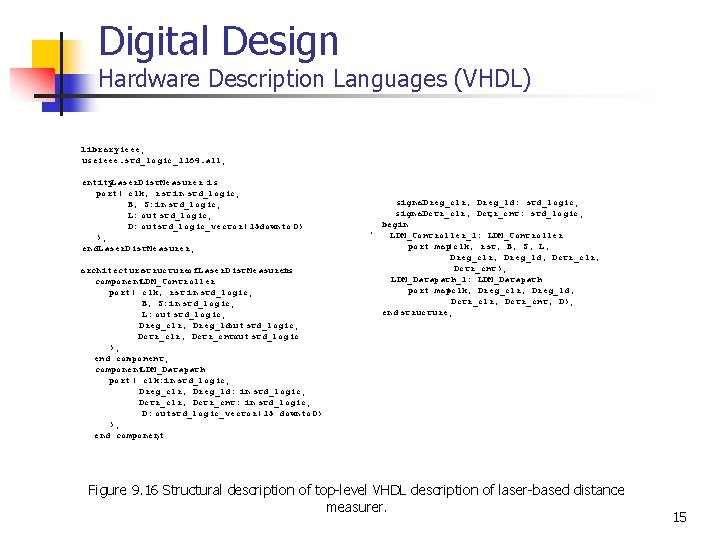

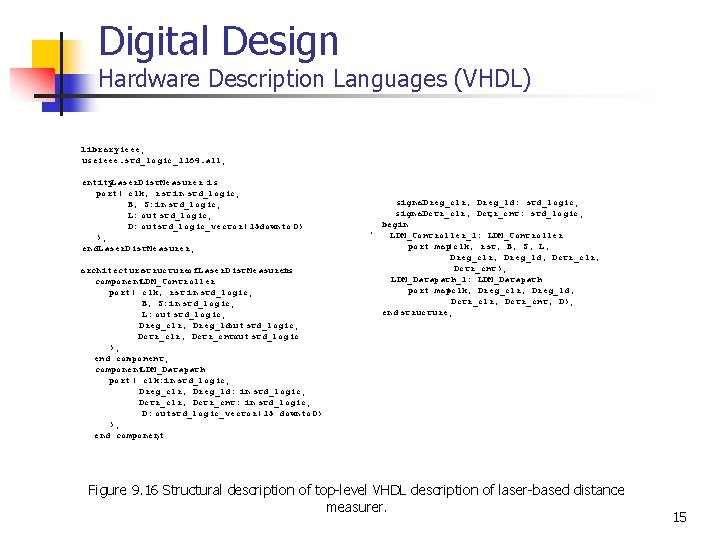

Digital Design Hardware Description Languages (VHDL) libraryieee; useieee. std_logic_1164. all; entity. Laser. Dist. Measurer is port( clk, rst: in std_logic; B, S: in std_logic; L: out std_logic; D: outstd_logic_vector(15 downto 0) ); end. Laser. Dist. Measurer; architecturestructureof. Laser. Dist. Measurer is component. LDM_Controller port ( clk, rst: in std_logic; B, S: in std_logic; L: out std_logic; Dreg_clr, Dreg_ld: out std_logic; Dctr_clr, Dctr_cnt: out std_logic ); end component; component. LDM_Datapath port ( clk: in std_logic; Dreg_clr, Dreg_ld: in std_logic; Dctr_clr, Dctr_cnt: in std_logic; D: outstd_logic_vector(15 downto 0) ); end component ; signal Dreg_clr, Dreg_ld: std_logic; signal Dctr_clr, Dctr_cnt: std_logic; begin LDM_Controller_1: LDM_Controller port map(clk, rst, B, S, L, Dreg_clr, Dreg_ld, Dctr_clr, Dctr_cnt); LDM_Datapath_1: LDM_Datapath port map (clk, Dreg_clr, Dreg_ld, Dctr_clr, Dctr_cnt, D); end structure; Figure 9. 16 Structural description of top-level VHDL description of laser-based distance measurer. 15

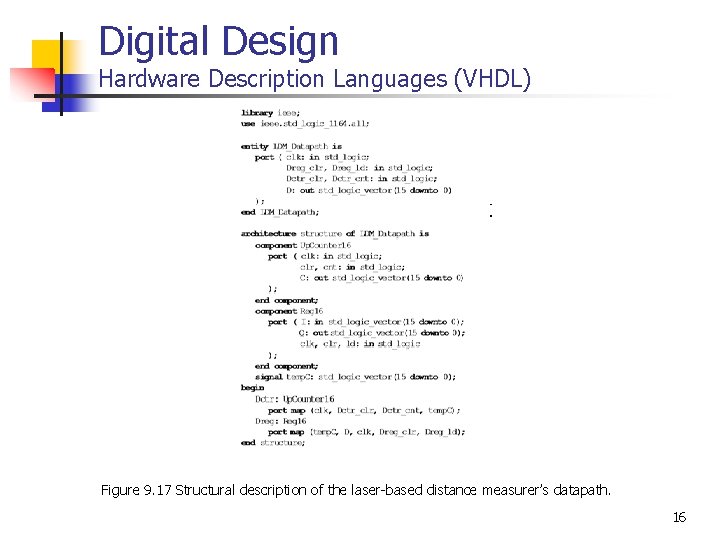

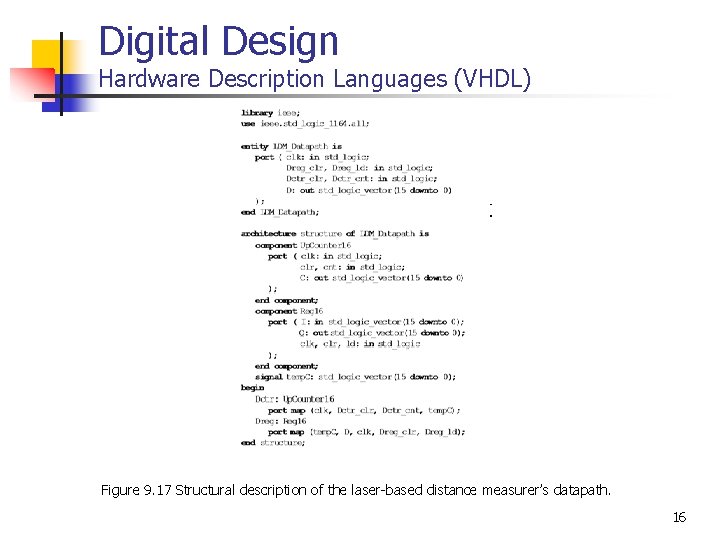

Digital Design Hardware Description Languages (VHDL) Figure 9. 17 Structural description of the laser-based distance measurer’s datapath. 16

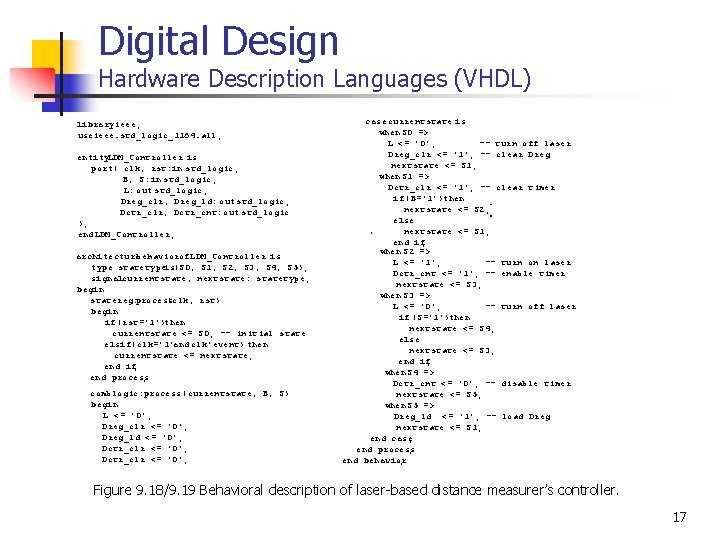

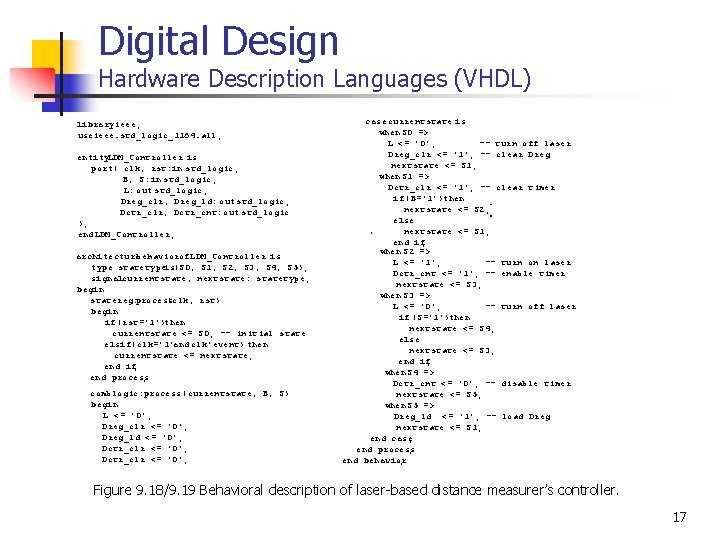

Digital Design Hardware Description Languages (VHDL) libraryieee; useieee. std_logic_1164. all; entity. LDM_Controller is port( clk, rst: in std_logic; B, S: in std_logic; L: out std_logic; Dreg_clr, Dreg_ld: out std_logic; Dctr_clr, Dctr_cnt: out std_logic ); end LDM_Controller; architecturebehaviorof LDM_Controller is type statetypeis(S 0, S 1, S 2, S 3, S 4, S 5); signalcurrentstate, nextstate: statetype; begin statereg: process (clk, rst) begin if (rst=’ 1’)then currentstate <= S 0; -- initial state elsif (clk=’ 1’and clk’event) then currentstate <= nextstate; end if; end process ; comblogic: process (currentstate, B, S) begin L <= ’ 0’; Dreg_clr <= ’ 0’; Dreg_ld <= ’ 0’; Dctr_clr <= ’ 0’; case currentstate is when S 0 => L <= ’ 0’; -- turn off laser Dreg_clr <= ’ 1’; -- clear Dreg nextstate <= S 1; when S 1 => Dctr_clr <= ’ 1’; -- clear timer if (B=’ 1’)then nextstate <= S 2; else nextstate <= S 1; end if ; when S 2 => L <= ’ 1’; -- turn on laser Dctr_cnt <= ’ 1’; -- enable timer nextstate <= S 3; when S 3 => L <= ’ 0’; -- turn off laser if (S=’ 1’)then nextstate <= S 4; else nextstate <= S 3; end if ; when S 4 => Dctr_cnt <= ’ 0’; -- disable timer nextstate <= S 5; when S 5 => Dreg_ld <= ’ 1’; -- load Dreg nextstate <= S 1; end case ; end process ; end behavior ; Figure 9. 18/9. 19 Behavioral description of laser-based distance measurer’s controller. 17

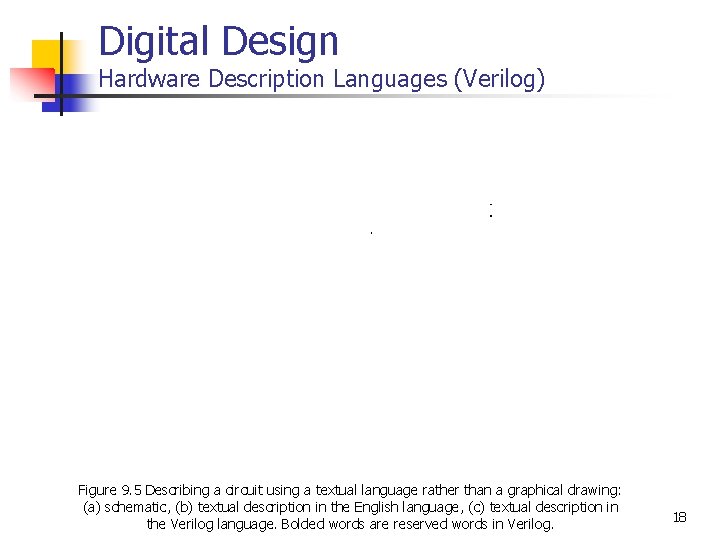

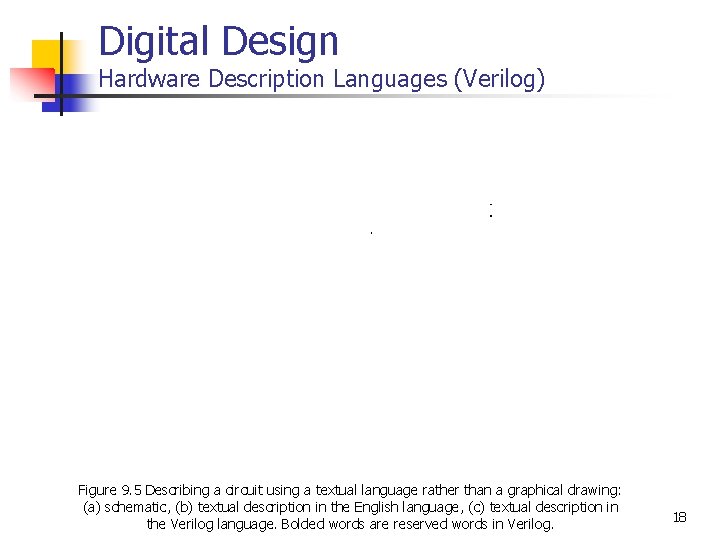

Digital Design Hardware Description Languages (Verilog) Figure 9. 5 Describing a circuit using a textual language rather than a graphical drawing: (a) schematic, (b) textual description in the English language, (c) textual description in the Verilog language. Bolded words are reserved words in Verilog. 18

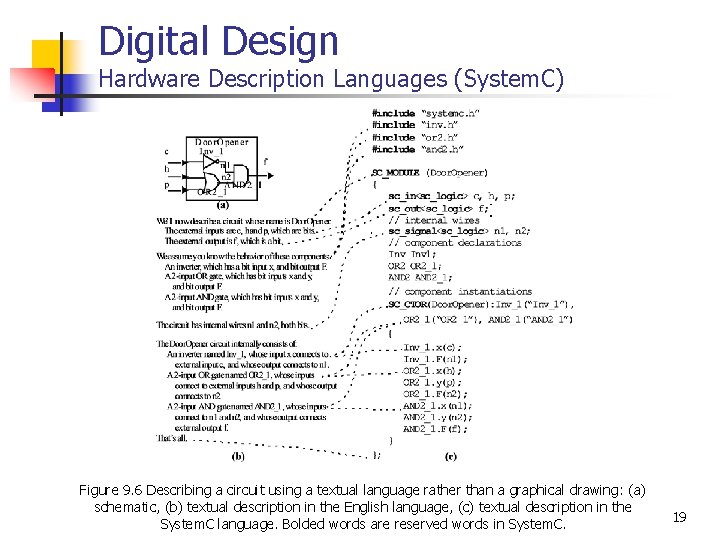

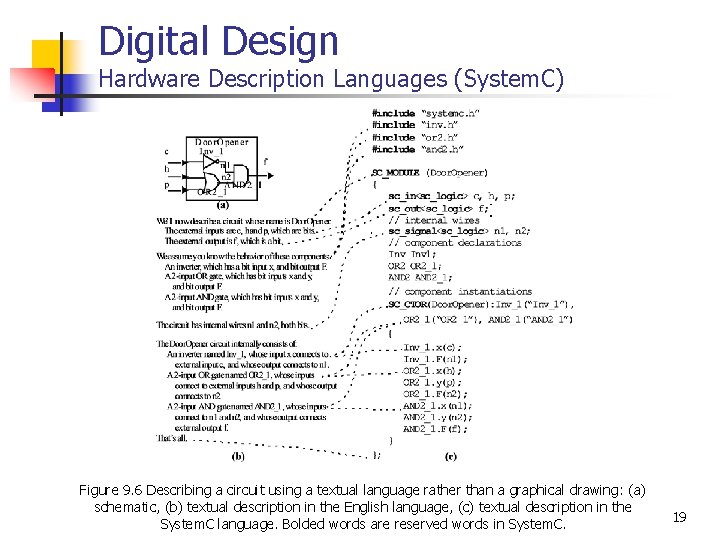

Digital Design Hardware Description Languages (System. C) Figure 9. 6 Describing a circuit using a textual language rather than a graphical drawing: (a) schematic, (b) textual description in the English language, (c) textual description in the System. C language. Bolded words are reserved words in System. C. 19