Digital Design Chapter 8 Programmable Processors Slides to

Digital Design Chapter 8: Programmable Processors Slides to accompany the textbook Digital Design, First Edition, by Frank Vahid, John Wiley and Sons Publishers, 2007. http: //www. ddvahid. com Copyright © 2007 Frank Vahid Instructors of courses requiring Vahid's Digital Design textbook (published by John Wiley and Sons) have permission to modify and use these slides for customary course-related activities, subject to keeping this copyright notice in place and unmodified. These slides may be posted as unanimated pdf versions on publicly-accessible course websites. . Power. Point source (or pdf Digital Design with animations) may not be posted to publicly-accessible websites, but may be posted for students on internal protected sites or distributed directly to students by other electronic means. Copyright © 2006 1 Instructors may make printouts of the slides available to students for a reasonable photocopying charge, without incurring royalties. Any other use requires explicit permission. Instructors Franksource Vahid may obtain Power. Point or obtain special use permissions from Wiley – see http: //www. ddvahid. com for information.

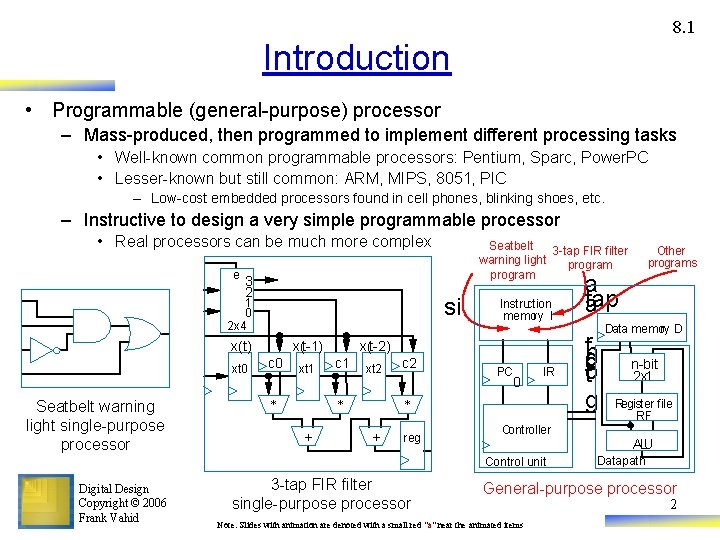

8. 1 Introduction • Programmable (general-purpose) processor – Mass-produced, then programmed to implement different processing tasks • Well-known common programmable processors: Pentium, Sparc, Power. PC • Lesser-known but still common: ARM, MIPS, 8051, PIC – Low-cost embedded processors found in cell phones, blinking shoes, etc. – Instructive to design a very simple programmable processor • Real processors can be much more complex e 3 2 si 1 0 2 x 4 x(t) xt 0 Seatbelt warning light single-purpose processor Seatbelt 3 -tap FIR filter warning light program x(t-1) c 0 xt 1 * x(t-2) c 1 xt 2 * + Instruction memory I c 2 PC 0 IR * + reg Controller Control unit Digital Design Copyright © 2006 Frank Vahid 3 -tap FIR filter single-purpose processor Other programs a tap a rtn o co t g Data memory D n-bit 2 x 1 Register file RF ALU Datapath General-purpose processor Note: Slides with animation are denoted with a small red "a" near the animated items 2

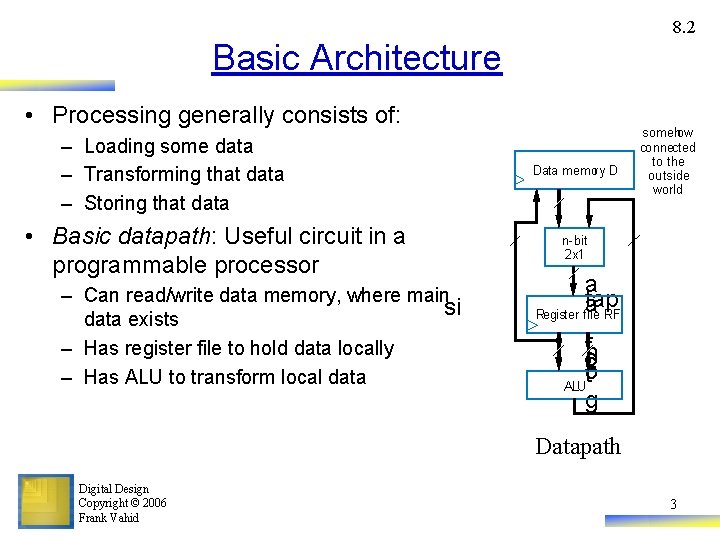

8. 2 Basic Architecture • Processing generally consists of: – Loading some data – Transforming that data – Storing that data • Basic datapath: Useful circuit in a programmable processor – Can read/write data memory, where main si data exists – Has register file to hold data locally – Has ALU to transform local data Data memory D somehow connected to the outside world n-bit 2 x 1 a tap a Register file RF rtn o co t ALU g Datapath Digital Design Copyright © 2006 Frank Vahid 3

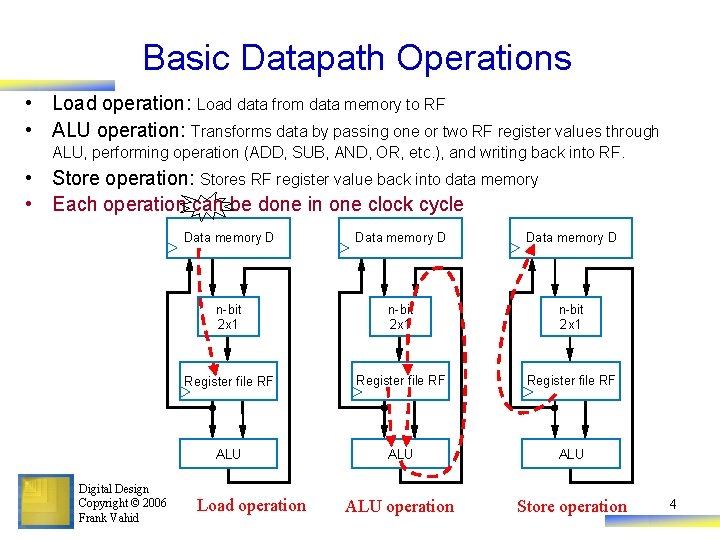

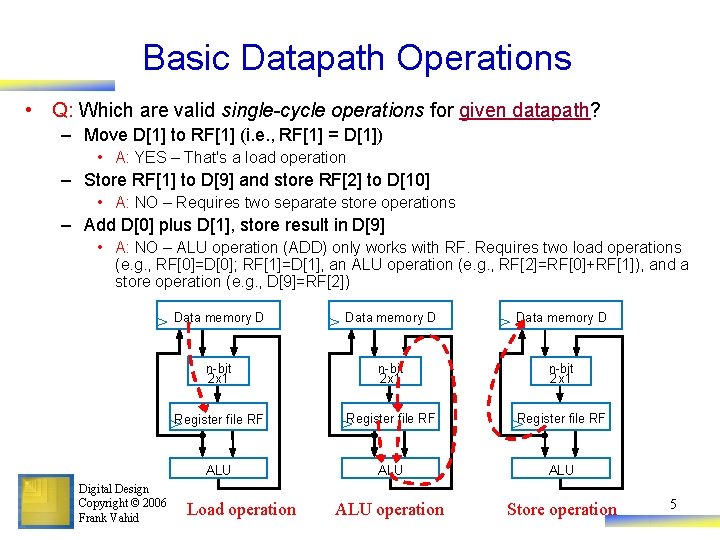

Basic Datapath Operations • Load operation: Load data from data memory to RF • ALU operation: Transforms data by passing one or two RF register values through ALU, performing operation (ADD, SUB, AND, OR, etc. ), and writing back into RF. • Store operation: Stores RF register value back into data memory • Each operation can be done in one clock cycle Digital Design Copyright © 2006 Frank Vahid Data memory D n-bit 2 x 1 Register file RF ALU ALU operation Store operation Load operation 4

Basic Datapath Operations • Q: Which are valid single-cycle operations for given datapath? – Move D[1] to RF[1] (i. e. , RF[1] = D[1]) • A: YES – That's a load operation – Store RF[1] to D[9] and store RF[2] to D[10] • A: NO – Requires two separate store operations – Add D[0] plus D[1], store result in D[9] • A: NO – ALU operation (ADD) only works with RF. Requires two load operations (e. g. , RF[0]=D[0]; RF[1]=D[1], an ALU operation (e. g. , RF[2]=RF[0]+RF[1]), and a store operation (e. g. , D[9]=RF[2]) Digital Design Copyright © 2006 Frank Vahid Data memory D n-bit 2 x 1 Register file RF ALU ALU operation Store operation Load operation 5

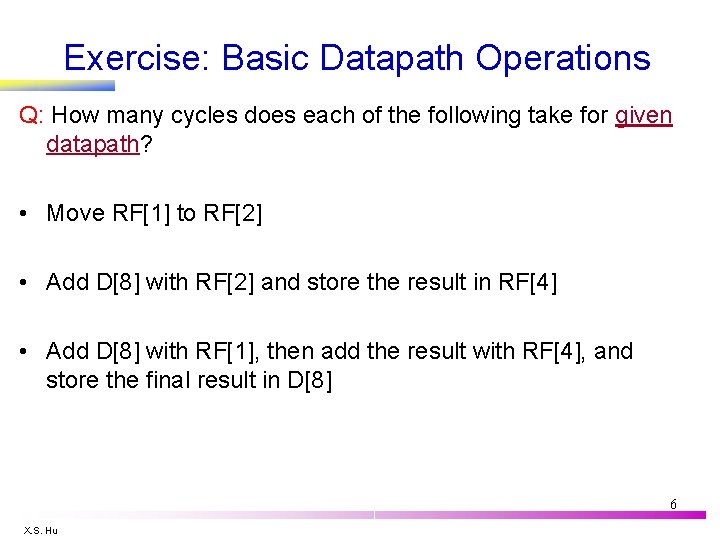

Exercise: Basic Datapath Operations Q: How many cycles does each of the following take for given datapath? • Move RF[1] to RF[2] 1 • Add D[8] with RF[2] and store the result in RF[4] 2 • Add D[8] with RF[1], then add the result with RF[4], and store the final result in D[8] 4 Digital Design Copyright © 2006 Frank Vahid X. S. Hu 6

![Basic Architecture – Control Unit • D[9] = D[0] + D[1] – requires a Basic Architecture – Control Unit • D[9] = D[0] + D[1] – requires a](http://slidetodoc.com/presentation_image/d0fc597dc0d8ef70555976c0bb16385d/image-7.jpg)

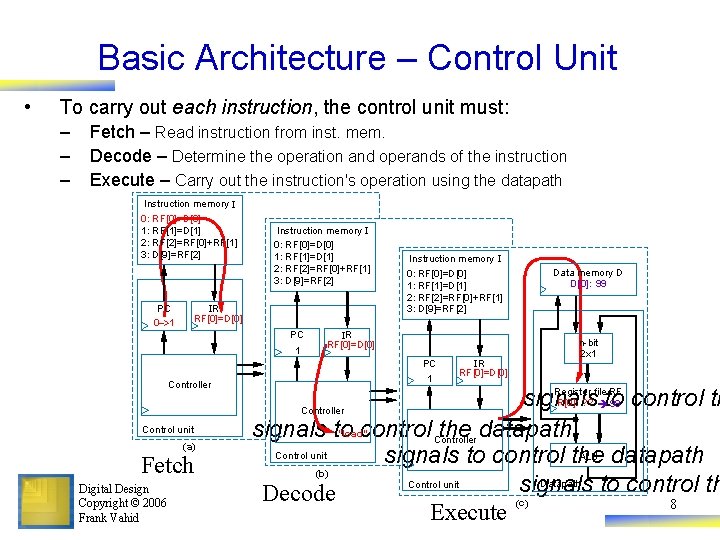

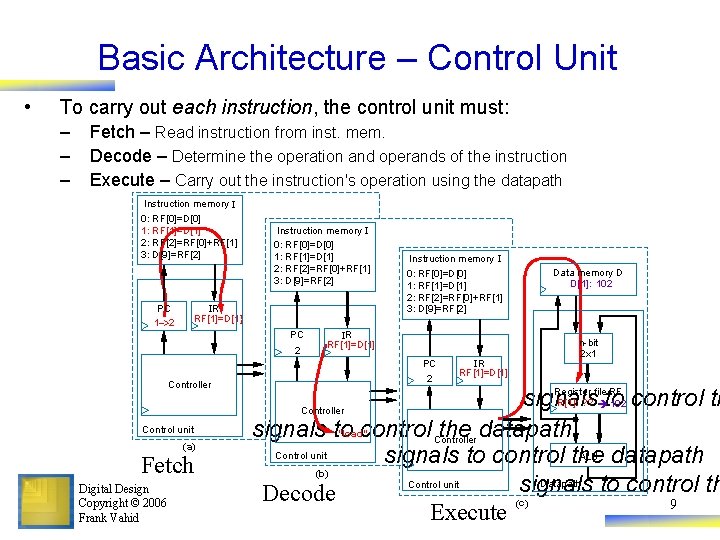

Basic Architecture – Control Unit • D[9] = D[0] + D[1] – requires a sequence of four datapath operations: 0: RF[0] = D[0] 1: RF[1] = D[1] 2: RF[2] = RF[0] + RF[1] 3: D[9] = RF[2] • Instruction memory I 0: RF[0]=D[0] 1: RF[1]=D[1] 2: RF[2]=RF[0]+RF[1] 3: D[9]=RF[2] Each operation is an instruction – – Sequence of instructions – program Looks cumbersome, but that's the world of programmable processors – Decomposing desired computations into processor-supported operations Store program in Instruction memory Control unit reads each instruction and executes it on the datapath • • PC: Program counter – address of current instruction IR: Instruction register – current instruction Digital Design Copyright © 2006 Frank Vahid Data memory D n-bit 2 x 1 PC IR Register file RF Controller ALU Control unit Datapathto control th signals 7

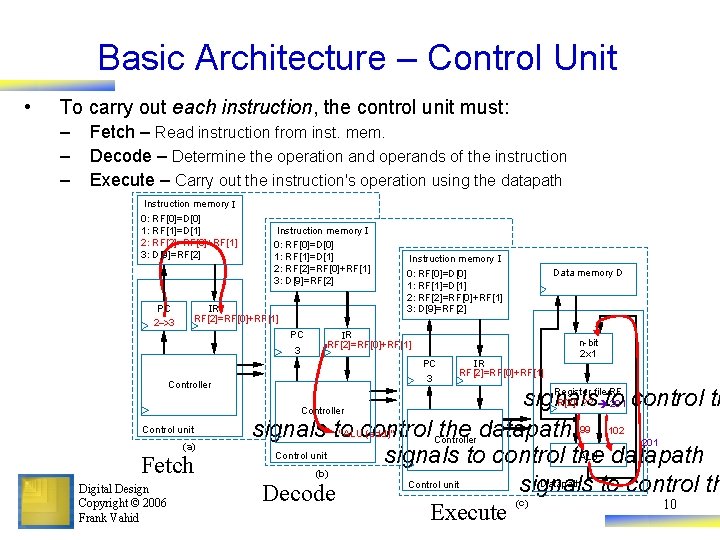

Basic Architecture – Control Unit • To carry out each instruction, the control unit must: – – – Fetch – Read instruction from inst. mem. Decode – Determine the operation and operands of the instruction Execute – Carry out the instruction's operation using the datapath Instruction memory I 0: RF[0]=D[0] 1: RF[1]=D[1] 2: RF[2]=RF[0]+RF[1] 3: D[9]=RF[2] PC 0 ->1 Instruction memory I 0: RF[0]=D[0] 1: RF[1]=D[1] 2: RF[2]=RF[0]+RF[1] 3: D[9]=RF[2] IR RF[0]=D[0] PC Controller Control unit (a) Fetch Digital Design Copyright © 2006 Frank Vahid 1 IR RF[0]=D[0] Data memory D D[0]: 99 n-bit 2 x 1 Register file RF signals R[0]: ? ? to 99 control th Controller "load" signals to control Controller the datapath Control unit ALU datapath signals to control the (b) Datapath Control unit signals to control th Decode (c) 8 Execute

Basic Architecture – Control Unit • To carry out each instruction, the control unit must: – – – Fetch – Read instruction from inst. mem. Decode – Determine the operation and operands of the instruction Execute – Carry out the instruction's operation using the datapath Instruction memory I 0: RF[0]=D[0] 1: RF[1]=D[1] 2: RF[2]=RF[0]+RF[1] 3: D[9]=RF[2] PC 1 ->2 Instruction memory I 0: RF[0]=D[0] 1: RF[1]=D[1] 2: RF[2]=RF[0]+RF[1] 3: D[9]=RF[2] IR RF[1]=D[1} PC 2 Instruction memory I 0: RF[0]=D[0] 1: RF[1]=D[1] 2: RF[2]=RF[0]+RF[1] 3: D[9]=RF[2] IR RF[1]=D[1] PC Controller Control unit (a) Fetch Digital Design Copyright © 2006 Frank Vahid 2 IR RF[1]=D[1] Data memory D D[1]: 102 n-bit 2 x 1 Register file RF signals R[1]: ? ? to 102 control th Controller "load" signals to control Controller the datapath Control unit ALU datapath signals to control the (b) Datapath Control unit signals to control th Decode (c) 9 Execute

Basic Architecture – Control Unit • To carry out each instruction, the control unit must: – – – Fetch – Read instruction from inst. mem. Decode – Determine the operation and operands of the instruction Execute – Carry out the instruction's operation using the datapath Instruction memory I 0: RF[0]=D[0] 1: RF[1]=D[1] 2: RF[2]=RF[0]+RF[1] 3: D[9]=RF[2] PC 2 ->3 Instruction memory I 0: RF[0]=D[0] 1: RF[1]=D[1] 2: RF[2]=RF[0]+RF[1] 3: D[9]=RF[2] IR RF[2]=RF[0]+RF[1] PC Controller Control unit (a) Fetch Digital Design Copyright © 2006 Frank Vahid 3 IR RF[2]=RF[0]+RF[1] Data memory D n-bit 2 x 1 Register file RF signals R[2]: ? ? to 201 control th Controller "ALUcontrol (add)" signals to the datapath 99 102 201 Controller Control unit ALU datapath signals to control the (b) Datapath Control unit signals to control th Decode (c) 10 Execute

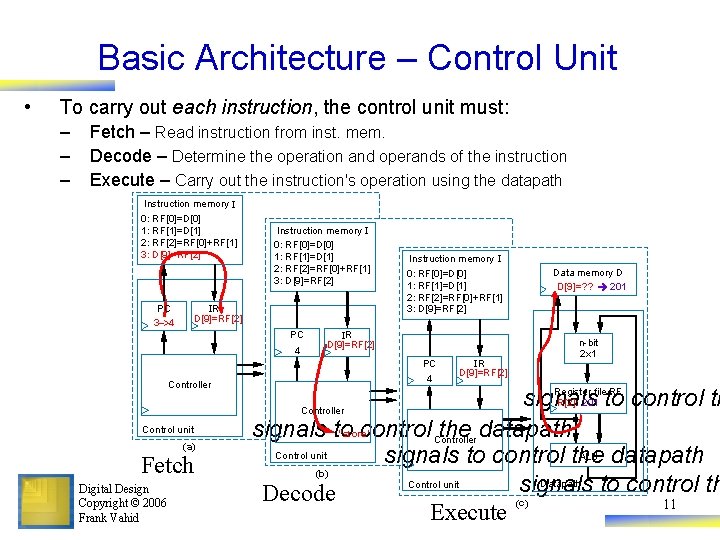

Basic Architecture – Control Unit • To carry out each instruction, the control unit must: – – – Fetch – Read instruction from inst. mem. Decode – Determine the operation and operands of the instruction Execute – Carry out the instruction's operation using the datapath Instruction memory I 0: RF[0]=D[0] 1: RF[1]=D[1] 2: RF[2]=RF[0]+RF[1] 3: D[9]=RF[2] PC 3 ->4 Instruction memory I 0: RF[0]=D[0] 1: RF[1]=D[1] 2: RF[2]=RF[0]+RF[1] 3: D[9]=RF[2] IR D[9]=RF[2] PC Controller Control unit (a) Fetch Digital Design Copyright © 2006 Frank Vahid 4 IR D[9]=RF[2] Data memory D D[9]=? ? 201 n-bit 2 x 1 Register file RF signals R[2]: 201 to control th Controller "store" signals to control Controller the datapath Control unit ALU datapath signals to control the (b) Datapath Control unit signals to control th Decode (c) 11 Execute

![Basic Architecture – Control Unit Instruction memory I 0: RF[0]=D[0] 1: RF[1]=D[1] 2: RF[2]=RF[0]+RF[1] Basic Architecture – Control Unit Instruction memory I 0: RF[0]=D[0] 1: RF[1]=D[1] 2: RF[2]=RF[0]+RF[1]](http://slidetodoc.com/presentation_image/d0fc597dc0d8ef70555976c0bb16385d/image-12.jpg)

Basic Architecture – Control Unit Instruction memory I 0: RF[0]=D[0] 1: RF[1]=D[1] 2: RF[2]=RF[0]+RF[1] 3: D[9]=RF[2] Data memory D n-bit 2 x 1 signals to control the Register datapath file RF signals to control the datapath Controller signals to control th ALU PC Digital Design Copyright © 2006 Frank Vahid Control unit IR Datapath 12

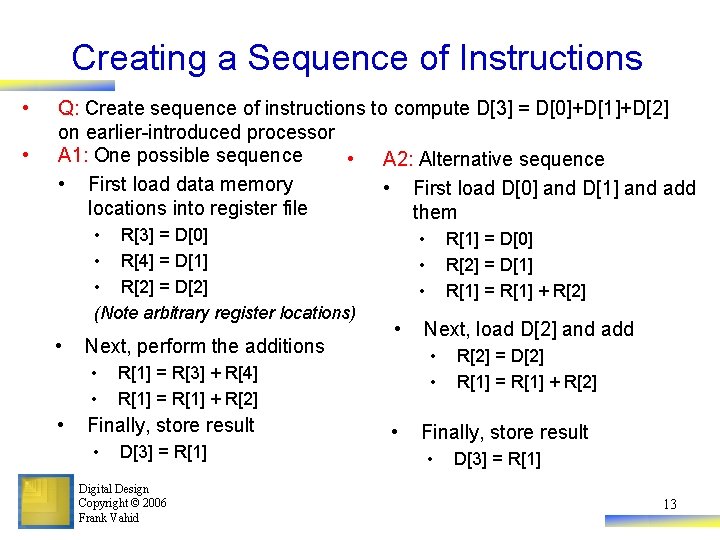

Creating a Sequence of Instructions • • Q: Create sequence of instructions to compute D[3] = D[0]+D[1]+D[2] on earlier-introduced processor A 1: One possible sequence • A 2: Alternative sequence • First load data memory • First load D[0] and D[1] and add locations into register file them • R[3] = D[0] • R[4] = D[1] • R[2] = D[2] (Note arbitrary register locations) • Next, perform the additions • • D[3] = R[1] Digital Design Copyright © 2006 Frank Vahid R[1] = D[0] R[2] = D[1] R[1] = R[1] + R[2] Next, load D[2] and add • • R[1] = R[3] + R[4] R[1] = R[1] + R[2] Finally, store result • • • R[2] = D[2] R[1] = R[1] + R[2] Finally, store result • D[3] = R[1] 13

![Exercise: Creating Instruction Sequences Q 1: D[8] = D[8] + RF[1] + RF[4] RF[2] Exercise: Creating Instruction Sequences Q 1: D[8] = D[8] + RF[1] + RF[4] RF[2]](http://slidetodoc.com/presentation_image/d0fc597dc0d8ef70555976c0bb16385d/image-14.jpg)

Exercise: Creating Instruction Sequences Q 1: D[8] = D[8] + RF[1] + RF[4] RF[2] = RF[1] + RF[4] RF[3] = D[8] RF[2] = RF[2] + RF[3] D[8] = RF[2] Q 2: RF[2] = RF[1] + 0 Digital Design Copyright © 2006 Frank Vahid X. S. Hu 14

Number of Cycles • Q: How many cycles are needed to execute six instructions using the earlier-described processor? • A: Each instruction requires 3 cycles – 1 to fetch, 1 to decode, and 1 to execute • Thus, 6 instr * 3 cycles/instr = 18 cycles Digital Design Copyright © 2006 Frank Vahid 15

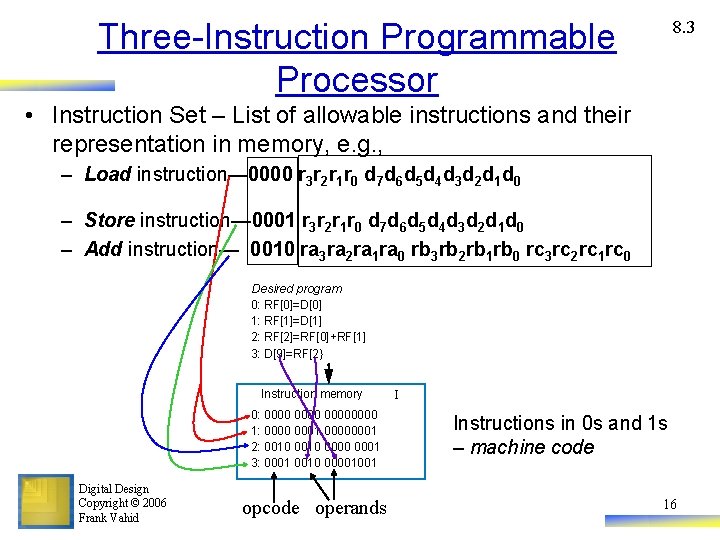

Three-Instruction Programmable Processor 8. 3 • Instruction Set – List of allowable instructions and their representation in memory, e. g. , – Load instruction— 0000 r 3 r 2 r 1 r 0 d 7 d 6 d 5 d 4 d 3 d 2 d 1 d 0 – Store instruction— 0001 r 3 r 2 r 1 r 0 d 7 d 6 d 5 d 4 d 3 d 2 d 1 d 0 – Add instruction— 0010 ra 3 ra 2 ra 1 ra 0 rb 3 rb 2 rb 1 rb 0 rc 3 rc 2 rc 1 rc 0 Desired program 0: RF[0]=D[0] 1: RF[1]=D[1] 2: RF[2]=RF[0]+RF[1] 3: D[9]=RF[2} Instruction memory 0: 0000 1: 0000 0001 00000001 2: 0010 0000 0001 3: 0001 0010 00001001 Digital Design Copyright © 2006 Frank Vahid opcode operands I Instructions in 0 s and 1 s – machine code 16

![Program for Three-Instruction Processor Desired program 0: RF[0]=D[0] 1: RF[1]=D[1] 2: RF[2]=RF[0]+RF[1] 3: D[9]=RF[2} Program for Three-Instruction Processor Desired program 0: RF[0]=D[0] 1: RF[1]=D[1] 2: RF[2]=RF[0]+RF[1] 3: D[9]=RF[2}](http://slidetodoc.com/presentation_image/d0fc597dc0d8ef70555976c0bb16385d/image-17.jpg)

Program for Three-Instruction Processor Desired program 0: RF[0]=D[0] 1: RF[1]=D[1] 2: RF[2]=RF[0]+RF[1] 3: D[9]=RF[2} Instruction memory. I 0: 0000 1: 0000 0001 00000001 2: 0010 0000 0001 3: 0001 0010 00001001 Computes D[9]=D[0]+D[1] Data memory D n-bit 2× 1 PC IR Register file RF Controller ALU Control unit Digital Design Copyright © 2006 Frank Vahid Datapath signals to control the 17

![Program for Three-Instruction Processor • Another example program in machine code – Compute D[5] Program for Three-Instruction Processor • Another example program in machine code – Compute D[5]](http://slidetodoc.com/presentation_image/d0fc597dc0d8ef70555976c0bb16385d/image-18.jpg)

Program for Three-Instruction Processor • Another example program in machine code – Compute D[5] = D[5] + D[6] + D[7] Digital Design Copyright © 2006 Frank Vahid –Load instruction— 0000 r 3 r 2 r 1 r 0 d 7 d 6 d 5 d 4 d 3 d 2 d 1 d 0 –Store instruction— 0001 r 3 r 2 r 1 r 0 d 7 d 6 d 5 d 4 d 3 d 2 d 1 d 0 –Add instruction— 0010 ra 3 ra 2 ra 1 ra 0 rb 3 rb 2 rb 1 rb 0 rc 3 rc 2 rc 1 rc 0 signals to control the 18

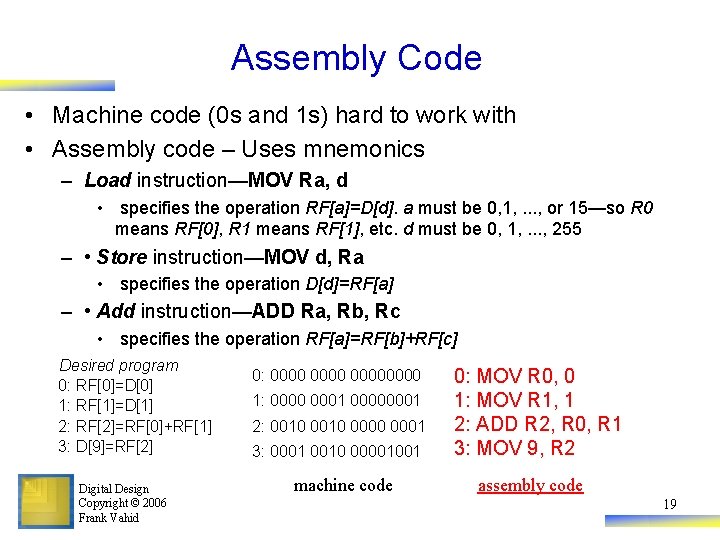

Assembly Code • Machine code (0 s and 1 s) hard to work with • Assembly code – Uses mnemonics – Load instruction—MOV Ra, d • specifies the operation RF[a]=D[d]. a must be 0, 1, . . . , or 15—so R 0 means RF[0], R 1 means RF[1], etc. d must be 0, 1, . . . , 255 – • Store instruction—MOV d, Ra • specifies the operation D[d]=RF[a] – • Add instruction—ADD Ra, Rb, Rc • specifies the operation RF[a]=RF[b]+RF[c] Desired program 0: RF[0]=D[0] 1: RF[1]=D[1] 2: RF[2]=RF[0]+RF[1] 3: D[9]=RF[2] Digital Design Copyright © 2006 Frank Vahid 0: 0000 1: 0000 0001 00000001 2: 0010 0000 0001 3: 0001 0010 00001001 machine code 0: MOV R 0, 0 1: MOV R 1, 1 2: ADD R 2, R 0, R 1 3: MOV 9, R 2 assembly code 19

![Exercise: Creating Assembly Code Q 1: D[8] = D[8] + RF[1] + RF[4] RF[2] Exercise: Creating Assembly Code Q 1: D[8] = D[8] + RF[1] + RF[4] RF[2]](http://slidetodoc.com/presentation_image/d0fc597dc0d8ef70555976c0bb16385d/image-20.jpg)

Exercise: Creating Assembly Code Q 1: D[8] = D[8] + RF[1] + RF[4] RF[2] = RF[1] + RF[4] RF[3] = D[8] RF[2] = RF[2] + RF[3] D[8] = RF[2] Add R 2, R 1, R 4 MOV R 3, 8 Add R 2, R 3 MOV 8, R 2 Q 2: RF[2] = RF[1] + 0 MOV R 1, 0? ? Digital Design Copyright © 2006 Frank Vahid X. S. Hu 20

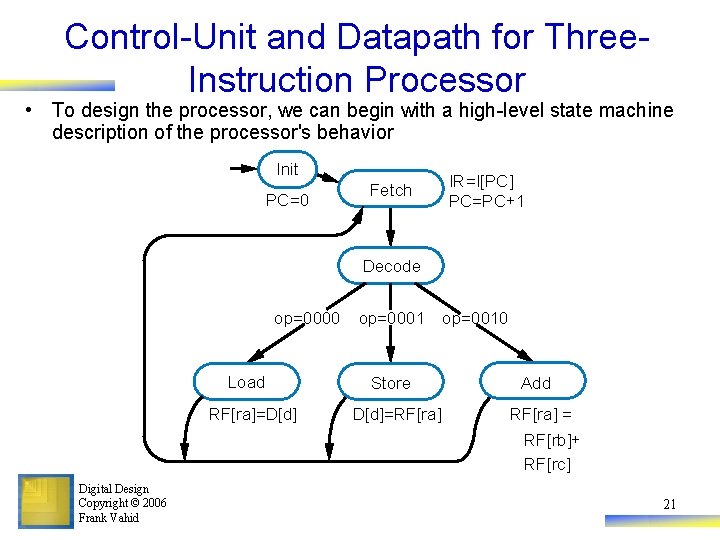

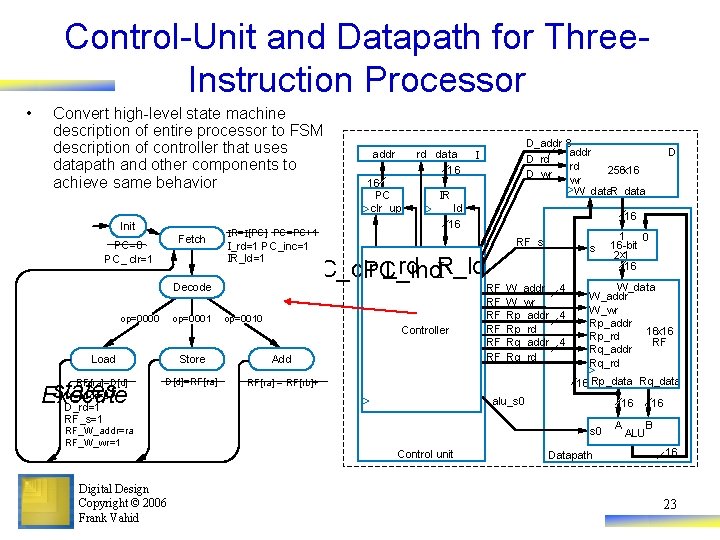

Control-Unit and Datapath for Three. Instruction Processor • To design the processor, we can begin with a high-level state machine description of the processor's behavior Init PC=0 Fetch IR=I[PC] PC=PC+1 Decode op=0000 Load RF[ra]=D[d] Digital Design Copyright © 2006 Frank Vahid op=0001 Store D[d]=RF[ra] op=0010 Add RF[ra] = RF[rb]+ RF[rc] 21

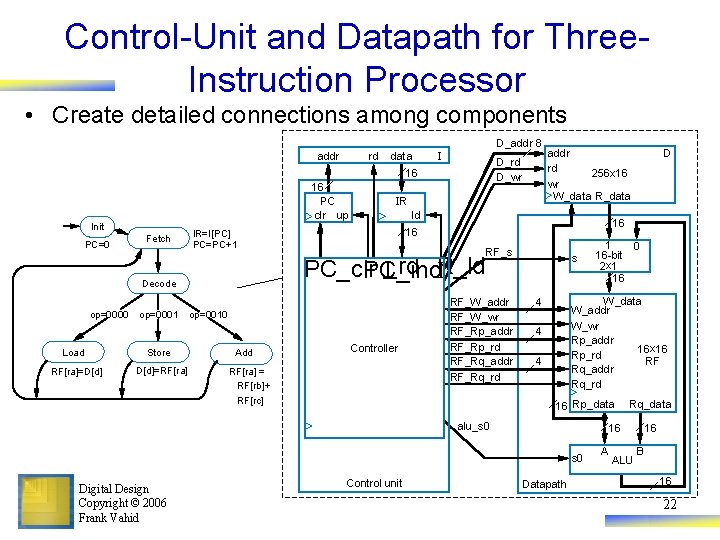

Control-Unit and Datapath for Three. Instruction Processor • Create detailed connections among components D_addr 8 addr rd data I D_rd D_wr 16 16 PC clr up Init PC=0 Fetch Load RF[ra]=D[d] op=0001 Store D[d]=RF[ra] Id _ PC_clr I rd R_ld PC_inc. I op=0010 Add Controller RF[ra] = RF[rb]+ RF[rc] RF_s RF_W_addr RF_W_wr RF_Rp_addr RF_Rp_rd RF_Rq_addr RF_Rq_rd s 1 0 16 -bit 2 x 1 16 W_data W_addr W_wr Rp_addr 16 x 16 Rp_rd RF Rq_addr Rq_rd 4 4 4 16 Rp_data alu_s 0 Control unit Rq_data 16 s 0 Digital Design Copyright © 2006 Frank Vahid D 16 16 IR=I[PC] PC=PC+1 Decode op=0000 IR addr rd 256 x 16 wr W_data R_data Datapath A ALU 16 B 16 22

Control-Unit and Datapath for Three. Instruction Processor • Convert high-level state machine description of entire processor to FSM description of controller that uses datapath and other components to achieve same behavior Init IR=I[PC] PC=PC+1 Fetch PC=0 PC_ clr=1 Load states D_addr=d Execute D_rd=1 RF[ra]=D[d] RF_s=1 RF_W_addr=ra RF_W_wr=1 op=0001 op=0010 D[d]=RF[ra] D_addr=d RF_Rp_addr=ra RF_Rp_rd=1 Digital Design Copyright © 2006 Frank Vahid 16 PC clr up D_addr 8 addr D_rd rd 256 x 16 D_wr wr W_data. R_data I IR Id 16 Controller Add 1 0 16 -bit 2 x 1 16 W_data W_addr W_wr Rp_addr 16 x 16 Rp_rd RF Rq_addr Rq_rd 16 Rp_data Rq_data RF[rc] RF_Rp_addr=rb RF_Rp_rd=1 RF_W_addr=ra RF_W_wr=1 alu_s 0=1 s RF_W_addr 4 RF_W_wr RF_Rp_addr 4 RF_Rp_rd RF_Rq_addr 4 RF_Rq_rd RF[ra] = RF[rb]+ RF_s=0 RF_Rq_addr=rc RF_Rq _rd=1 D 16 RF_s _ PC_clr I rd R_ld PC_inc. I Store D_wr=1 RF_s=X rd data 16 I_rd=1 PC_inc=1 IR_ld=1 Decode op=0000 addr alu_s 0 16 s 0 Control unit Datapath A 16 B ALU 16 23

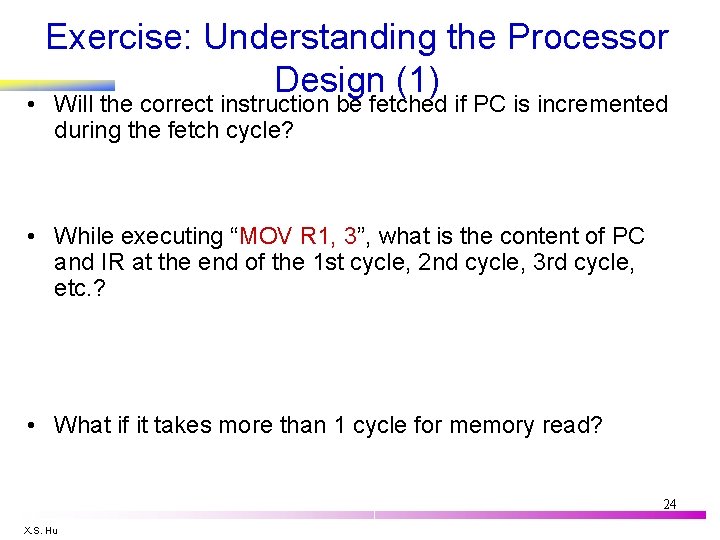

Exercise: Understanding the Processor Design (1) • Will the correct instruction be fetched if PC is incremented during the fetch cycle? – No, since PC will not be updated until the beginning of the next cycle • While executing “MOV R 1, 3”, what is the content of PC and IR at the end of the 1 st cycle, 2 nd cycle, 3 rd cycle, etc. ? – 1 st cycle: PC = 0, IR = xxxx – 2 nd cycle: PC = 1, IR = I[0] – 3 rd cycle: PC = 1, IR = I[0] • What if it takes more than 1 cycle for memory read? – Cannot decode until IR is loaded Digital Design Copyright © 2006 Frank Vahid X. S. Hu 24

![Exercise: Understanding the Processor Design (2) Q 1: D[8] = D[8] + RF[1] + Exercise: Understanding the Processor Design (2) Q 1: D[8] = D[8] + RF[1] +](http://slidetodoc.com/presentation_image/d0fc597dc0d8ef70555976c0bb16385d/image-25.jpg)

Exercise: Understanding the Processor Design (2) Q 1: D[8] = D[8] + RF[1] + RF[4] … I[15]: Add R 2, R 1, R 4 I[16]: MOV R 3, 8 I[17]: Add R 2, R 3 … RF[1] = 4 RF[4] = 5 D[8] = 7 CLK (n+1) Fetch PC=15 IR=xxxx (n+2) (n+3) Decode Execute PC=16 IR=2214 h RF[2]= xxxxh Digital Design Copyright © 2006 Frank Vahid X. S. Hu (n+4) (n+5) Fetch Decode PC=16 PC=17 IR=2214 h IR=0308 h RF[2]= 0009 h (n+6) Execute PC=17 IR=0308 h RF[3]= xxxxh (n+7) Fetch PC=17 IR=0308 h RF[3]= 0007 h 25

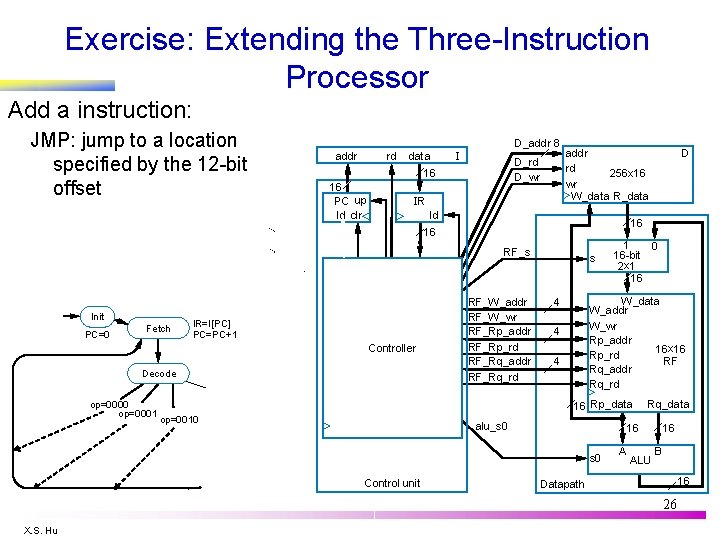

Exercise: Extending the Three-Instruction Processor Add a instruction: Init PC=0 Fetch D_addr 8 addr rd data 16 16 PC up ld clr D_rd D_wr IR RF_s s 12 Decode RF_W_addr RF_W_wr RF_Rp_addr RF_Rp_rd RF_Rq_addr RF_Rq_rd op=1000 W_data W_addr W_wr Rp_addr 16 x 16 Rp_rd RF Rq_addr Rq_rd 4 4 4 alu_s 0 X. S. Hu s 0 Control unit Rq_data 16 PC_ld =1 Digital Design Copyright © 2006 Frank Vahid 1 0 16 -bit 2 x 1 16 16 Rp_data Jump D 16 16 IR=I[PC] PC=PC+1 op=0010 addr rd 256 x 16 wr W_data R_data Id Controller op=0000 op=0001 I 16 a+b-1 JMP: jump to a location specified by the 12 -bit offset RTL: PC = PC+I[15: 4] 16 AS: JMP 3 MC: 1000000011 A ALU 16 B 16 Datapath 26

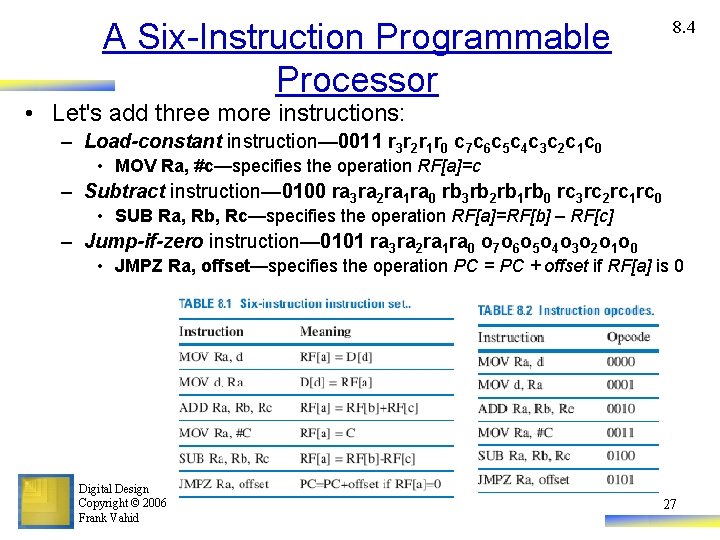

A Six-Instruction Programmable Processor 8. 4 • Let's add three more instructions: – Load-constant instruction— 0011 r 3 r 2 r 1 r 0 c 7 c 6 c 5 c 4 c 3 c 2 c 1 c 0 • MOV Ra, #c—specifies the operation RF[a]=c – Subtract instruction— 0100 ra 3 ra 2 ra 1 ra 0 rb 3 rb 2 rb 1 rb 0 rc 3 rc 2 rc 1 rc 0 • SUB Ra, Rb, Rc—specifies the operation RF[a]=RF[b] – RF[c] – Jump-if-zero instruction— 0101 ra 3 ra 2 ra 1 ra 0 o 7 o 6 o 5 o 4 o 3 o 2 o 1 o 0 • JMPZ Ra, offset—specifies the operation PC = PC + offset if RF[a] is 0 Digital Design Copyright © 2006 Frank Vahid 27

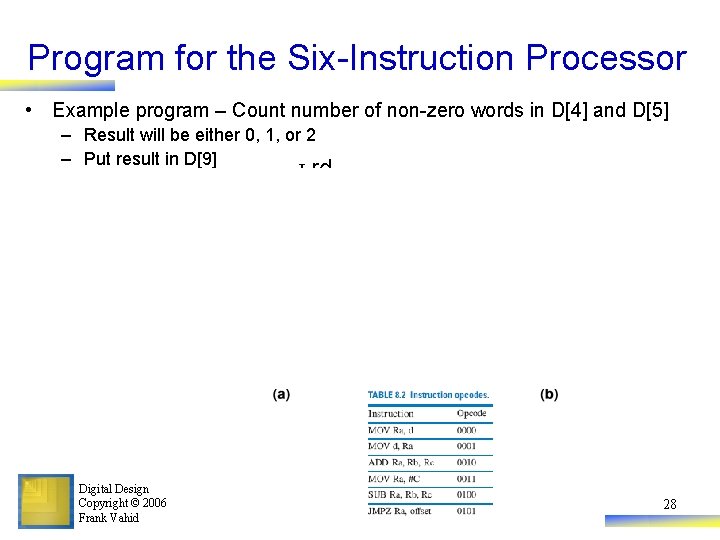

Program for the Six-Instruction Processor • Example program – Count number of non-zero words in D[4] and D[5] – Result will be either 0, 1, or 2 – Put result in D[9] I_rd PC_ld PC_clr PC_inc. IR_ld Digital Design Copyright © 2006 Frank Vahid 28

![Exercise: More on Programming Q 1: Compare the contents of D[4] and D[5]. If Exercise: More on Programming Q 1: Compare the contents of D[4] and D[5]. If](http://slidetodoc.com/presentation_image/d0fc597dc0d8ef70555976c0bb16385d/image-29.jpg)

Exercise: More on Programming Q 1: Compare the contents of D[4] and D[5]. If equal, D[3] =1, otherwise set D[3]=0. MOV MOV SUB JMPZ SUB B 1: MOV R 0, #1 R 1, 4 R 2, 5 R 3, R 1, R 2 R 3, B 1 R 0, R 0 3, R 0 Digital Design Copyright © 2006 Frank Vahid X. S. Hu // RF[0] = 1 // RF[1] = D[4] // RF[2] = D[5] // RF[3] = RF[1]-RF[2] // if RF[3] = 0, jump to B 1 // RF[0] = 0 // D[3] = RF[0] 29

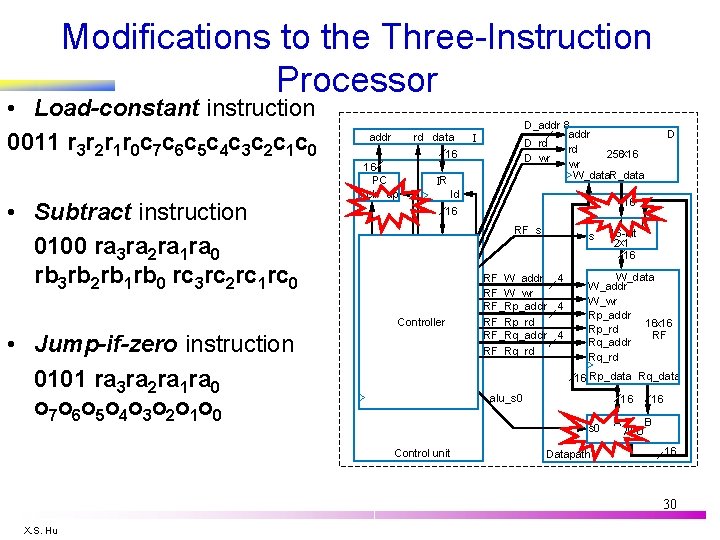

Modifications to the Three-Instruction Processor • Load-constant instruction 0011 r 3 r 2 r 1 r 0 c 7 c 6 c 5 c 4 c 3 c 2 c 1 c 0 • Subtract instruction 0100 ra 3 ra 2 ra 1 ra 0 rb 3 rb 2 rb 1 rb 0 rc 3 rc 2 rc 1 rc 0 addr rd data 16 16 PC clr up IR Id RF_s • Jump-if-zero instruction 0101 ra 3 ra 2 ra 1 ra 0 o 7 o 6 o 5 o 4 o 3 o 2 o 1 o 0 s RF_W_addr RF_W_wr RF_Rp_addr RF_Rp_rd RF_Rq_addr RF_Rq_rd 4 4 4 1 0 16 -bit 2 x 1 16 W_data W_addr W_wr Rp_addr 16 x 16 Rp_rd RF Rq_addr Rq_rd 16 Rp_data Rq_data alu_s 0 16 s 0 Control unit X. S. Hu D 16 16 Controller Digital Design Copyright © 2006 Frank Vahid D_addr 8 addr D_rd rd 256 x 16 D_wr wr W_data. R_data I Datapath A 16 B ALU 16 30

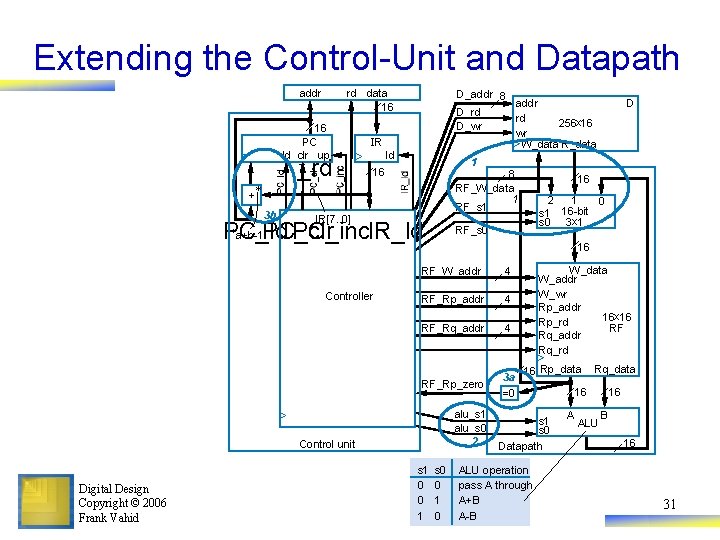

Extending the Control-Unit and Datapath addr 1: The load constant instruction requires that the register file be able to load data from IR[7. . 0], in addition to data from data memory or the ALU 16 output. Thus, we widen the register file’s PC multiplexer from 2 x 1 to 3 x 1, add another mux ld clr up control signal, and also create a new signal coming from the controller labeled RF_W_data, which will * + connect with IR[7. . 0]. rd data 16 I_rd 2: The subtract instruction requires that we use 3 ban *a+b-1 ALU capable of subtraction, so we add another ALU control signal. D_addr 8 addr D_rd rd 256 x 16 D_wr wr W_data R_data IR Id 1 16 8 RF_W_data 1 RF_s 1 IR[7. . 0] PC_ld PC_clr PC_inc. IR_ld 3: The jump-if-zero instruction requires that we be able to detect if a register is zero, and that we be able to add IR[7. . 0] to the PC. 3 a: We insert a datapath component to detect if the register file’s Rp read port is all zeros (that component would just be a NOR gate). 3 b: We also upgrade the PC register so it can be loaded with PC plus IR[7. . 0]. The adder used for this also subtracts 1 from the sum, to compensate for the fact that the Fetch state already added 1 to the PC. Controller 2 1 0 s 1 16 -bit s 0 3 x 1 16 RF_W_addr 4 RF_Rp_addr 4 RF_Rq_addr 4 RF_Rp_zero 3 a =0 alu_s 1 alu_s 0 2 s 1 0 0 1 16 RF_s 0 Control unit Digital Design Copyright © 2006 Frank Vahid D s 0 0 1 0 W_data W_addr W_wr Rp_addr 16 x 16 Rp_rd RF Rq_addr Rq_rd 16 Rp_data s 1 s 0 Datapath ALU operation pass A through A+B A-B Rq_data 16 A ALU 16 B 16 31

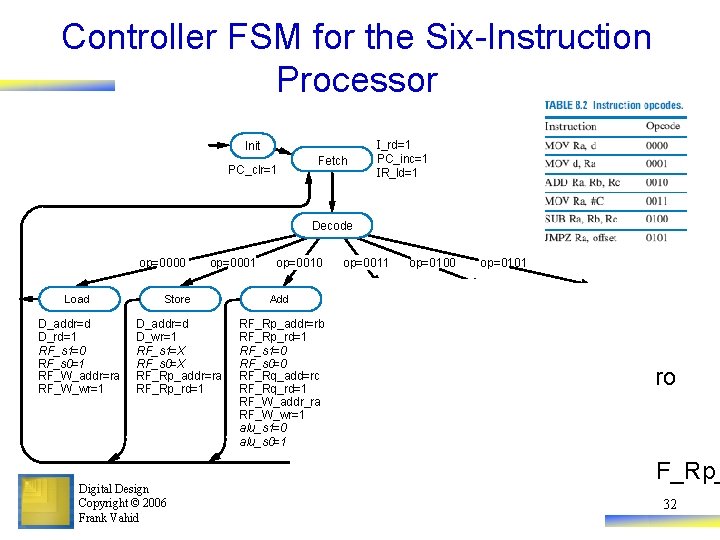

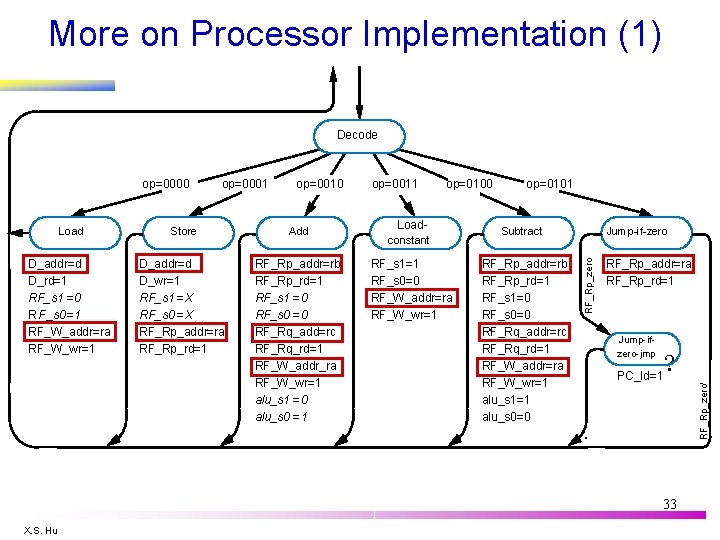

Controller FSM for the Six-Instruction Processor Init PC_clr=1 Fetch I_rd=1 PC_inc=1 IR_ld=1 Decode op=0010 Load Store Add D_addr=d D_rd=1 RF_s 1=0 RF_s 0=1 RF_W_addr=ra RF_W_wr=1 D_addr=d D_wr=1 RF_s 1=X RF_s 0=X RF_Rp_addr=ra RF_Rp_rd=1 RF_Rp_addr=rb RF_Rp_rd=1 RF_s 1=0 RF_s 0=0 RF_Rq_add=rc RF_Rq_rd=1 RF_W_addr_ra RF_W_wr=1 alu_s 1=0 alu_s 0=1 Digital Design Copyright © 2006 Frank Vahid op=0011 op=0100 Load- constant RF_s 1=1 RF_s 0=0 RF_W_addr=ra RF_W_wr=1 op=0101 Subtract RF_Rp_addr=rb RF_Rp_rd=1 RF_s 1=0 RF_s 0=0 RF_Rq_addr=rc RF_Rq_rd=1 RF_W_addr=ra RF_W_wr=1 alu_s 1=1 alu_s 0=0 Jump-if-zero RF_Rp_addr=ra RF_Rp_rd=1 RF_Rp_zero Jump-ifzero-jmp ? PC_ld=1 RF_Rp_zero' op=0001 RF_Rp_zero op=0000 RF_Rp_ 32

More on Processor Implementation (1) Decode op=0010 Load Store Add D_addr=d D_rd=1 RF_s 1 =0 RF_s 0=1 RF_W_addr=ra RF_W_wr=1 D_addr=d D_wr=1 RF_s 1 =X RF_s 0 =X RF_Rp_addr=ra RF_Rp_rd=1 RF_Rp_addr=rb RF_Rp_rd=1 RF_s 1 =0 RF_s 0 =0 RF_Rq_add=rc RF_Rq_rd=1 RF_W_addr_ra RF_W_wr=1 alu_s 1 =0 alu_s 0 =1 Digital Design Copyright © 2006 Frank Vahid X. S. Hu op=0011 op=0100 Loadconstant RF_s 1=1 RF_s 0=0 RF_W_addr=ra RF_W_wr=1 op=0101 Subtract RF_Rp_addr=rb RF_Rp_rd=1 RF_s 1=0 RF_s 0=0 RF_Rq_addr=rc RF_Rq_rd=1 RF_W_addr=ra RF_W_wr=1 alu_s 1=1 alu_s 0=0 Jump-if-zero RF_Rp_addr=ra RF_Rp_rd=1 Jump-ifzero-jmp PC_ld=1 ? 33 RF_Rp_zero' op=0001 RF_Rp_zero op=0000

![More on Processor Implementation (2) addr rd data 16 D_addr IR[7: 0] 16 ld More on Processor Implementation (2) addr rd data 16 D_addr IR[7: 0] 16 ld](http://slidetodoc.com/presentation_image/d0fc597dc0d8ef70555976c0bb16385d/image-34.jpg)

More on Processor Implementation (2) addr rd data 16 D_addr IR[7: 0] 16 ld PC clr up IR 256 x 16 R_data 8 RF_W_data IR[7. . 0] 16 1 RF_s 1 2 s 1 s 0 RF_s 0 1 16 -bit 3 x 1 0 16 IR[11: 8] RF_Rp_s IR[11: 8] IR[7: 4] IR[3: 0] RF_W_addr 4 RF_Rp_addr 4 RF_Rq_addr 4 W_addr W_wr Rp_addr Rp_rd Rq_addr Rq_rd 16 RF_Rp_zero Controller Control unit Digital Design Copyright © 2006 Frank Vahid W_data Rq_data 16 s 1 s 0 Datapath 16 x 16 RF Rp_data =0 alu_s 1 alu_s 0 X. S. Hu D Id * * a+b-1 addr rd wr W_data D_rd D_wr 16 + 8 A ALU ? 16 B 16 34

What is the Problem? ? Digital Design Copyright © 2006 Frank Vahid X. S. Hu 35

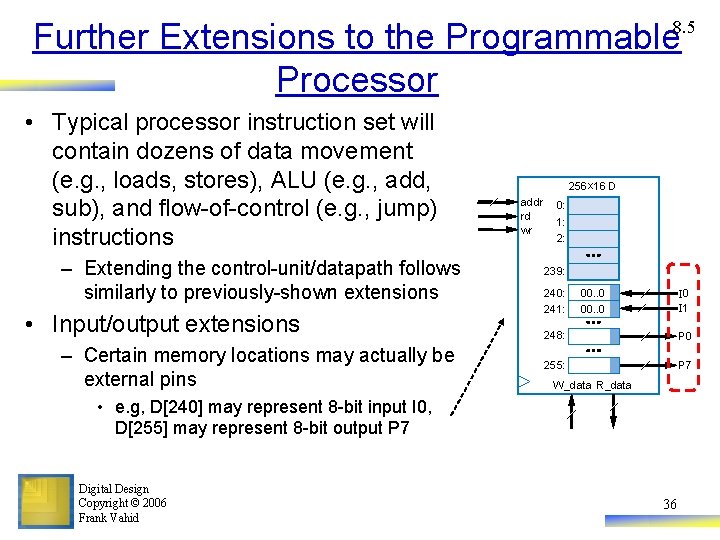

Further Extensions to the Programmable Processor 8. 5 • Typical processor instruction set will contain dozens of data movement (e. g. , loads, stores), ALU (e. g. , add, sub), and flow-of-control (e. g. , jump) instructions – Extending the control-unit/datapath follows similarly to previously-shown extensions • Input/output extensions – Certain memory locations may actually be external pins 256 x 16 D addr rd wr 0: 1: 2: 239: 240: 241: 00. . 0 I 0 I 1 248: P 0 255: P 7 W_data R_data • e. g, D[240] may represent 8 -bit input I 0, D[255] may represent 8 -bit output P 7 Digital Design Copyright © 2006 Frank Vahid 36

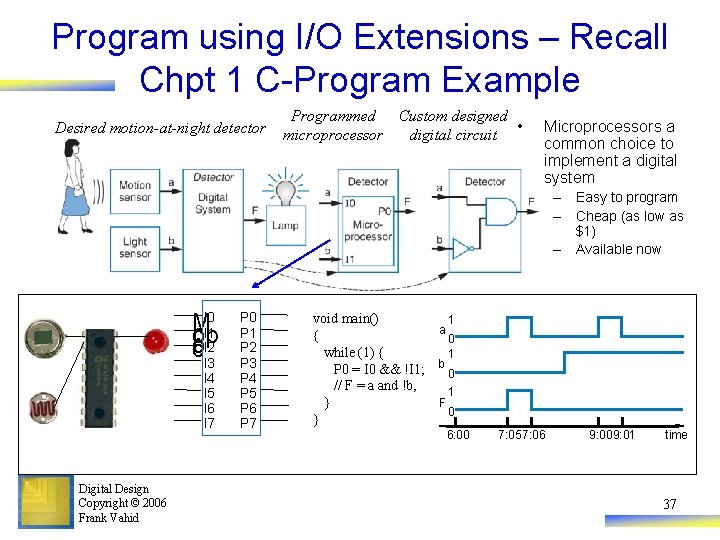

Program using I/O Extensions – Recall Chpt 1 C-Program Example Desired motion-at-night detector Programmed Custom designed • microprocessor digital circuit Microprocessors a common choice to implement a digital system – Easy to program – Cheap (as low as $1) – Available now I 0 M I 1 ro p ro I 2 c. I 3 I 4 I 5 I 6 I 7 Digital Design Copyright © 2006 Frank Vahid P 0 P 1 P 2 P 3 P 4 P 5 P 6 P 7 void main() 1 a { 0 while (1) { 1 b P 0 = I 0 && !I 1; 0 // F = a and !b, 1 F } 0 } 6: 00 7: 057: 06 9: 009: 01 time 37

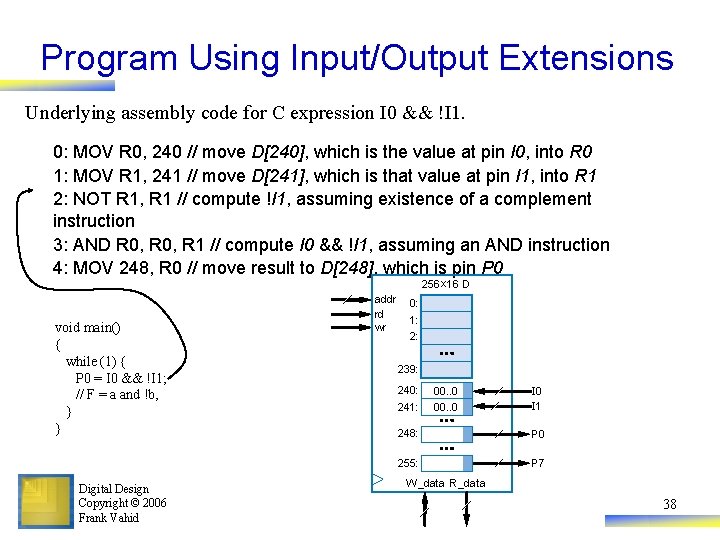

Program Using Input/Output Extensions Underlying assembly code for C expression I 0 && !I 1. 0: MOV R 0, 240 // move D[240], which is the value at pin I 0, into R 0 1: MOV R 1, 241 // move D[241], which is that value at pin I 1, into R 1 2: NOT R 1, R 1 // compute !I 1, assuming existence of a complement instruction 3: AND R 0, R 1 // compute I 0 && !I 1, assuming an AND instruction 4: MOV 248, R 0 // move result to D[248], which is pin P 0 256 x 16 D void main() { while (1) { P 0 = I 0 && !I 1; // F = a and !b, } } Digital Design Copyright © 2006 Frank Vahid addr rd wr 0: 1: 2: 239: 240: 241: 00. . 0 I 0 I 1 248: P 0 255: P 7 W_data R_data 38

Chapter Summary • Programmable processors are widely used – Easy availability, short design time • Basic architecture – – Datapath with register file and ALU Control unit with PC, IR, and controller Memories for instructions and data Control unit fetches, decodes, and executes • Three-instruction processor with machine-level programs – – Extended to six instructions Real processors have dozens or hundreds of instructions Extended to access external pins Modern processors are far more sophisticated • Instructive to see how one general circuit (programmable processor) can execute variety of behaviors just by programming 0 s and 1 s into an instruction memory Digital Design Copyright © 2006 Frank Vahid 39

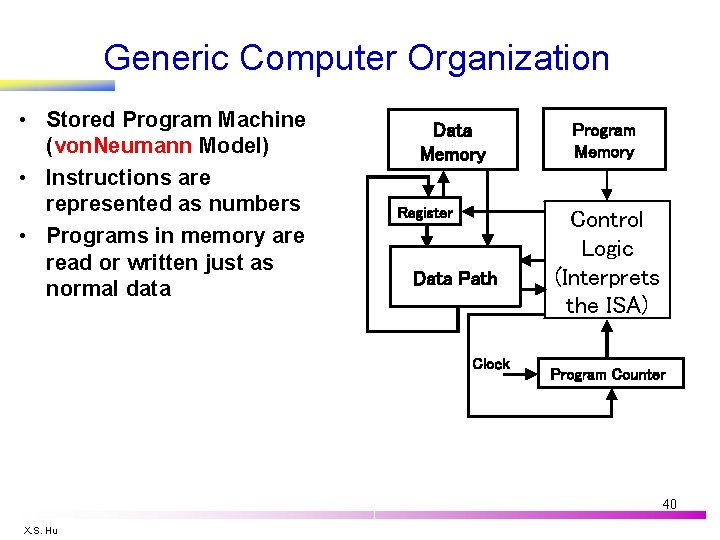

Generic Computer Organization • Stored Program Machine (von. Neumann Model) • Instructions are represented as numbers • Programs in memory are read or written just as normal data Data Memory Register Data Path Clock Digital Design Copyright © 2006 Frank Vahid X. S. Hu Program Memory Control Logic (Interprets the ISA) Program Counter 40

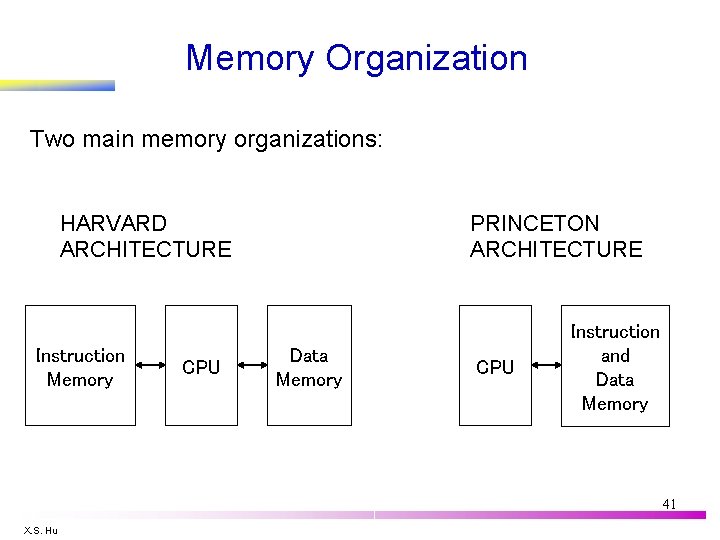

Memory Organization Two main memory organizations: HARVARD ARCHITECTURE Instruction Memory Digital Design Copyright © 2006 Frank Vahid X. S. Hu CPU PRINCETON ARCHITECTURE Data Memory CPU Instruction and Data Memory 41

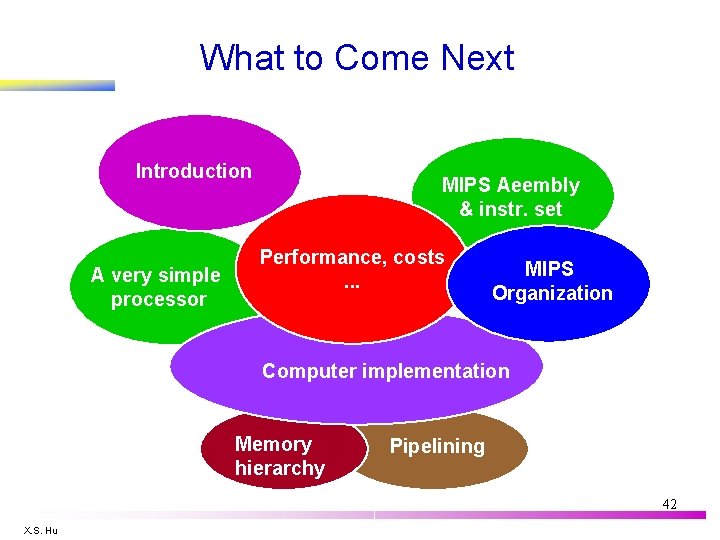

What to Come Next Introduction A very simple processor MIPS Aeembly & instr. set Performance, costs. . . MIPS Organization Computer implementation Memory hierarchy Digital Design Copyright © 2006 Frank Vahid X. S. Hu Pipelining 42

- Slides: 42