Digital block implementation methodology for a 130 nm

Digital block implementation methodology for a 130 nm process Microelecronics User Group meeting TWEPP 2009 – Paris Sandro Bonacini CERN PH/ESE sandro. bonacini@cern. ch

Motivation n Implementation of digital blocks q q n Using the IBM 130 nm standard cell library q n for small (~200 kgate) logic cores for digital or mixed signal ASICs Separate substrate/ground and n-well/VDD biasing for mixed signal designs Defined methodology compatible with mixed signal design flows q Open Access based Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch

Design flow components n Tools q q q n Virtuoso 6. 1. 3 (OA based) SOC Encounter 7. 1 Conformal 7. 2 EXT 7. 1. 2 (QRC) Assura 3. 2 Calibre 2008. 3 Design Kits q IBM CMOS 8 RF DM design kit V 1. 6 n q 3 thin, 2 thick, 3 RF metals. IBM CMOS 8 RF LM design kit V 1. 6 n 6 thin, 2 thick metals. Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch

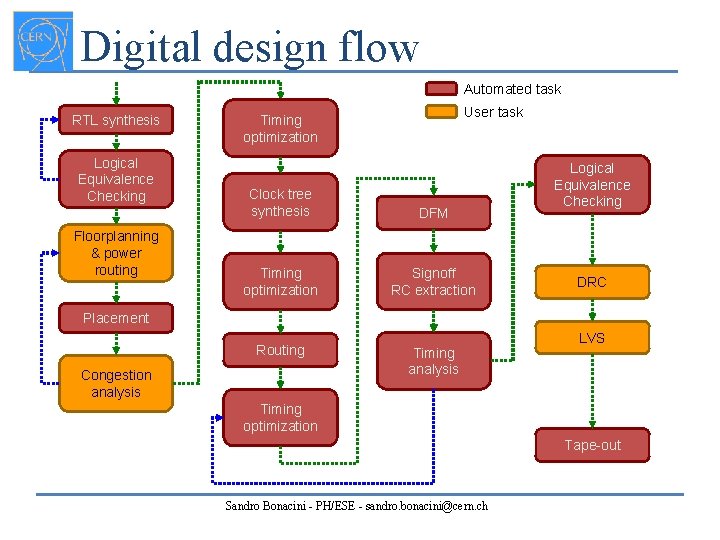

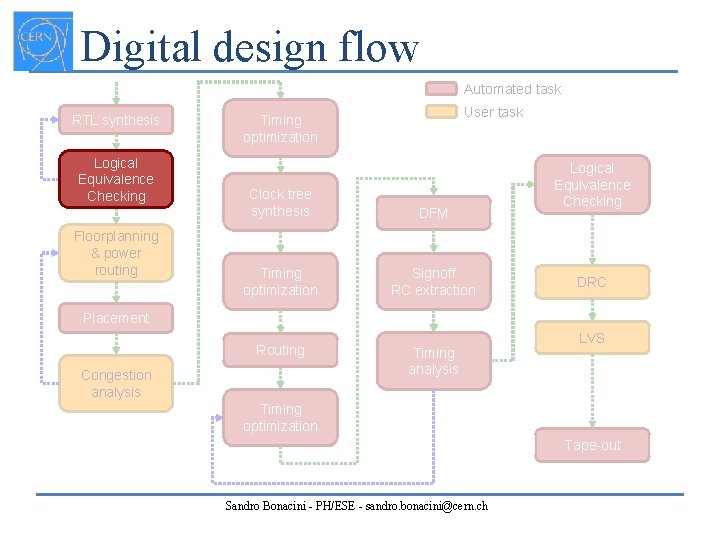

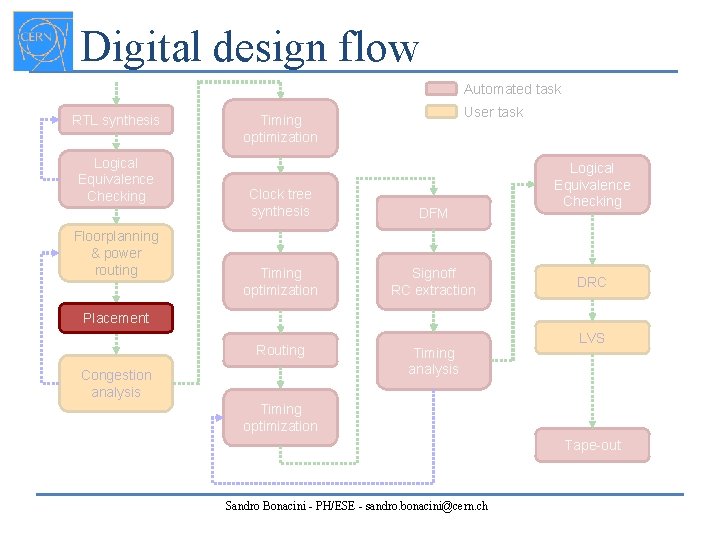

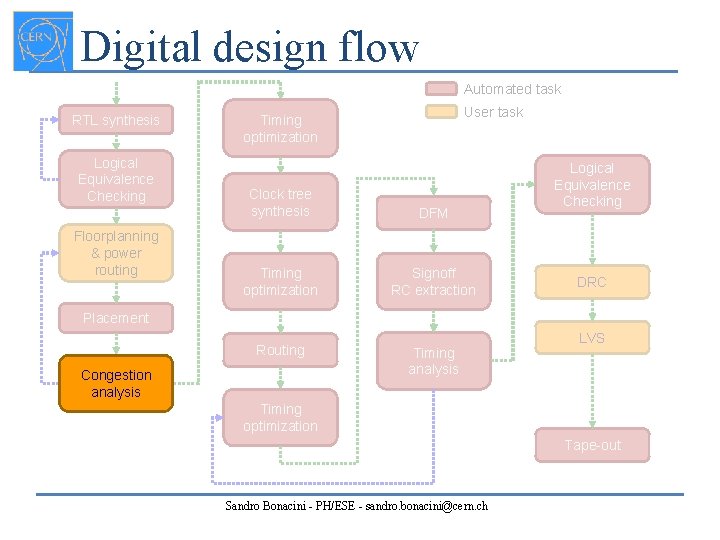

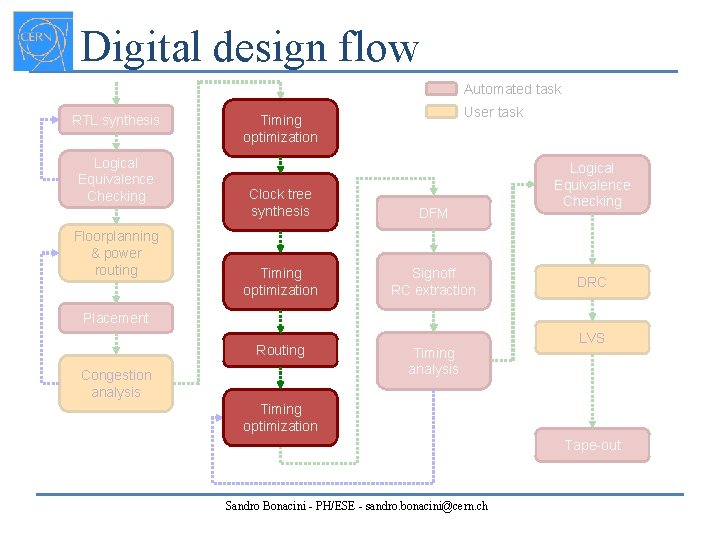

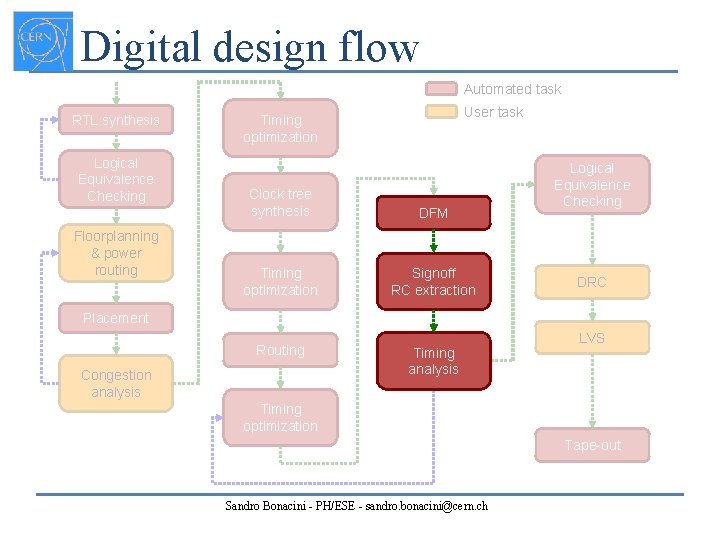

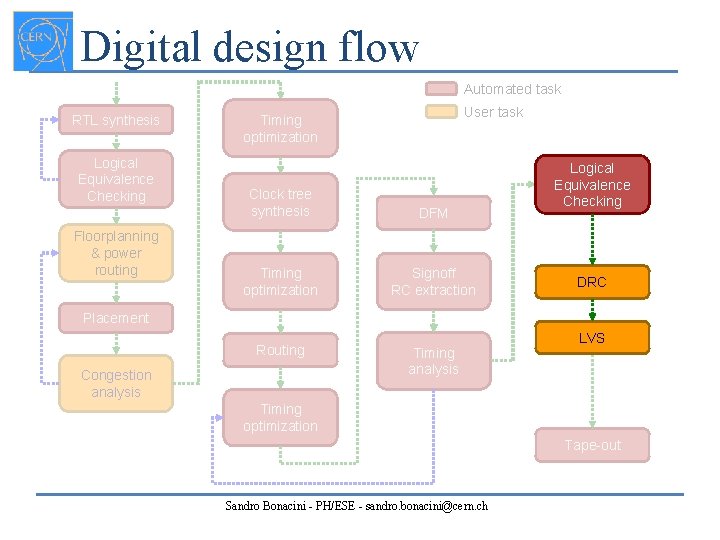

Digital design flow Automated task RTL synthesis Logical Equivalence Checking Floorplanning & power routing User task Timing optimization Clock tree synthesis DFM Timing optimization Signoff RC extraction Logical Equivalence Checking DRC Placement Routing Congestion analysis Timing analysis LVS Timing optimization Tape-out Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch

Synthesis n Timing constraints: q q q Clock definitions Input delays, fanout, transition, etc. Output load, etc. Max timing Liberty libraries [. lib] Timing constraints [. sdc] RTL description [. v] / [. vhd] RTL synthesis Synthesis, mapping and timing reports Capacitance tables [. Cap. Tbl] Abstract layout Definition [. lef] Mapped netlist [. v] RTL compiler script [. tcl] Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch Conformal script [. lec]

![RTL Compiler [rc] Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch RTL Compiler [rc] Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch](http://slidetodoc.com/presentation_image_h2/f2729e31b4acb2612085d6a7e964bebb/image-6.jpg)

RTL Compiler [rc] Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch

Digital design flow Automated task RTL synthesis Logical Equivalence Checking Floorplanning & power routing User task Timing optimization Clock tree synthesis DFM Timing optimization Signoff RC extraction Logical Equivalence Checking DRC Placement Routing Congestion analysis Timing analysis LVS Timing optimization Tape-out Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch

![Logic Equivalence Checking RTL description [. v] / [. vhd] Mapped netlist [. v] Logic Equivalence Checking RTL description [. v] / [. vhd] Mapped netlist [. v]](http://slidetodoc.com/presentation_image_h2/f2729e31b4acb2612085d6a7e964bebb/image-8.jpg)

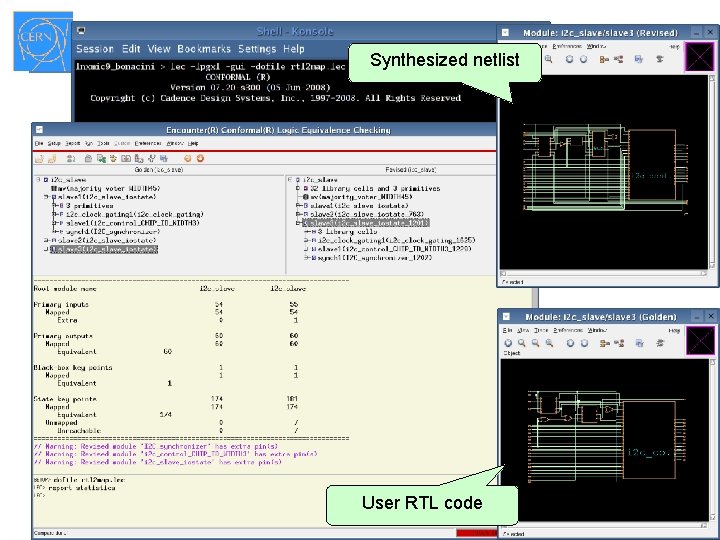

Logic Equivalence Checking RTL description [. v] / [. vhd] Mapped netlist [. v] Conformal script [. lec] Max timing Liberty libraries [. lib] Logical Equivalence Checking n LEC report Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch Tool: Conformal

Synthesized netlist RTL code Sandro Bonacini - PH/ESE -User sandro. bonacini@cern. ch

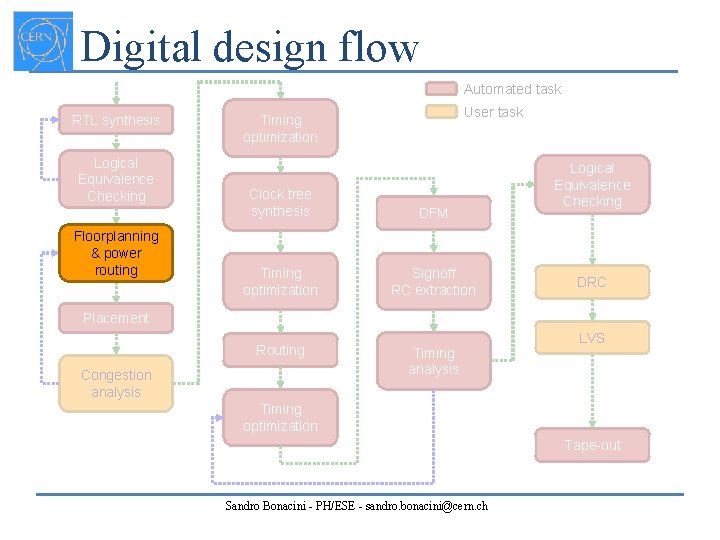

Digital design flow Automated task RTL synthesis Logical Equivalence Checking Floorplanning & power routing User task Timing optimization Clock tree synthesis DFM Timing optimization Signoff RC extraction Logical Equivalence Checking DRC Placement Routing Congestion analysis Timing analysis LVS Timing optimization Tape-out Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch

![Design import and floorplanning RTL description [. v] / [. vhd] Min/Max timing Liberty Design import and floorplanning RTL description [. v] / [. vhd] Min/Max timing Liberty](http://slidetodoc.com/presentation_image_h2/f2729e31b4acb2612085d6a7e964bebb/image-11.jpg)

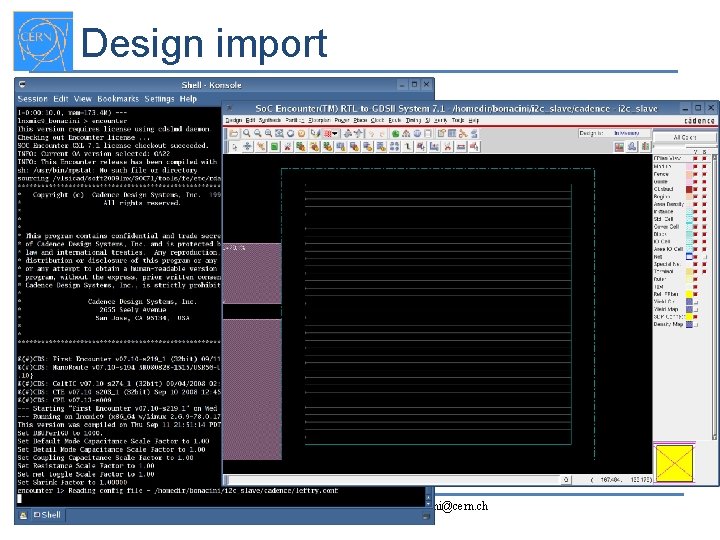

Design import and floorplanning RTL description [. v] / [. vhd] Min/Max timing Liberty libraries [. lib] Mapped netlist [. v] Floorplanning & power routing Reports Capacitance tables [. Cap. Tbl] QX tech file [. tch] Open Access Standard cells library [. oa] n Open Access Floorplanned Design [. oa] Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch Tool: Encounter

Design import Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch

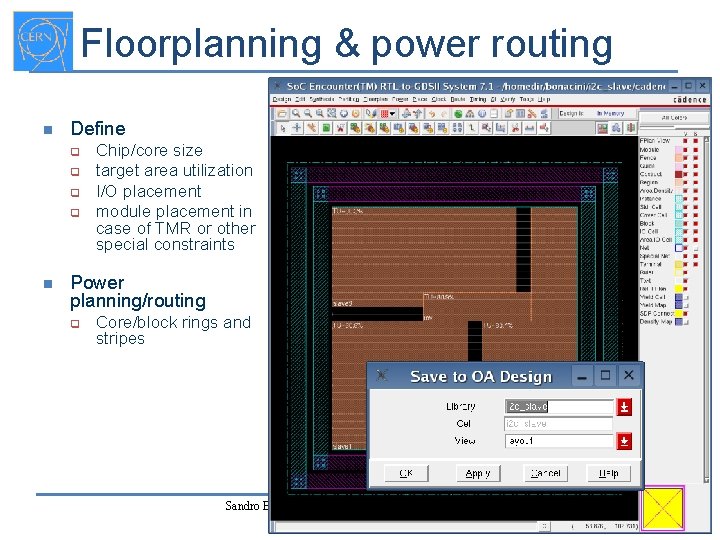

Floorplanning & power routing n Define q q n Chip/core size target area utilization I/O placement module placement in case of TMR or other special constraints Power planning/routing q Core/block rings and stripes Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch

Digital design flow Automated task RTL synthesis Logical Equivalence Checking Floorplanning & power routing User task Timing optimization Clock tree synthesis DFM Timing optimization Signoff RC extraction Logical Equivalence Checking DRC Placement Routing Congestion analysis Timing analysis LVS Timing optimization Tape-out Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch

![Placement n Encounter command file Open Access Floorplanned Design [. oa] Connect cells power/ground Placement n Encounter command file Open Access Floorplanned Design [. oa] Connect cells power/ground](http://slidetodoc.com/presentation_image_h2/f2729e31b4acb2612085d6a7e964bebb/image-15.jpg)

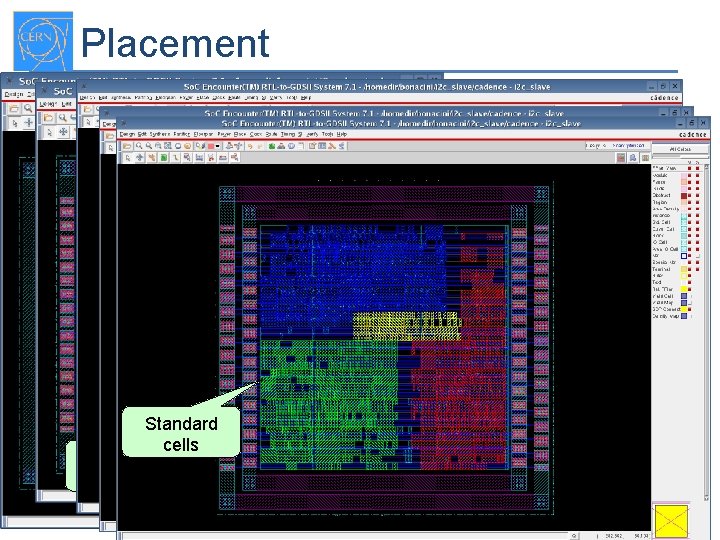

Placement n Encounter command file Open Access Floorplanned Design [. oa] Connect cells power/ground Add tap cells Placement Scan-chain reorder Reports Open Access Placed Design [. oa] Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch

Placement Tap cells Standard cells Power/ground connections Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch

Digital design flow Automated task RTL synthesis Logical Equivalence Checking Floorplanning & power routing User task Timing optimization Clock tree synthesis DFM Timing optimization Signoff RC extraction Logical Equivalence Checking DRC Placement Routing Congestion analysis Timing analysis LVS Timing optimization Tape-out Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch

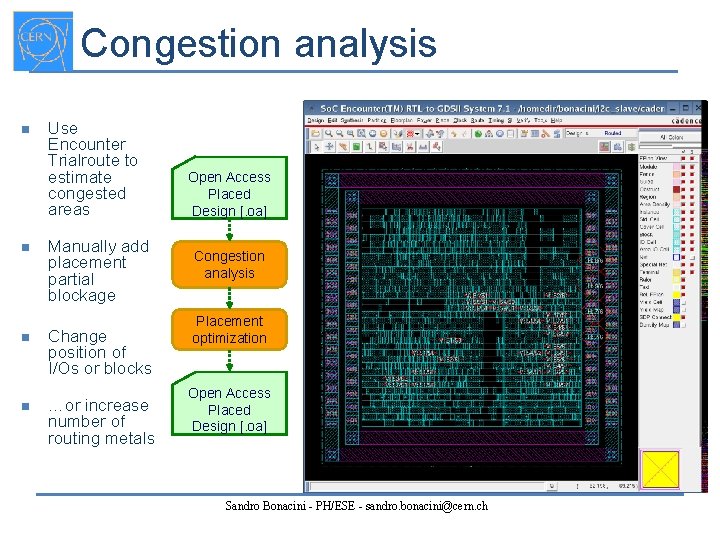

Congestion analysis n n Use Encounter Trialroute to estimate congested areas Manually add placement partial blockage n Change position of I/Os or blocks n …or increase number of routing metals Open Access Placed Design [. oa] Congestion analysis Placement optimization Open Access Placed Design [. oa] Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch

Digital design flow Automated task RTL synthesis Logical Equivalence Checking Floorplanning & power routing User task Timing optimization Clock tree synthesis DFM Timing optimization Signoff RC extraction Logical Equivalence Checking DRC Placement Routing Congestion analysis Timing analysis LVS Timing optimization Tape-out Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch

![Automatic P&R steps Open Access Placed Design [. oa] Timing optimization Clock tree synthesis Automatic P&R steps Open Access Placed Design [. oa] Timing optimization Clock tree synthesis](http://slidetodoc.com/presentation_image_h2/f2729e31b4acb2612085d6a7e964bebb/image-20.jpg)

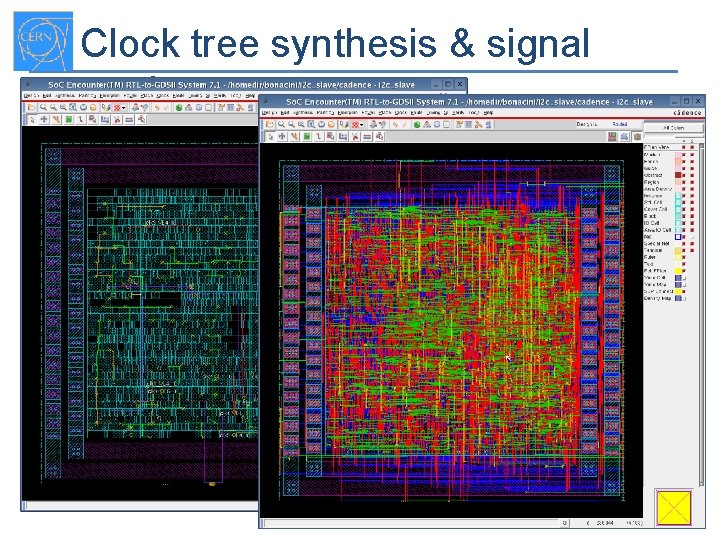

Automatic P&R steps Open Access Placed Design [. oa] Timing optimization Clock tree synthesis Timing optimization Routing Timing optimization Open Access Routed Design [. oa] Reports Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch

Clock tree synthesis & signal routing Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch

Digital design flow Automated task RTL synthesis Logical Equivalence Checking Floorplanning & power routing User task Timing optimization Clock tree synthesis DFM Timing optimization Signoff RC extraction Logical Equivalence Checking DRC Placement Routing Congestion analysis Timing analysis LVS Timing optimization Tape-out Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch

![Design for manufacturing Open Access Routed Design [. oa] Antenna fix Via optimization Cells Design for manufacturing Open Access Routed Design [. oa] Antenna fix Via optimization Cells](http://slidetodoc.com/presentation_image_h2/f2729e31b4acb2612085d6a7e964bebb/image-23.jpg)

Design for manufacturing Open Access Routed Design [. oa] Antenna fix Via optimization Cells & metal fill Signoff RC extraction Final netlist [. v] Open Access Final Design [. oa] Signal integrity analysis Delay file [. sdf] Timing analysis Signoff timing report Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch

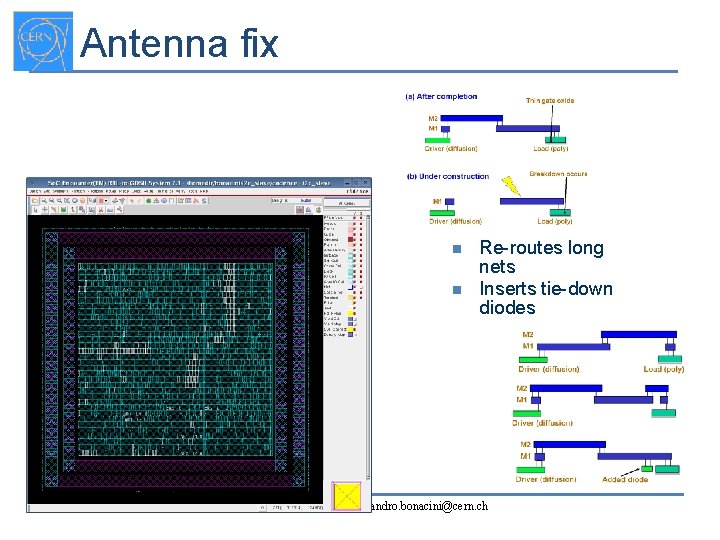

Antenna fix n n Re-routes long nets Inserts tie-down diodes Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch

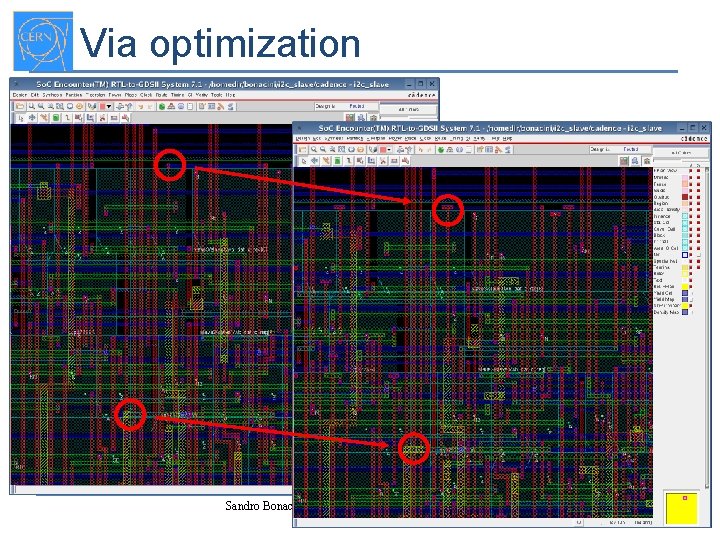

Via optimization Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch

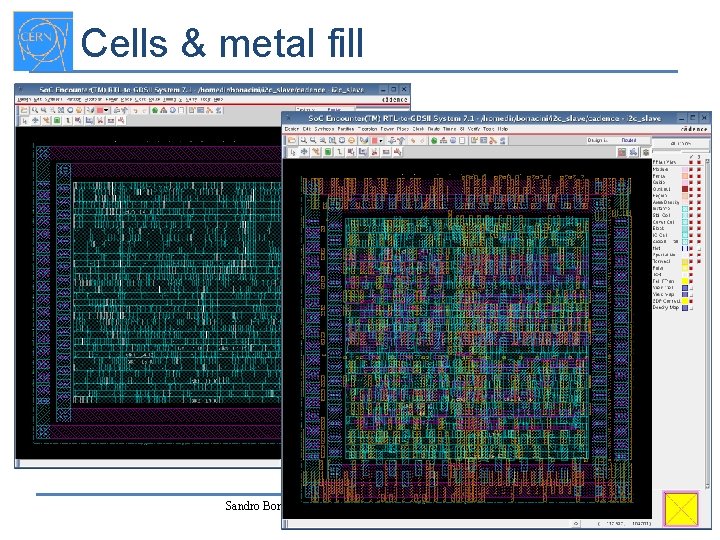

Cells & metal fill Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch

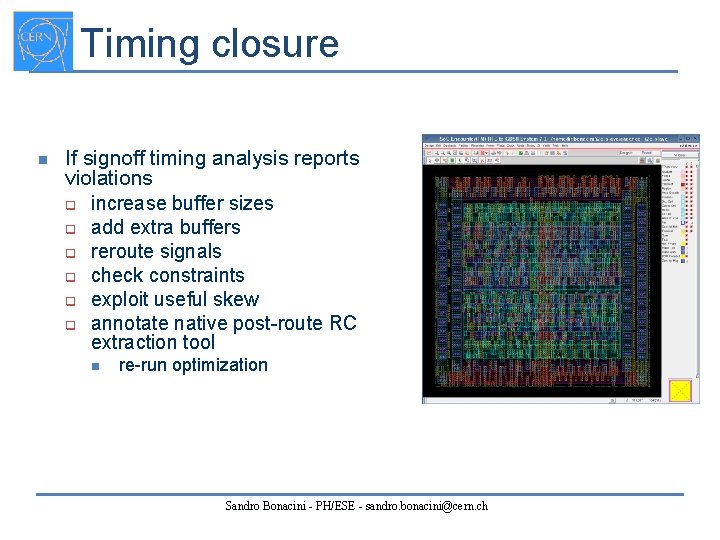

Timing closure n If signoff timing analysis reports violations q increase buffer sizes q add extra buffers q reroute signals q check constraints q exploit useful skew q annotate native post-route RC extraction tool n re-run optimization Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch

Digital design flow Automated task RTL synthesis Logical Equivalence Checking Floorplanning & power routing User task Timing optimization Clock tree synthesis DFM Timing optimization Signoff RC extraction Logical Equivalence Checking DRC Placement Routing Congestion analysis Timing analysis LVS Timing optimization Tape-out Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch

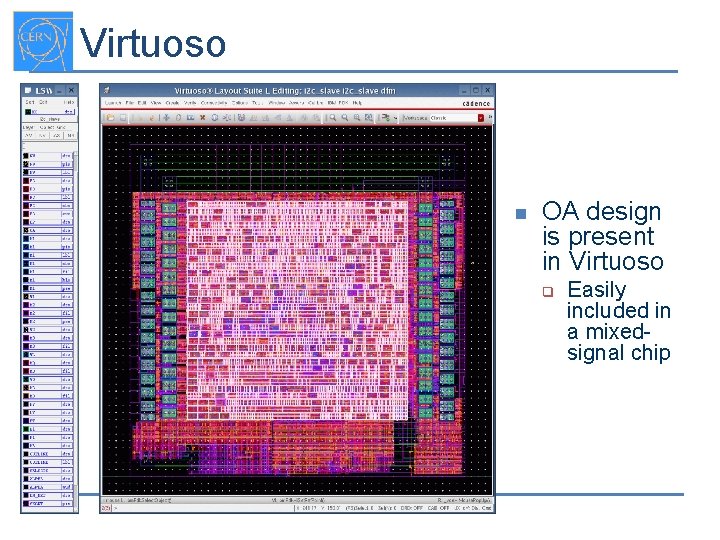

Virtuoso n OA design is present in Virtuoso q Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch Easily included in a mixedsignal chip

Thank you… n Design flow q …is soon to be available q Implementation of digital blocks n n q Using the IBM 130 nm standard cell library Defined methodology compatible with mixed signal design flows Open Access based Sandro Bonacini - PH/ESE - sandro. bonacini@cern. ch

- Slides: 30