Digital Atlas Vme Electronics DAVE Module Poster Number

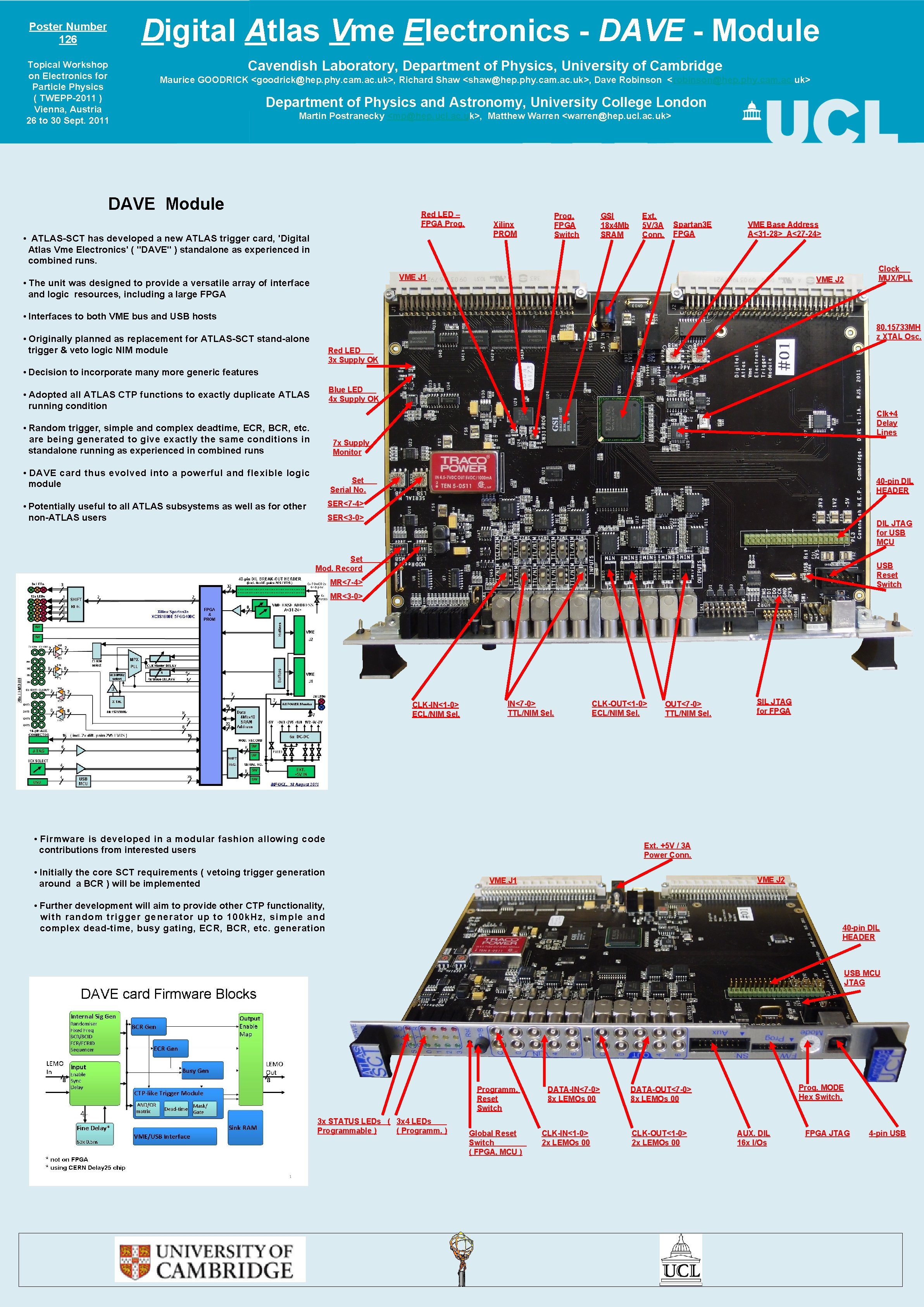

Digital Atlas Vme Electronics - DAVE - Module Poster Number 126 Topical Workshop on Electronics for Particle Physics ( TWEPP-2011 ) Vienna, Austria 26 to 30 Sept. 2011 Cavendish Laboratory, Department of Physics, University of Cambridge Maurice GOODRICK <goodrick@hep. phy. cam. ac. uk>, Richard Shaw <shaw@hep. phy. cam. ac. uk>, Dave Robinson <robinson@hep. phy. cam. ac. uk> Department of Physics and Astronomy, University College London Martin Postranecky <mp@hep. ucl. ac. uk>, Matthew Warren <warren@hep. ucl. ac. uk> DAVE Module Red LED – FPGA Prog. • ATLAS-SCT has developed a new ATLAS trigger card, 'Digital Atlas Vme Electronics' ( "DAVE" ) standalone as experienced in combined runs. Prog. FPGA Switch Xilinx PROM GSI 18 x 4 Mb SRAM Ext. 5 V/3 A Conn. Spartan 3 E FPGA VME Base Address A<31 -28> A<27 -24> VME J 1 • The unit was designed to provide a versatile array of interface and logic resources, including a large FPGA Clock MUX/PLL VME J 2 • Interfaces to both VME bus and USB hosts 80. 15733 MH z XTAL Osc. • Originally planned as replacement for ATLAS-SCT stand-alone trigger & veto logic NIM module Red LED 3 x Supply OK • Decision to incorporate many more generic features Blue LED 4 x Supply OK • Adopted all ATLAS CTP functions to exactly duplicate ATLAS running condition Clk+4 Delay Lines • Random trigger, simple and complex deadtime, ECR, BCR, etc. are being generated to give exactly the same conditions in standalone running as experienced in combined runs 7 x Supply Monitor • DAVE card thus evolved into a powerful and flexible logic module Set Serial No. 40 -pin DIL HEADER SER<7 -4> • Potentially useful to all ATLAS subsystems as well as for other non-ATLAS users SER<3 -0> DIL JTAG for USB MCU Set Mod. Record USB Reset Switch MR<7 -4> MR<3 -0> CLK-IN<1 -0> ECL/NIM Sel. IN<7 -0> TTL/NIM Sel. CLK-OUT<1 -0> ECL/NIM Sel. • Firmware is developed in a modular fashion allowing code contributions from interested users • Initially the core SCT requirements ( vetoing trigger generation around a BCR ) will be implemented OUT<7 -0> TTL/NIM Sel. SIL JTAG for FPGA Ext. +5 V / 3 A Power Conn. VME J 2 VME J 1 • Further development will aim to provide other CTP functionality, with random trigger generator up to 100 k. Hz, simple and complex dead-time, busy gating, ECR, BCR, etc. generation 40 -pin DIL HEADER USB MCU JTAG Programm. Reset Switch 3 x STATUS LEDs ( 3 x 4 LEDs Programmable ) ( Programm. ) Global Reset Switch ( FPGA, MCU ) DATA-IN<7 -0> 8 x LEMOs 00 CLK-IN<1 -0> 2 x LEMOs 00 Prog. MODE Hex Switch. DATA-OUT<7 -0> 8 x LEMOs 00 CLK-OUT<1 -0> 2 x LEMOs 00 AUX. DIL 16 x I/Os FPGA JTAG 4 -pin USB

- Slides: 1