Development of new ASIC 1 New pilot ASIC

- Slides: 8

Development of new ASIC 1. New pilot ASIC progress report 2. GOL test 3. Development of new pilot module Hiroyuki Kano RIKEN

New ASIC was submitted The new ASIC was submitted at the end of May. • 6 x 8 mm chip size • IBM 0. 25 mm process with radhard cell library (same as ALICE pilot) • CERN Multi Project Wafer (same as ALICE pilot) • Additional 32 bit input and 16 bit output

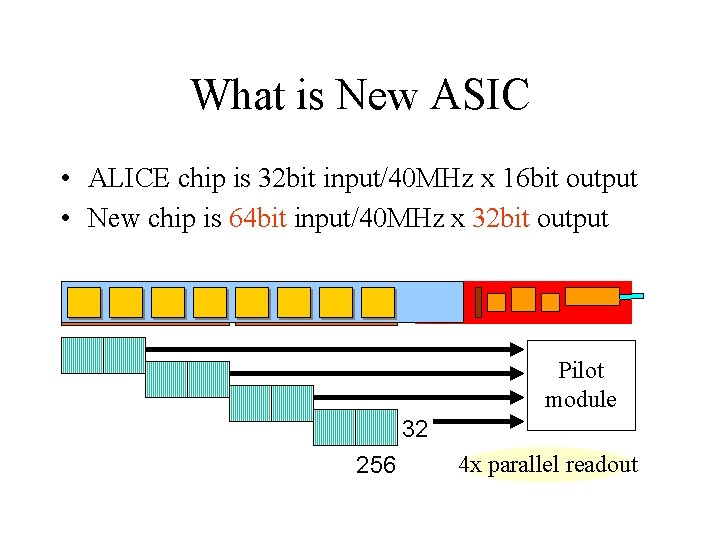

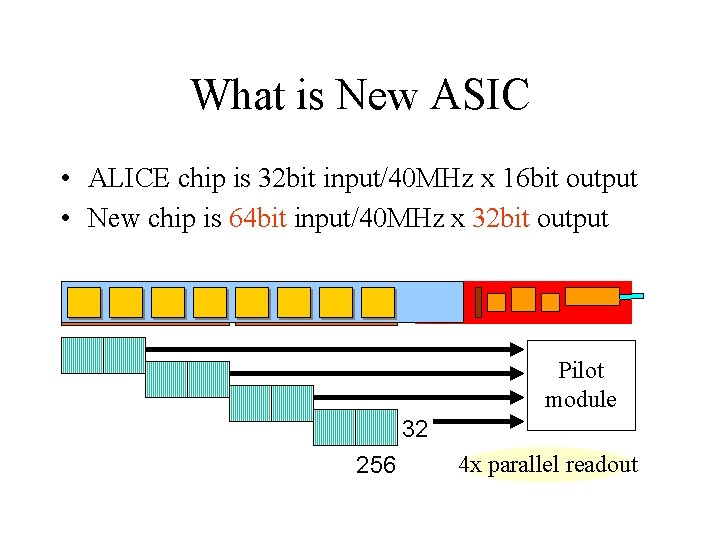

What is New ASIC • ALICE chip is 32 bit input/40 MHz x 16 bit output • New chip is 64 bit input/40 MHz x 32 bit output Pilot module 32 256 4 x parallel readout

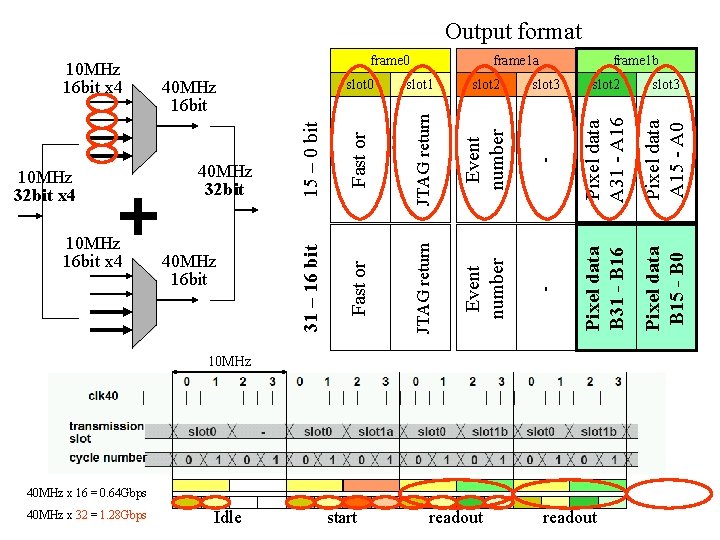

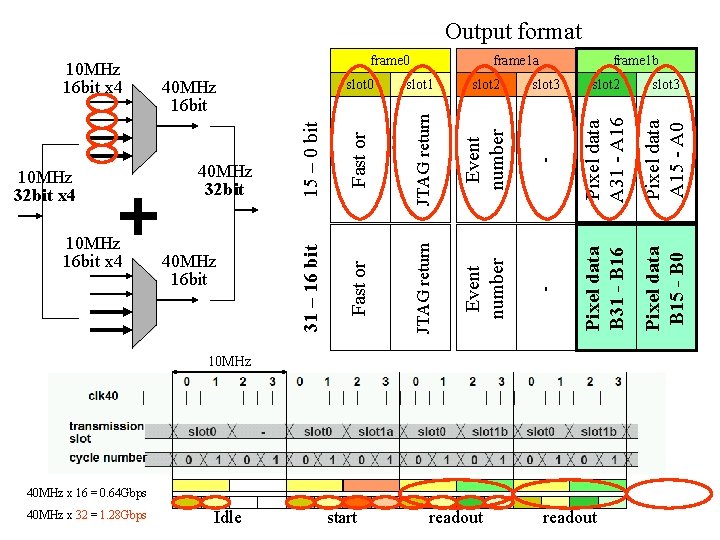

Output format slot 0 slot 1 JTAG return Event number - Pixel data A 31 - A 16 Pixel data A 15 - A 0 JTAG return Event number - Pixel data B 31 - B 16 Pixel data B 15 - B 0 40 MHz 16 bit slot 2 frame 1 b Fast or 40 MHz 32 bit frame 1 a Fast or 10 MHz 16 bit x 4 40 MHz 16 bit 15 – 0 bit 10 MHz 32 bit x 4 frame 0 31 – 16 bit 10 MHz 16 bit x 4 slot 3 slot 2 10 MHz 40 MHz x 16 = 0. 64 Gbps 40 MHz x 32 = 1. 28 Gbps Idle start readout slot 3

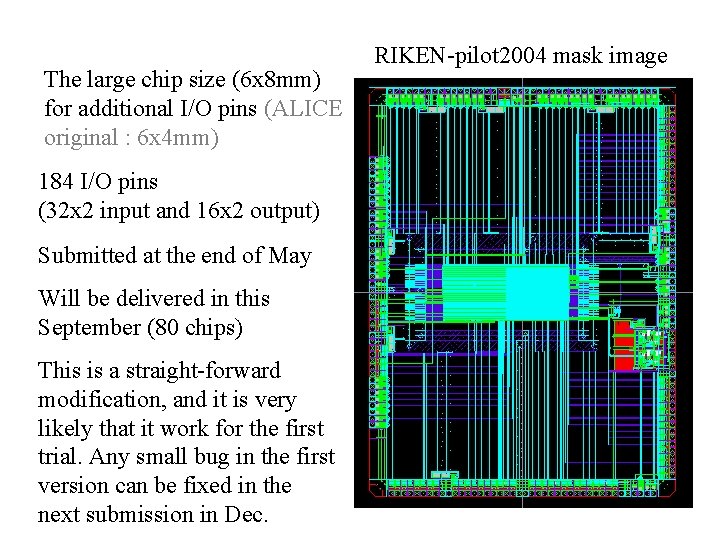

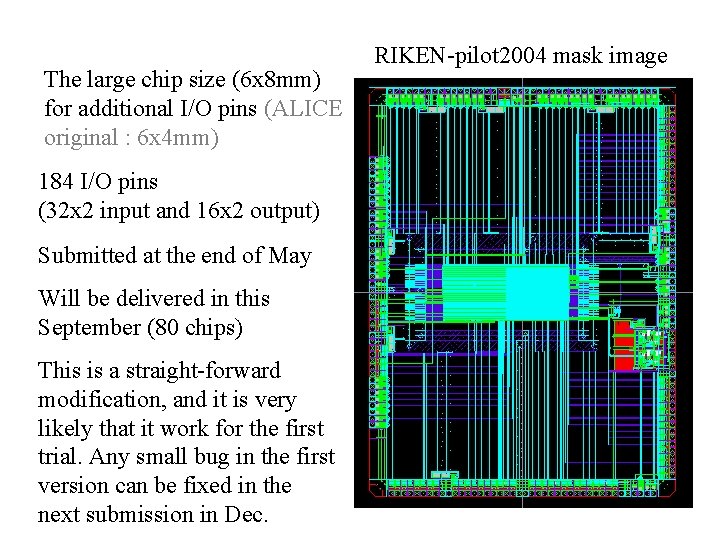

The large chip size (6 x 8 mm) for additional I/O pins (ALICE original : 6 x 4 mm) 184 I/O pins (32 x 2 input and 16 x 2 output) Submitted at the end of May Will be delivered in this September (80 chips) This is a straight-forward modification, and it is very likely that it work for the first trial. Any small bug in the first version can be fixed in the next submission in Dec. RIKEN-pilot 2004 mask image

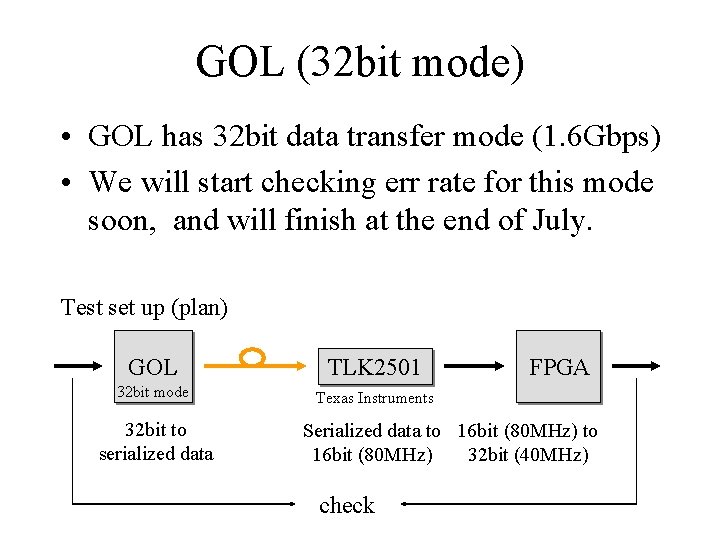

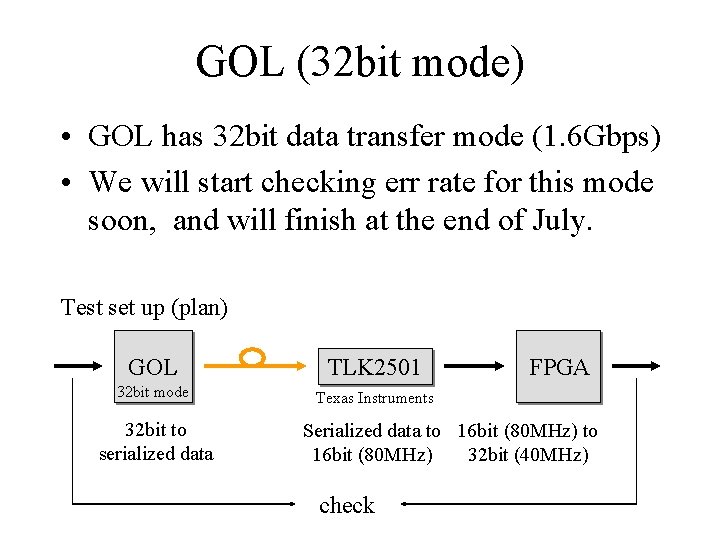

GOL (32 bit mode) • GOL has 32 bit data transfer mode (1. 6 Gbps) • We will start checking err rate for this mode soon, and will finish at the end of July. Test set up (plan) GOL TLK 2501 32 bit mode Texas Instruments 32 bit to serialized data FPGA Serialized data to 16 bit (80 MHz) 32 bit (40 MHz) check

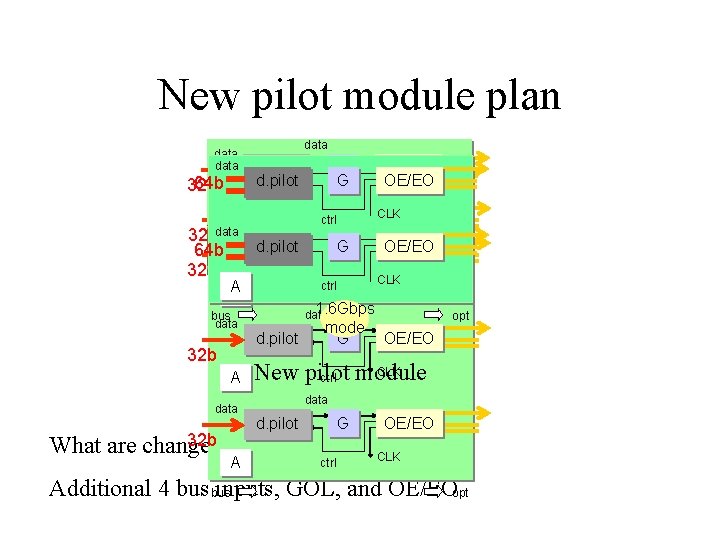

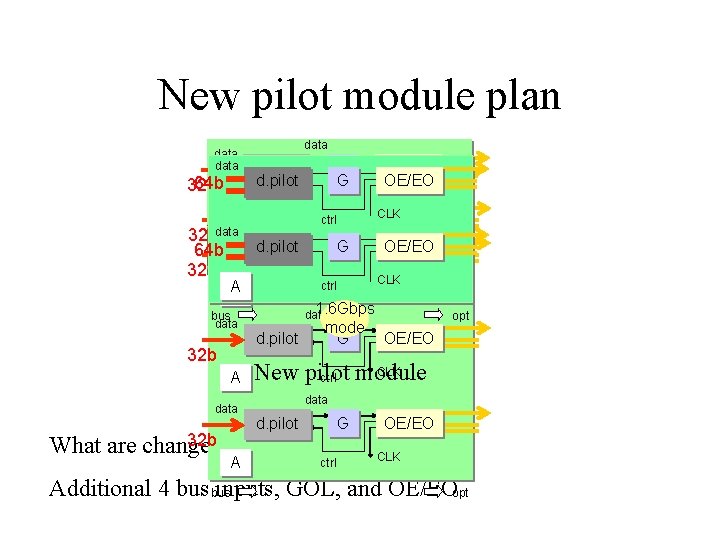

New pilot module plan data 64 b 32 b data A data d. pilot data 32 bbus data d. pilot 64 b A d. pilot 32 b bus. A A G G OE/EO data ctrl G data CLK OE/EO G ctrl. G OE/EO CLK OE/EO ctrl CLK opt 1. 6 Gbps data The original pilot moduleopt bus data 32 b A bus data 32 b What are changes: A d. pilot mode G OE/EO CLK New pilot module ctrl data d. pilot opt G ctrl OE/EO CLK Additional 4 bus inputs, GOL, and OE/EOopt

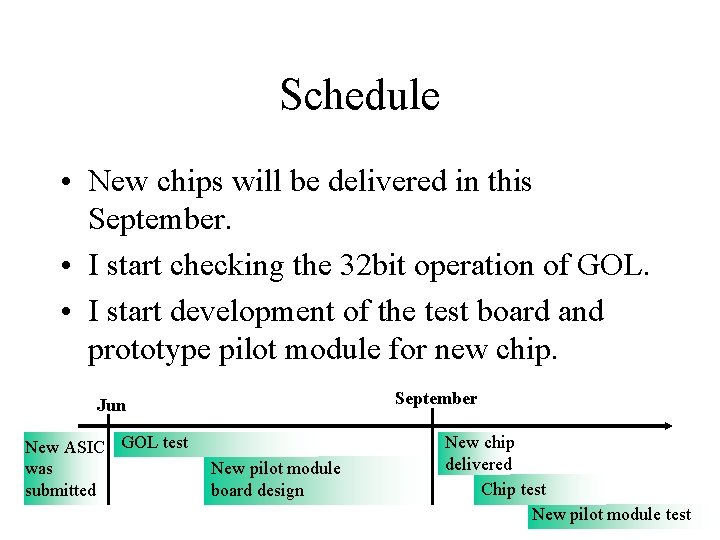

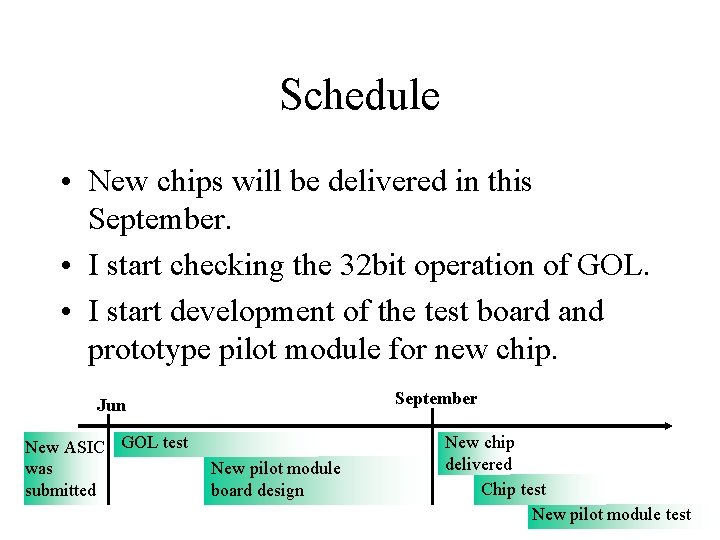

Schedule • New chips will be delivered in this September. • I start checking the 32 bit operation of GOL. • I start development of the test board and prototype pilot module for new chip. September Jun New ASIC GOL test was submitted New pilot module board design New chip delivered Chip test New pilot module test