Development of ATLAS Liquid Argon Calorimeter Frontend Electronics

- Slides: 23

Development of ATLAS Liquid Argon Calorimeter Front‐end Electronics for the HL‐LHC Andy Tiankuan Liu on behalf of the ATLAS Liquid Argon Group

Outline 1. Introduction 2. Analog front‐end – 65 nm – 130 nm – Si. Ge 3. ADCs 4. Optical links – Laser driver array ASICs – Optical transmitter array module 5. Summary Tiankuan Liu, TWEPP, Karlsruhe, Germany, September 27, 2016 2

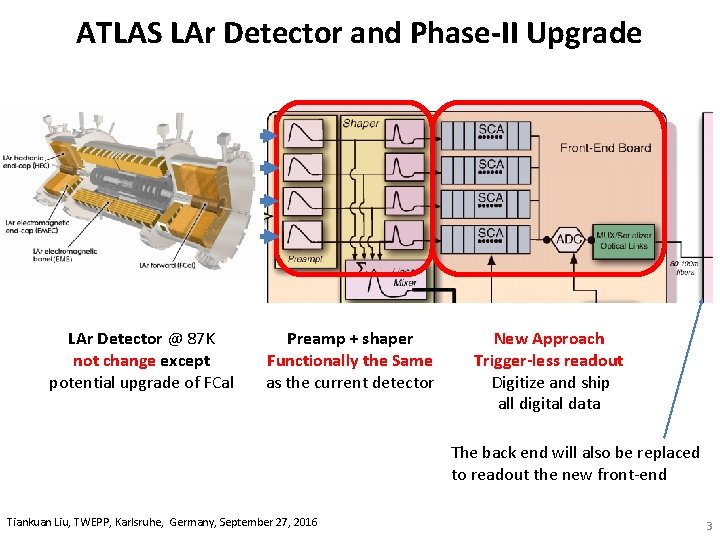

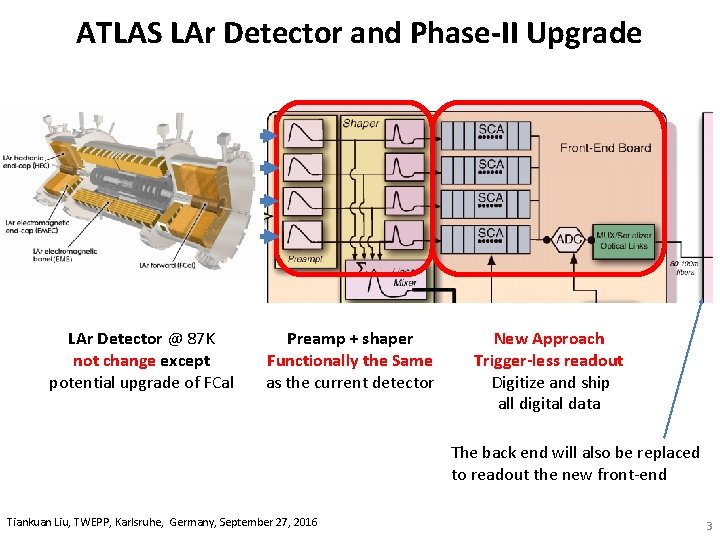

ATLAS LAr Detector and Phase-II Upgrade LAr Detector @ 87 K not change except potential upgrade of FCal Preamp + shaper Functionally the Same as the current detector New Approach Trigger-less readout Digitize and ship all digital data The back end will also be replaced to readout the new front‐end Tiankuan Liu, TWEPP, Karlsruhe, Germany, September 27, 2016 3

Upgrade Objectives Detector capacitance 0. 2 to 1. 5 n. F Signal dynamic range ~ 16 bits Noise requirements ~ 100 n. A Selectable input impedance 25 or 50 Ω for cable termination Moderate radiation tolerance requirements ~300 krad, 1013 cm‐ 2 1‐Me. V eq. neutrons • Digitize all 128 channels/FEB @ 14 bits, 40 or 80 MS/s with 2 gain scales. • Ship data from all channels off detector (trigger‐less readout). • Keep the power dissipation to the current one or lower. • • • Tiankuan Liu, TWEPP, Karlsruhe, Germany, September 27, 2016 4

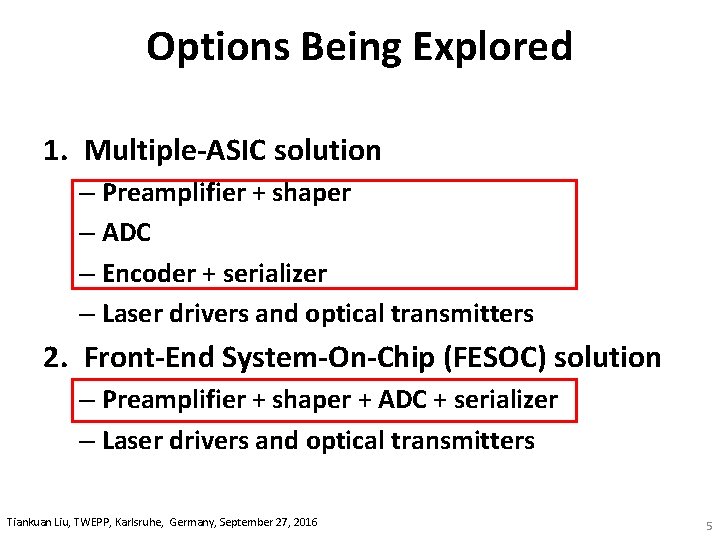

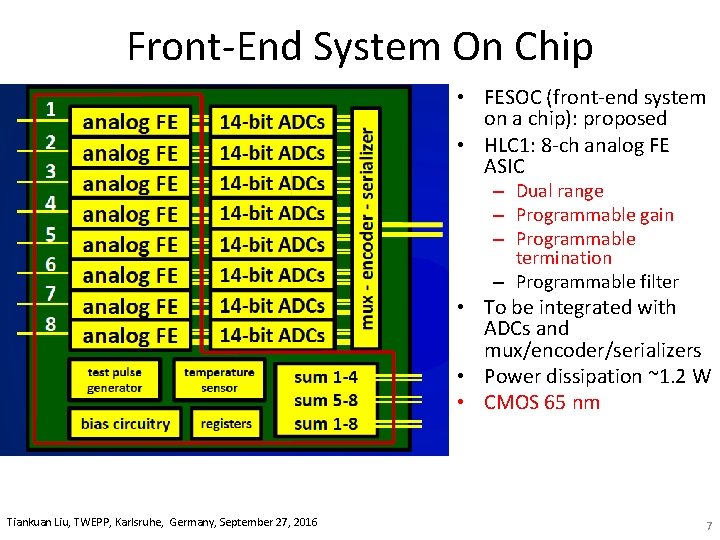

Options Being Explored 1. Multiple-ASIC solution – Preamplifier + shaper – ADC – Encoder + serializer – Laser drivers and optical transmitters 2. Front-End System-On-Chip (FESOC) solution – Preamplifier + shaper + ADC + serializer – Laser drivers and optical transmitters Tiankuan Liu, TWEPP, Karlsruhe, Germany, September 27, 2016 5

Outline 1. Introduction 2. Analog front‐end – 65 nm – 130 nm – Si. Ge 3. ADCs 4. Optical links – Laser driver array ASICs – Optical transmitter array module 5. Summary Tiankuan Liu, TWEPP, Karlsruhe, Germany, September 27, 2016 6

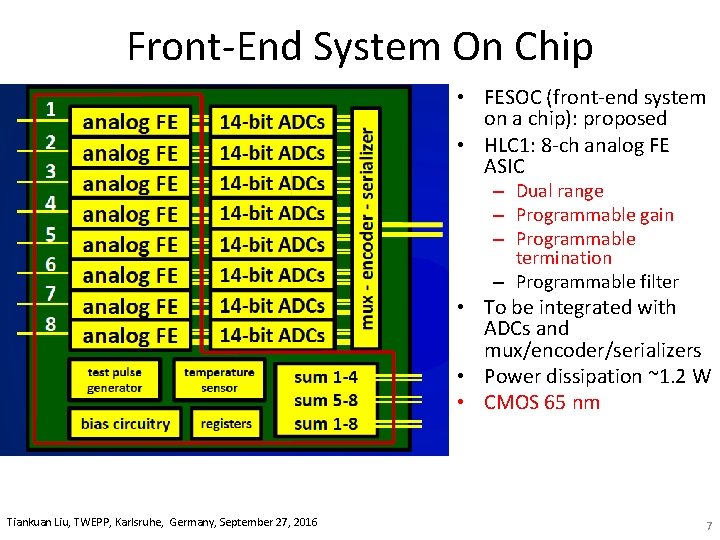

Front‐End System On Chip • FESOC (front‐end system on a chip): proposed • HLC 1: 8‐ch analog FE ASIC – Dual range – Programmable gain – Programmable termination – Programmable filter • To be integrated with ADCs and mux/encoder/serializers • Power dissipation ~1. 2 W • CMOS 65 nm Tiankuan Liu, TWEPP, Karlsruhe, Germany, September 27, 2016 7

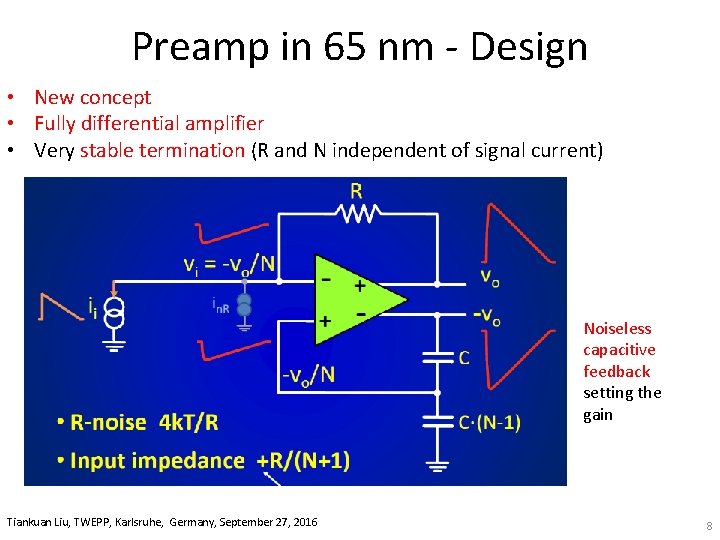

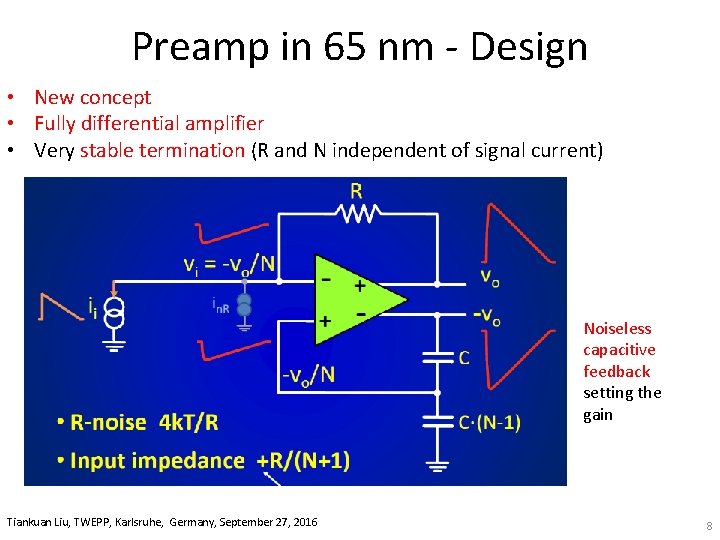

Preamp in 65 nm ‐ Design • New concept • Fully differential amplifier • Very stable termination (R and N independent of signal current) Noiseless capacitive feedback setting the gain Tiankuan Liu, TWEPP, Karlsruhe, Germany, September 27, 2016 8

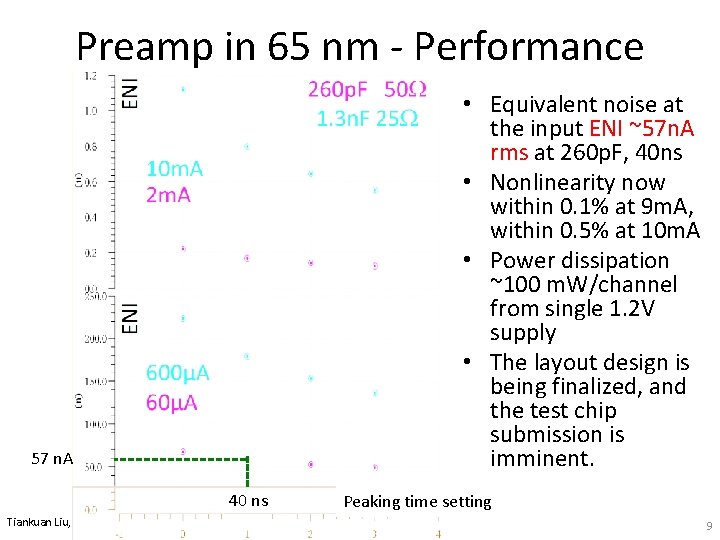

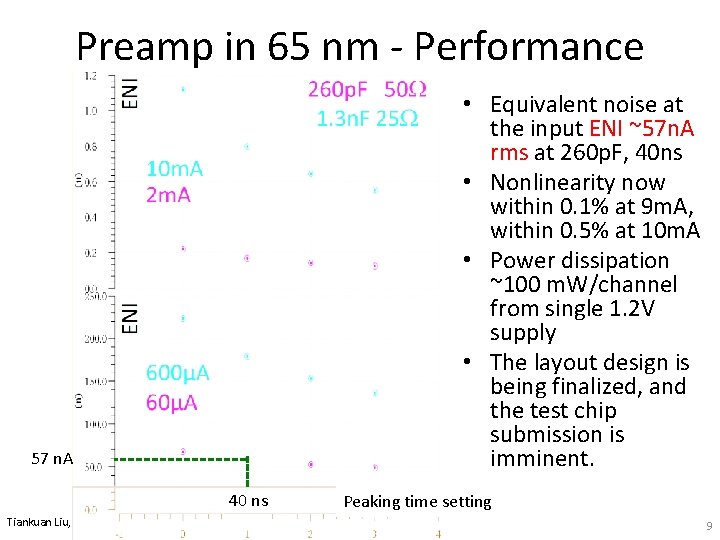

Preamp in 65 nm ‐ Performance • Equivalent noise at the input ENI ~57 n. A rms at 260 p. F, 40 ns • Nonlinearity now within 0. 1% at 9 m. A, within 0. 5% at 10 m. A • Power dissipation ~100 m. W/channel from single 1. 2 V supply • The layout design is being finalized, and the test chip submission is imminent. 57 n. A 40 ns Tiankuan Liu, TWEPP, Karlsruhe, Germany, September 27, 2016 Peaking time setting 9

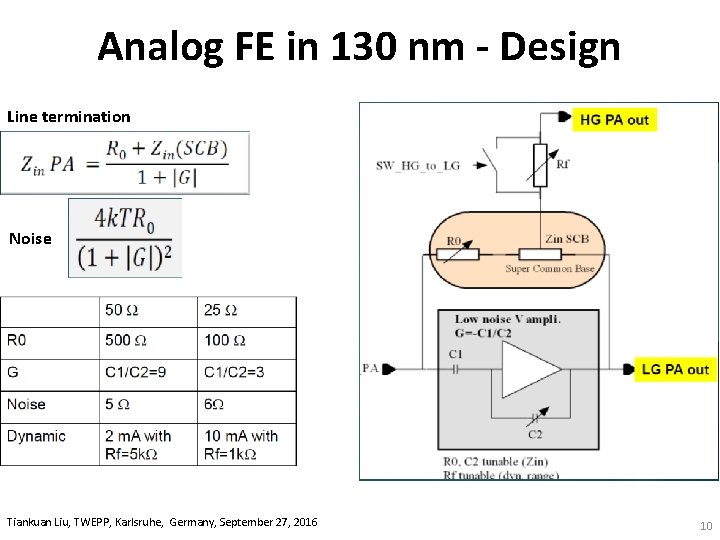

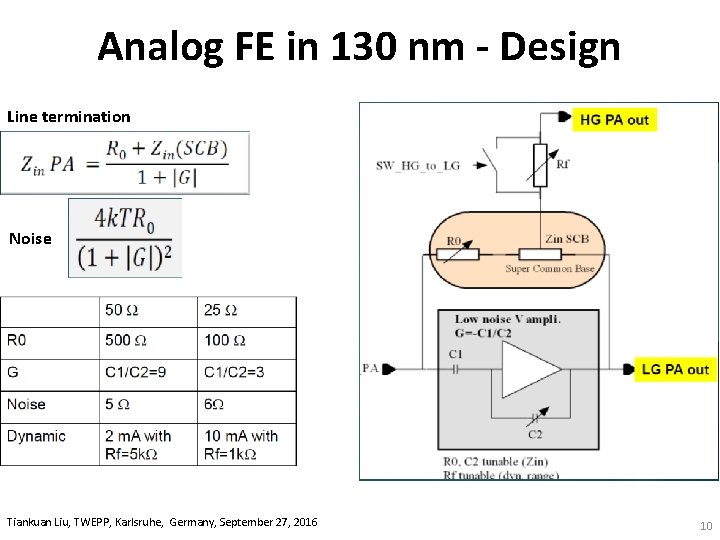

Analog FE in 130 nm - Design Line termination Noise Tiankuan Liu, TWEPP, Karlsruhe, Germany, September 27, 2016 10

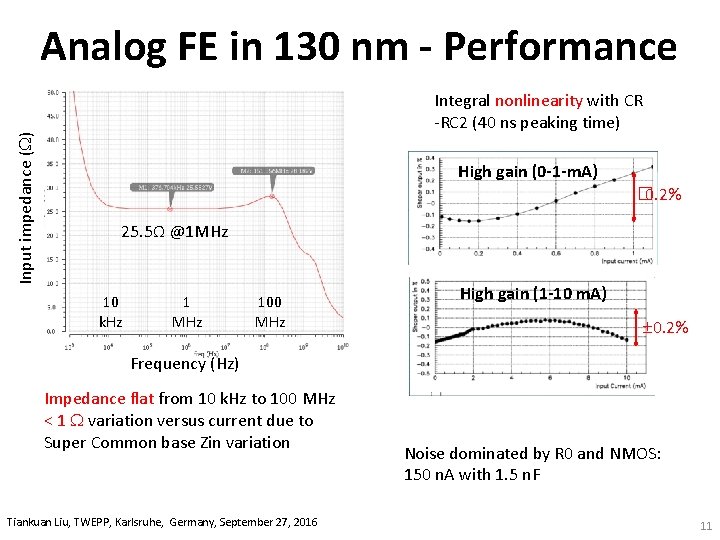

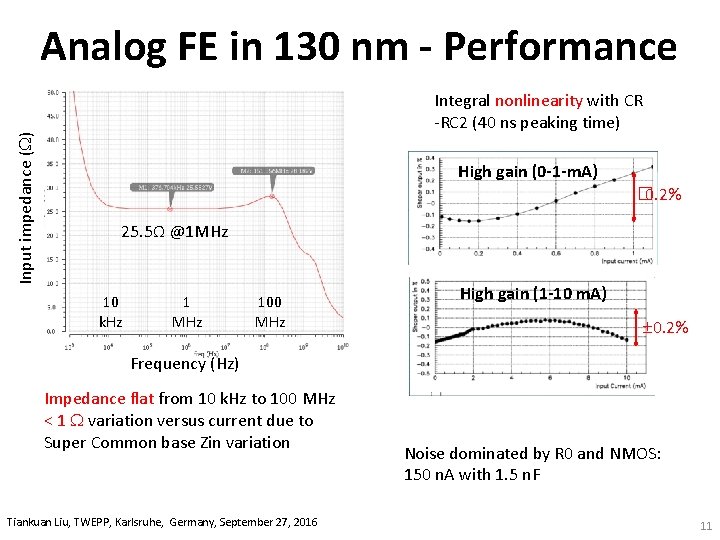

Input impedance ( ) Analog FE in 130 nm - Performance Integral nonlinearity with CR ‐RC 2 (40 ns peaking time) High gain (0 -1 -m. A) � 0. 2% 25. 5Ω @1 MHz 10 k. Hz 1 MHz 100 MHz High gain (1 -10 m. A) 0. 2% Frequency (Hz) Impedance flat from 10 k. Hz to 100 MHz < 1 variation versus current due to Super Common base Zin variation Tiankuan Liu, TWEPP, Karlsruhe, Germany, September 27, 2016 Noise dominated by R 0 and NMOS: 150 n. A with 1. 5 n. F 11

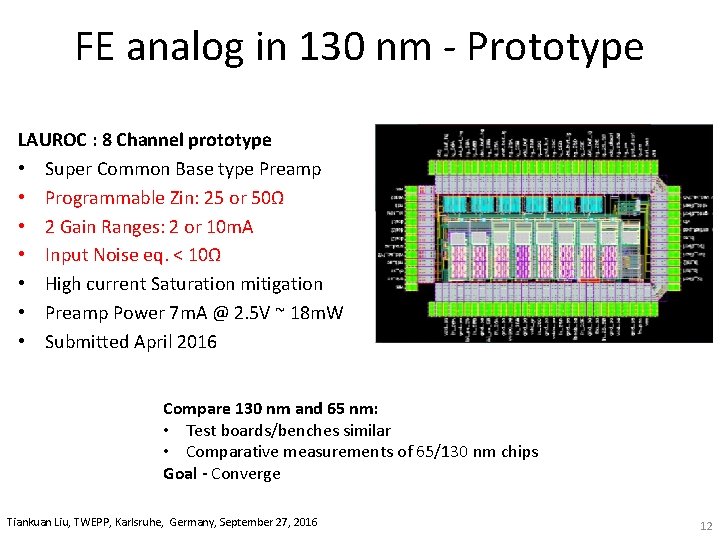

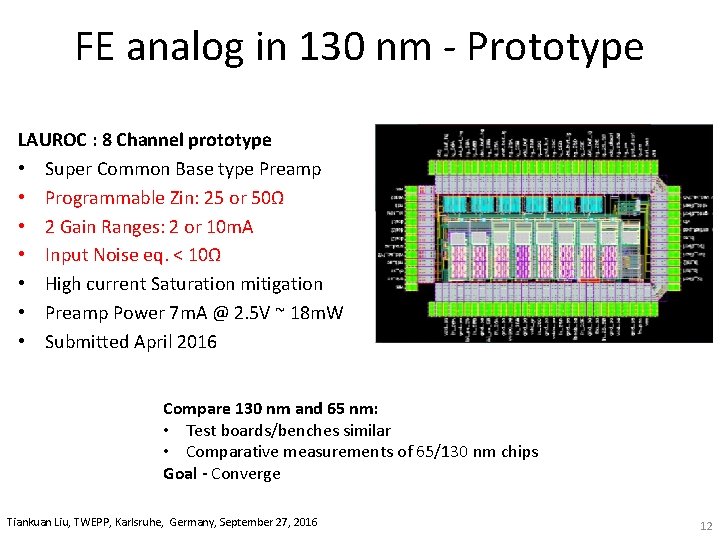

FE analog in 130 nm ‐ Prototype LAUROC : 8 Channel prototype • Super Common Base type Preamp • Programmable Zin: 25 or 50Ω • 2 Gain Ranges: 2 or 10 m. A • Input Noise eq. < 10Ω • High current Saturation mitigation • Preamp Power 7 m. A @ 2. 5 V ~ 18 m. W • Submitted April 2016 Compare 130 nm and 65 nm: • Test boards/benches similar • Comparative measurements of 65/130 nm chips Goal - Converge Tiankuan Liu, TWEPP, Karlsruhe, Germany, September 27, 2016 12

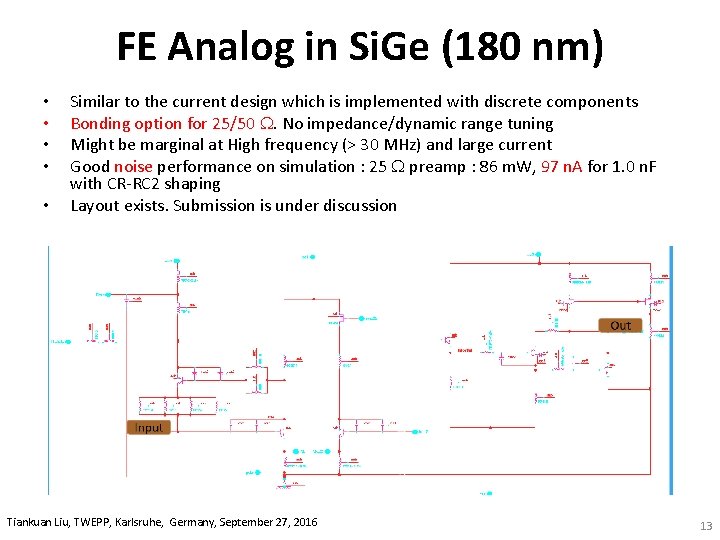

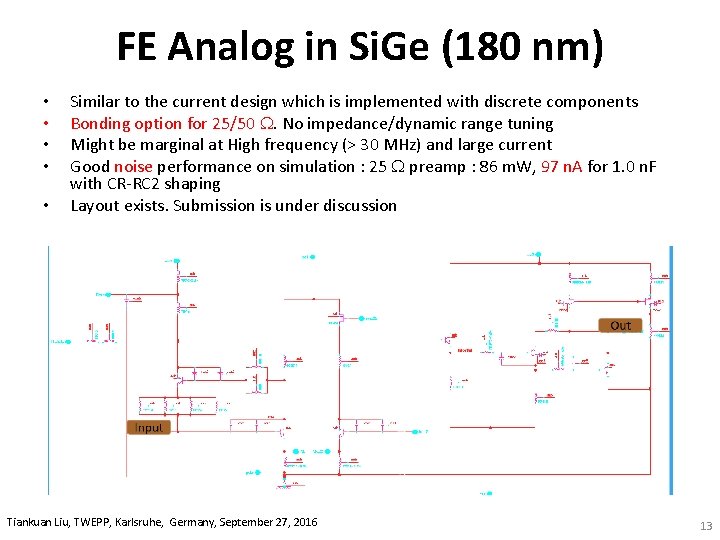

FE Analog in Si. Ge (180 nm) • • • Similar to the current design which is implemented with discrete components Bonding option for 25/50 . No impedance/dynamic range tuning Might be marginal at High frequency (> 30 MHz) and large current Good noise performance on simulation : 25 preamp : 86 m. W, 97 n. A for 1. 0 n. F with CR‐RC 2 shaping Layout exists. Submission is under discussion Tiankuan Liu, TWEPP, Karlsruhe, Germany, September 27, 2016 13

Outline 1. Introduction 2. Analog front‐end – 65 nm – 130 nm – Si. Ge 3. ADCs 4. Optical links – Laser driver array ASICs – Optical transmitter array module 5. Summary Tiankuan Liu, TWEPP, Karlsruhe, Germany, September 27, 2016 14

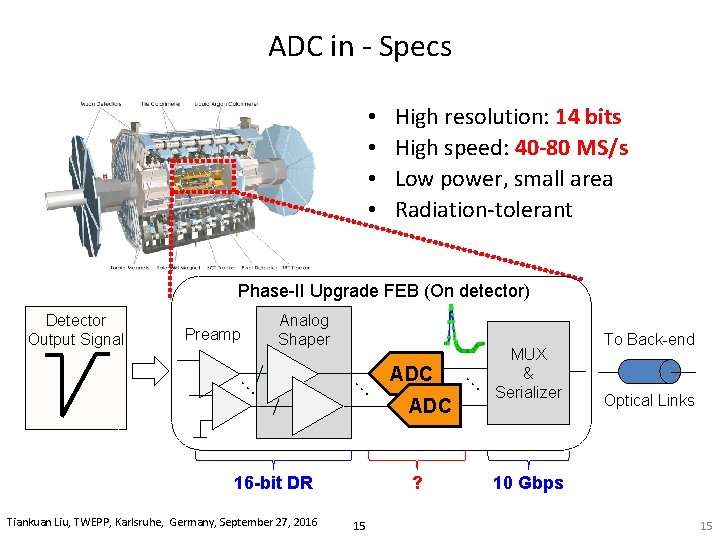

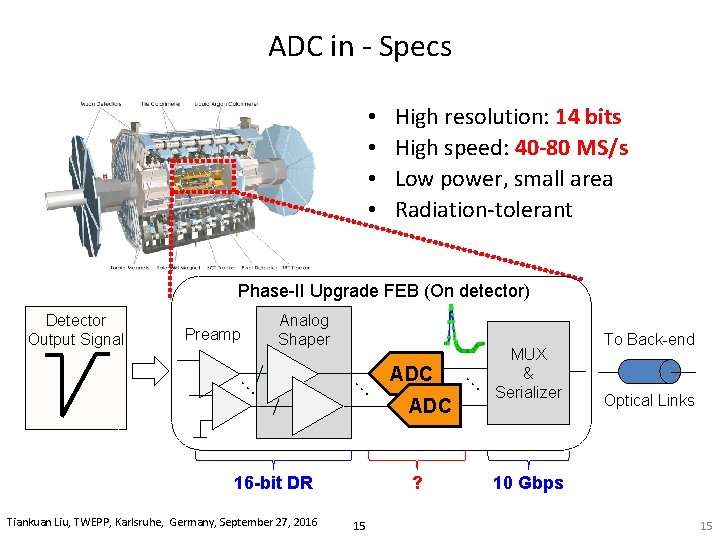

ADC in ‐ Specs • • High resolution: 14 bits High speed: 40 -80 MS/s Low power, small area Radiation‐tolerant Phase-II Upgrade FEB (On detector) Detector Output Signal Preamp Analog Shaper … … ADC 16 -bit DR Tiankuan Liu, TWEPP, Karlsruhe, Germany, September 27, 2016 ? 15 … MUX & Serializer To Back-end Optical Links 10 Gbps 15

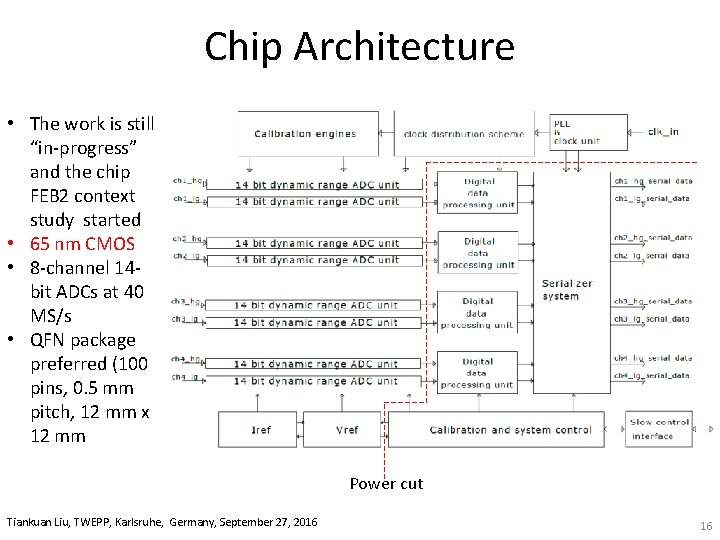

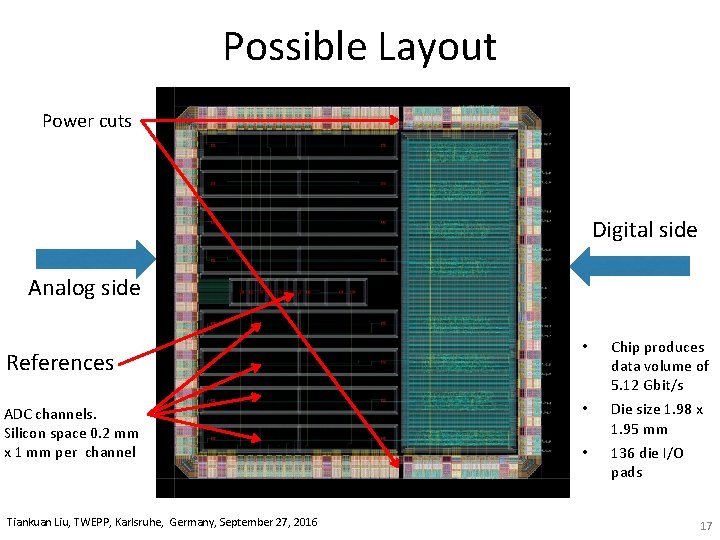

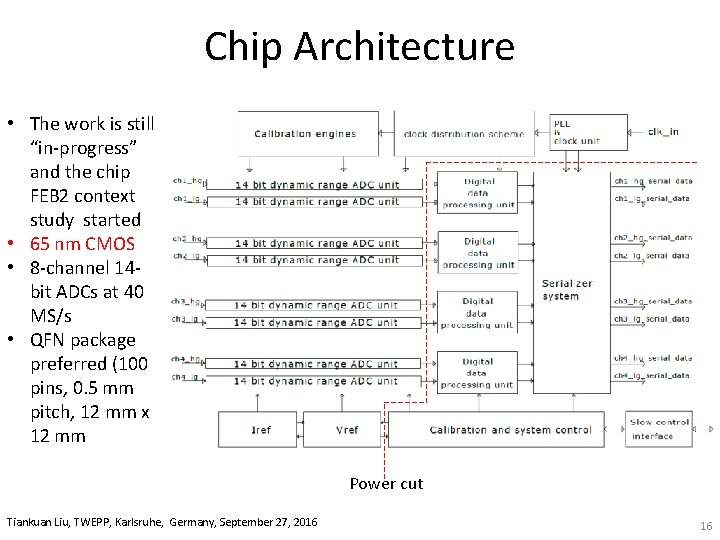

Chip Architecture • The work is still “in‐progress” and the chip FEB 2 context study started • 65 nm CMOS • 8‐channel 14‐ bit ADCs at 40 MS/s • QFN package preferred (100 pins, 0. 5 mm pitch, 12 mm x 12 mm Power cut Tiankuan Liu, TWEPP, Karlsruhe, Germany, September 27, 2016 16

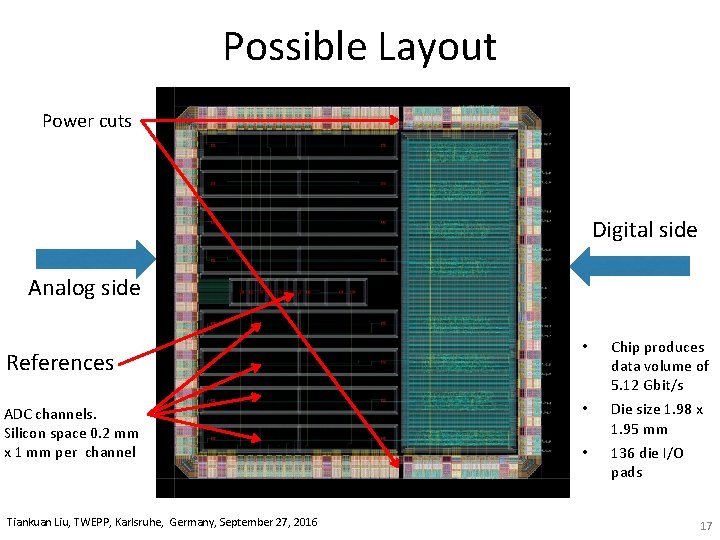

Possible Layout Power cuts Digital side Analog side References ADC channels. Silicon space 0. 2 mm x 1 mm per channel Tiankuan Liu, TWEPP, Karlsruhe, Germany, September 27, 2016 • Chip produces data volume of 5. 12 Gbit/s • Die size 1. 98 x 1. 95 mm • 136 die I/O pads 17

Outline 1. Introduction 2. Analog front‐end – 65 nm – 130 nm – Si. Ge 3. ADCs 4. Optical links – Laser driver array ASICs – Optical transmitter array module 5. Summary Tiankuan Liu, TWEPP, Karlsruhe, Germany, September 27, 2016 18

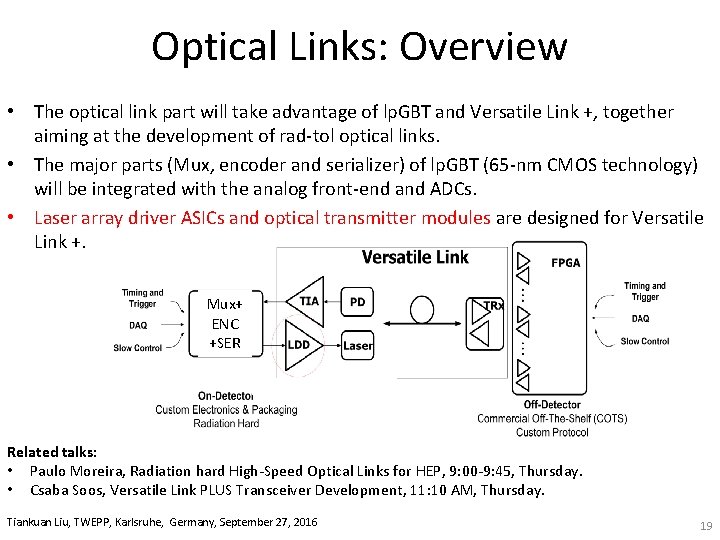

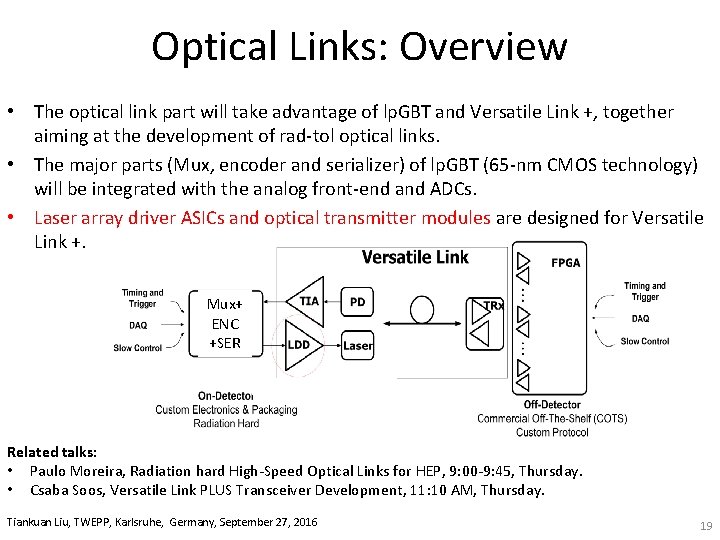

Optical Links: Overview • The optical link part will take advantage of lp. GBT and Versatile Link +, together aiming at the development of rad‐tol optical links. • The major parts (Mux, encoder and serializer) of lp. GBT (65‐nm CMOS technology) will be integrated with the analog front‐end and ADCs. • Laser array driver ASICs and optical transmitter modules are designed for Versatile Link +. Mux+ ENC +SER Related talks: • Paulo Moreira, Radiation hard High‐Speed Optical Links for HEP, 9: 00‐ 9: 45, Thursday. • Csaba Soos, Versatile Link PLUS Transceiver Development, 11: 10 AM, Thursday. Tiankuan Liu, TWEPP, Karlsruhe, Germany, September 27, 2016 19

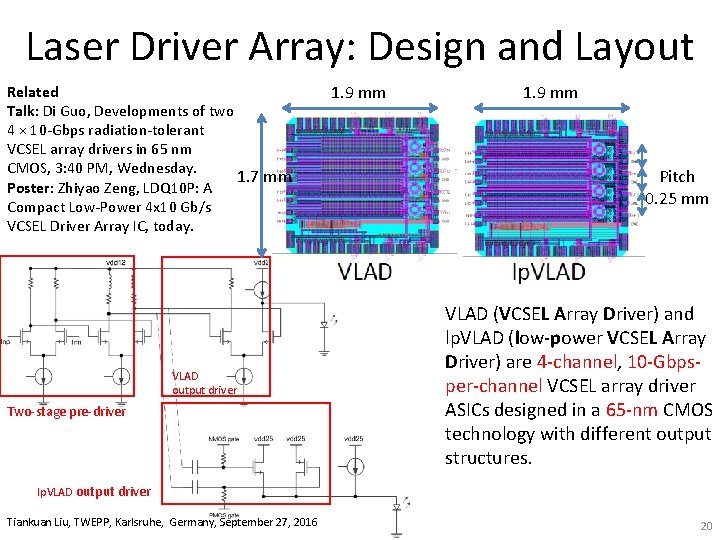

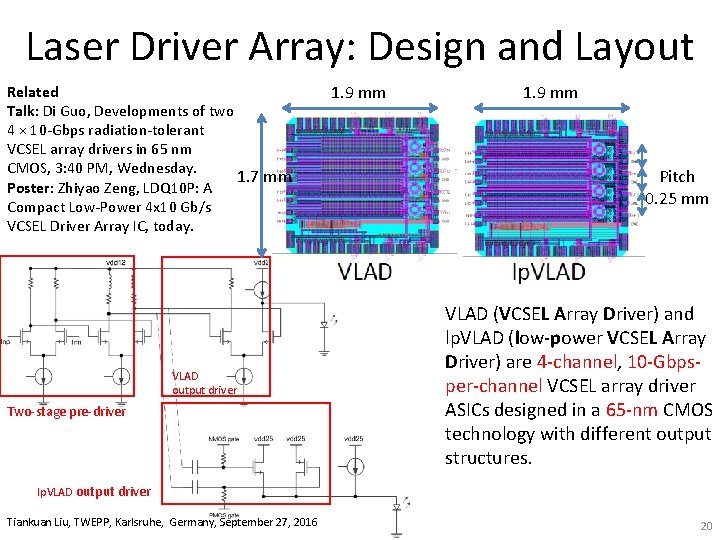

Laser Driver Array: Design and Layout Related Talk: Di Guo, Developments of two 4 × 10‐Gbps radiation‐tolerant VCSEL array drivers in 65 nm CMOS, 3: 40 PM, Wednesday. 1. 7 mm Poster: Zhiyao Zeng, LDQ 10 P: A Compact Low‐Power 4 x 10 Gb/s VCSEL Driver Array IC, today. VLAD output driver Two‐stage pre‐driver 1. 9 mm Pitch 0. 25 mm VLAD (VCSEL Array Driver) and lp. VLAD (low‐power VCSEL Array Driver) are 4‐channel, 10‐Gbps‐ per‐channel VCSEL array driver ASICs designed in a 65‐nm CMOS technology with different output structures. lp. VLAD output driver Tiankuan Liu, TWEPP, Karlsruhe, Germany, September 27, 2016 20

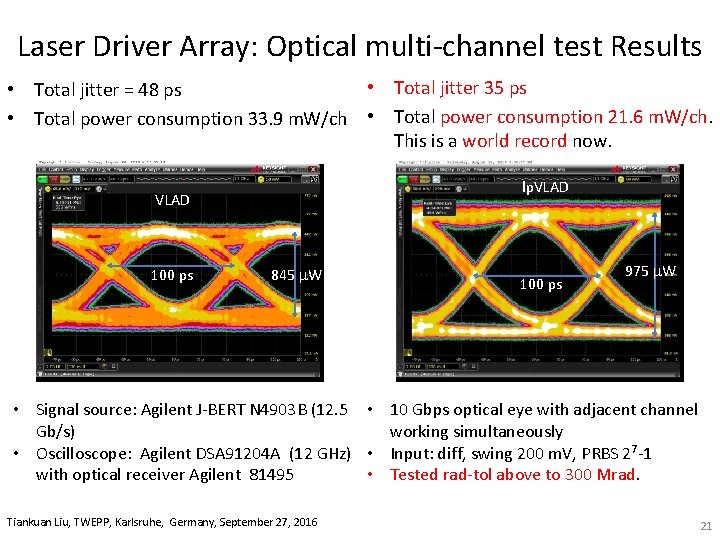

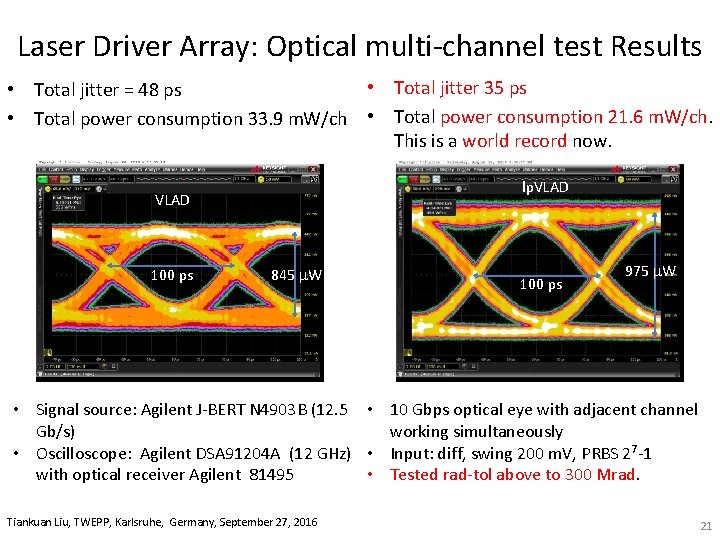

Laser Driver Array: Optical multi‐channel test Results • Total jitter 35 ps • Total jitter = 48 ps • Total power consumption 33. 9 m. W/ch • Total power consumption 21. 6 m. W/ch. This is a world record now. lp. VLAD 100 ps 845 W 100 ps 975 W • Signal source: Agilent J‐BERT N 4903 B (12. 5 • 10 Gbps optical eye with adjacent channel Gb/s) working simultaneously • Oscilloscope: Agilent DSA 91204 A (12 GHz) • Input: diff, swing 200 m. V, PRBS 27‐ 1 with optical receiver Agilent 81495 • Tested rad‐tol above to 300 Mrad. Tiankuan Liu, TWEPP, Karlsruhe, Germany, September 27, 2016 21

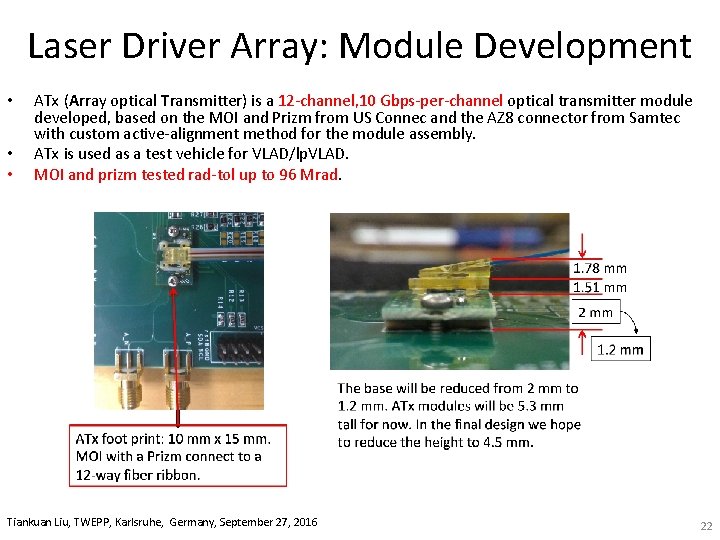

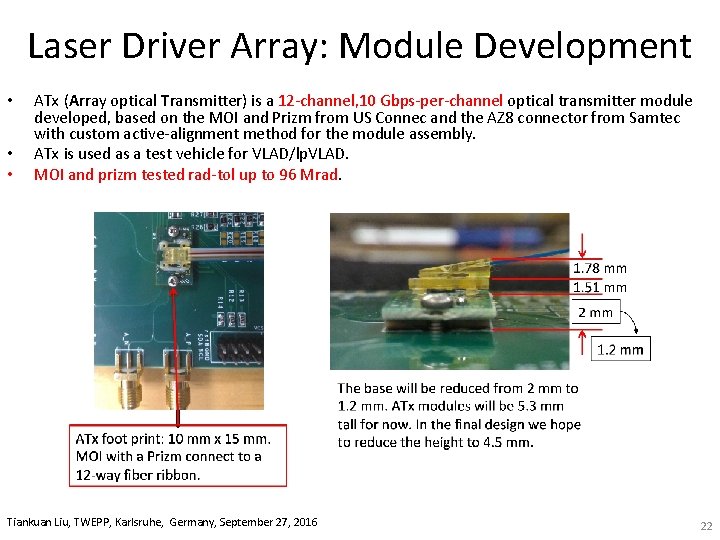

Laser Driver Array: Module Development • • • ATx (Array optical Transmitter) is a 12‐channel, 10 Gbps‐per‐channel optical transmitter module developed, based on the MOI and Prizm from US Connec and the AZ 8 connector from Samtec with custom active‐alignment method for the module assembly. ATx is used as a test vehicle for VLAD/lp. VLAD. MOI and prizm tested rad‐tol up to 96 Mrad. Tiankuan Liu, TWEPP, Karlsruhe, Germany, September 27, 2016 22

Summary • The ATLAS LAr front‐end readout electronics without trigger is under development to meet the high luminosity requirements. • An approach of System‐On‐Chip is being targeted: integrating all front‐end functional blocks (preamplifiers/shapers/ADCs/mux/encoders/serializers). • Three analog front‐end ASICs in early development stages show promising performances within termination, capacitance range, input signal dynamic range and power requirements. • New ADC design has been started. • Two radiation‐tolerant laser driver array ASICs and an optical transmitter modules are prototyped and tested. Tiankuan Liu, TWEPP, Karlsruhe, Germany, September 27, 2016 23