Detector Data Link DDL DDL hardware Csaba SOOS

Detector Data Link (DDL) DDL hardware Csaba SOOS DDL hardware, DATE training 1

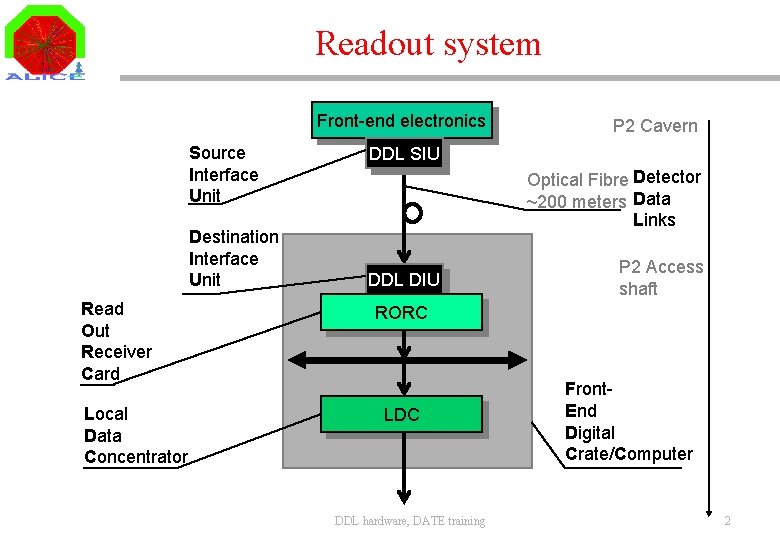

Readout system Front-end electronics Source Interface Unit Destination Interface Unit Read Out Receiver Card Local Data Concentrator P 2 Cavern DDL SIU Optical Fibre Detector ~200 meters Data Links DDL DIU P 2 Access shaft RORC LDC DDL hardware, DATE training Front. End Digital Crate/Computer 2

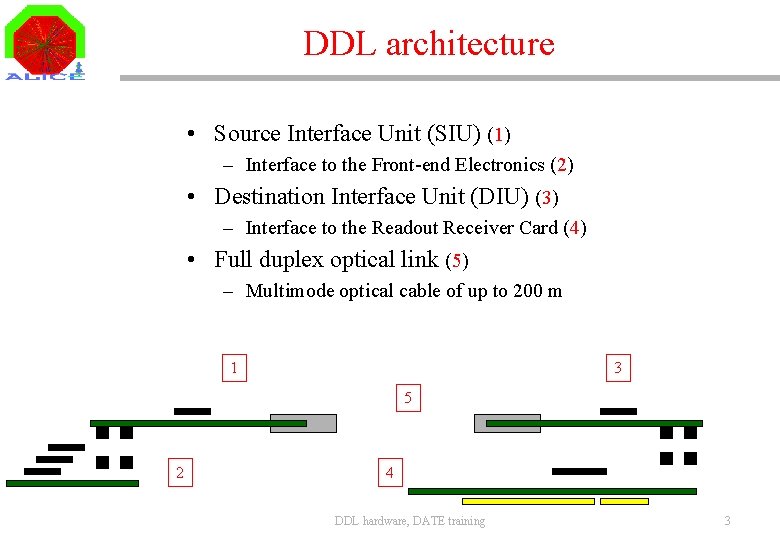

DDL architecture • Source Interface Unit (SIU) (1) – Interface to the Front-end Electronics (2) • Destination Interface Unit (DIU) (3) – Interface to the Readout Receiver Card (4) • Full duplex optical link (5) – Multimode optical cable of up to 200 m 1 3 5 2 4 DDL hardware, DATE training 3

DDL hardware, DATE training 4

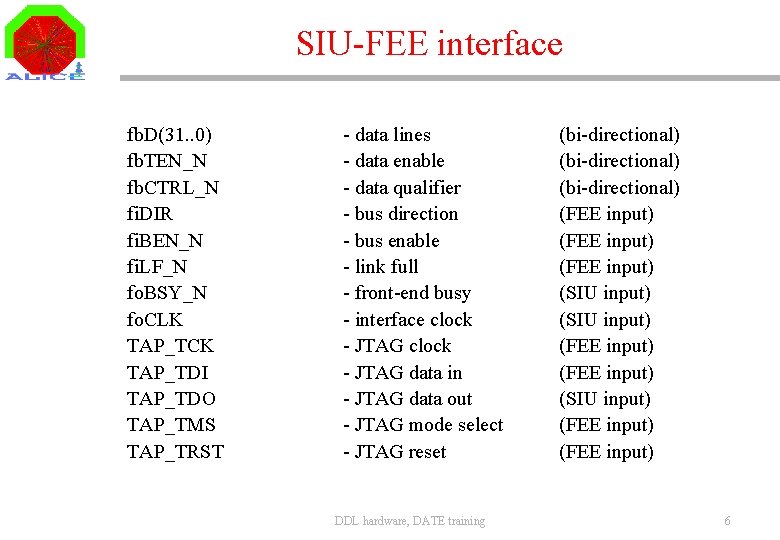

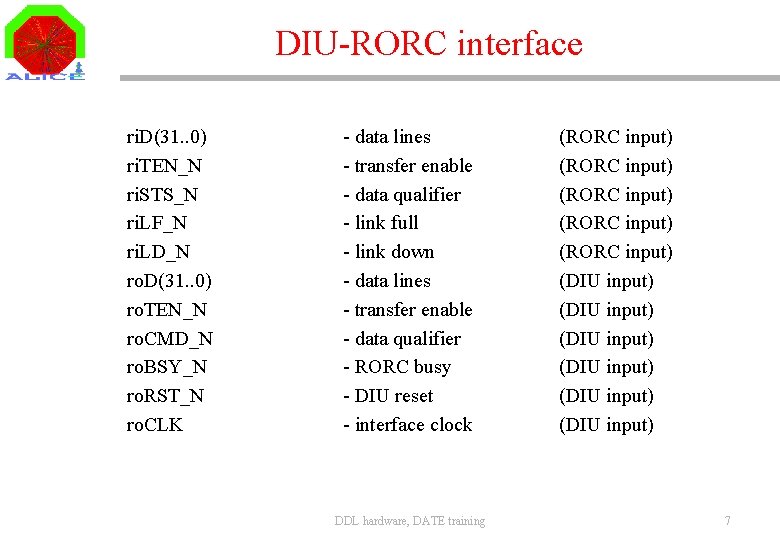

DDL interfaces • SIU-FEE interface – – – 3. 3 V (LVTTL) interface 32 -bit wide half-duplex data bus (bi-directional bus) Bi-directional flow control User defined clock (synchronous interface) JTAG interface • DIU-RORC interface – – 3. 3 V (LVTTL) interface 32 -bit wide full-duplex data bus Bi-directional flow control User defined clock (synchronous interface) DDL hardware, DATE training 5

SIU-FEE interface fb. D(31. . 0) fb. TEN_N fb. CTRL_N fi. DIR fi. BEN_N fi. LF_N fo. BSY_N fo. CLK TAP_TCK TAP_TDI TAP_TDO TAP_TMS TAP_TRST - data lines - data enable - data qualifier - bus direction - bus enable - link full - front-end busy - interface clock - JTAG data in - JTAG data out - JTAG mode select - JTAG reset DDL hardware, DATE training (bi-directional) (FEE input) (SIU input) (FEE input) 6

DIU-RORC interface ri. D(31. . 0) ri. TEN_N ri. STS_N ri. LF_N ri. LD_N ro. D(31. . 0) ro. TEN_N ro. CMD_N ro. BSY_N ro. RST_N ro. CLK - data lines - transfer enable - data qualifier - link full - link down - data lines - transfer enable - data qualifier - RORC busy - DIU reset - interface clock DDL hardware, DATE training (RORC input) (RORC input) (DIU input) (DIU input) 7

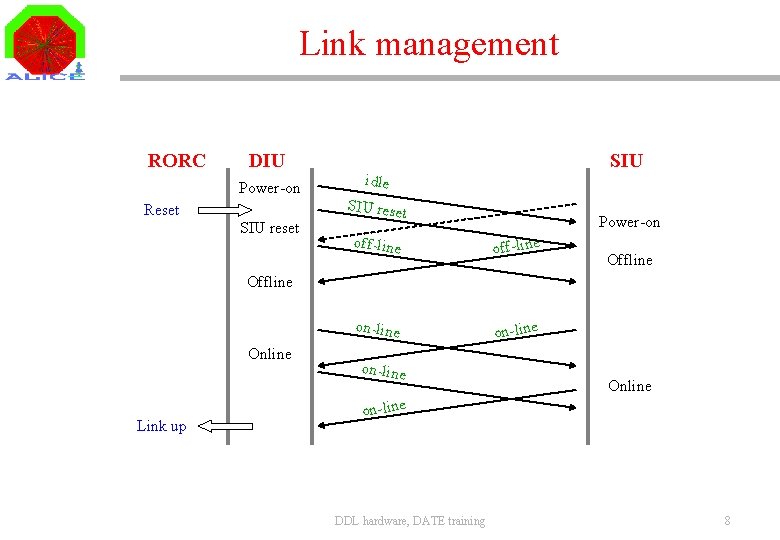

Link management RORC DIU Power-on Reset SIU reset SIU idle SIU reset Power-on off-line on-line Offline Online Link up on-line Online on-line DDL hardware, DATE training 8

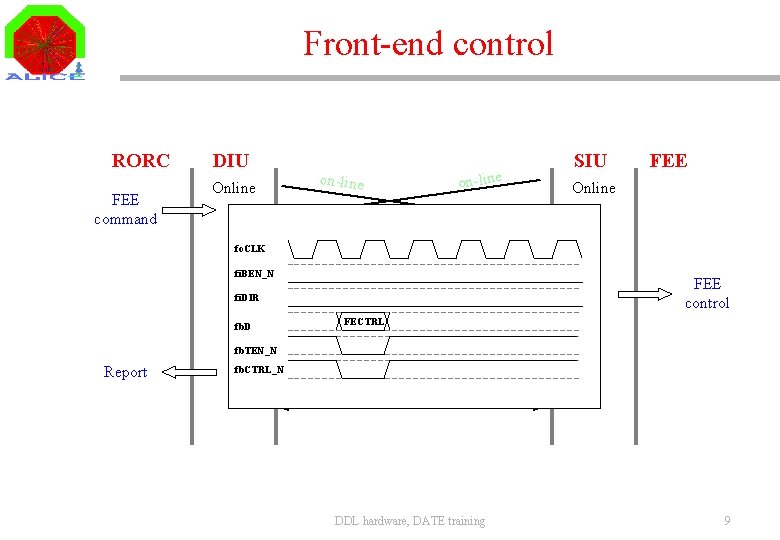

Front-end control RORC FEE command DIU Online fo. CLK fi. BEN_N on-line FEE Online FECTRL idle FEE control fi. DIR fb. D SIU FECTRL CTSTW fb. TEN_N Report fb. CTRL_N on-line DDL hardware, DATE training 9

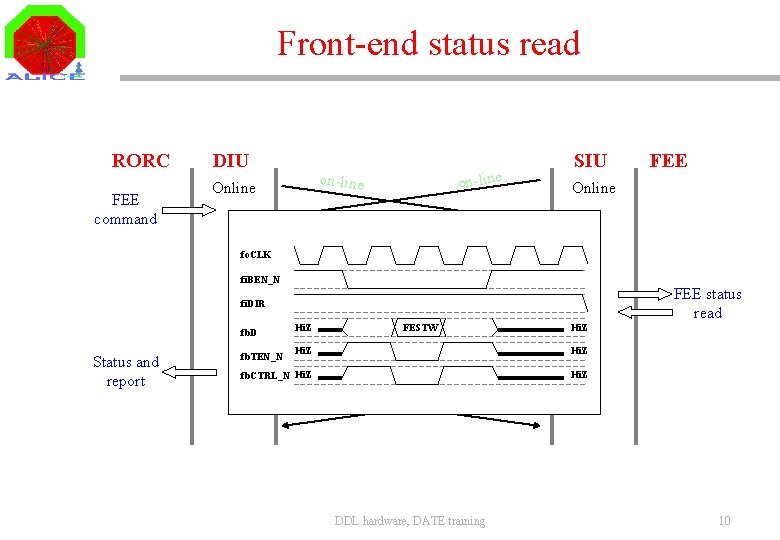

Front-end status read RORC FEE command DIU fo. CLK on-line Online SIU Online FECTRL on-line fi. BEN_N FEE status read fi. DIR fb. D Status and report fb. TEN_N FEE Hi. Z FESTRD Hi. Z fb. CTRL_N Hi. Z on-line FESTW CTSTW on-line DDL hardware, DATE training Hi. Z 10

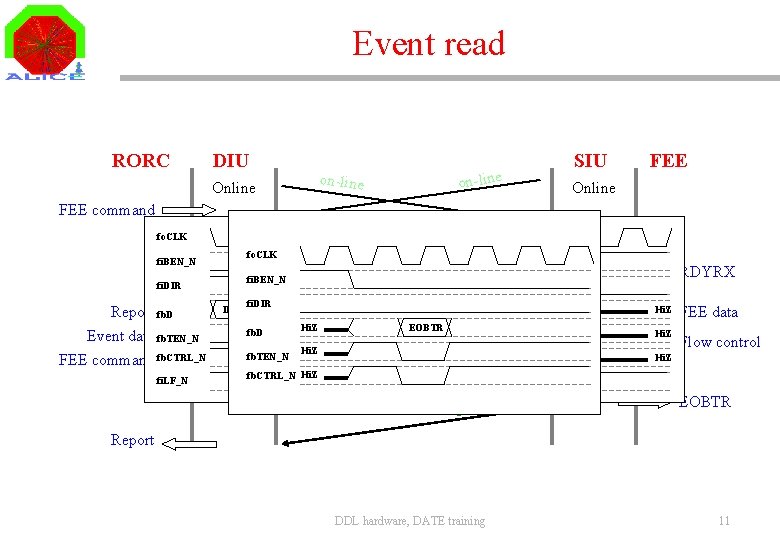

Event read RORC DIU on-line Online SIU FEE Online FEE command RDYRX fo. CLK fi. BEN_N fi. DIR Report fb. D Event data fb. TEN_N FEE command fb. CTRL_N fi. LF_N fi. DIR Hi. ZDn-1 Dn Hi. Z fb. D D 0 Hi. Z FESTW D 1 RDYRX D 2 CTSTW ks a bl 16 occycles datmin. EOBTR RDYRX D 4 Hi. Z fb. CTRL_N Hi. Z fb. TEN_N EOBTR CTSTW D 5 D 0 Hi. Z FEE data Hi. Z Flow control Hi. Z EOBTR Report DDL hardware, DATE training 11

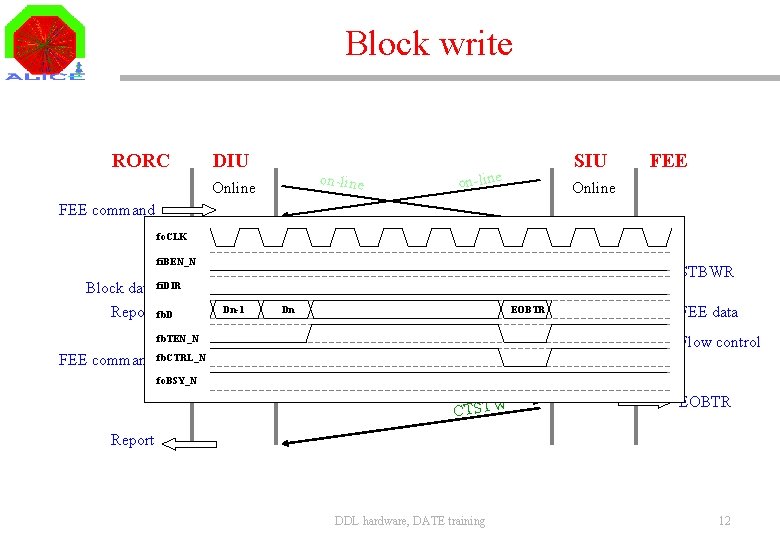

Block write RORC DIU on-line Online SIU FEE Online FEE command STBWR fo. CLK fi. BEN_N Block data Report fb. D k STBWR Dn-1 Dn D 0 D 1 D 2 EOBTR fo. BSY_N D 4 D 5 FEE data Flow control fb. TEN_N FEE command fb. CTRL_N STBWR CTSTW data bloc fi. DIR EOBTR CTSTW EOBTR Report DDL hardware, DATE training 12

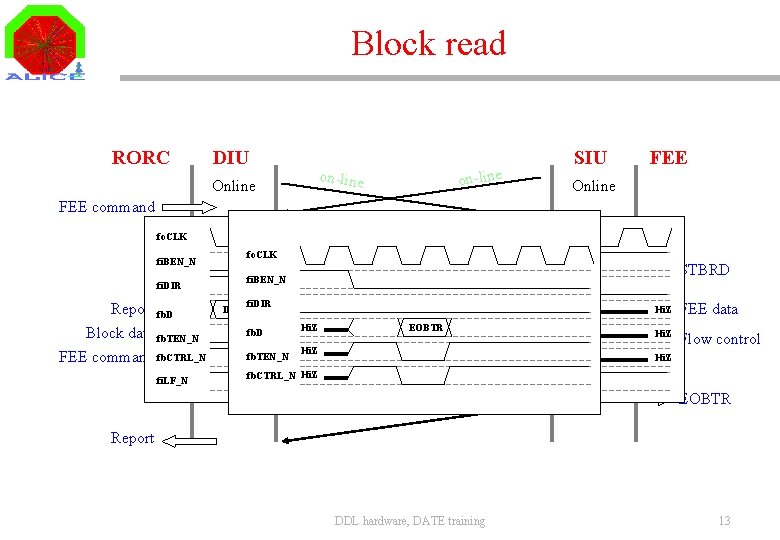

Block read RORC DIU on-line Online SIU FEE Online FEE command STBRD fo. CLK fi. BEN_N fi. DIR Report fb. D Block data fb. TEN_N FEE command fb. CTRL_N fi. LF_N fi. DIR Hi. ZDn-1 Dn Hi. Z fb. D D 0 Hi. Z FESTW D 1 STBRD D 2 CTSTW k data bloc EOBTR STBRD D 4 Hi. Z fb. CTRL_N Hi. Z fb. TEN_N EOBTR CTSTW D 5 Hi. Z FEE data Hi. Z Flow control Hi. Z EOBTR Report DDL hardware, DATE training 13

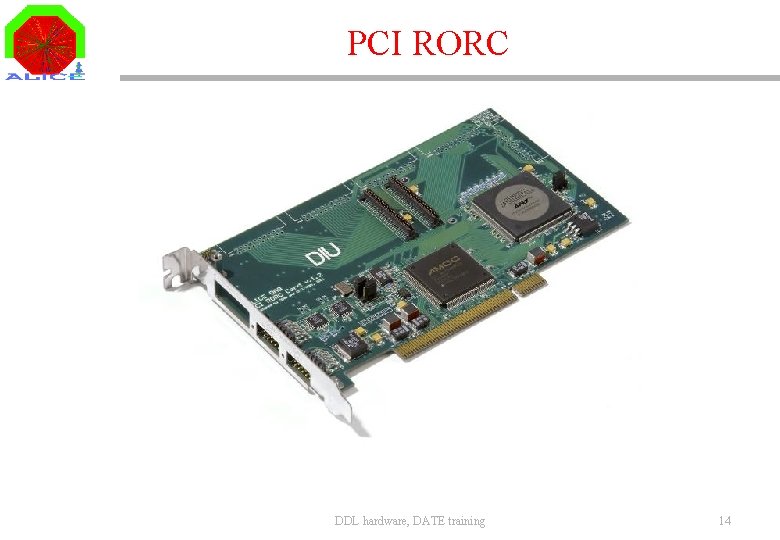

PCI RORC DDL hardware, DATE training 14

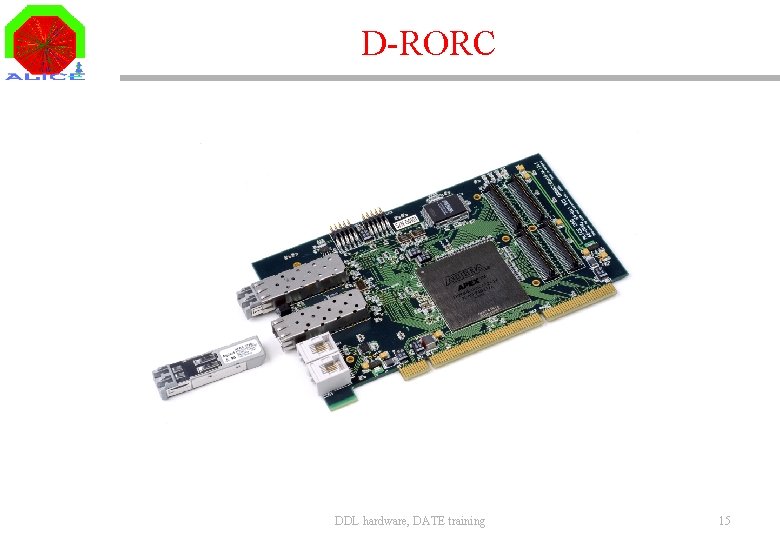

D-RORC DDL hardware, DATE training 15

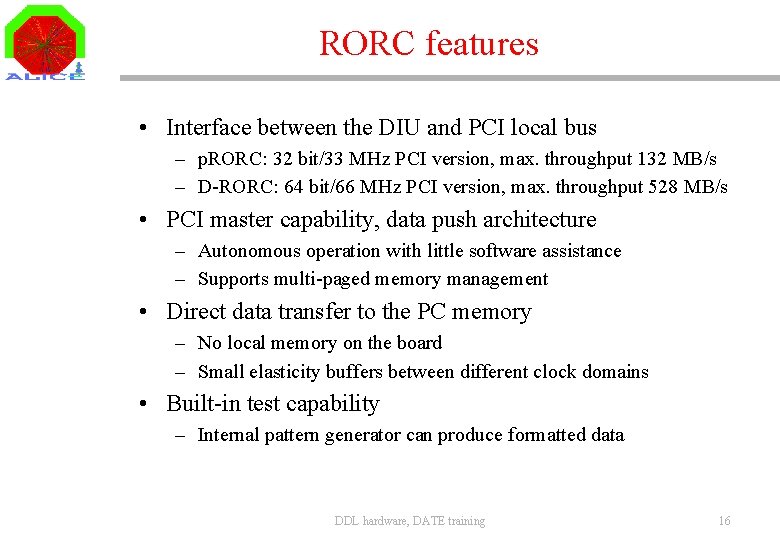

RORC features • Interface between the DIU and PCI local bus – p. RORC: 32 bit/33 MHz PCI version, max. throughput 132 MB/s – D-RORC: 64 bit/66 MHz PCI version, max. throughput 528 MB/s • PCI master capability, data push architecture – Autonomous operation with little software assistance – Supports multi-paged memory management • Direct data transfer to the PC memory – No local memory on the board – Small elasticity buffers between different clock domains • Built-in test capability – Internal pattern generator can produce formatted data DDL hardware, DATE training 16

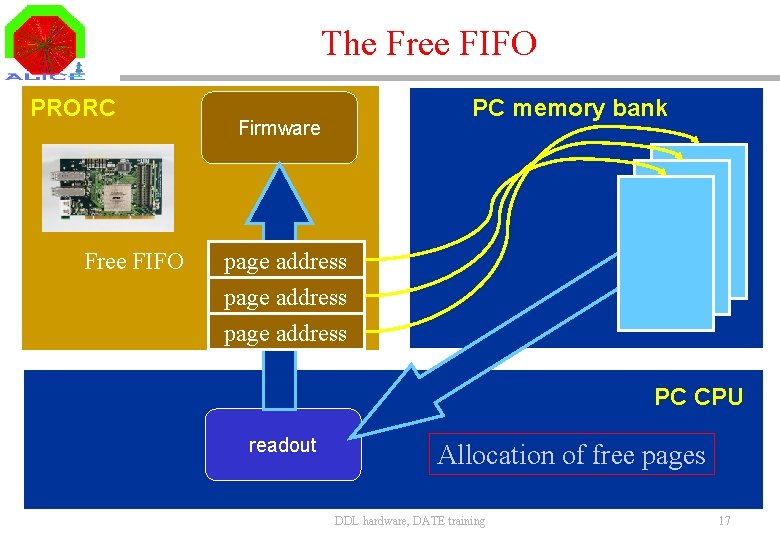

The Free FIFO PRORC Free FIFO PC memory bank Firmware page address PC CPU readout Allocation of free pages DDL hardware, DATE training 17

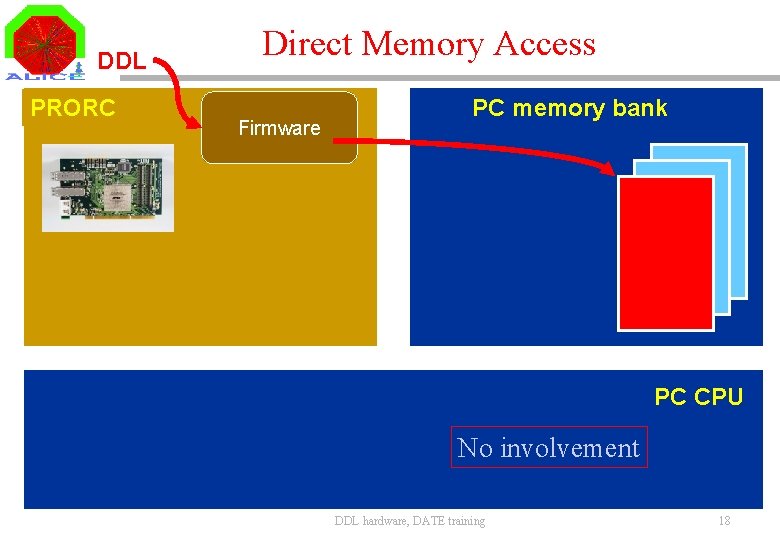

DDL PRORC Direct Memory Access Firmware PC memory bank PC CPU No involvement DDL hardware, DATE training 18

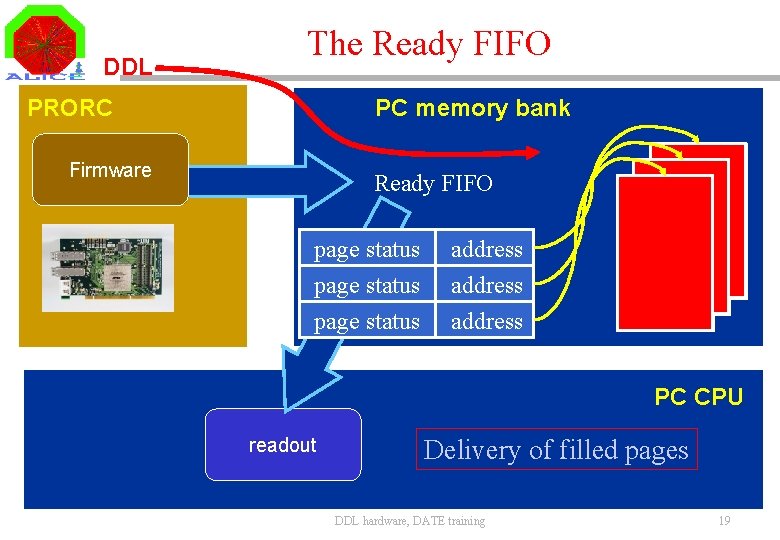

DDL The Ready FIFO PRORC PC memory bank Firmware Ready FIFO page status address PC CPU readout Delivery of filled pages DDL hardware, DATE training 19

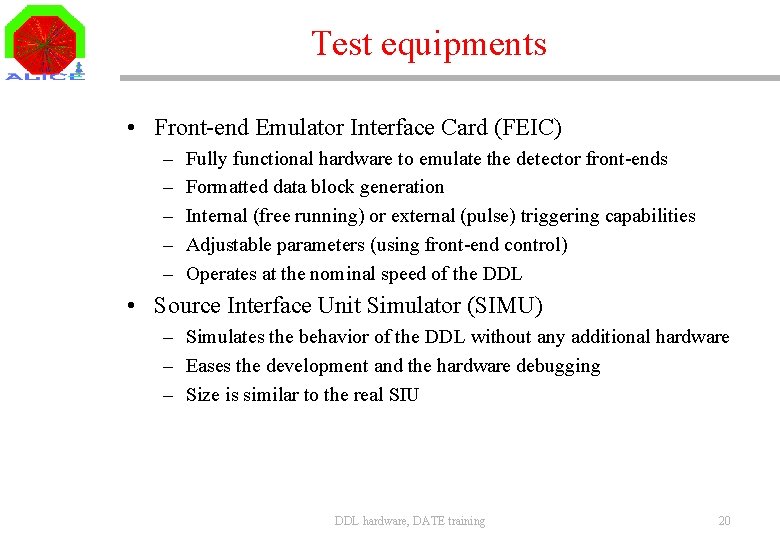

Test equipments • Front-end Emulator Interface Card (FEIC) – – – Fully functional hardware to emulate the detector front-ends Formatted data block generation Internal (free running) or external (pulse) triggering capabilities Adjustable parameters (using front-end control) Operates at the nominal speed of the DDL • Source Interface Unit Simulator (SIMU) – Simulates the behavior of the DDL without any additional hardware – Eases the development and the hardware debugging – Size is similar to the real SIU DDL hardware, DATE training 20

- Slides: 20