Designing SystemsOnaChip Impact on Engineering Research Education ICT

![Filling the gap between systems and IP UML x[i]= fft(4 py[k]). . . c. Filling the gap between systems and IP UML x[i]= fft(4 py[k]). . . c.](https://slidetodoc.com/presentation_image_h2/7fef544560f44e4199337e7f804674b7/image-10.jpg)

- Slides: 35

Designing Systems-On-a-Chip : Impact on Engineering Research & Education ICT EE CE Hugo De Man K. U. Leuven / IMEC Belgium deman@imec. be VTS-Aix-EMS’ 99

Points. . . 1. Ability to exploit DS technology will depend critically on availability of adequately skilled So. C architects 2. The need to invest in training and education of these So. C architects is grossly underestimated 3. Education in design of So. C is to be based on new organization of R&D in system design © H. De Man EMS’ 99 2

Outline 1. Paradigm shifts 2. Require new skills 3. How to create these skills ? © H. De Man EMS’ 99 3

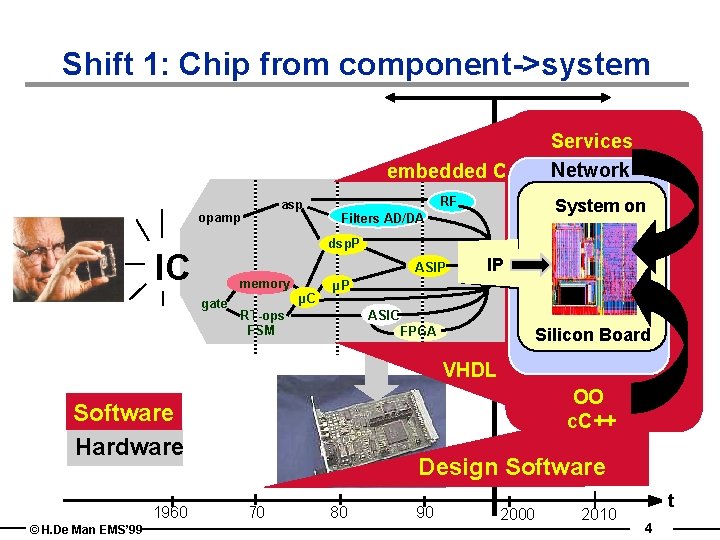

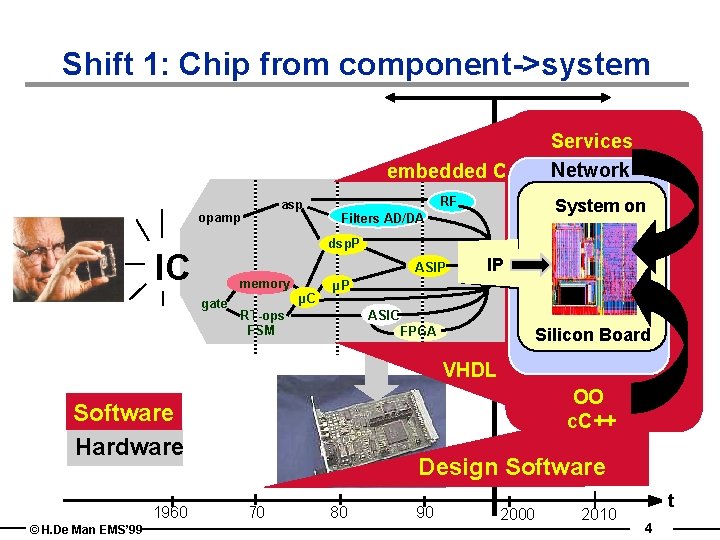

Shift 1: Chip from component->system Services Network embedded C asp opamp RF System on Filters AD/DA dsp. P IC ASIP memory gate µC IP µP RT-ops FSM ASIC FPGA Silicon Board VHDL OO c. C++ Software Hardware 1960 © H. De Man EMS’ 99 Design Software 70 80 90 2000 2010 t 4

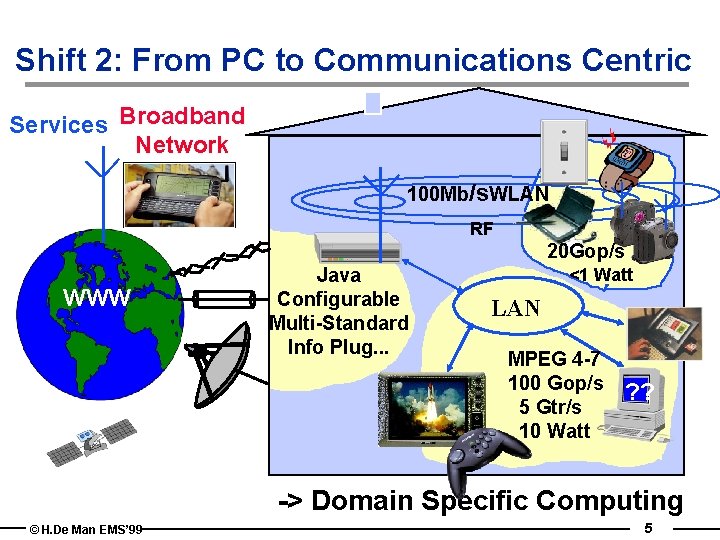

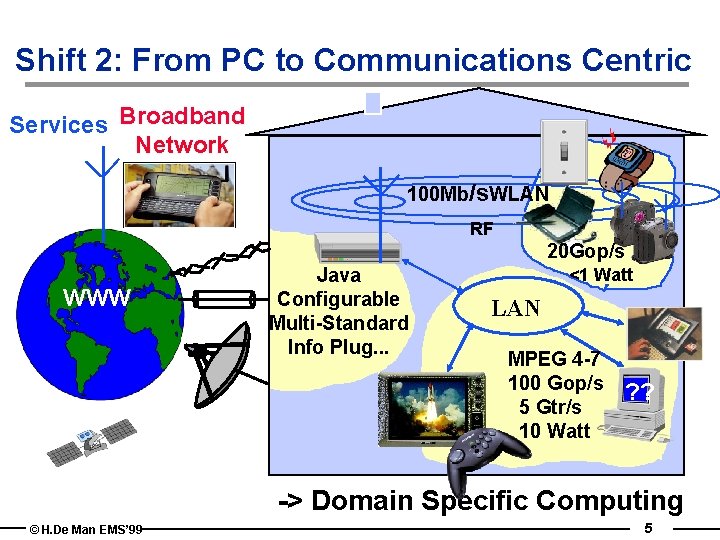

Shift 2: From PC to Communications Centric Services Broadband Network 100 Mb/s. WLAN RF 20 Gop/s WWW Java Configurable Multi-Standard Info Plug. . . <1 Watt LAN MPEG 4 -7 100 Gop/s 5 Gtr/s 10 Watt ? ? -> Domain Specific Computing © H. De Man EMS’ 99 5

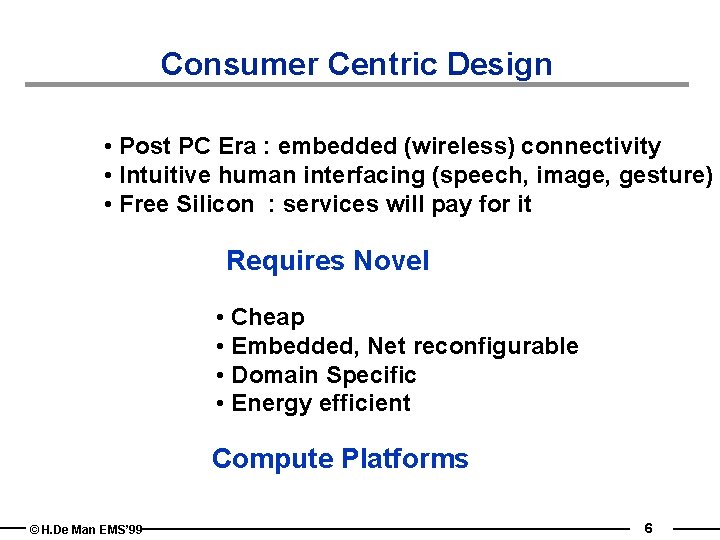

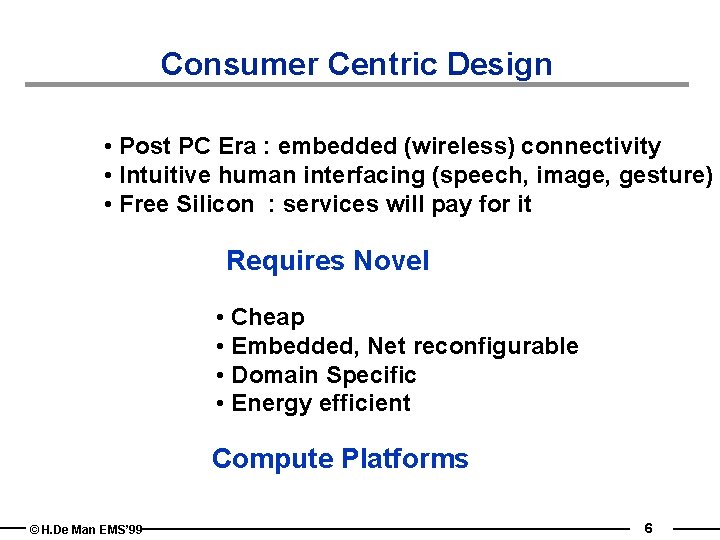

Consumer Centric Design • Post PC Era : embedded (wireless) connectivity • Intuitive human interfacing (speech, image, gesture) • Free Silicon : services will pay for it Requires Novel • Cheap • Embedded, Net reconfigurable • Domain Specific • Energy efficient Compute Platforms © H. De Man EMS’ 99 6

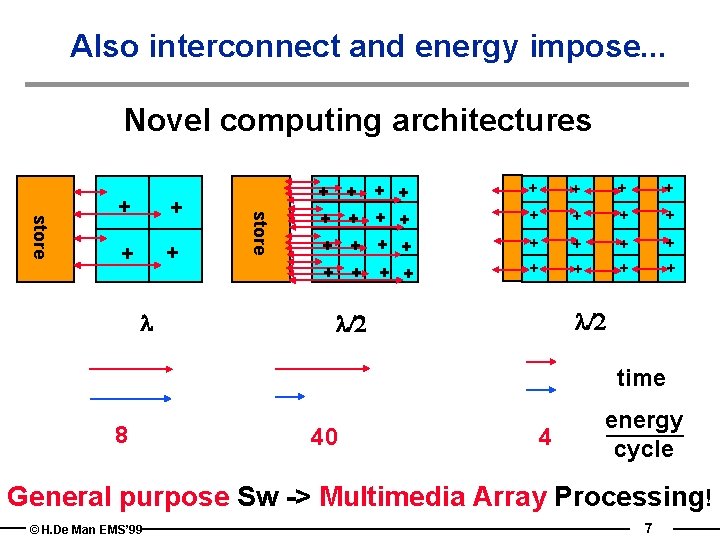

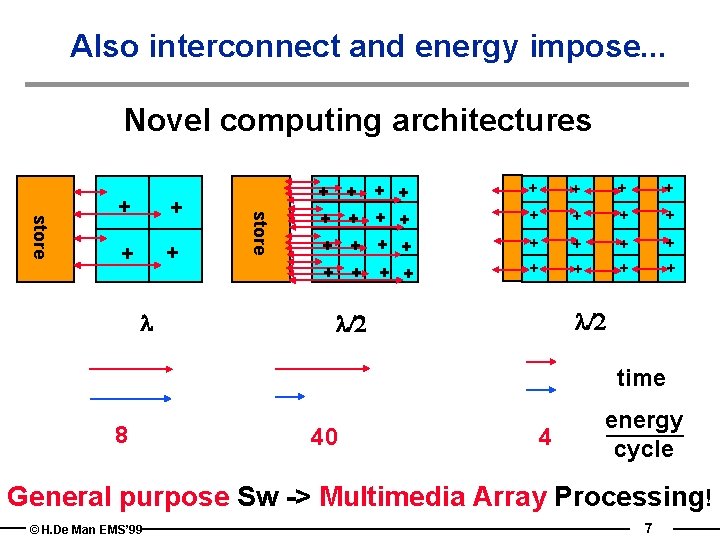

Also interconnect and energy impose. . . Novel computing architectures + + + l store + + + + + + + + + l/2 time 8 40 4 energy cycle General purpose Sw -> Multimedia Array Processing! © H. De Man EMS’ 99 7

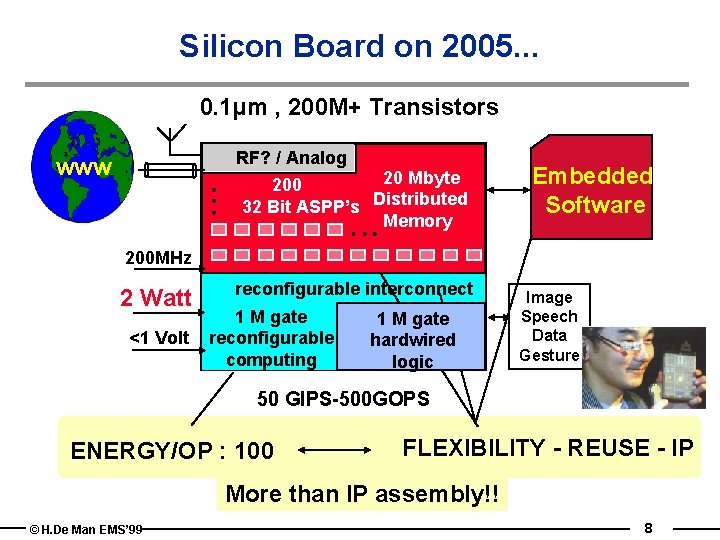

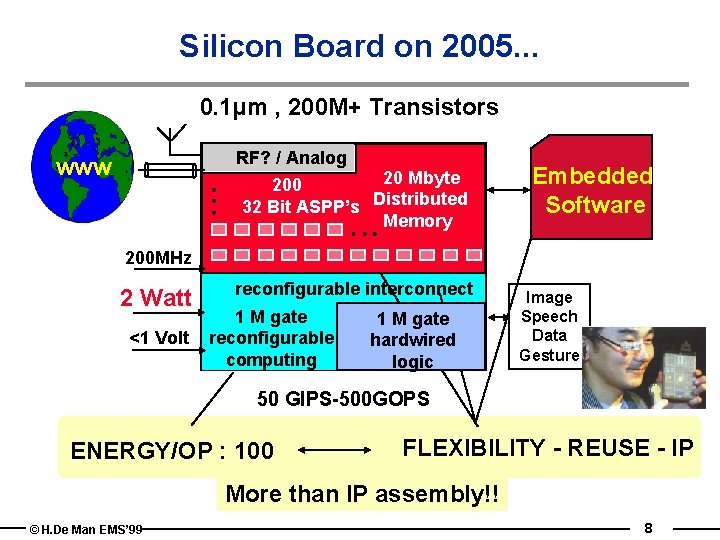

Silicon Board on 2005. . . 0. 1µm , 200 M+ Transistors RF? / Analog 20 Mbyte 200 32 Bit ASPP’s Distributed Memory www Embedded Software 200 MHz 2 Watt <1 Volt reconfigurable interconnect 1 M gate reconfigurable computing 1 M gate hardwired logic Image Speech Data Gesture 50 GIPS-500 GOPS ENERGY/OP : 100 FLEXIBILITY - REUSE - IP More than IP assembly!! © H. De Man EMS’ 99 8

Outline 1. Paradigm shifts 2. Require new skills 3. How to create these skills ? © H. De Man EMS’ 99 9

![Filling the gap between systems and IP UML xi fft4 pyk c Filling the gap between systems and IP UML x[i]= fft(4 py[k]). . . c.](https://slidetodoc.com/presentation_image_h2/7fef544560f44e4199337e7f804674b7/image-10.jpg)

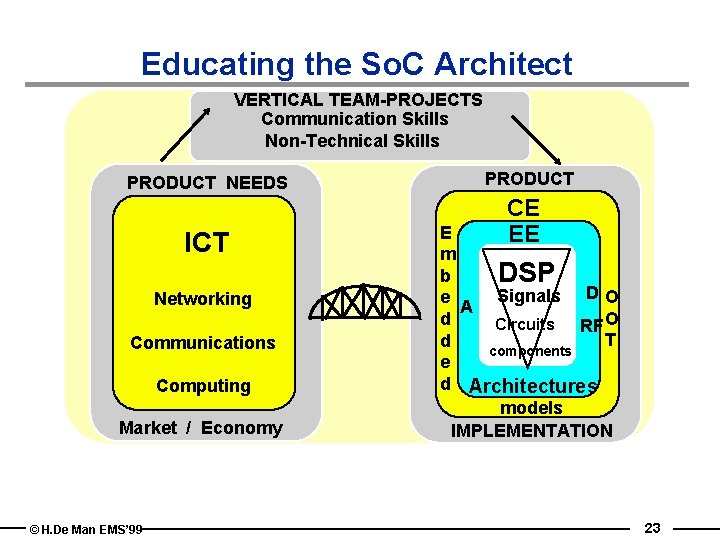

Filling the gap between systems and IP UML x[i]= fft(4 py[k]). . . c. C++, JAVA System specs -> 7 th Heaven of software People MATLAB S 200 M+ transistors So. C Architecture A CAE, IP, VSIA DS Hell of Physics Global System Thinking Concurrent Engineering Team & Communication Skills © H. De Man EMS’ 99 VHDL 1 V, 1 Watt 10

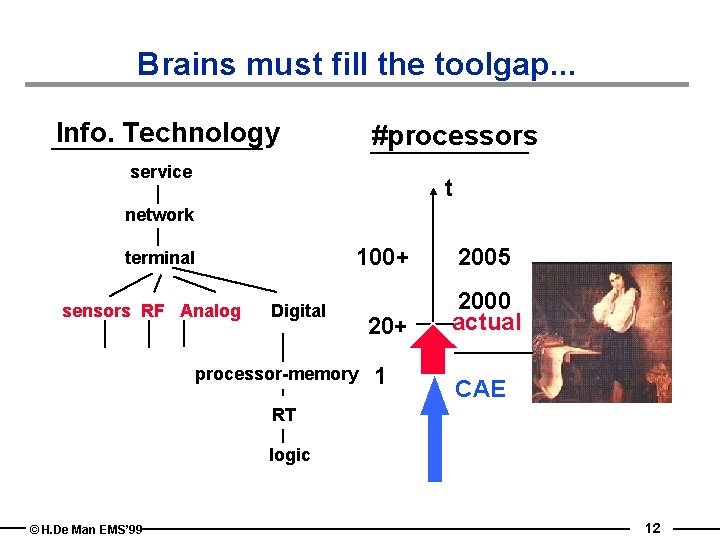

Key challenge. . . Create Brains able to. . . Rennequin Samuel • Map multi-standard wired-wireless communication services into flexible silicon board architectures • Taking wiring and energy constraints into account Methods and Tools will follow later. . . © H. De Man EMS’ 99 11

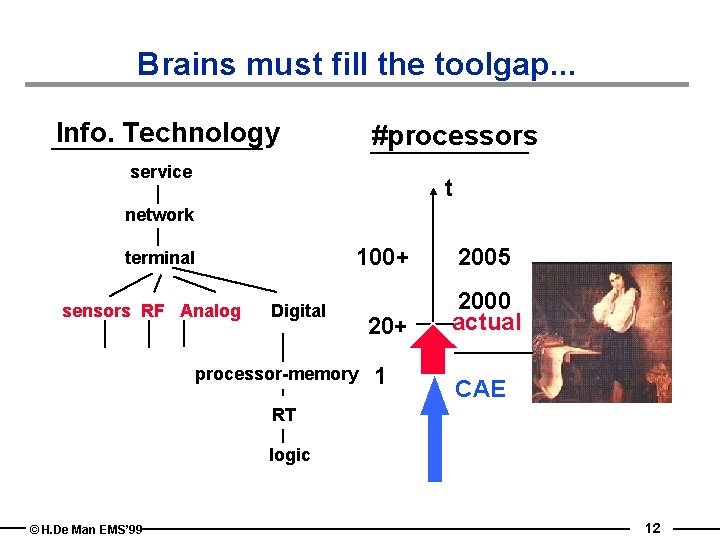

Brains must fill the toolgap. . . Info. Technology #processors service t network terminal sensors RF Analog 100+ 2005 20+ 2000 actual Digital processor-memory 1 CAE RT logic © H. De Man EMS’ 99 12

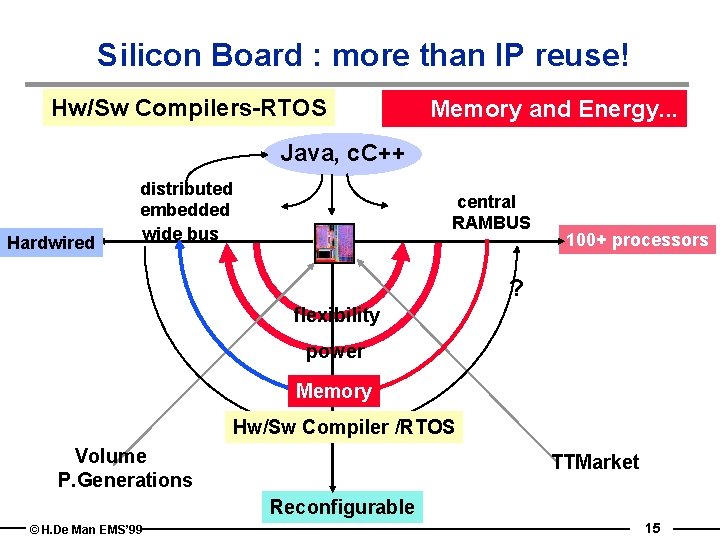

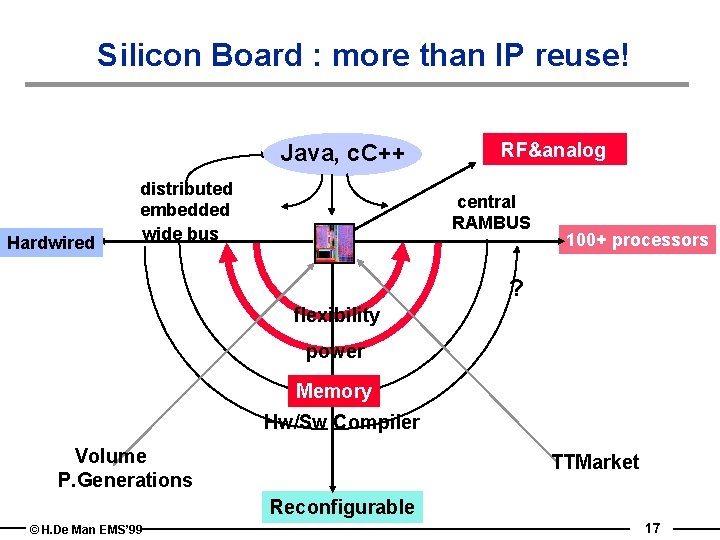

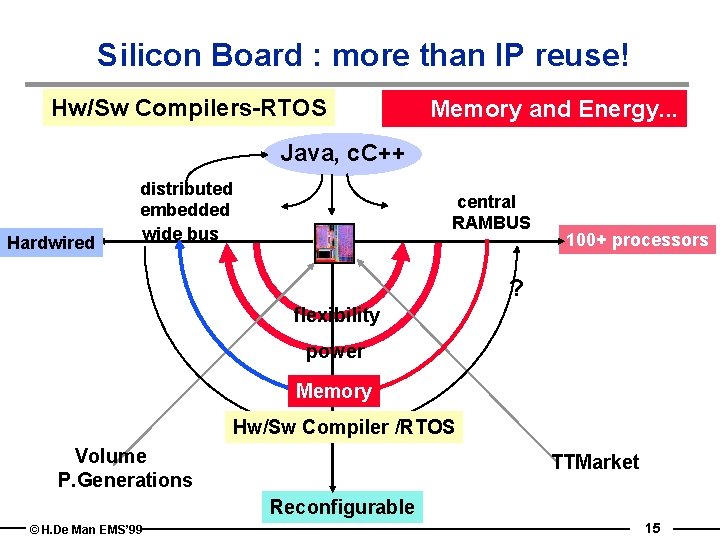

Silicon Board : more than IP reuse! Create radically new architectures for 100 GOPS+ systems within energy, memory and design budget. . . Java, c. C++ Hardwired m. W W 100+ processors flexibility power Volume P. Generations TTMarket Reconfigurable © H. De Man EMS’ 99 13

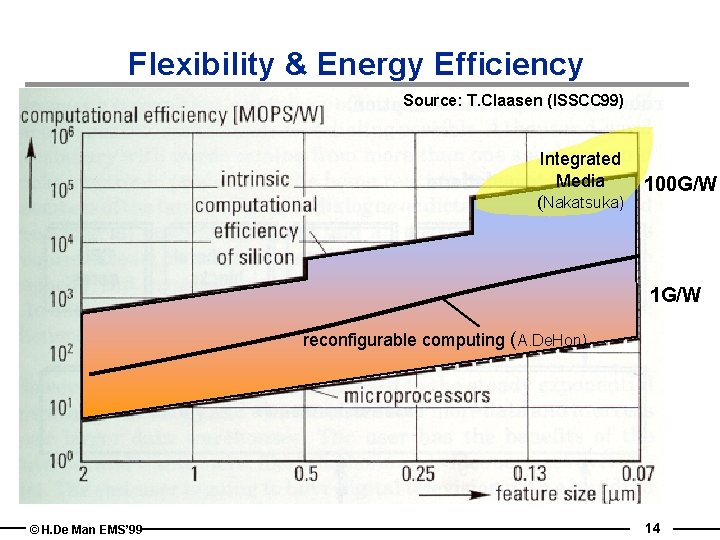

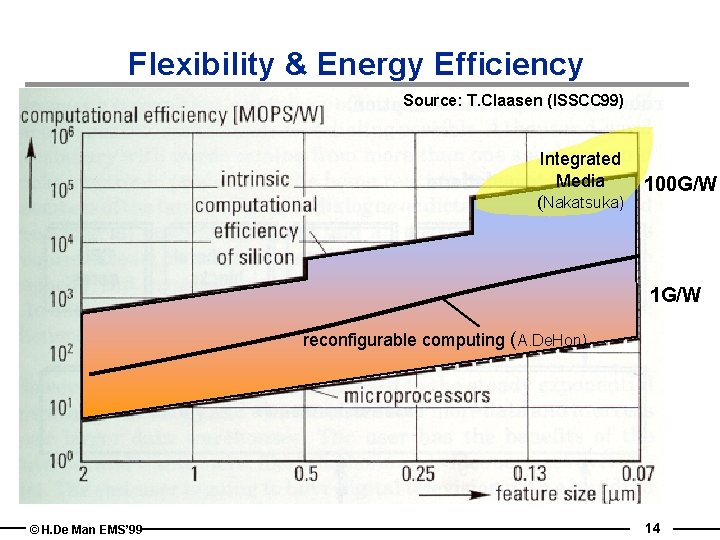

Flexibility & Energy Efficiency Source: T. Claasen (ISSCC 99) Integrated Media (Nakatsuka) 100 G/W 1 G/W reconfigurable computing (A. De. Hon) © H. De Man EMS’ 99 14

Silicon Board : more than IP reuse! Hw/Sw Compilers-RTOS Memory and Energy. . . Java, c. C++ Hardwired distributed embedded wide bus central RAMBUS 100+ processors ? flexibility power Memory Hw/Sw Compiler /RTOS Volume P. Generations TTMarket Reconfigurable © H. De Man EMS’ 99 15

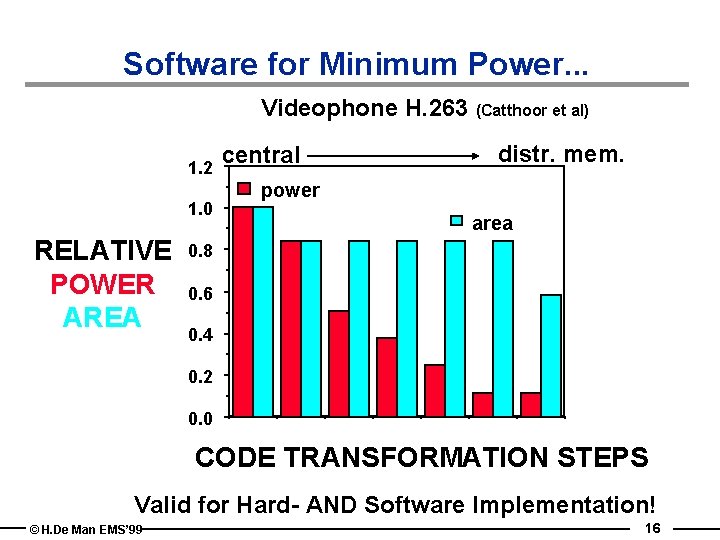

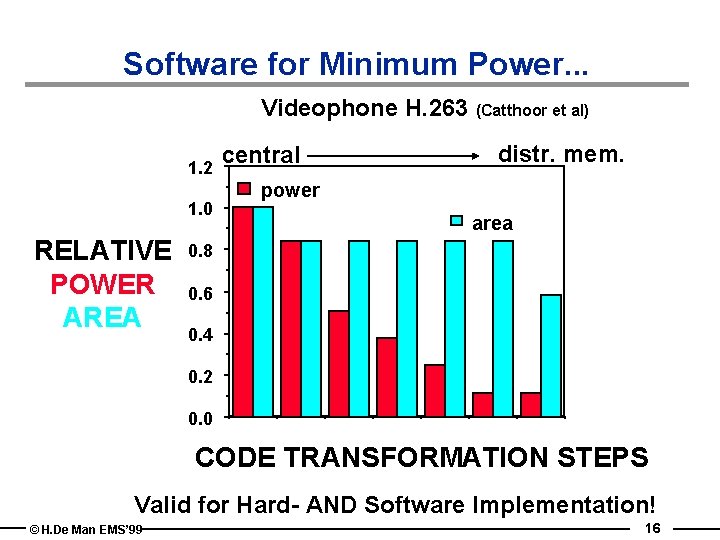

Software for Minimum Power. . . Videophone H. 263 (Catthoor et al) 1. 2 1. 0 RELATIVE POWER AREA central distr. mem. power area 0. 8 0. 6 0. 4 0. 2 0. 0 CODE TRANSFORMATION STEPS Valid for Hard- AND Software Implementation! © H. De Man EMS’ 99 16

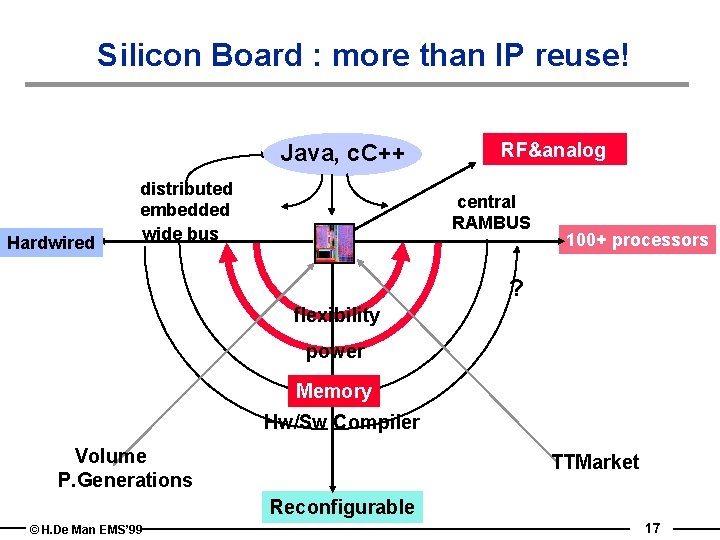

Silicon Board : more than IP reuse! Java, c. C++ Hardwired distributed embedded wide bus RF&analog central RAMBUS 100+ processors ? flexibility power Memory Hw/Sw Compiler Volume P. Generations TTMarket Reconfigurable © H. De Man EMS’ 99 17

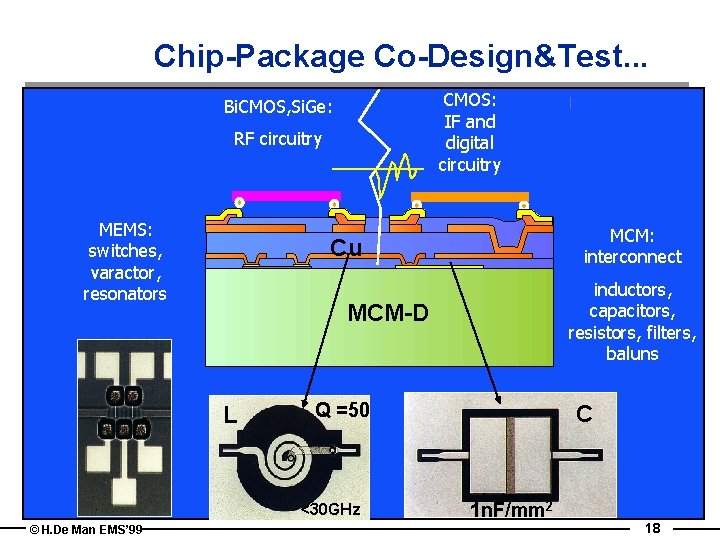

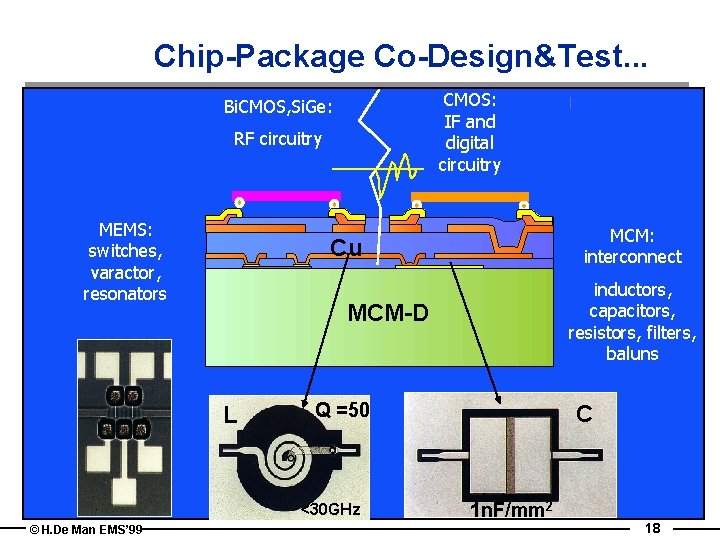

Chip-Package Co-Design&Test. . . CMOS: IF and digital circuitry Bi. CMOS, Si. Ge: RF circuitry MEMS: switches, varactor, resonators Cu inductors, capacitors, resistors, filters, baluns MCM-D L Q =50 <30 GHz © H. De Man EMS’ 99 MCM: interconnect C 1 n. F/mm 2 18

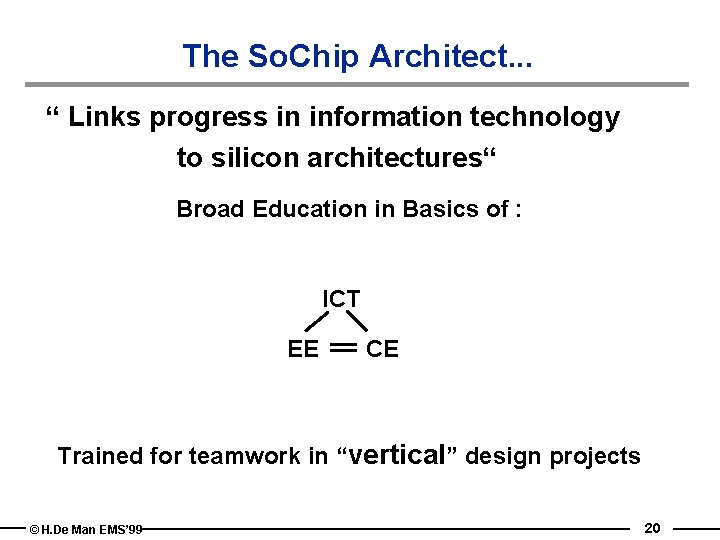

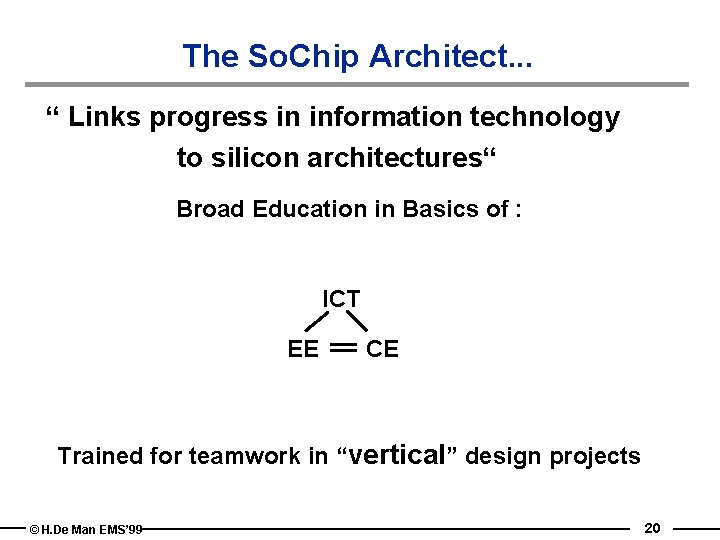

Summary Sofar. . . • Chip + Package becomes system • Software all over the place • Heterogeneous Architectural Design Space • New Trade-offs - Energy- software-RTOS- hardware- A / D - Chip-Package Co. Design and Test. . . WHAT KIND OF ENGINEER NEEDED ? © H. De Man EMS’ 99 19

The So. Chip Architect. . . “ Links progress in information technology to silicon architectures“ Broad Education in Basics of : ICT EE CE Trained for teamwork in “vertical” design projects © H. De Man EMS’ 99 20

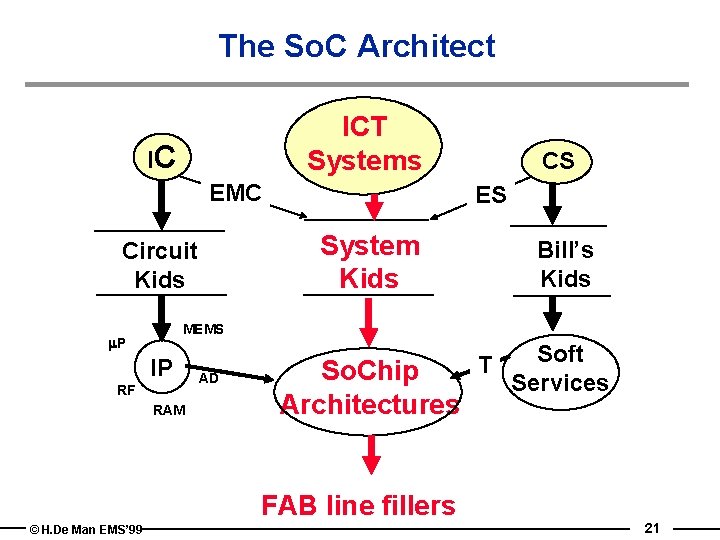

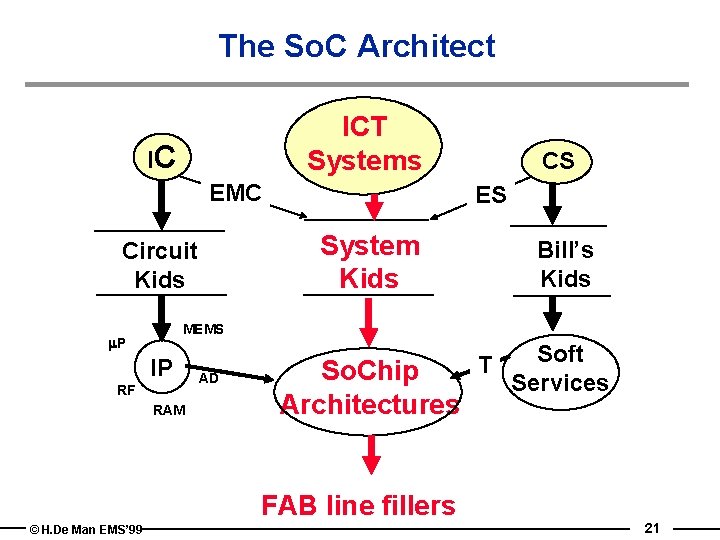

The So. C Architect ICT Systems IC EMC ES System Kids Circuit Kids Bill’s Kids MEMS m. P IP RF RAM AD So. Chip Architectures FAB line fillers © H. De Man EMS’ 99 CS T Soft Services 21

Outline 1. Paradigm shifts 2. Require new skills 3. How to create these skills ? © H. De Man EMS’ 99 22

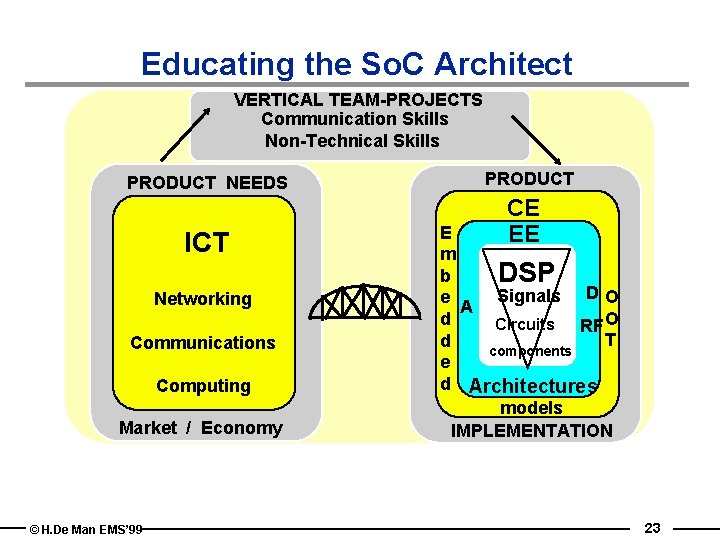

Educating the So. C Architect VERTICAL TEAM-PROJECTS Communication Skills Non-Technical Skills PRODUCT NEEDS ICT Networking Communications Computing Market / Economy © H. De Man EMS’ 99 PRODUCT CE EE E m DSP b Signals D O e A d Circuits RF O T d components e d Architectures models IMPLEMENTATION 23

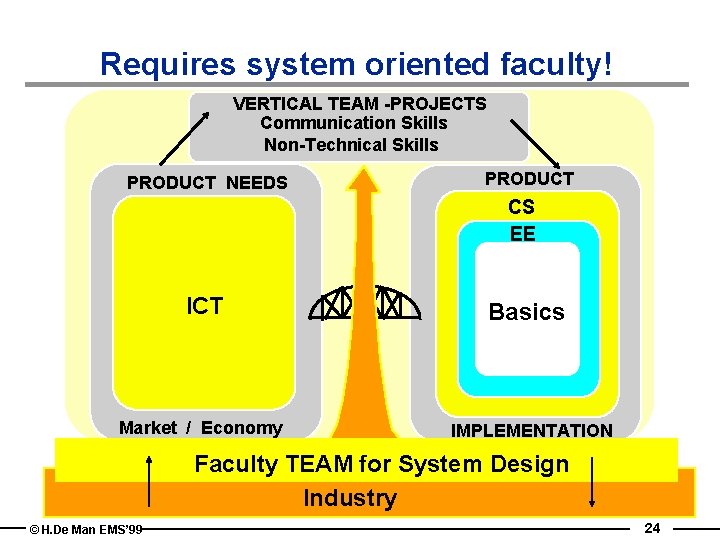

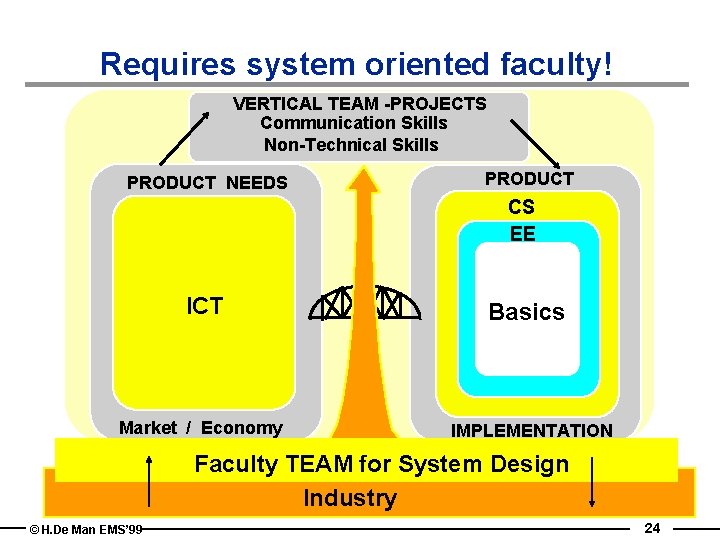

Requires system oriented faculty! VERTICAL TEAM -PROJECTS Communication Skills Non-Technical Skills PRODUCT NEEDS PRODUCT CS EE ICT Market / Economy Basics IMPLEMENTATION Faculty TEAM for System Design Industry © H. De Man EMS’ 99 24

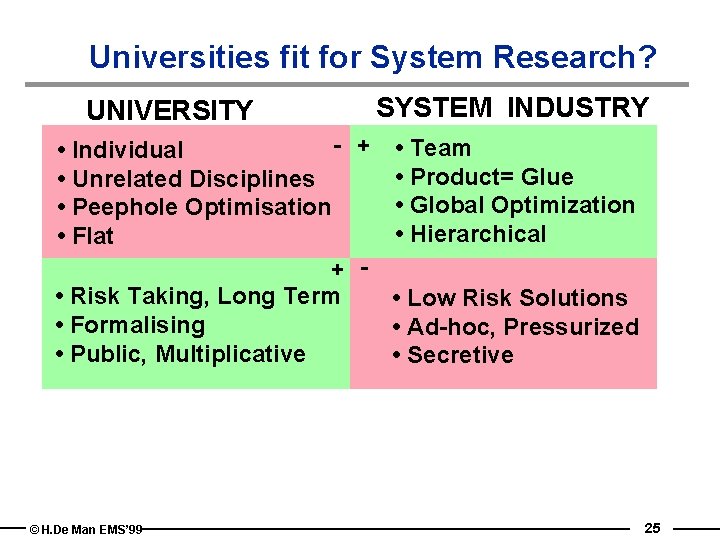

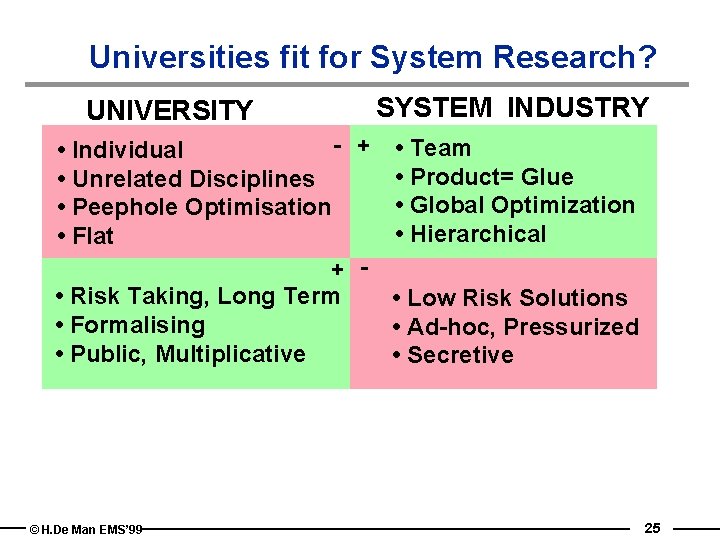

Universities fit for System Research? UNIVERSITY SYSTEM INDUSTRY - + • Team • Individual • Product= Glue • Unrelated Disciplines • Global Optimization • Peephole Optimisation • Hierarchical • Flat + • Risk Taking, Long Term • Low Risk Solutions • Formalising • Ad-hoc, Pressurized • Public, Multiplicative • Secretive © H. De Man EMS’ 99 25

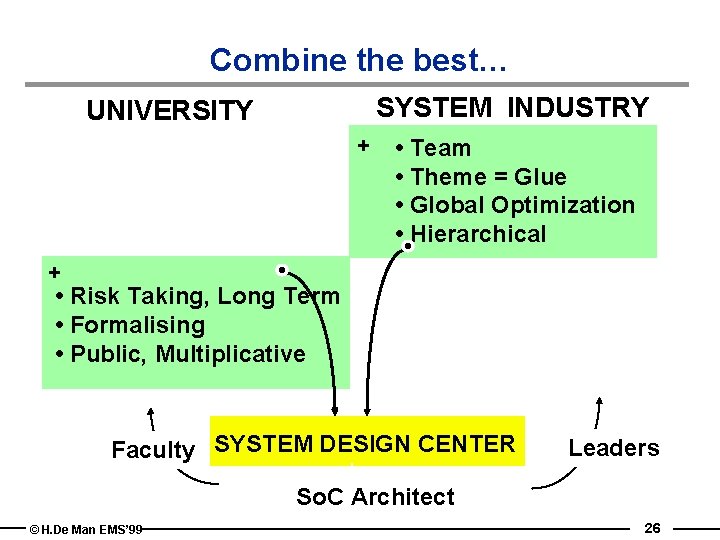

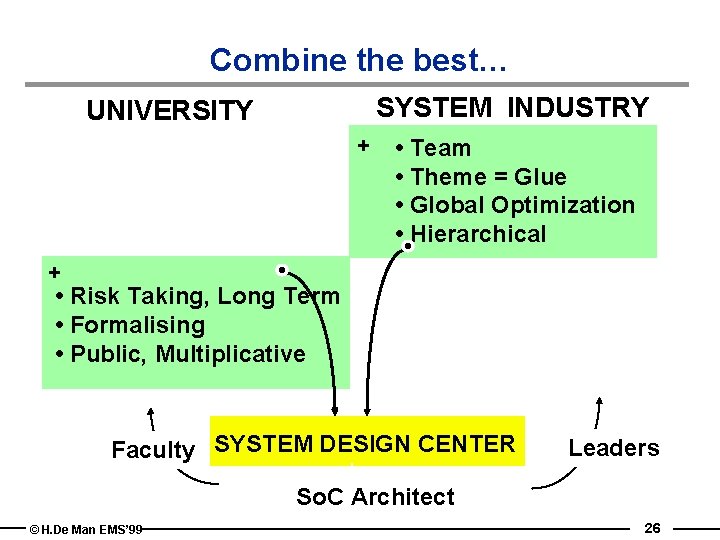

Combine the best… SYSTEM INDUSTRY UNIVERSITY + • Team • Theme = Glue • Global Optimization • Hierarchical + • Risk Taking, Long Term • Formalising • Public, Multiplicative Faculty SYSTEM DESIGN CENTER Leaders So. C Architect © H. De Man EMS’ 99 26

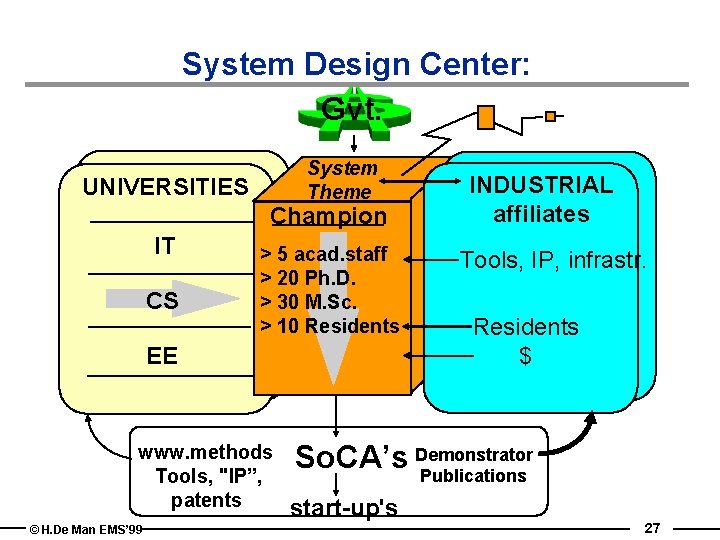

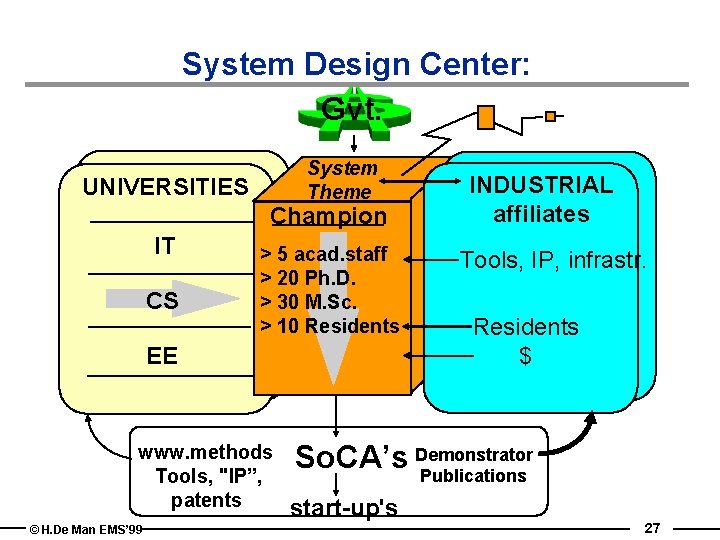

System Design Center: Gvt. System Theme UNIVERSITIES Champion IT CS > 5 acad. staff > 20 Ph. D. > 30 M. Sc. > 10 Residents EE www. methods Tools, "IP”, patents © H. De Man EMS’ 99 INDUSTRIAL affiliates Tools, IP, infrastr. Residents $ So. CA’s Demonstrator Publications start-up's 27

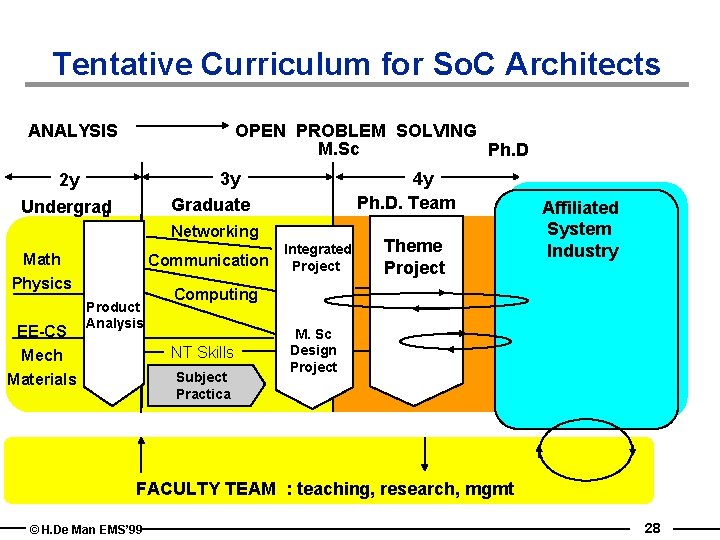

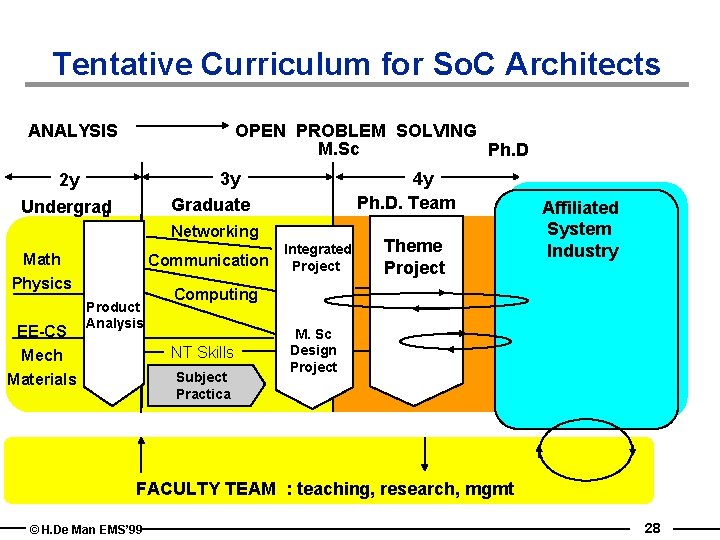

Tentative Curriculum for So. C Architects ANALYSIS OPEN PROBLEM SOLVING M. Sc Ph. D 3 y Graduate 2 y Undergrad 4 y Ph. D. Team Networking Math Physics EE-CS Mech Materials Communication Product Analysis Integrated Project Theme Project Affiliated System Industry Computing NT Skills Subject Practica M. Sc Design Project FACULTY TEAM : teaching, research, mgmt © H. De Man EMS’ 99 28

Examples • Berkeley Wireless Research Center • Broadband Access Project IMEC • Alba Project, Scotland • Yamacraw Project, Georgia • Eindhoven Embedded Systems Institute • Human Computer Interface Institute CMU • Marco, Gigascale Integration • Integrated Media Systems Center(USC). . . IMSC © H. De Man EMS’ 99 29

Advantages. . . • Delivers the right skills to ICT industry • Creates faculty and students with global system vision • Has multiplicative effect : www oriented, distributive • Encourages start up of SME’s in ICT, IP (innovation layers) © H. De Man EMS’ 99 30

Roadblocks to overcome. . . • Academic reward system (Citation Index…) • Academic inertia (kingdoms…) • Insufficient supply of brains (high school…) • Financing of training (invest in brains…) © H. De Man EMS’ 99 31

Summarizing. . . • Silicon Technology will be brain limited • In post-PC era: architectural platform = differentiator • Needed : So. C Architects linking ICT to Silicon • System Design Research -> Open System Design Centers • Linking future industrial strategy to academic teams • Breeding ground for So. CA's and their faculty • Produce product driven methodologies and tools © H. De Man EMS’ 99 32

Thank YOU ! deman@imec. be

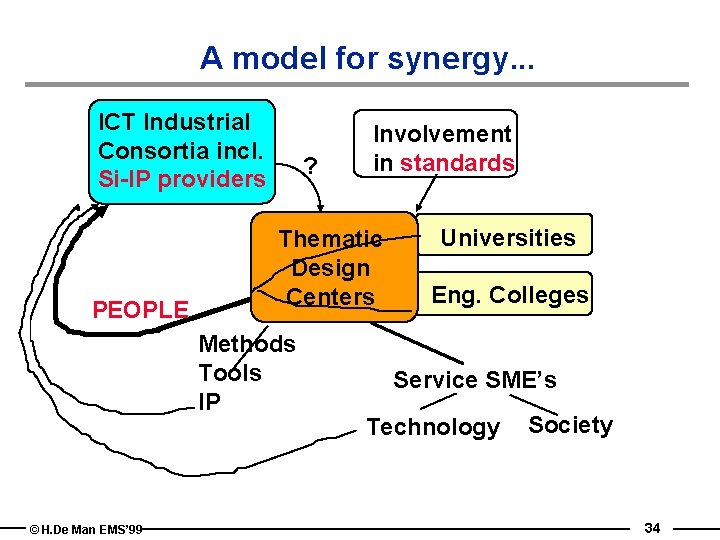

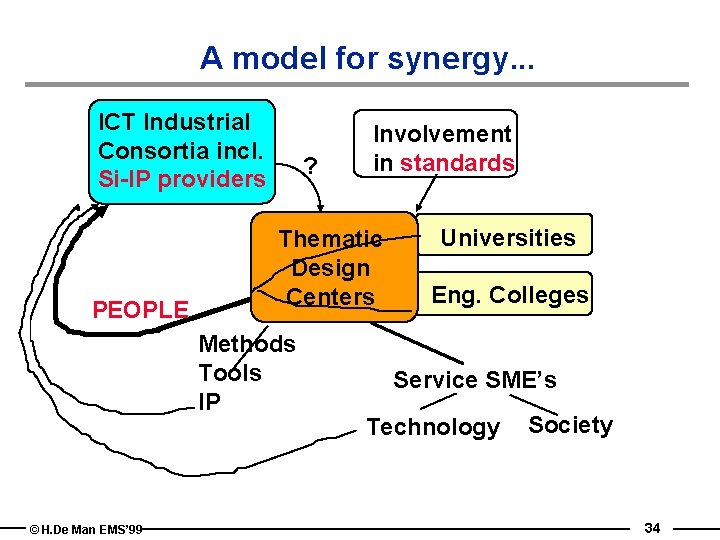

A model for synergy. . . ICT Industrial Consortia incl. Si-IP providers PEOPLE ? Thematic Design Centers Methods Tools IP © H. De Man EMS’ 99 Involvement in standards Universities Eng. Colleges Service SME’s Technology Society 34

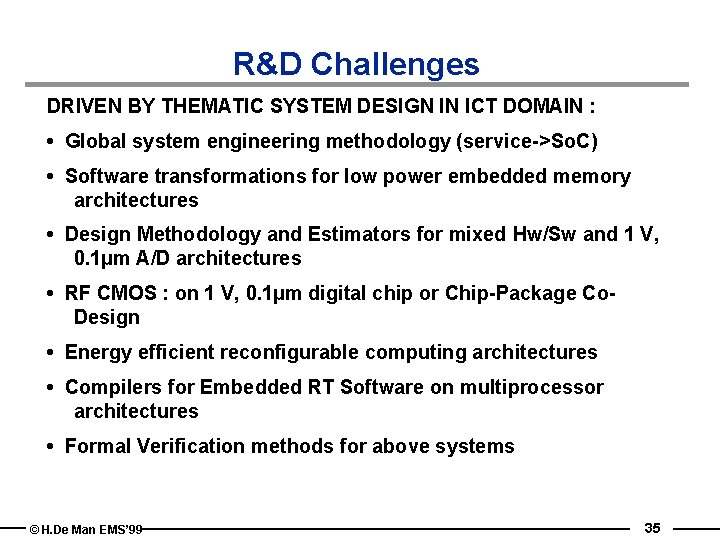

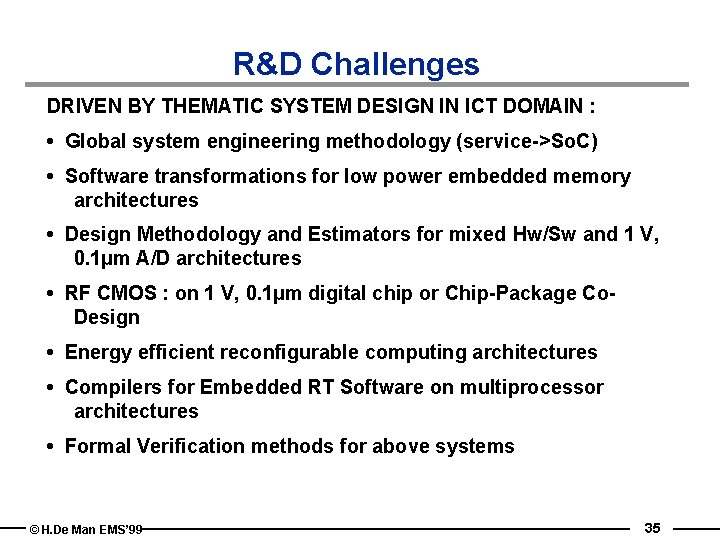

R&D Challenges DRIVEN BY THEMATIC SYSTEM DESIGN IN ICT DOMAIN : • Global system engineering methodology (service->So. C) • Software transformations for low power embedded memory architectures • Design Methodology and Estimators for mixed Hw/Sw and 1 V, 0. 1µm A/D architectures • RF CMOS : on 1 V, 0. 1µm digital chip or Chip-Package Co. Design • Energy efficient reconfigurable computing architectures • Compilers for Embedded RT Software on multiprocessor architectures • Formal Verification methods for above systems © H. De Man EMS’ 99 35