Designing HighVoltage Programmable Power Supply for driving Highcurrent

Designing High-Voltage, Programmable Power Supply for driving High-current Pulsed loads Part - 1 Presented by: Sanjay Pithadia SEM – Industrial Systems, Medical Sector

Challenge to Solve Driving High-Voltage Piezo sensors without using Big Capacitor banks 2

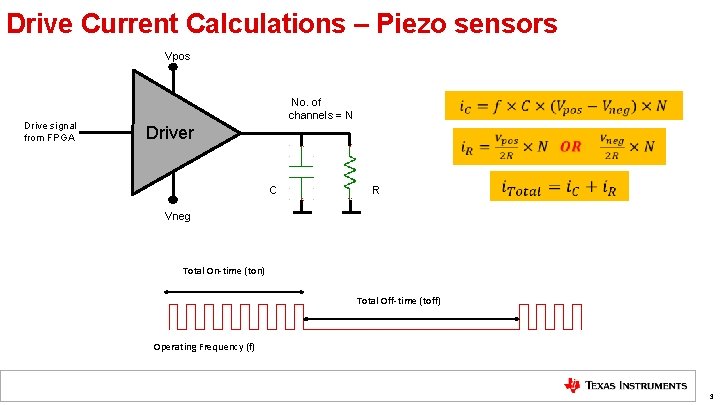

Drive Current Calculations – Piezo sensors Vpos Drive signal from FPGA No. of channels = N Driver C R Vneg Total On-time (ton) Total Off-time (toff) Operating Frequency (f) 3

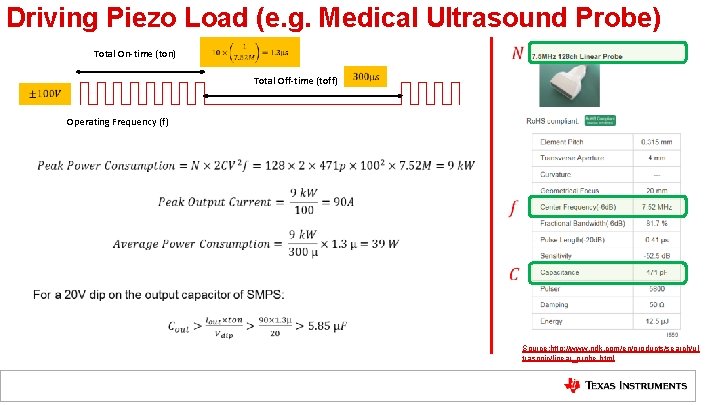

Driving Piezo Load (e. g. Medical Ultrasound Probe) Total On-time (ton) Total Off-time (toff) Operating Frequency (f) Source: http: //www. ndk. com/en/products/search/ul trasonic/linear_probe. html

Driving Medical Ultrasound Probe – Elastography Total On-time (ton) Total Off-time (toff) Operating Frequency (f) Elastography is a medical imaging modality that maps the elastic properties and stiffness of soft tissue.

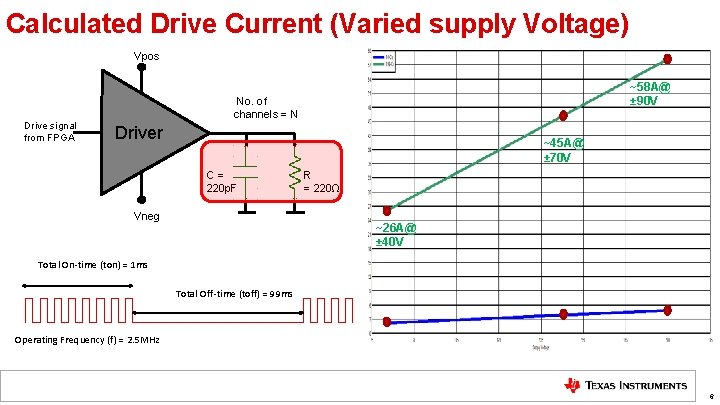

Calculated Drive Current (Varied supply Voltage) Vpos Drive signal from FPGA ~58 A@ ± 90 V No. of channels = N Driver ~45 A@ ± 70 V C = 220 p. F Vneg R = 220Ω ~26 A@ ± 40 V Total On-time (ton) = 1 ms Total Off-time (toff) = 99 ms Operating Frequency (f) = 2. 5 MHz 6

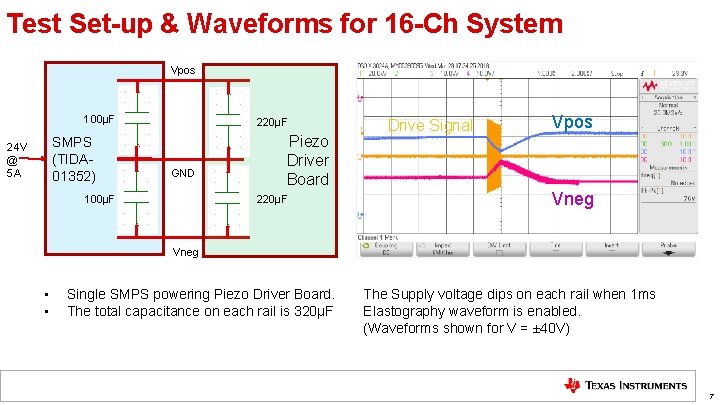

Test Set-up & Waveforms for 16 -Ch System Vpos 100µF SMPS (TIDA 01352) 24 V @ 5 A 220µF GND 100µF Piezo Driver Board 220µF Drive Signal Vpos Vneg • • Single SMPS powering Piezo Driver Board. The total capacitance on each rail is 320µF The Supply voltage dips on each rail when 1 ms Elastography waveform is enabled. (Waveforms shown for V = ± 40 V) 7

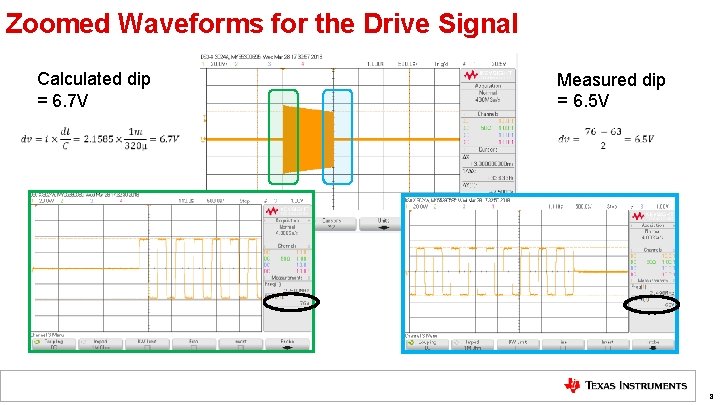

Zoomed Waveforms for the Drive Signal Calculated dip = 6. 7 V Measured dip = 6. 5 V 8

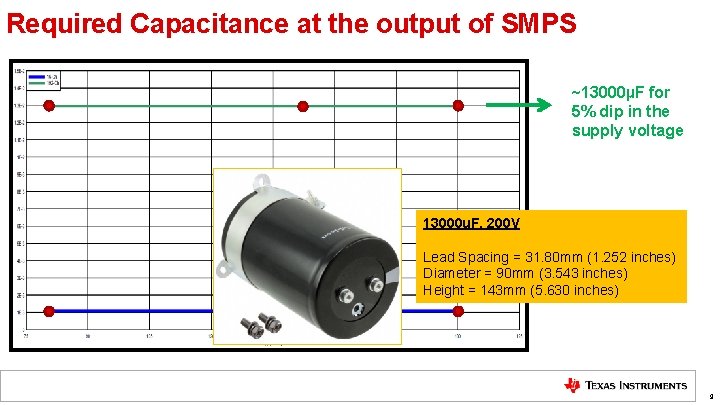

Required Capacitance at the output of SMPS ~13000µF for 5% dip in the supply voltage 13000 u. F, 200 V Lead Spacing = 31. 80 mm (1. 252 inches) Diameter = 90 mm (3. 543 inches) Height = 143 mm (5. 630 inches) 9

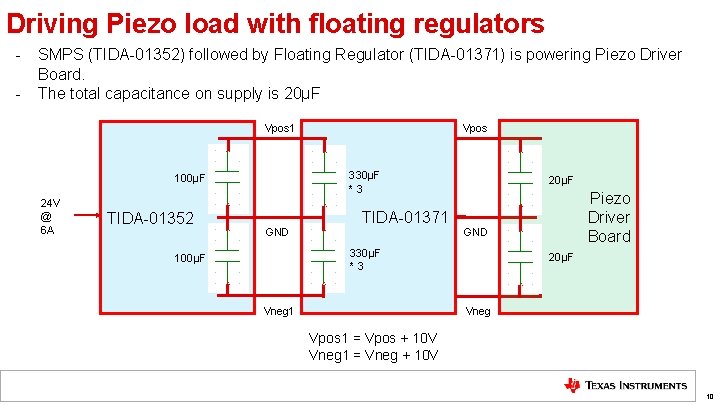

Driving Piezo load with floating regulators - SMPS (TIDA-01352) followed by Floating Regulator (TIDA-01371) is powering Piezo Driver Board. The total capacitance on supply is 20µF Vpos 1 330µF * 3 100µF 24 V @ 6 A TIDA-01352 Vpos GND TIDA-01371 20µF GND 330µF * 3 100µF Vneg 1 Piezo Driver Board 20µF Vneg Vpos 1 = Vpos + 10 V Vneg 1 = Vneg + 10 V 10

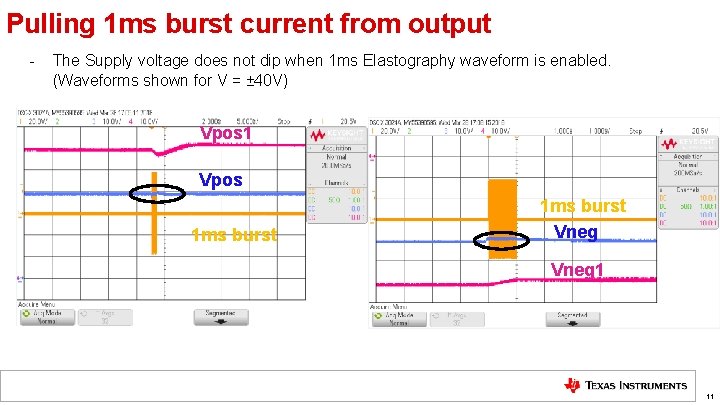

Pulling 1 ms burst current from output - The Supply voltage does not dip when 1 ms Elastography waveform is enabled. (Waveforms shown for V = ± 40 V) Vpos 1 ms burst Vneg 1 11

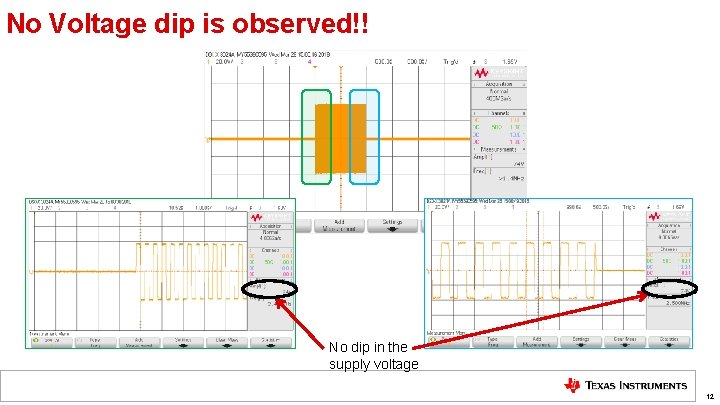

No Voltage dip is observed!! No dip in the supply voltage 12

Capacitor Size Comparison ~70% Board Space Saving 13000 u. F, 200 V 1000 u. F, 200 V Lead Spacing = 31. 80 mm (1. 252 inches) Diameter = 90 mm (3. 543 inches) Height = 143 mm (5. 630 inches) Lead Spacing = 10 mm (0. 394 inches) Diameter = 22 mm (0. 866 inches) Height = 50 mm (1. 969 inches) 13

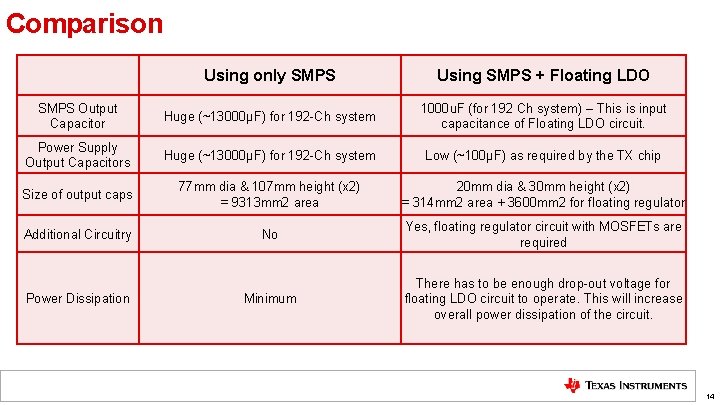

Comparison Using only SMPS Using SMPS + Floating LDO SMPS Output Capacitor Huge (~13000µF) for 192 -Ch system 1000 u. F (for 192 Ch system) – This is input capacitance of Floating LDO circuit. Power Supply Output Capacitors Huge (~13000µF) for 192 -Ch system Low (~100µF) as required by the TX chip Size of output caps 77 mm dia & 107 mm height (x 2) = 9313 mm 2 area 20 mm dia & 30 mm height (x 2) = 314 mm 2 area + 3600 mm 2 for floating regulator Additional Circuitry No Yes, floating regulator circuit with MOSFETs are required Minimum There has to be enough drop-out voltage for floating LDO circuit to operate. This will increase overall power dissipation of the circuit. Power Dissipation 14

TIDA-01352 & TIDA-01371 are available on TI. com Visit www. ti. com/tool/TIDA-01352 to find design resources (Gerbers, Schematics and more). Visit www. ti. com/tool/TIDA-01371 to find design resources (Gerbers, Schematics and more). 15

Other Resources http: //www. ti. com/lit/an/sloa 262. pdf 16

TI Information – Selective Disclosure

- Slides: 17