DesignHouses Oportunidades para o Brasil e Amrica Latina

Design-Houses: Oportunidades para o Brasil e América Latina Edna Barros (ensb@cin. ufpe. br) Centro de Informática – UFPE

Roteiro • Sistemas Embarcados e Novas tecnologias de Implementação • Tecnologias de Projeto • System Level Design • Oportunidades de Mercado – O Projeto Brazil_IP – Programa CI Brasil • Conclusões

Sistemas Embarcados e Novas Tecnologias de Implementação System on a Chip

Sistemas Embarcados

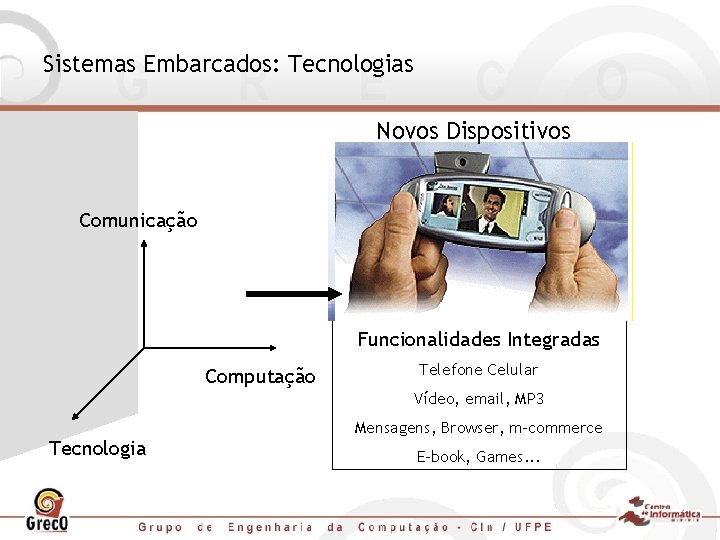

Sistemas Embarcados: Tecnologias Novos Dispositivos Comunicação Funcionalidades Integradas Computação Telefone Celular Vídeo, email, MP 3 Tecnologia Mensagens, Browser, m-commerce E-book, Games. . .

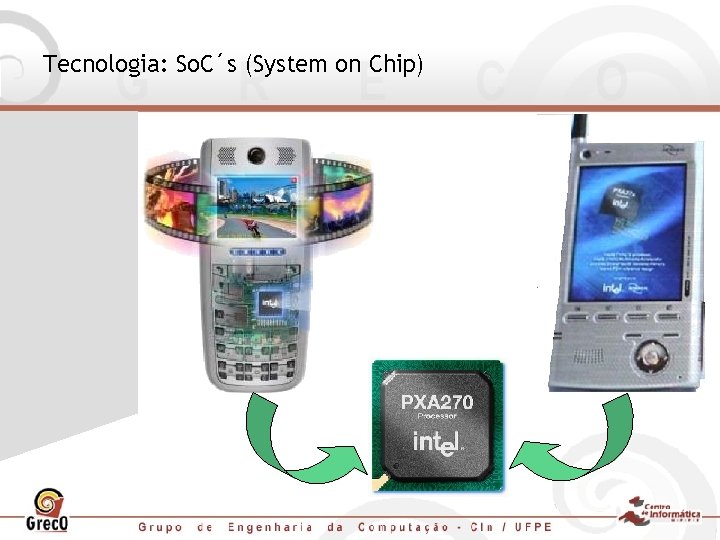

Tecnologia: So. C´s (System on Chip)

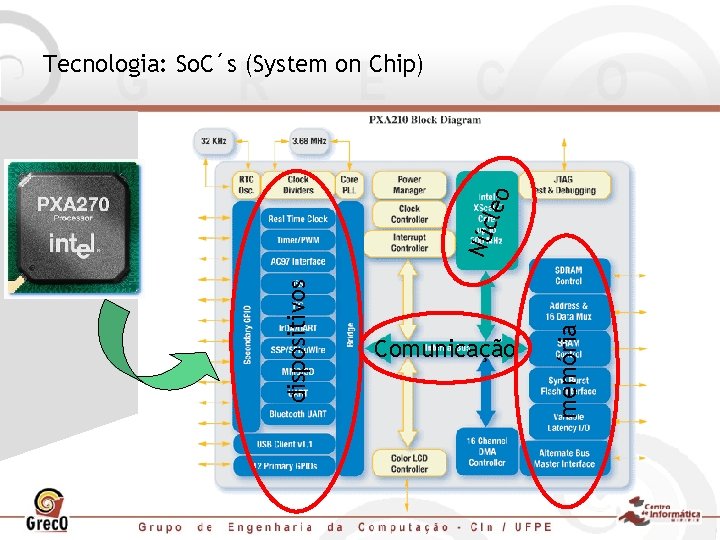

Comunicação memória dispositivos Núc leo Tecnologia: So. C´s (System on Chip)

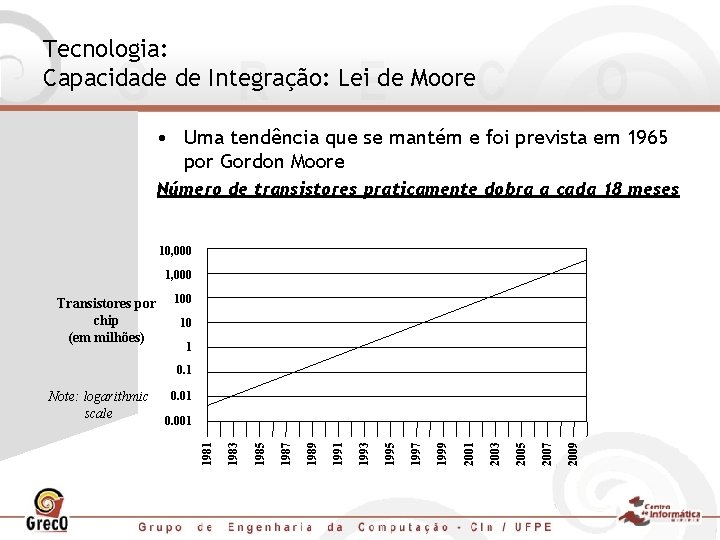

Tecnologia: Capacidade de Integração: Lei de Moore • Uma tendência que se mantém e foi prevista em 1965 por Gordon Moore Número de transistores praticamente dobra a cada 18 meses 10, 000 1, 000 Transistores por chip (em milhões) 100 10 1 0. 01 2009 2007 2005 2003 2001 1999 1997 1995 1993 1991 1989 1987 1985 1983 0. 001 1981 Note: logarithmic scale

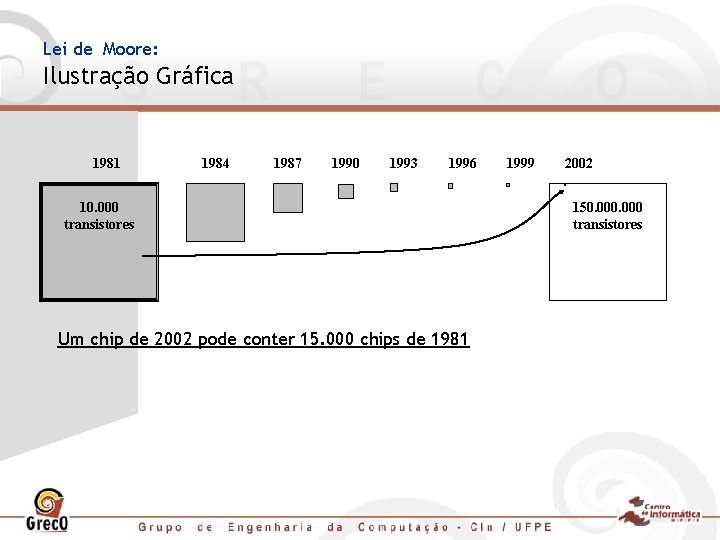

Lei de Moore: Ilustração Gráfica 1981 1984 1987 1990 1993 1996 10. 000 transistores Um chip de 2002 pode conter 15. 000 chips de 1981 1999 2002 150. 000 transistores

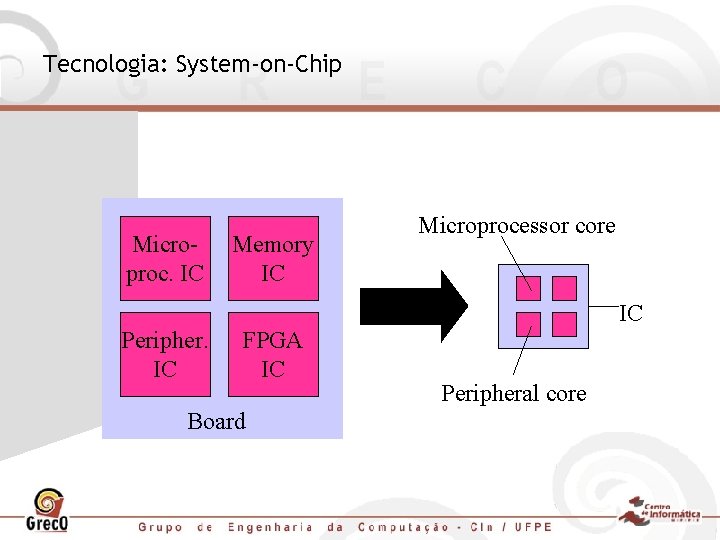

Tecnologia: System-on-Chip Microproc. IC Memory IC Microprocessor core IC Peripher. IC FPGA IC Board Peripheral core

System-On-Chip • • Uso de núcleos de processadores (cores) Baixo custo de fabricação em série Alta qualidade Diminuição de defeitos de montagem e fabricação em geral • Baixa potência consumida • Pequeno tamanho • Alta velocidade

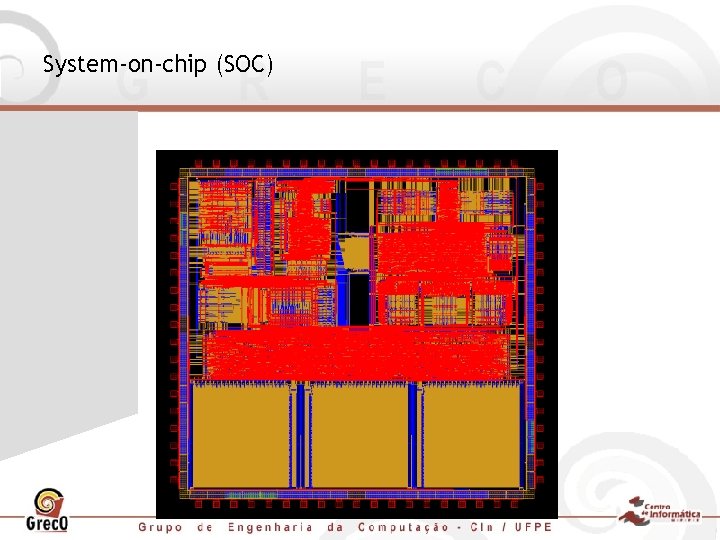

System-on-chip (SOC)

Tecnologias de Projeto A maneira de converter uma funcionalidade em implementação

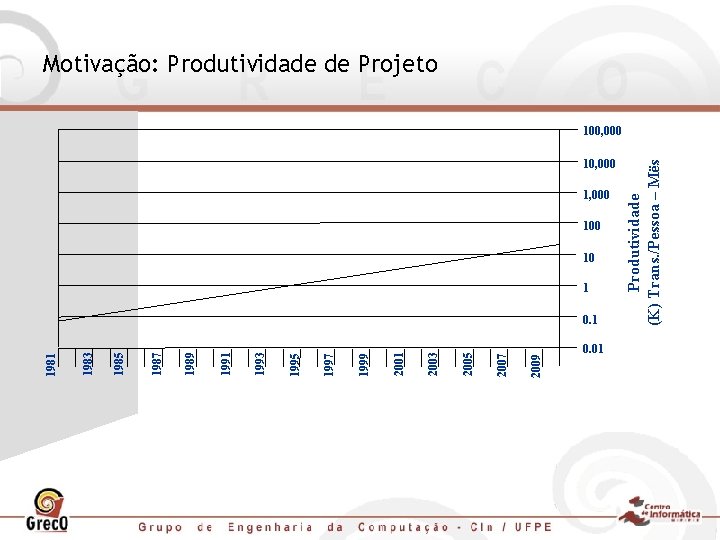

2009 2007 2005 2003 2001 1999 1997 1995 1993 1991 1989 1987 1985 1983 1981 10, 000 100 10 1 0. 01 Produtividade (K) Trans. /Pessoa – Mës Motivação: Produtividade de Projeto 100, 000

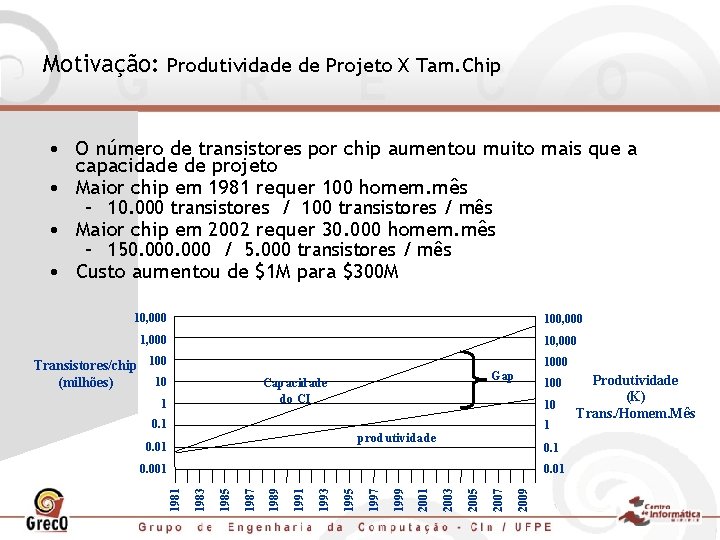

Motivação: Produtividade de Projeto X Tam. Chip • O número de transistores por chip aumentou muito mais que a capacidade de projeto • Maior chip em 1981 requer 100 homem. mês – 10. 000 transistores / 100 transistores / mês • Maior chip em 2002 requer 30. 000 homem. mês – 150. 000 / 5. 000 transistores / mês • Custo aumentou de $1 M para $300 M 10, 000 100, 000 10, 000 Transistores/chip 100 10 (milhões) 1000 Gap Capacidade do CI 1 100 10 0. 1 1 produtividade 0. 01 0. 001 2009 2007 2005 2003 2001 1999 1997 1995 1993 1991 1989 1987 1985 1983 1981 0. 01 Produtividade (K) Trans. /Homem. Mês

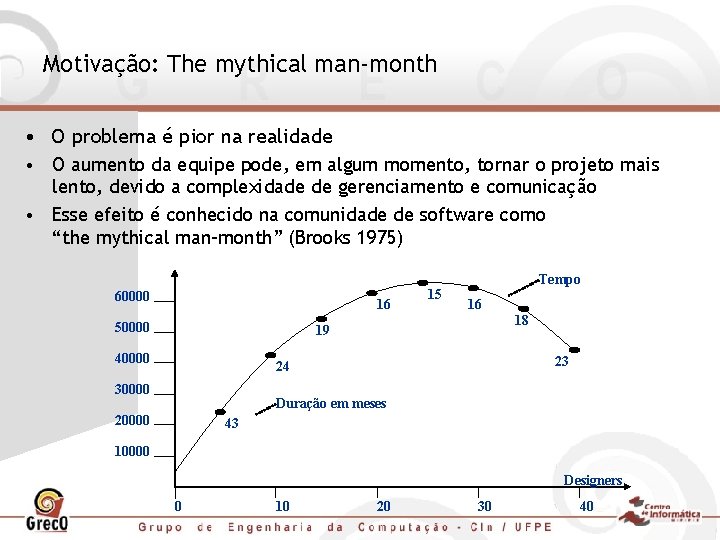

Motivação: The mythical man-month • O problema é pior na realidade • O aumento da equipe pode, em algum momento, tornar o projeto mais lento, devido a complexidade de gerenciamento e comunicação • Esse efeito é conhecido na comunidade de software como “the mythical man-month” (Brooks 1975) Tempo 60000 16 50000 15 16 18 19 40000 23 24 30000 Duração em meses 20000 43 10000 Designers 0 10 20 30 40

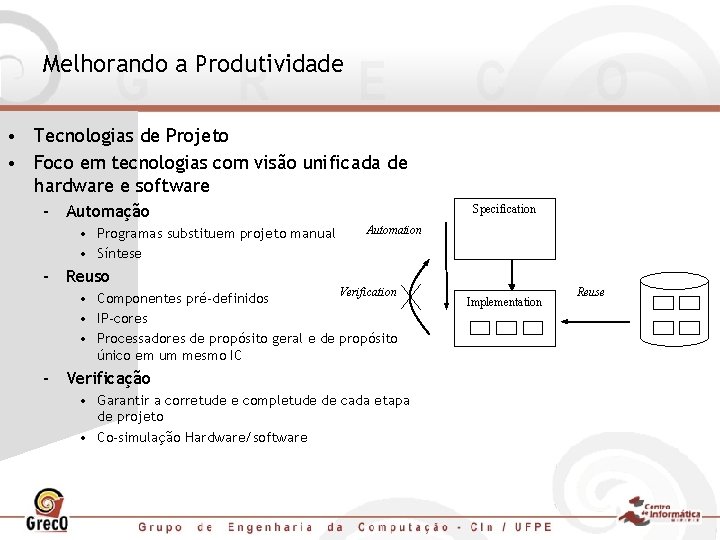

Melhorando a Produtividade • Tecnologias de Projeto • Foco em tecnologias com visão unificada de hardware e software – Automação • Programas substituem projeto manual • Síntese Specification Automation – Reuso Verification • Componentes pré-definidos • IP-cores • Processadores de propósito geral e de propósito único em um mesmo IC – Verificação • Garantir a corretude e completude de cada etapa de projeto • Co-simulação Hardware/software Implementation Reuse

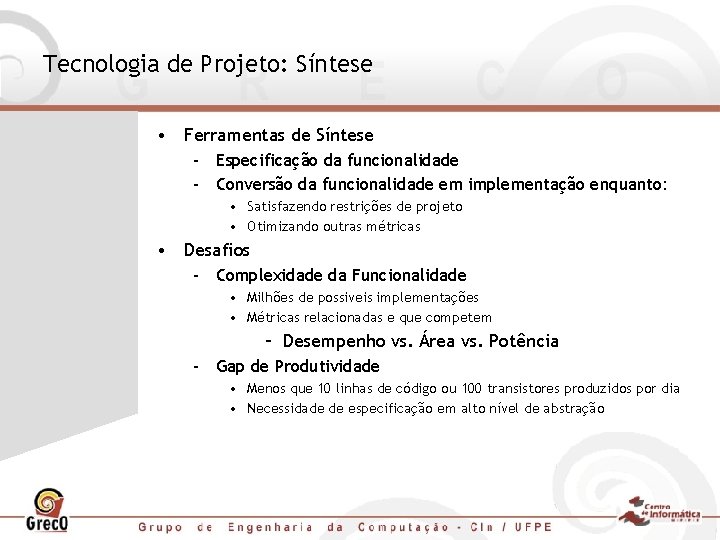

Tecnologia de Projeto: Síntese • Ferramentas de Síntese – Especificação da funcionalidade – Conversão da funcionalidade em implementação enquanto: • Satisfazendo restrições de projeto • Otimizando outras métricas • Desafios – Complexidade da Funcionalidade • Milhões de possiveis implementações • Métricas relacionadas e que competem – Desempenho vs. Área vs. Potência – Gap de Produtividade • Menos que 10 linhas de código ou 100 transistores produzidos por dia • Necessidade de especificação em alto nível de abstração

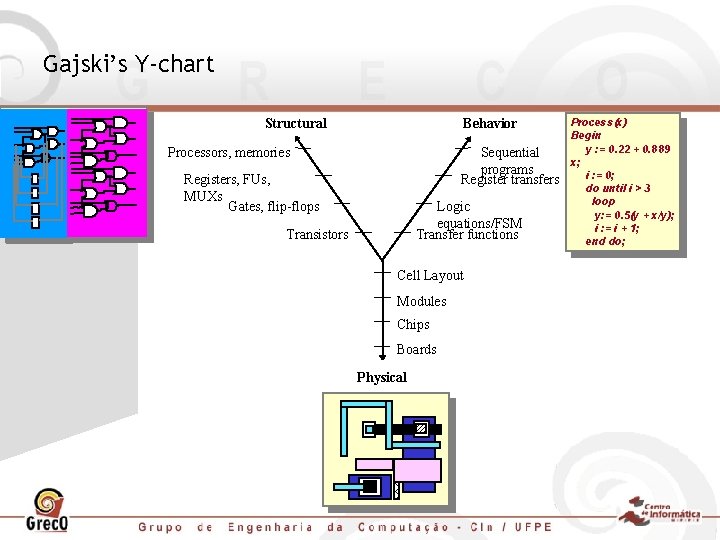

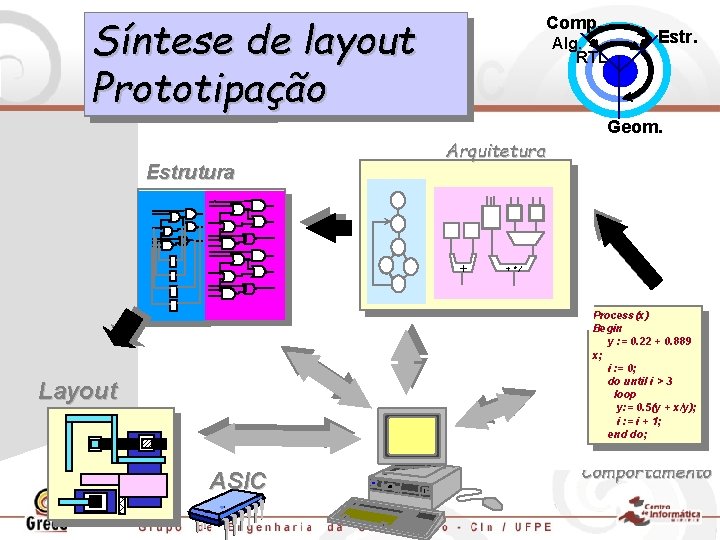

Gajski’s Y-chart Behavior Structural Processors, memories Sequential programs Register transfers Registers, FUs, MUXs Gates, flip-flops Logic equations/FSM Transfer functions Transistors Cell Layout Modules Chips Boards Physical Process(x) Begin y : = 0. 22 + 0. 889 x; i : = 0; do until i > 3 loop y: = 0. 5(y + x/y); i : = i + 1; end do;

Síntese algorítmica lógica de layout Especificação (alto Prototipação Inicialnível) Arquitetura Controle Estr. Geom. Arquitetura + ASIC Alg. RTL Processamento Estrutura Layout Comp. + + + * */ / Process(x) Begin y : = 0. 22 + 0. 889 Process(x) x; Begin i : = 0; y : = 0. 22 + 0. 889 do x; until i>3 i : = 0; loopdo until i > 3 loop y: = 0. 5(y x/y); y: = 0. 5(y++ x/y); : = i 1; + 1; i : = ii + end do; Comportamento

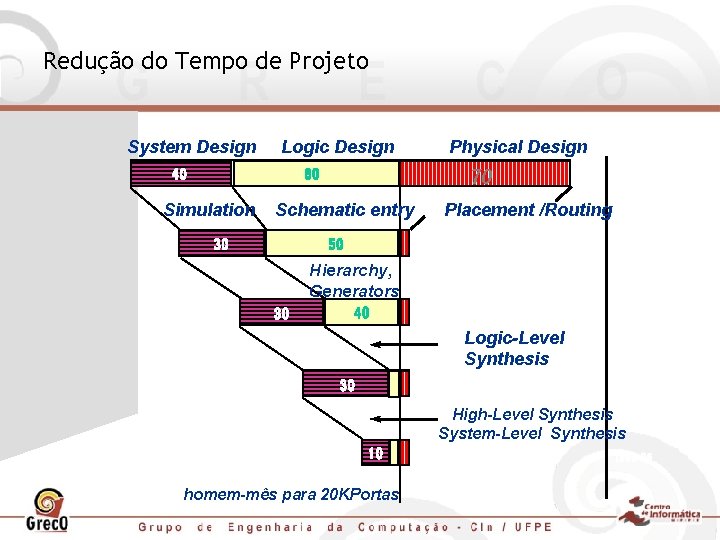

Redução do Tempo de Projeto System Design Logic Design Physical Design 70 Simulation Schematic entry Placement /Routing Hierarchy, Generators Logic-Level Synthesis High-Level Synthesis System-Level Synthesis homem-mês para 20 KPortas

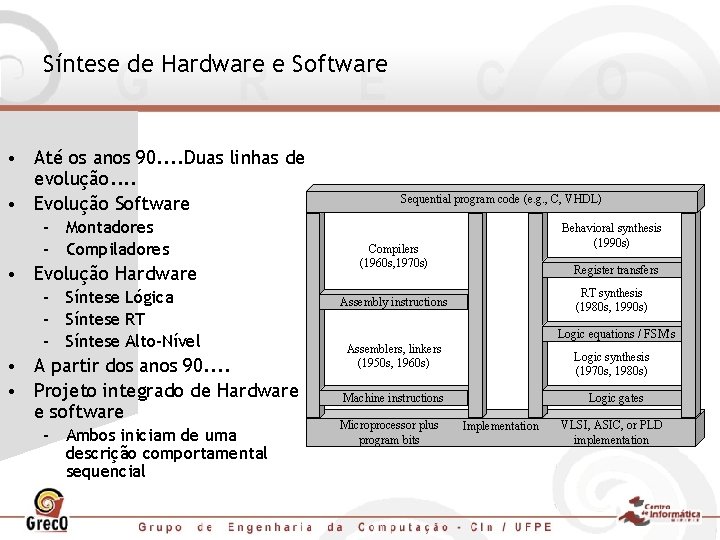

Síntese de Hardware e Software • Até os anos 90. . Duas linhas de evolução. . • Evolução Software – Montadores – Compiladores • Evolução Hardware – Síntese Lógica – Síntese RT – Síntese Alto-Nível • A partir dos anos 90. . • Projeto integrado de Hardware e software – Ambos iniciam de uma descrição comportamental sequencial Sequential program code (e. g. , C, VHDL) Behavioral synthesis (1990 s) Compilers (1960 s, 1970 s) Register transfers RT synthesis (1980 s, 1990 s) Assembly instructions Logic equations / FSM's Assemblers, linkers (1950 s, 1960 s) Logic synthesis (1970 s, 1980 s) Machine instructions Microprocessor plus program bits Logic gates Implementation VLSI, ASIC, or PLD implementation

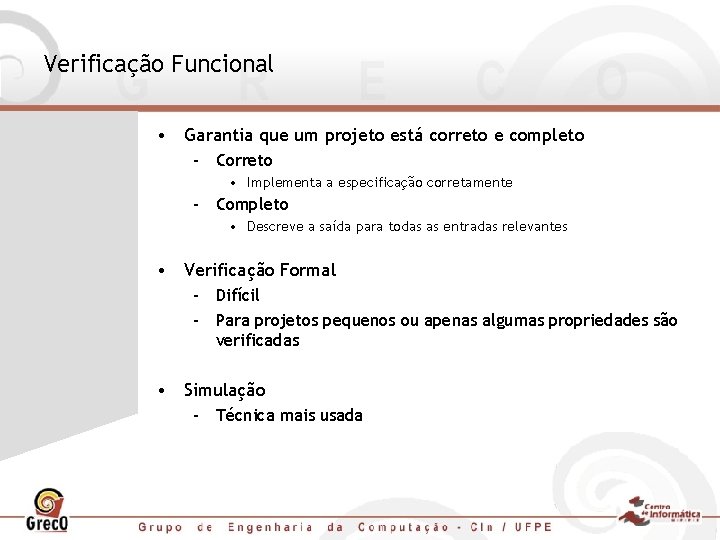

Verificação Funcional • Garantia que um projeto está correto e completo – Correto • Implementa a especificação corretamente – Completo • Descreve a saída para todas as entradas relevantes • Verificação Formal – Difícil – Para projetos pequenos ou apenas algumas propriedades são verificadas • Simulação – Técnica mais usada

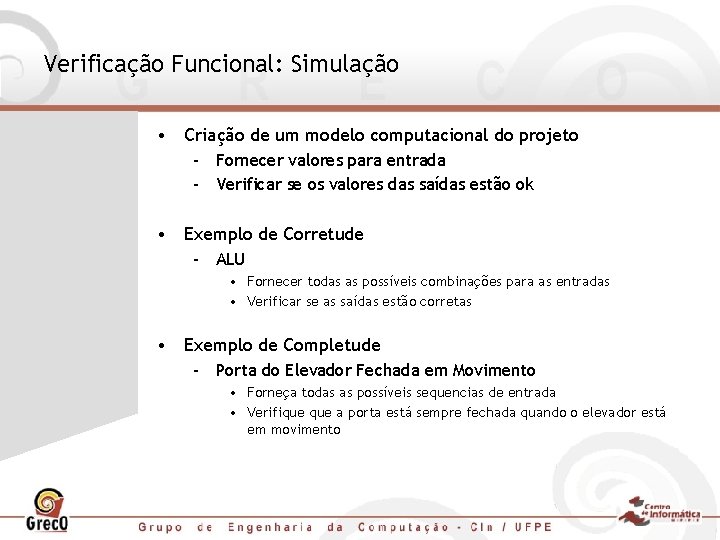

Verificação Funcional: Simulação • Criação de um modelo computacional do projeto – Fornecer valores para entrada – Verificar se os valores das saídas estão ok • Exemplo de Corretude – ALU • Fornecer todas as possíveis combinações para as entradas • Verificar se as saídas estão corretas • Exemplo de Completude – Porta do Elevador Fechada em Movimento • Forneça todas as possíveis sequencias de entrada • Verifique a porta está sempre fechada quando o elevador está em movimento

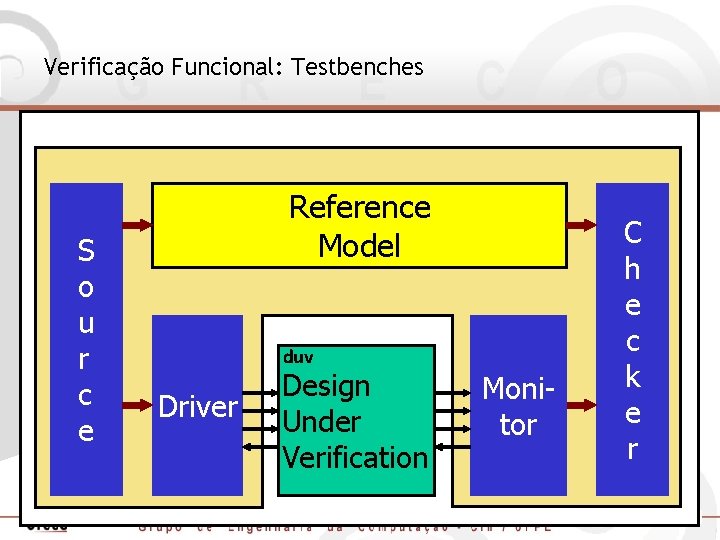

Verificação Funcional: Testbenches S o u r c e Reference Model duv Driver Design Under Verification Monitor C h e c k e r

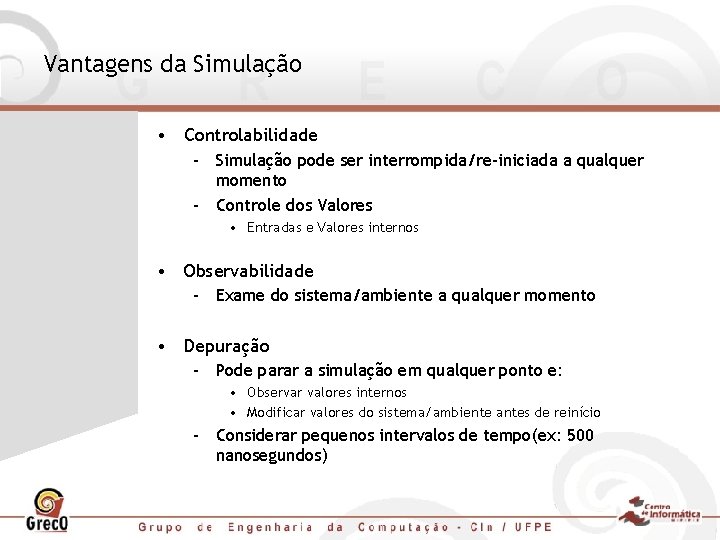

Vantagens da Simulação • Controlabilidade – Simulação pode ser interrompida/re-iniciada a qualquer momento – Controle dos Valores • Entradas e Valores internos • Observabilidade – Exame do sistema/ambiente a qualquer momento • Depuração – Pode parar a simulação em qualquer ponto e: • Observar valores internos • Modificar valores do sistema/ambiente antes de reinício – Considerar pequenos intervalos de tempo(ex: 500 nanosegundos)

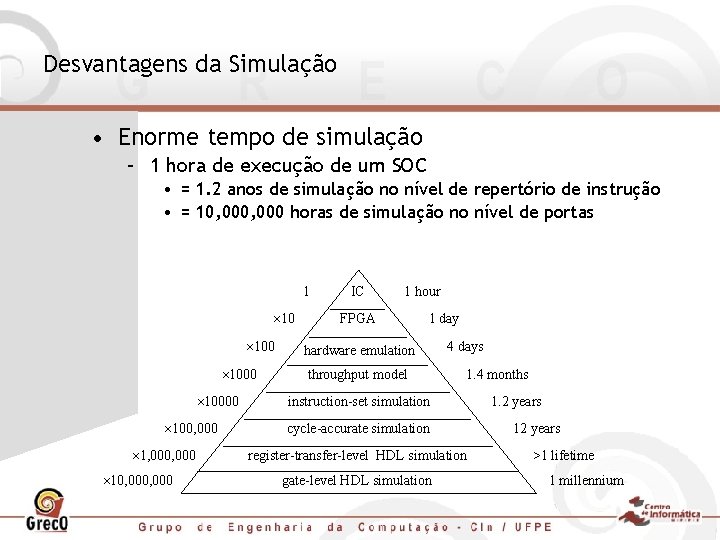

Desvantagens da Simulação • Enorme tempo de simulação – 1 hora de execução de um SOC • = 1. 2 anos de simulação no nível de repertório de instrução • = 10, 000 horas de simulação no nível de portas 1 10 1000 100, 000 1, 000 10, 000 IC 1 hour FPGA 1 day hardware emulation throughput model 4 days 1. 4 months instruction-set simulation cycle-accurate simulation register-transfer-level HDL simulation gate-level HDL simulation 1. 2 years 12 years >1 lifetime 1 millennium

Tendências e Necessidades: • Modelos de Simulação que permitam simulação rápida • Modelos descritos em níveis mais abstratos • Análise de Cobertura de Testes

System Level Design Tendências e Oportunidades

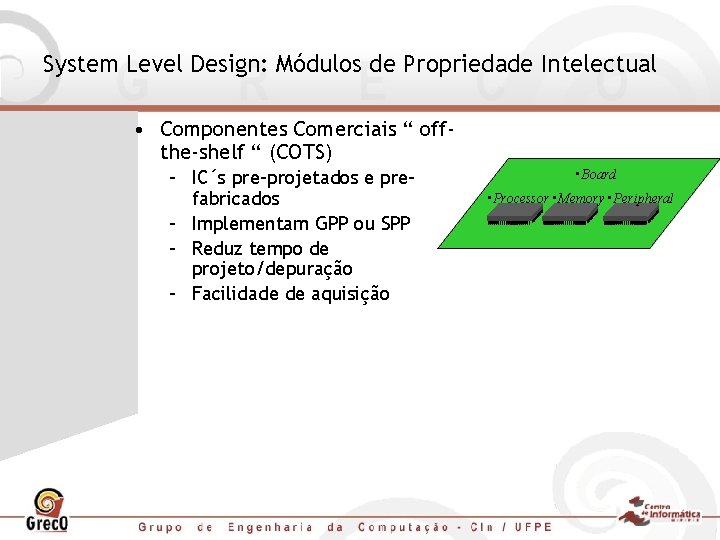

System Level Design: Módulos de Propriedade Intelectual • Componentes Comerciais “ offthe-shelf “ (COTS) – IC´s pre-projetados e prefabricados – Implementam GPP ou SPP – Reduz tempo de projeto/depuração – Facilidade de aquisição • Board • Processor • Memory • Peripheral

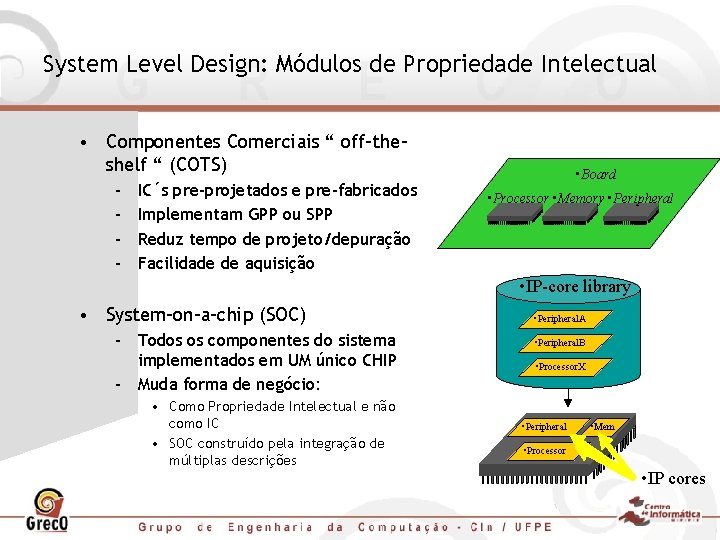

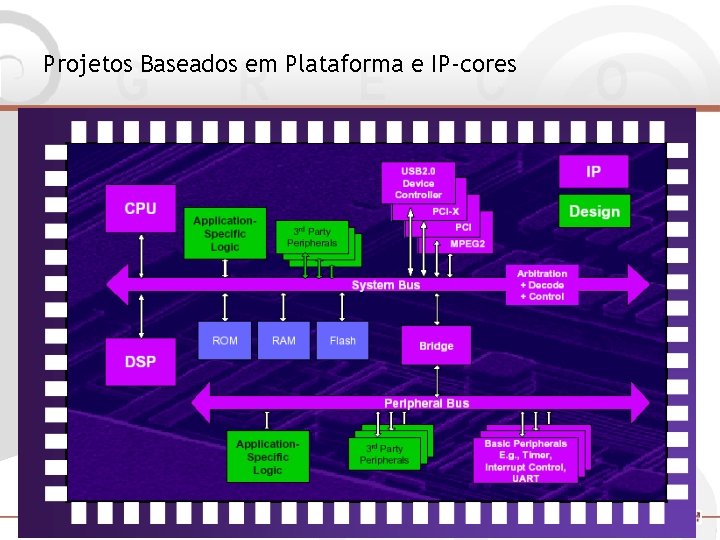

System Level Design: Módulos de Propriedade Intelectual • Componentes Comerciais “ off-theshelf “ (COTS) – – IC´s pre-projetados e pre-fabricados Implementam GPP ou SPP Reduz tempo de projeto/depuração Facilidade de aquisição • Board • Processor • Memory • Peripheral • IP-core Core library • System-on-a-chip (SOC) – Todos os componentes do sistema implementados em UM único CHIP – Muda forma de negócio: • Como Propriedade Intelectual e não como IC • SOC construído pela integração de múltiplas descrições • Peripheral. A • Peripheral. B • Processor. X • Peripheral • Mem • Processor • IP cores

Projetos Baseados em Plataforma e IP-cores

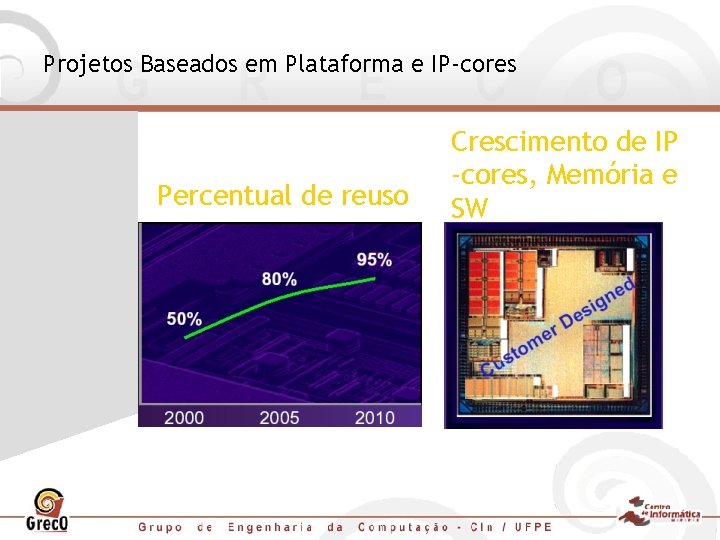

Projetos Baseados em Plataforma e IP-cores Percentual de reuso Crescimento de IP -cores, Memória e SW

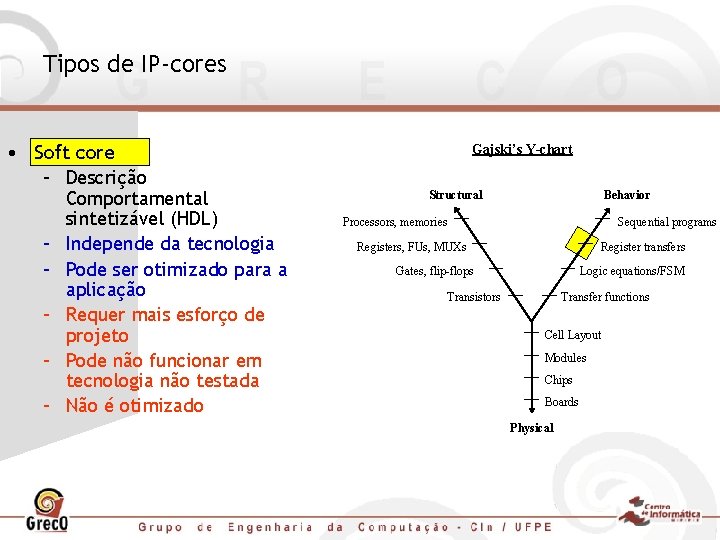

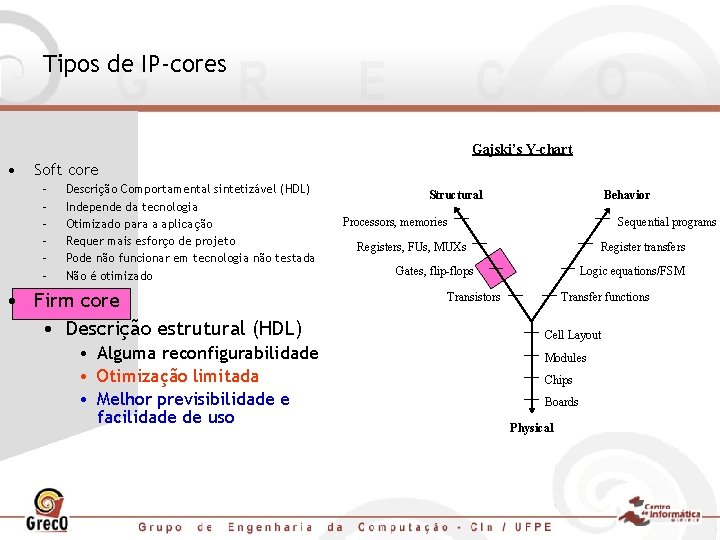

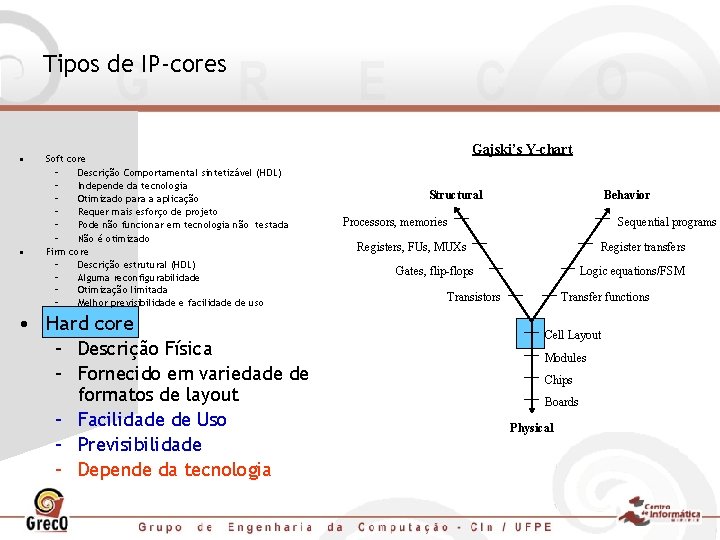

Tipos de IP-cores • Soft core – Descrição – – – Comportamental sintetizável (HDL) Independe da tecnologia Pode ser otimizado para a aplicação Requer mais esforço de projeto Pode não funcionar em tecnologia não testada Não é otimizado Gajski’s Y-chart Behavior Structural Processors, memories Sequential programs Registers, FUs, MUXs Register transfers Gates, flip-flops Logic equations/FSM Transistors Transfer functions Cell Layout Modules Chips Boards Physical

Tipos de IP-cores Gajski’s Y-chart • Soft core – – – Descrição Comportamental sintetizável (HDL) Independe da tecnologia Otimizado para a aplicação Requer mais esforço de projeto Pode não funcionar em tecnologia não testada Não é otimizado • Firm core • Descrição estrutural (HDL) • Alguma reconfigurabilidade • Otimização limitada • Melhor previsibilidade e facilidade de uso Behavior Structural Processors, memories Sequential programs Registers, FUs, MUXs Register transfers Gates, flip-flops Logic equations/FSM Transistors Transfer functions Cell Layout Modules Chips Boards Physical

Tipos de IP-cores • • Soft core – Descrição Comportamental sintetizável (HDL) – Independe da tecnologia – Otimizado para a aplicação – Requer mais esforço de projeto – Pode não funcionar em tecnologia não testada – Não é otimizado Firm core – Descrição estrutural (HDL) – Alguma reconfigurabilidade – Otimização limitada – Melhor previsibilidade e facilidade de uso • Hard core – Descrição Física – Fornecido em variedade de formatos de layout – Facilidade de Uso – Previsibilidade – Depende da tecnologia Gajski’s Y-chart Behavior Structural Processors, memories Sequential programs Registers, FUs, MUXs Register transfers Gates, flip-flops Logic equations/FSM Transistors Transfer functions Cell Layout Modules Chips Boards Physical

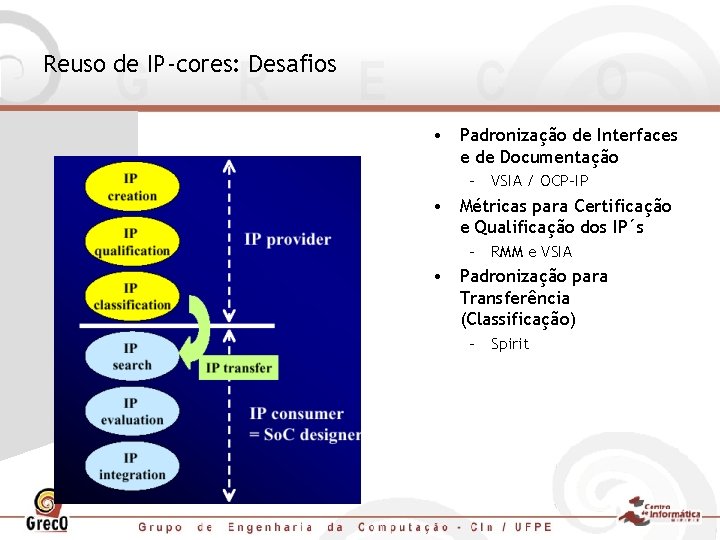

Reuso de IP-cores: Desafios • Padronização de Interfaces e de Documentação – VSIA / OCP-IP • Métricas para Certificação e Qualificação dos IP´s – RMM e VSIA • Padronização para Transferência (Classificação) – Spirit

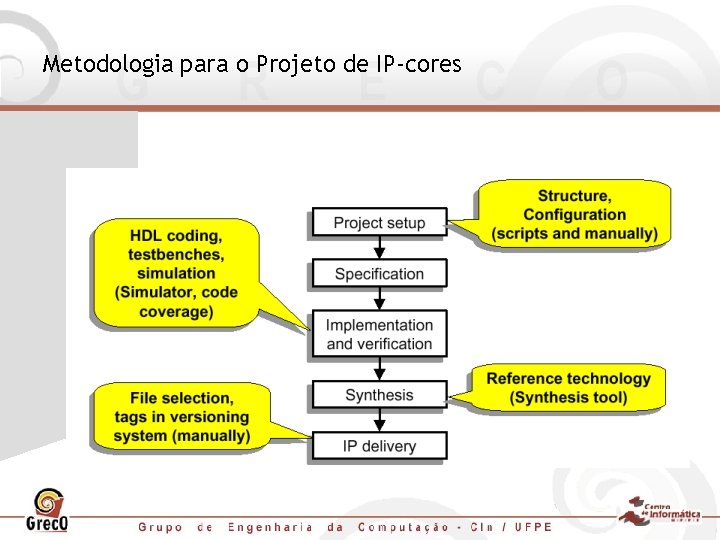

Metodologia para o Projeto de IP-cores

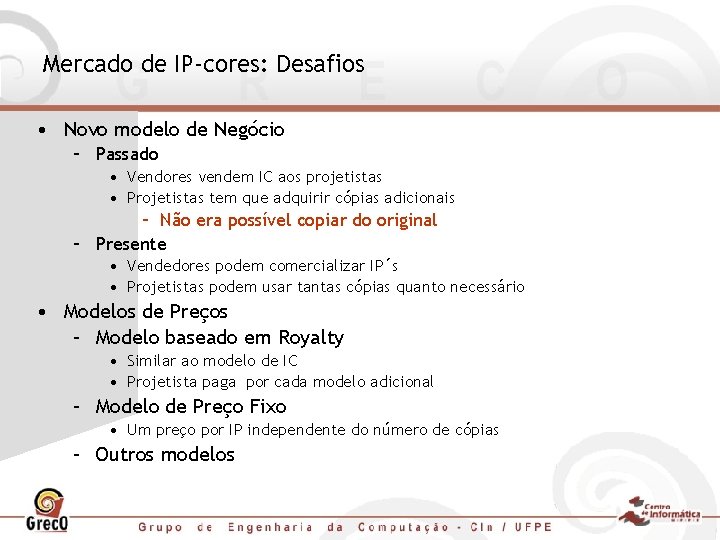

Mercado de IP-cores: Desafios • Novo modelo de Negócio – Passado • Vendores vendem IC aos projetistas • Projetistas tem que adquirir cópias adicionais – Não era possível copiar do original – Presente • Vendedores podem comercializar IP´s • Projetistas podem usar tantas cópias quanto necessário • Modelos de Preços – Modelo baseado em Royalty • Similar ao modelo de IC • Projetista paga por cada modelo adicional – Modelo de Preço Fixo • Um preço por IP independente do número de cópias – Outros modelos

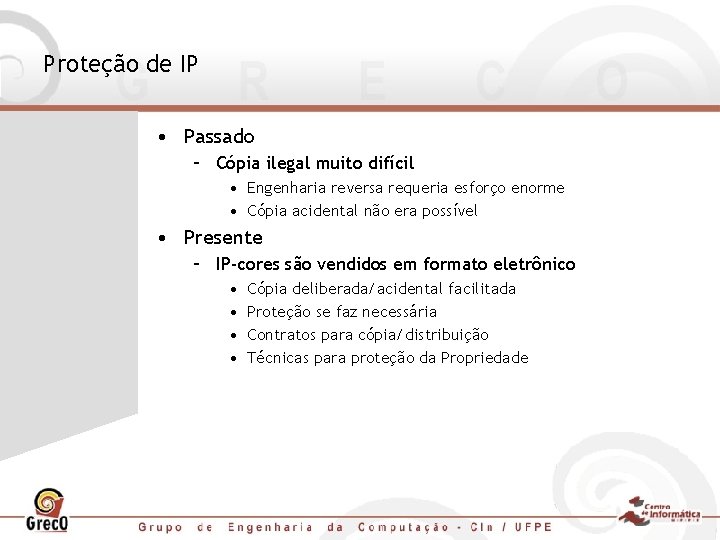

Proteção de IP • Passado – Cópia ilegal muito difícil • Engenharia reversa requeria esforço enorme • Cópia acidental não era possível • Presente – IP-cores são vendidos em formato eletrônico • • Cópia deliberada/acidental facilitada Proteção se faz necessária Contratos para cópia/distribuição Técnicas para proteção da Propriedade

Novos desafios para usuários de IPs • Licença – Mais difícil do que comprar um IC – Muitos contratos estabelecem modelo de preço e proteção • Assistência jurídica • Esforço extra de projeto – Especialmente para soft cores • Devem ser sintetizados e testados • Diferenças mínimas pode causar problemas • Verificação é mais difícil – Teste extensivo para soft cores sintetizados e soft/firm cores mapeados a tecnologia particular • Tempo e potência pode variar entre implementações – Verificação é crítica • IP-cores produzidos como IC • Não se pode substituir IP-core ruim

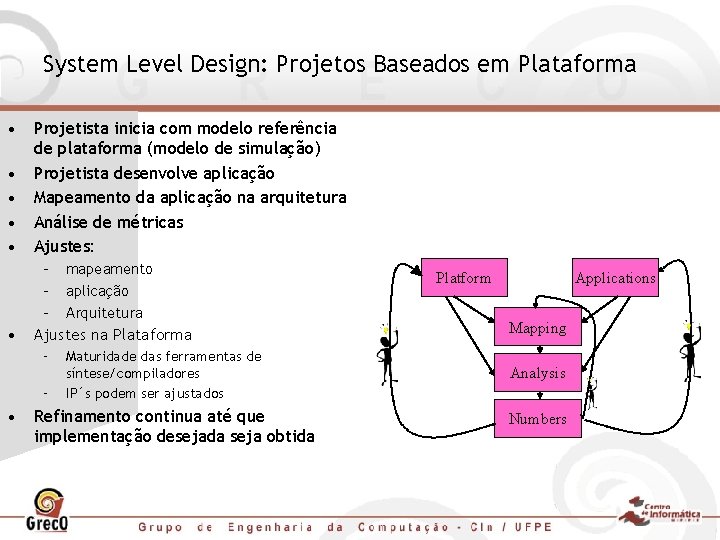

System Level Design: Projetos Baseados em Plataforma • • • Projetista inicia com modelo referência de plataforma (modelo de simulação) Projetista desenvolve aplicação Mapeamento da aplicação na arquitetura Análise de métricas Ajustes: • – mapeamento – aplicação – Arquitetura Ajustes na Plataforma – – • Maturidade das ferramentas de síntese/compiladores IP´s podem ser ajustados Refinamento continua até que implementação desejada seja obtida Platform Applications Mapping Analysis Numbers

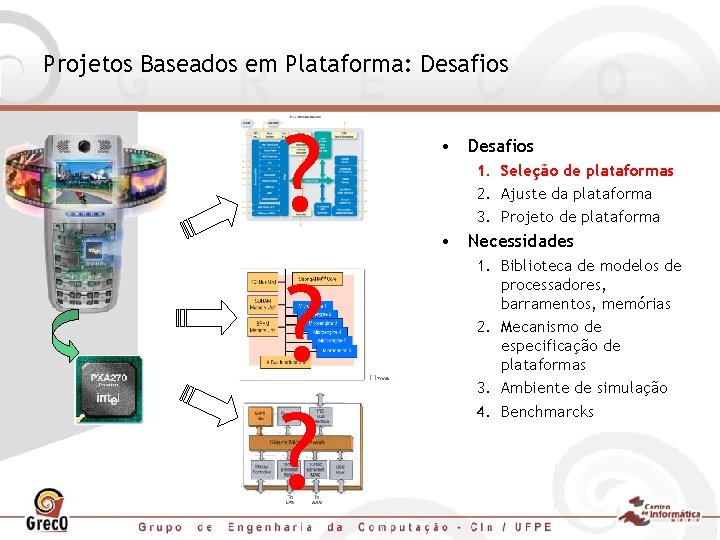

Projetos Baseados em Plataforma: Desafios ? ? ? • Desafios 1. Seleção de plataformas 2. Ajuste da plataforma 3. Projeto de plataforma • Necessidades 1. Biblioteca de modelos de processadores, barramentos, memórias 2. Mecanismo de especificação de plataformas 3. Ambiente de simulação 4. Benchmarcks

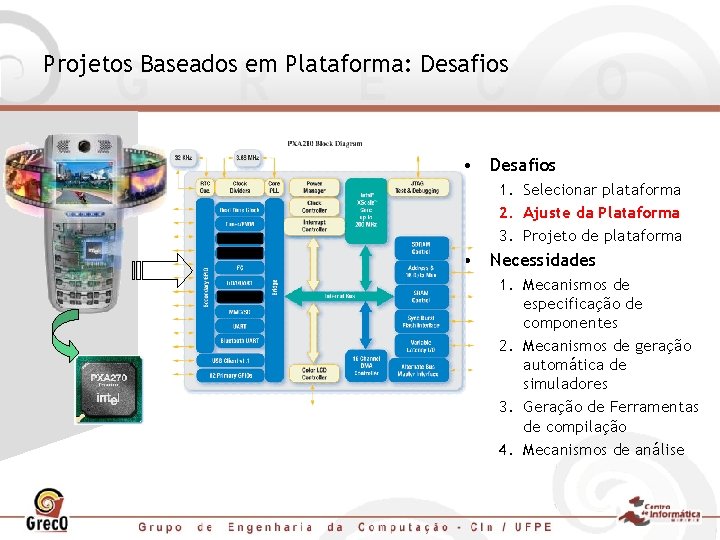

Projetos Baseados em Plataforma: Desafios • Desafios 1. Selecionar plataforma 2. Ajuste da Plataforma 3. Projeto de plataforma • Necessidades 1. Mecanismos de especificação de componentes 2. Mecanismos de geração automática de simuladores 3. Geração de Ferramentas de compilação 4. Mecanismos de análise

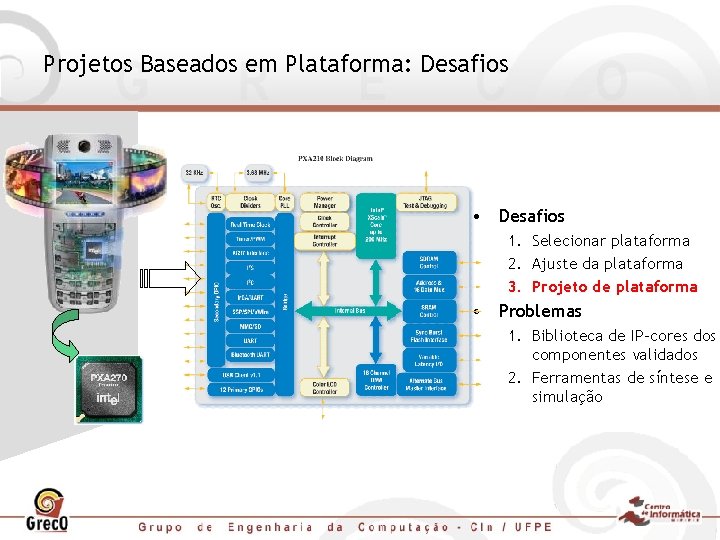

Projetos Baseados em Plataforma: Desafios • Desafios 1. Selecionar plataforma 2. Ajuste da plataforma 3. Projeto de plataforma • Problemas 1. Biblioteca de IP-cores dos componentes validados 2. Ferramentas de síntese e simulação

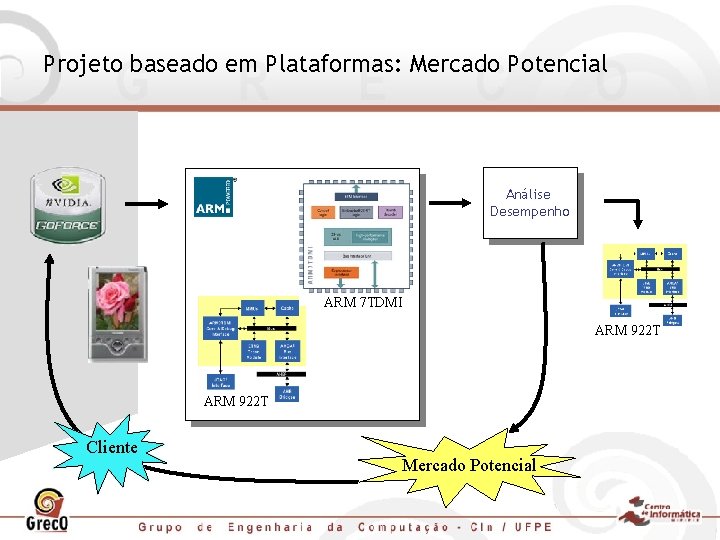

Projeto baseado em Plataformas: Mercado Potencial Análise Desempenho ARM 7 TDMI ARM 922 T Cliente Mercado Potencial

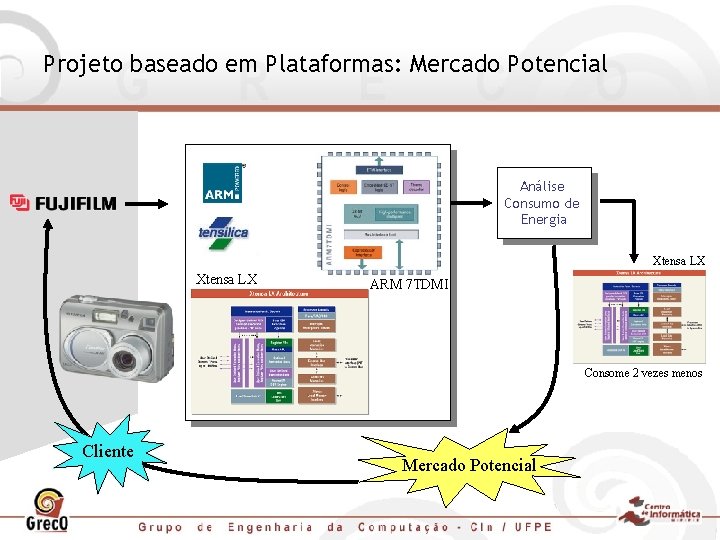

Projeto baseado em Plataformas: Mercado Potencial Análise Consumo de Energia Xtensa LX ARM 7 TDMI Consome 2 vezes menos Cliente Mercado Potencial

Aplicações WDM, Sistemas de Transmissões Ópticos sonares, WCDMA Serviços CISCO CRS-1 (40 Gbps) Serviços Aplicações Eletrônicas de consumidor Serviços Mercado Potencial: Oferecendo Soluções Aplicações de Processamento de Imagem Future Digital Camera (Digital Still Cameras) Próxima geração de produtos imagem Próxima geração de digital video camcoder

Ambiente Platform-Designer Especificação de plataformas Análise do desempenho de comunicação Análise do desempenho em memórias Análise do consumo de energia em memórias

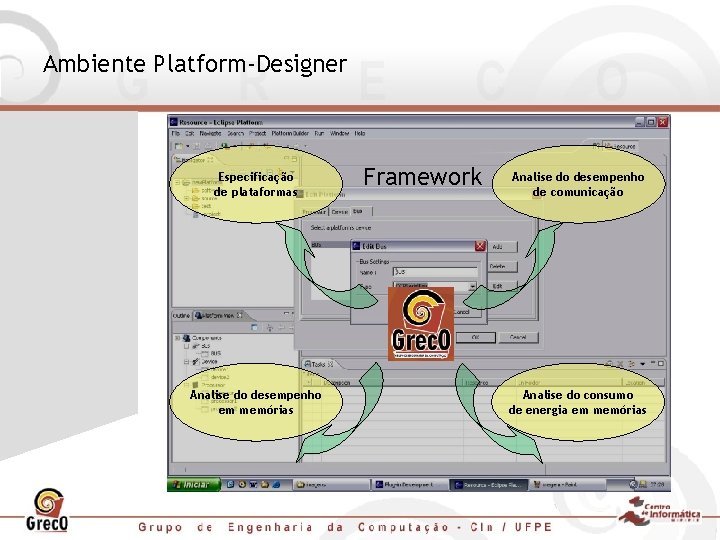

Ambiente Platform-Designer Especificação de plataformas Analise do desempenho em memórias Framework Analise do desempenho de comunicação Analise do consumo de energia em memórias

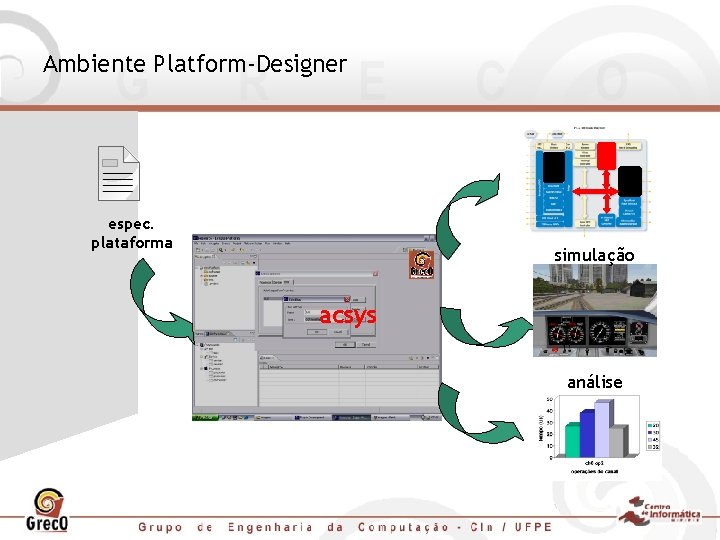

Ambiente Platform-Designer espec. plataforma simulação acsys análise

Oportunidades de Mercado Iniciativas para a Criação e Fortalecimento de Design-Houses

O Projeto Brazil IP THE TIME HAS COME…

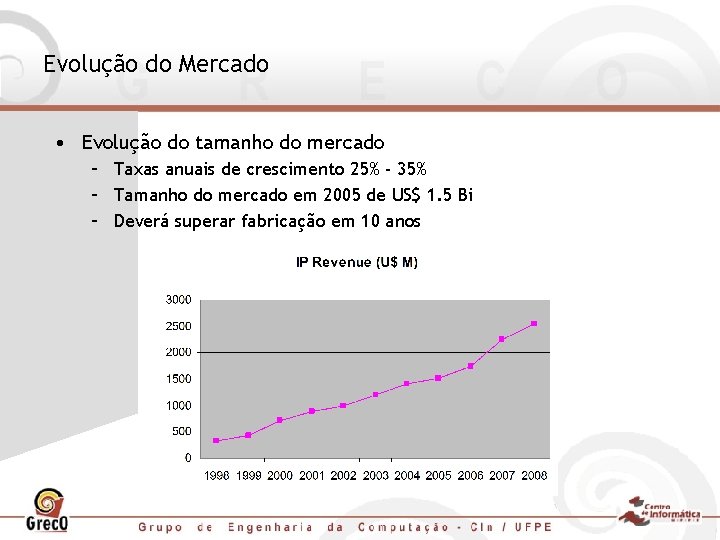

Evolução do Mercado • Evolução do tamanho do mercado – Taxas anuais de crescimento 25% - 35% – Tamanho do mercado em 2005 de US$ 1. 5 Bi – Deverá superar fabricação em 10 anos

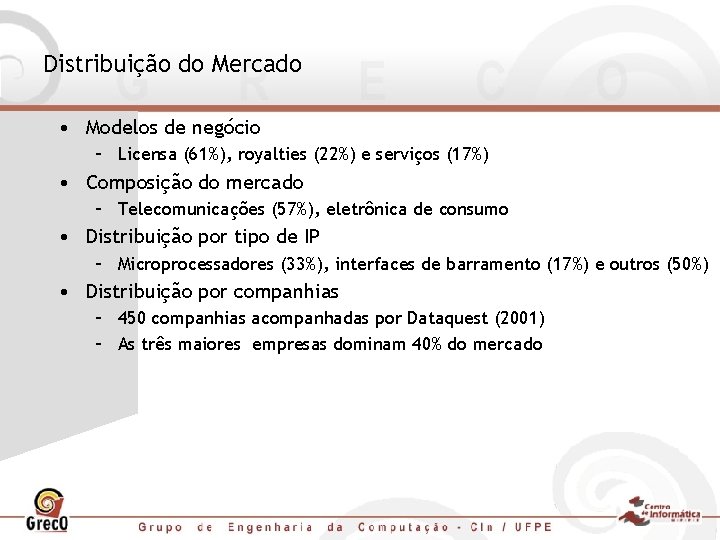

Distribuição do Mercado • Modelos de negócio – Licensa (61%), royalties (22%) e serviços (17%) • Composição do mercado – Telecomunicações (57%), eletrônica de consumo • Distribuição por tipo de IP – Microprocessadores (33%), interfaces de barramento (17%) e outros (50%) • Distribuição por companhias – 450 companhias acompanhadas por Dataquest (2001) – As três maiores empresas dominam 40% do mercado

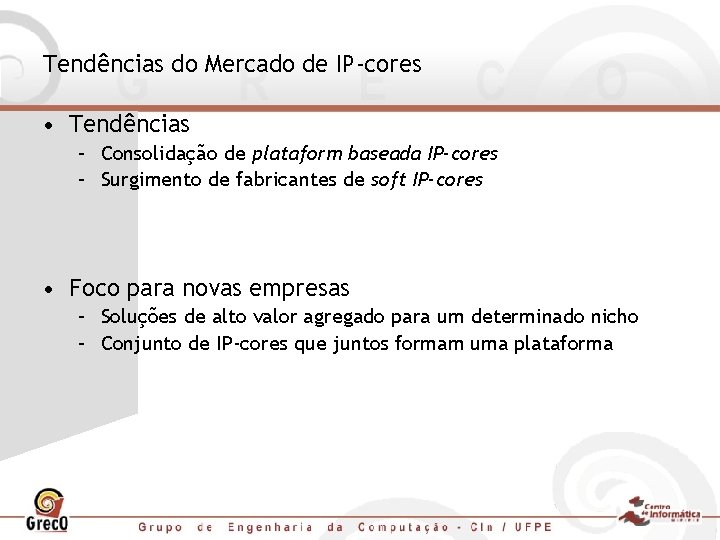

Tendências do Mercado de IP-cores • Tendências – Consolidação de plataform baseada IP-cores – Surgimento de fabricantes de soft IP-cores • Foco para novas empresas – Soluções de alto valor agregado para um determinado nicho – Conjunto de IP-cores que juntos formam uma plataforma

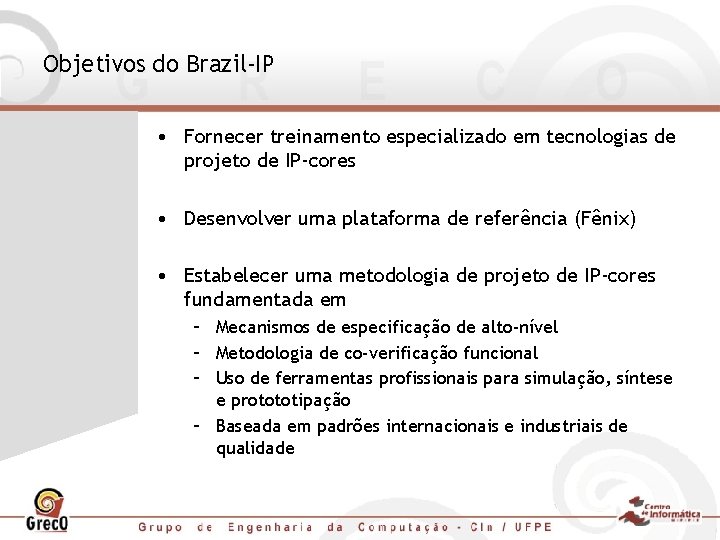

Objetivos do Brazil-IP • Fornecer treinamento especializado em tecnologias de projeto de IP-cores • Desenvolver uma plataforma de referência (Fênix) • Estabelecer uma metodologia de projeto de IP-cores fundamentada em – Mecanismos de especificação de alto-nível – Metodologia de co-verificação funcional – Uso de ferramentas profissionais para simulação, síntese e protototipação – Baseada em padrões internacionais e industriais de qualidade

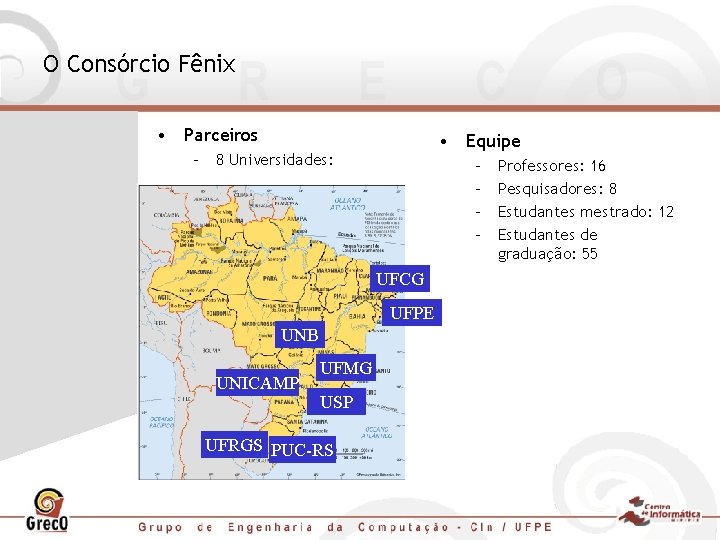

O Consórcio Fênix • Parceiros • Equipe – 8 Universidades: – – UFCG UFPE UNB UNICAMP UFMG USP UFRGS PUC-RS Professores: 16 Pesquisadores: 8 Estudantes mestrado: 12 Estudantes de graduação: 55

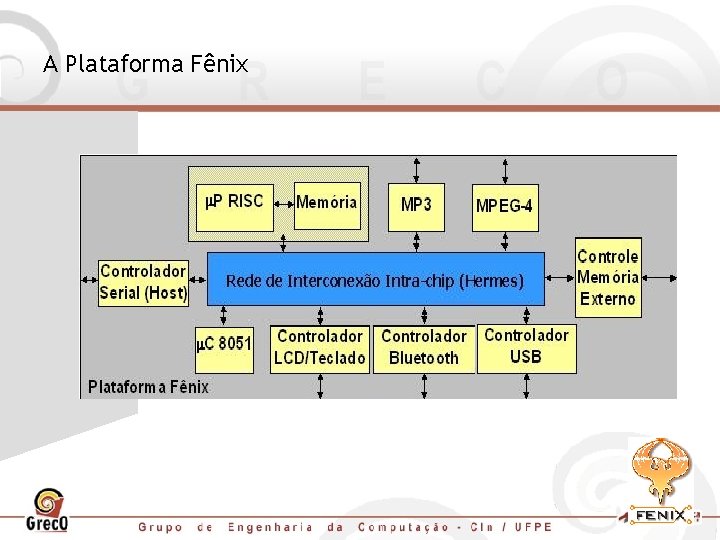

A Plataforma Fênix

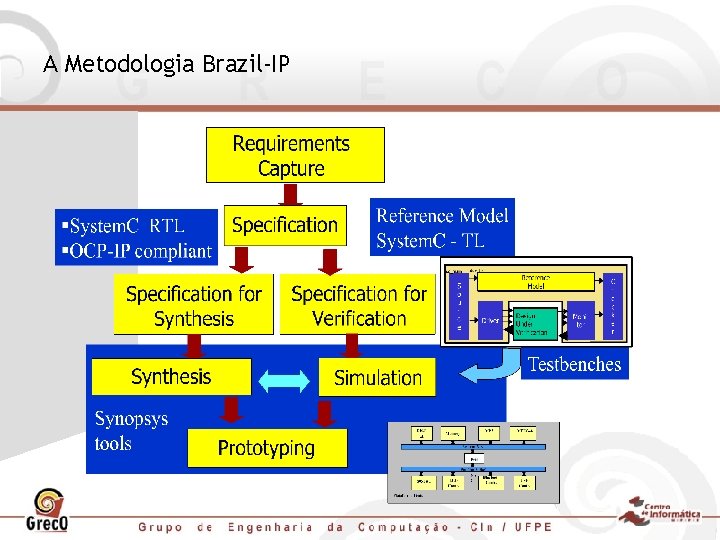

A Metodologia Brazil-IP

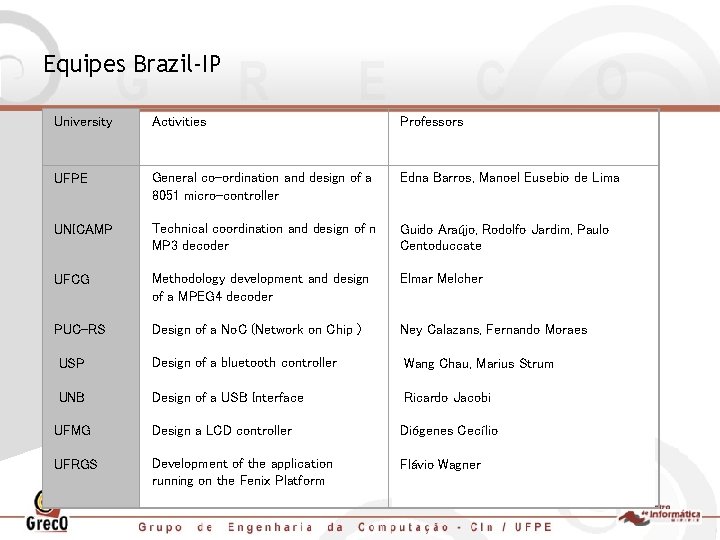

Equipes Brazil-IP University Activities Professors UFPE General co-ordination and design of a 8051 micro-controller Edna Barros, Manoel Eusebio de Lima UNICAMP Technical coordination and design of n MP 3 decoder Guido Araújo, Rodolfo Jardim, Paulo Centoduccate UFCG Methodology development and design of a MPEG 4 decoder Elmar Melcher PUC-RS Design of a No. C (Network on Chip ) Ney Calazans, Fernando Moraes USP Design of a bluetooth controller Wang Chau, Marius Strum UNB Design of a USB Interface Ricardo Jacobi UFMG Design a LCD controller Diógenes Cecílio UFRGS Development of the application running on the Fenix Platform Flávio Wagner

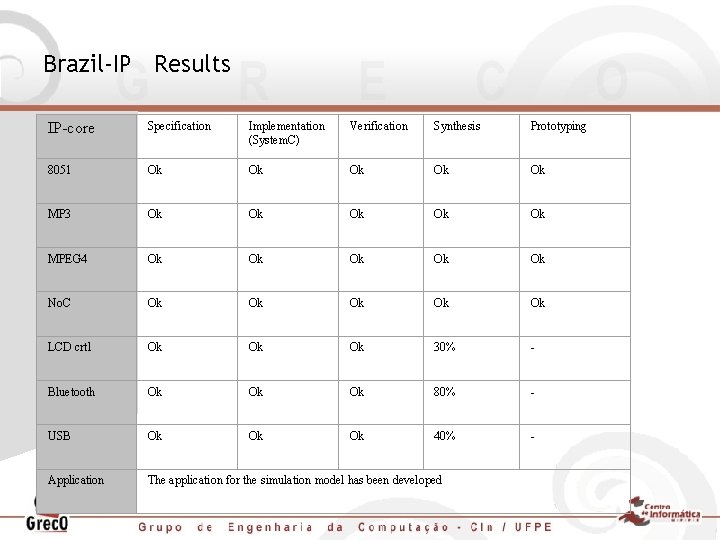

Brazil-IP Results IP-core Specification Implementation (System. C) Verification Synthesis Prototyping 8051 Ok Ok Ok MP 3 Ok Ok Ok MPEG 4 Ok Ok Ok No. C Ok Ok Ok LCD crtl Ok Ok Ok 30% - Bluetooth Ok Ok Ok 80% - USB Ok Ok Ok 40% - Application The application for the simulation model has been developed

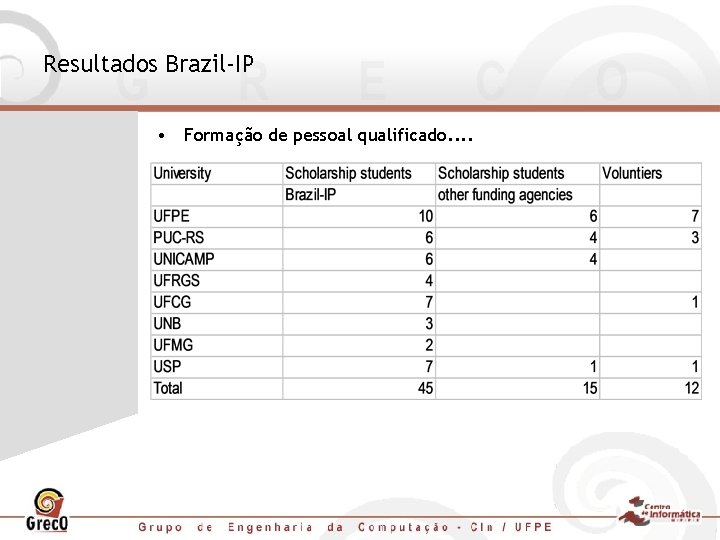

Resultados Brazil-IP • Formação de pessoal qualificado. .

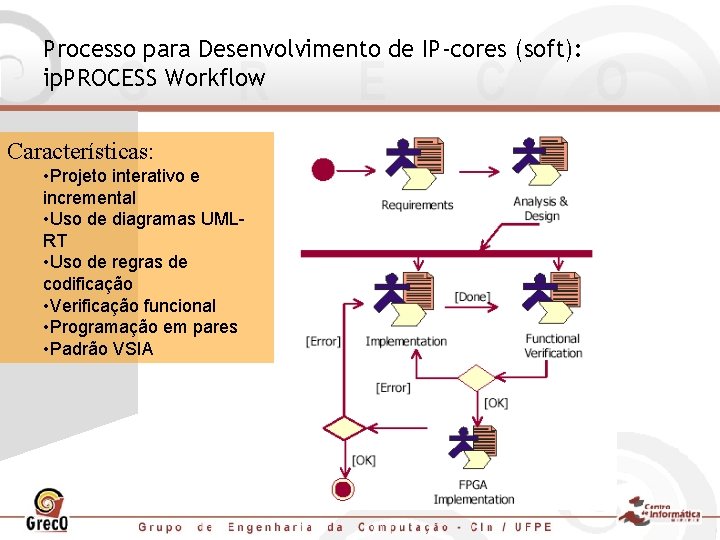

Processo para Desenvolvimento de IP-cores (soft): ip. PROCESS Workflow Características: • Projeto interativo e incremental • Uso de diagramas UMLRT • Uso de regras de codificação • Verificação funcional • Programação em pares • Padrão VSIA

Programa CI Brasil • Lançado em Junho 2004 • Objetivo – Criação de cinco design-houses – Expansão do Projeto Brazil-IP – Formação Especializada em projeto de sistemas embarcados

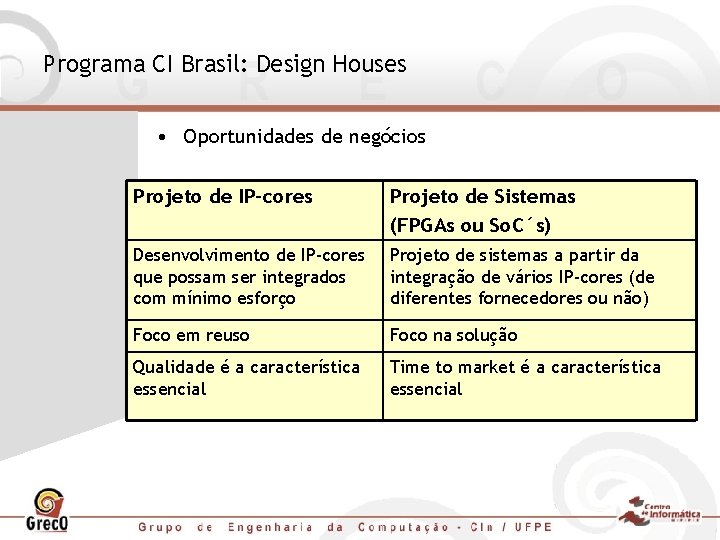

Programa CI Brasil: Design Houses • Oportunidades de negócios Projeto de IP-cores Projeto de Sistemas (FPGAs ou So. C´s) Desenvolvimento de IP-cores que possam ser integrados com mínimo esforço Projeto de sistemas a partir da integração de vários IP-cores (de diferentes fornecedores ou não) Foco em reuso Foco na solução Qualidade é a característica essencial Time to market é a característica essencial

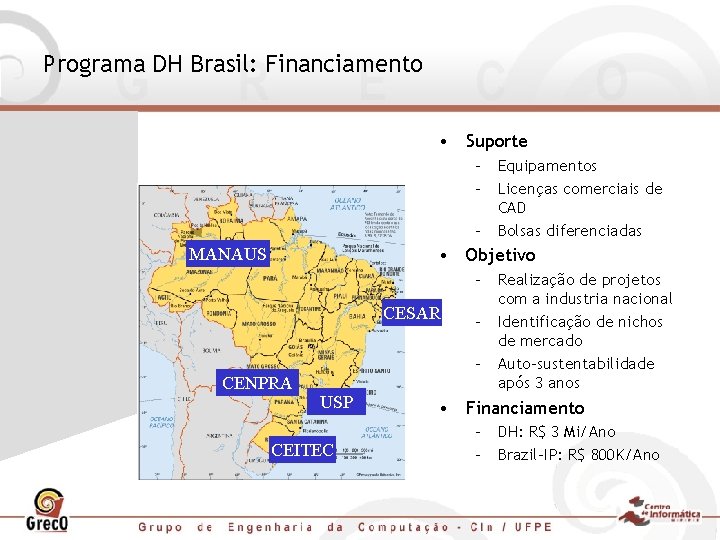

Programa DH Brasil: Financiamento • Suporte – Equipamentos – Licenças comerciais de CAD – Bolsas diferenciadas MANAUS • Objetivo CESAR CENPRA USP CEITEC – Realização de projetos com a industria nacional – Identificação de nichos de mercado – Auto-sustentabilidade após 3 anos • Financiamento – DH: R$ 3 Mi/Ano – Brazil-IP: R$ 800 K/Ano

Conclusões • Tendências na área de Sistemas Embarcados – Projetos Nível de Sistema – Desenvolvimento de IP-cores de qualidade • Aplicação específica • Agregação de valor • Outsourcing – Desenvolvimento de plataformas de simulação • Modelos em alto nível de abstração • Mecanismos de análise • Suporte a software embarcado – Desenvolvimento de soluções • Plataformas • Software embarcado

Conclusões • Iniciativas e Suporte – Projeto Brazil-IP • Formação de recursos humanos • Projetos com qualidade – Programa DH Brasil • Suportar cooperação com a indústria • Descoberta de vocações e nichos de mercado – Projeto Arch. C • Desenvolvimento de plataformas de simulação

- Slides: 69