Design of RF CMOS Low Noise Amplifiers Using

- Slides: 25

Design of RF CMOS Low Noise Amplifiers Using a Current Based MOSFET Model Virgínia Helena Varotto Baroncini Oscar da Costa Gouveia Filho

OUTLINE 1. 2. 3. 4. 5. 6. Introduction MOSFET Model High-Frequency Noise Model LNA Analysis LNA Design Example Conclusion

Introduction • Submicrometer CMOS technology integration of RF circuits. allows the • Low voltage and low power operation → moderate inversion • Model valid from weak to strong inversion

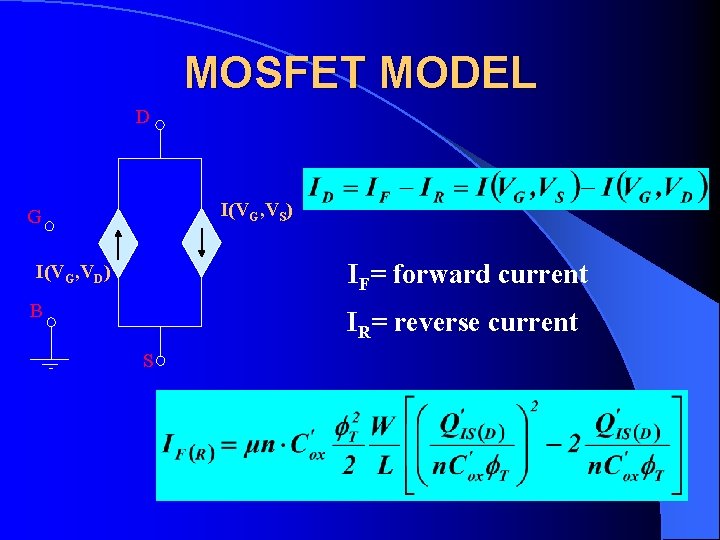

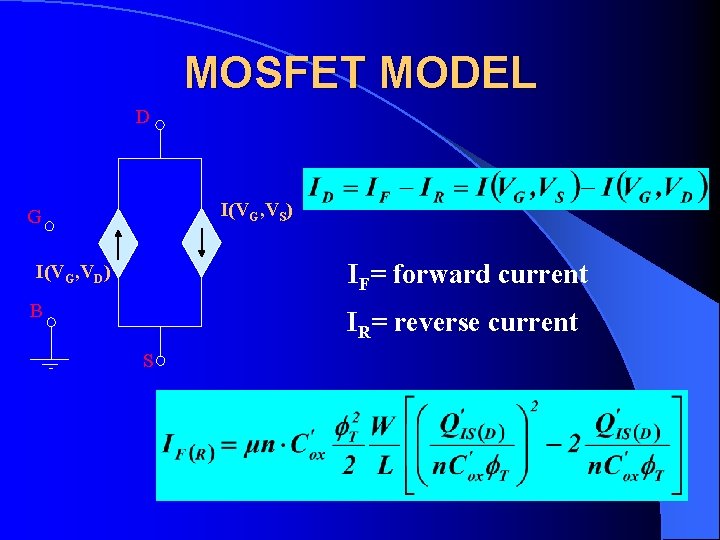

MOSFET MODEL D I(VG, VS) G I(VG, VD) IF= forward current B IR= reverse current S

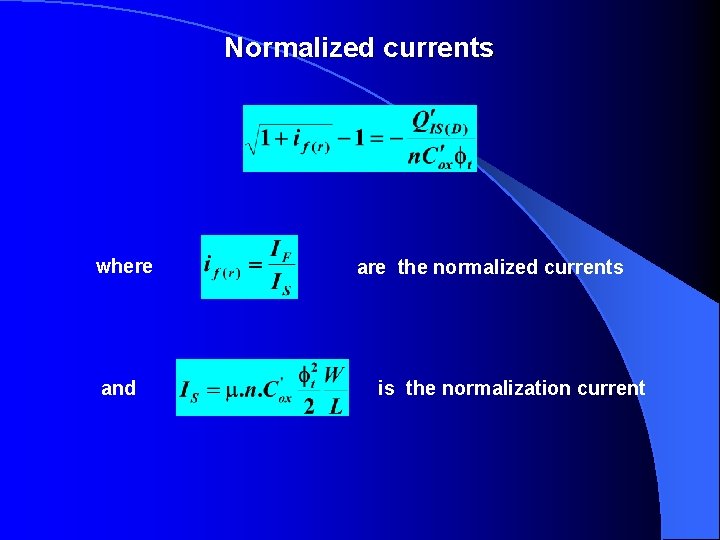

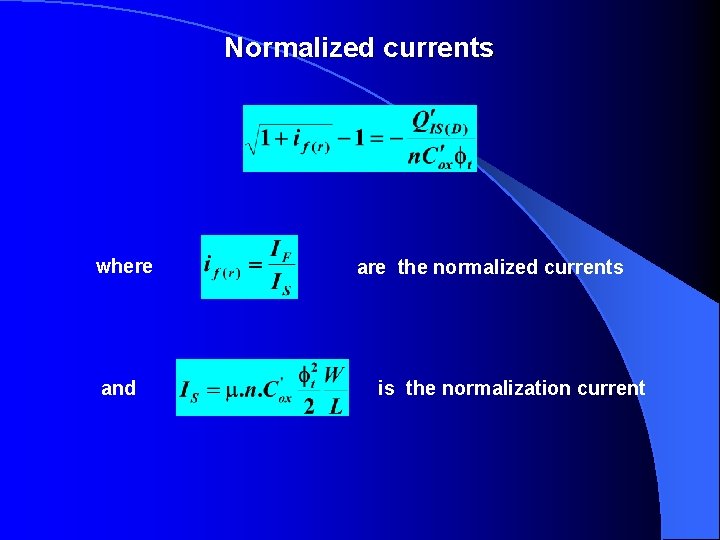

Normalized currents where and are the normalized currents is the normalization current

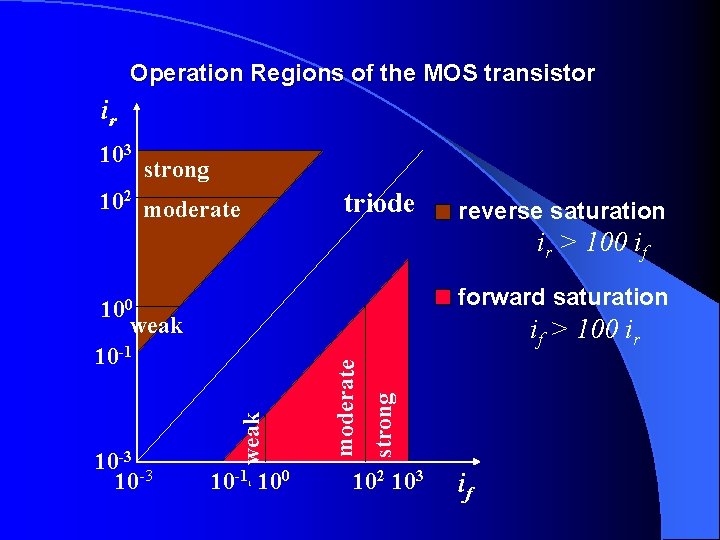

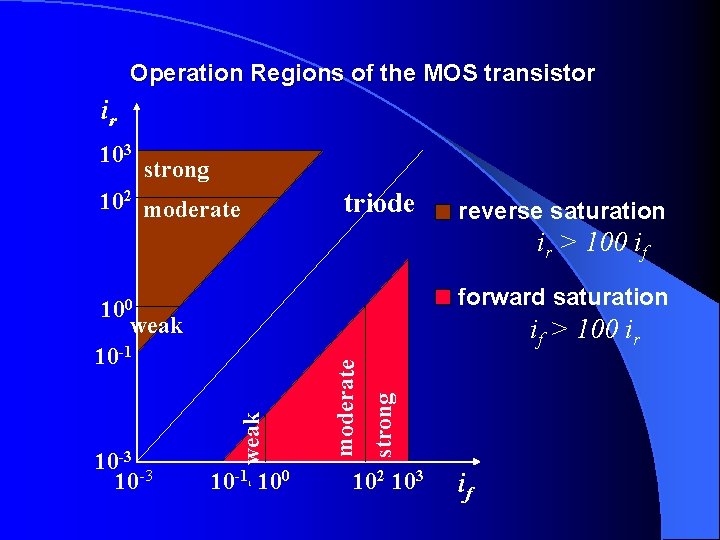

Operation Regions of the MOS transistor ir 103 strong 102 moderate triode reverse saturation ir > 100 if forward saturation 100 weak 10 -1 100 1 strong moderate weak 10 -3 if > 100 ir 102 103 if

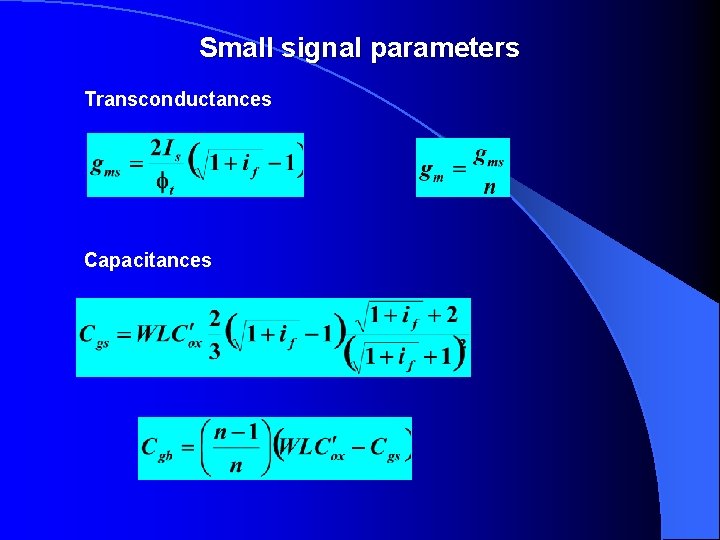

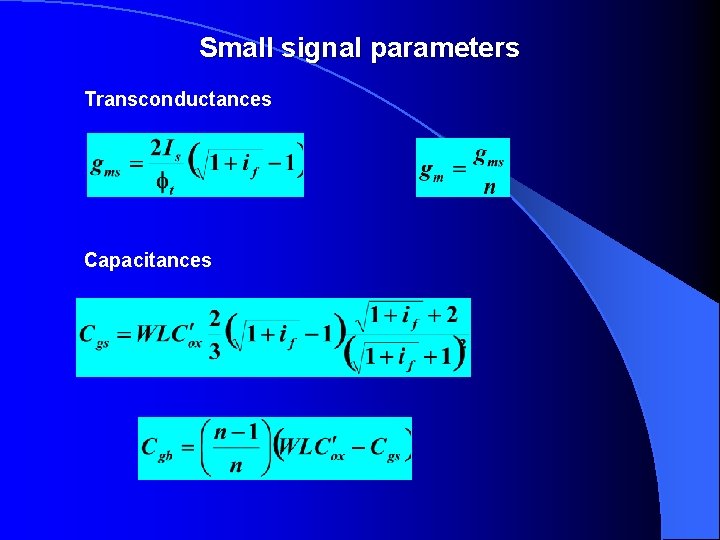

Small signal parameters Transconductances Capacitances

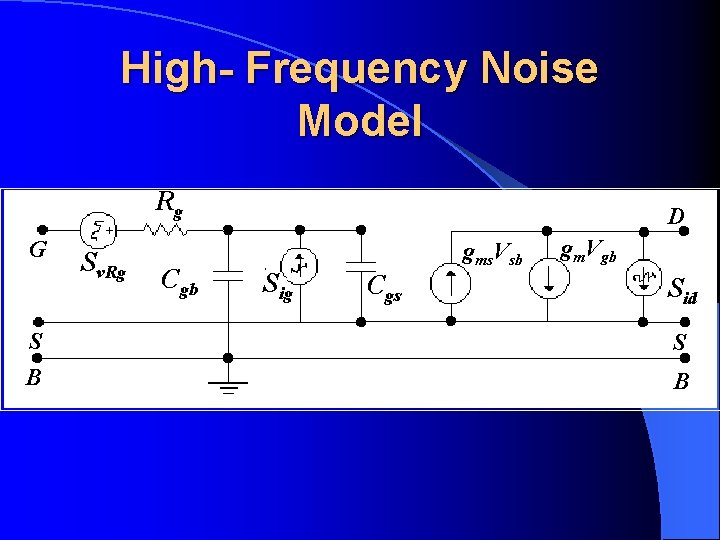

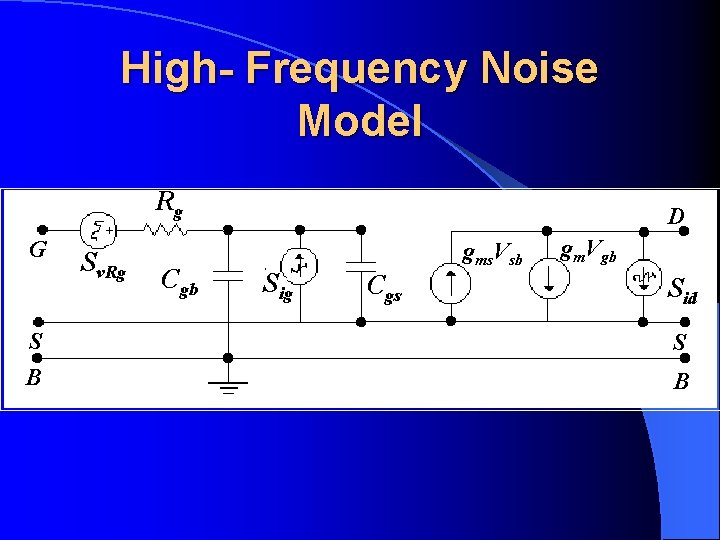

High- Frequency Noise Model Rg G S B Sv. Rg Cgb D Sig gms. Vsb Cgs gm. Vgb Sid S B

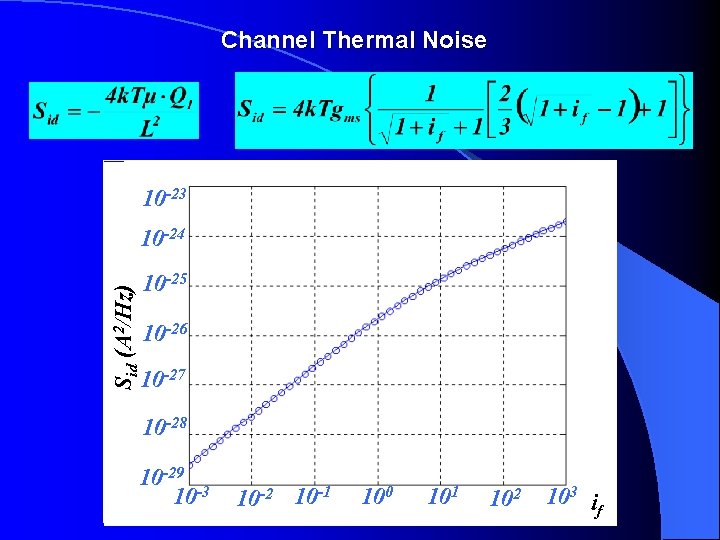

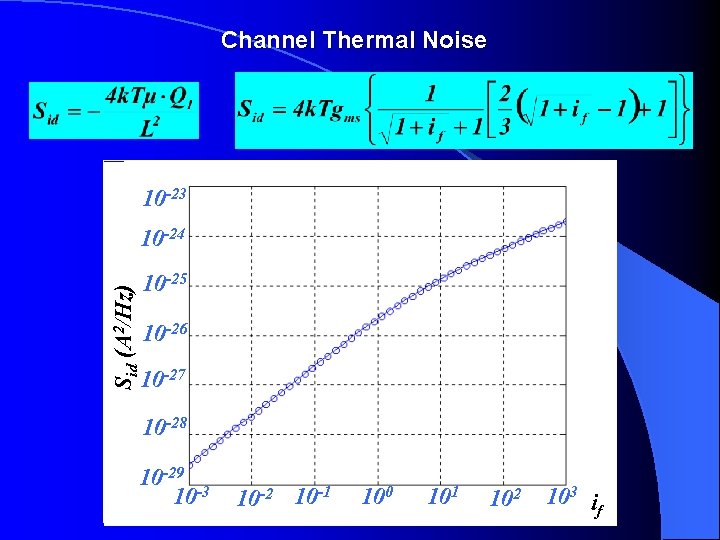

Channel Thermal Noise 10 -23 Sid (A 2/Hz) 10 -24 10 -25 10 -26 10 -27 10 -28 10 -29 10 -3 10 -2 10 -1 100 101 102 103 if

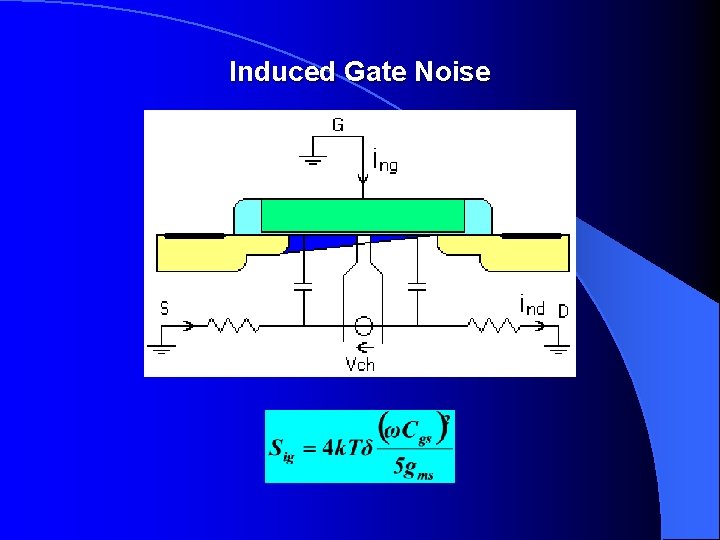

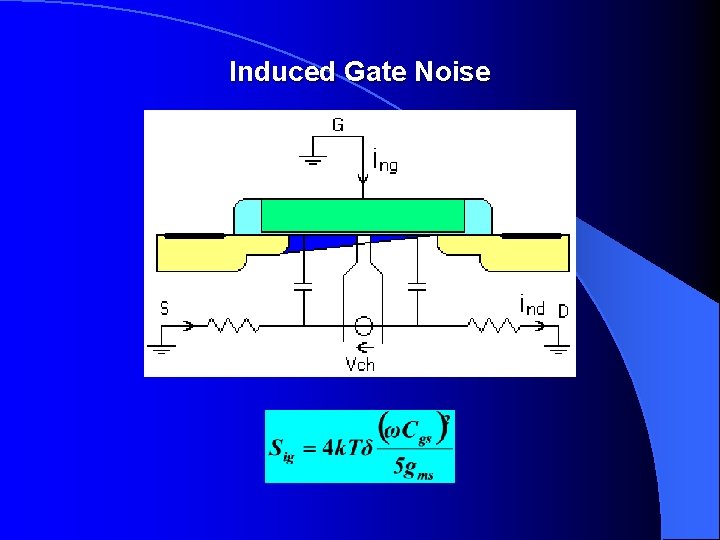

Induced Gate Noise

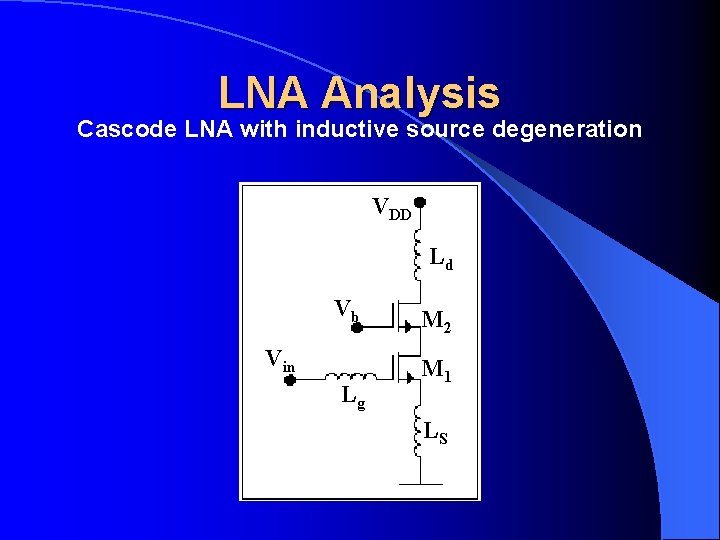

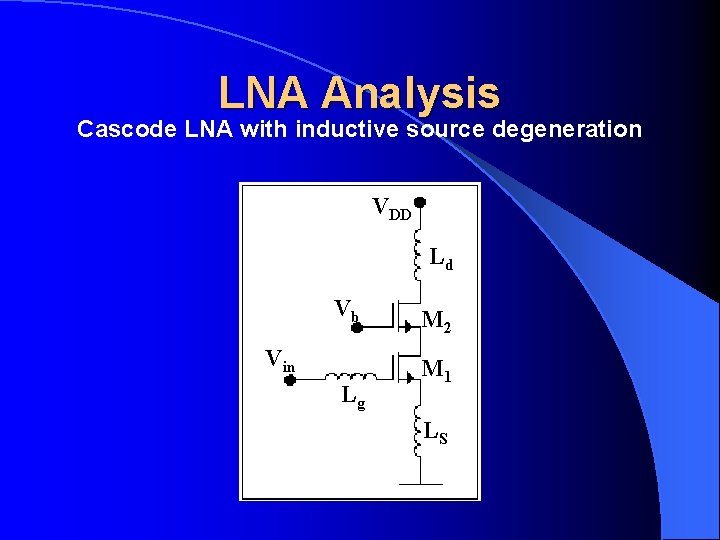

LNA Analysis Cascode LNA with inductive source degeneration VDD Ld Vb Vin Lg M 2 M 1 LS

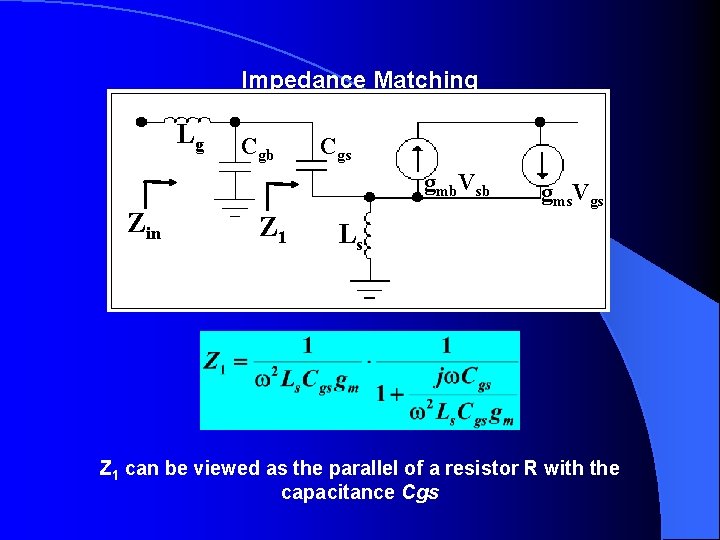

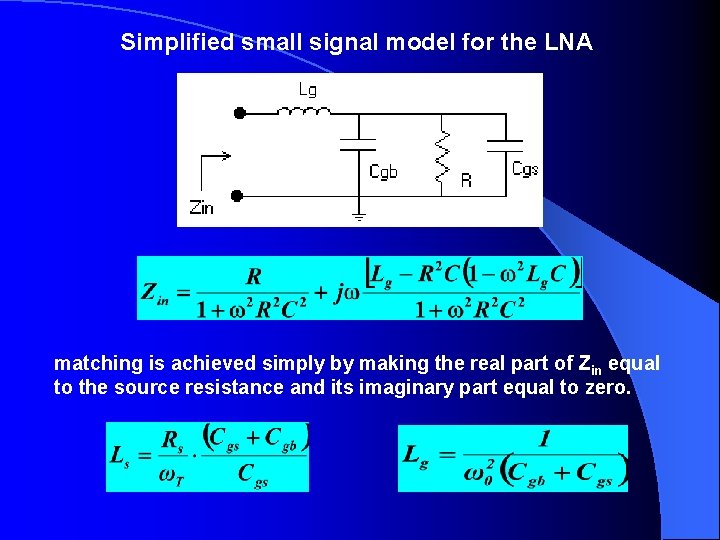

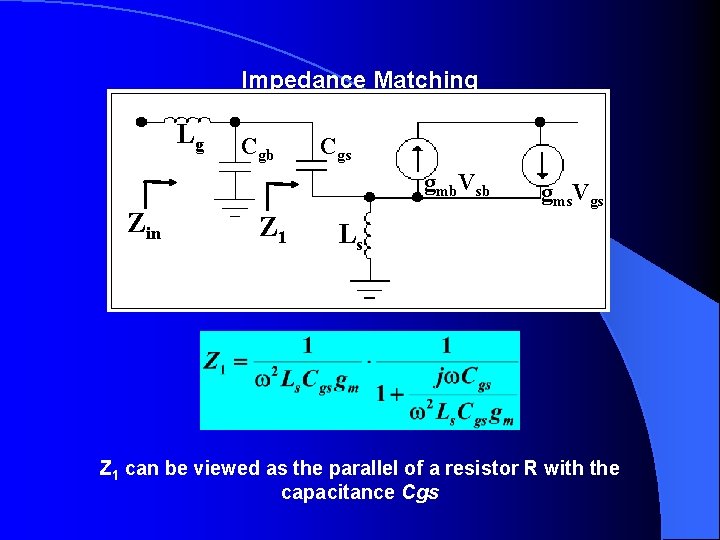

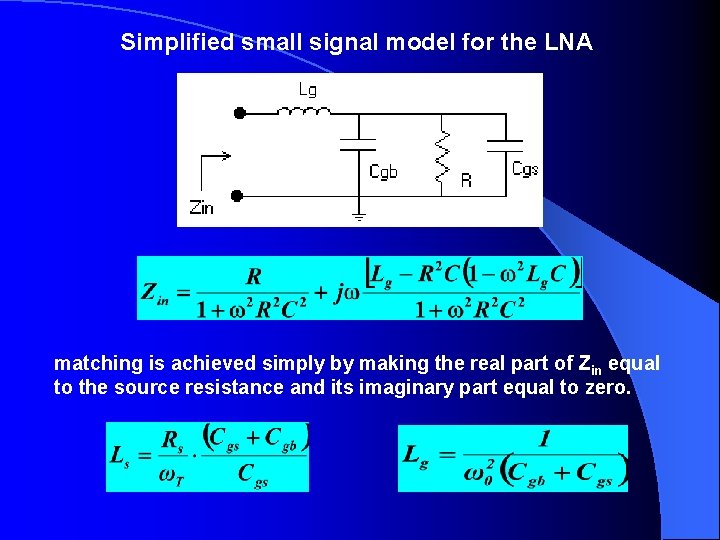

Impedance Matching Lg Cgb Cgs gmb. Vsb Zin Z 1 gms. Vgs Ls Z 1 can be viewed as the parallel of a resistor R with the capacitance Cgs

Simplified small signal model for the LNA matching is achieved simply by making the real part of Zin equal to the source resistance and its imaginary part equal to zero.

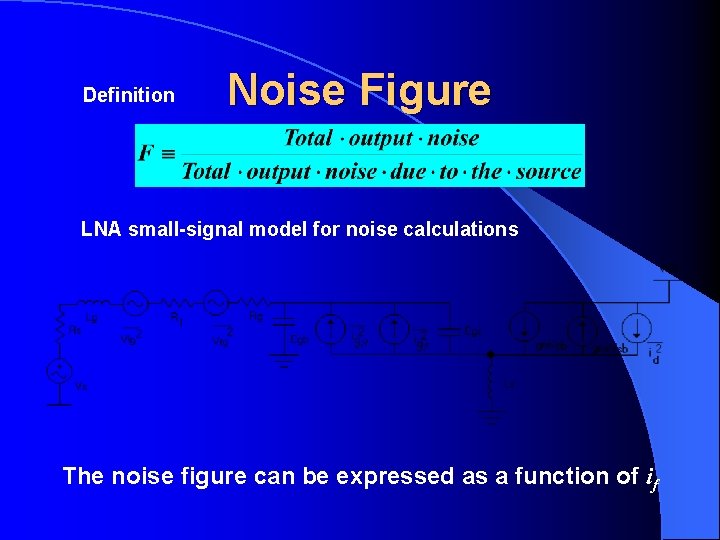

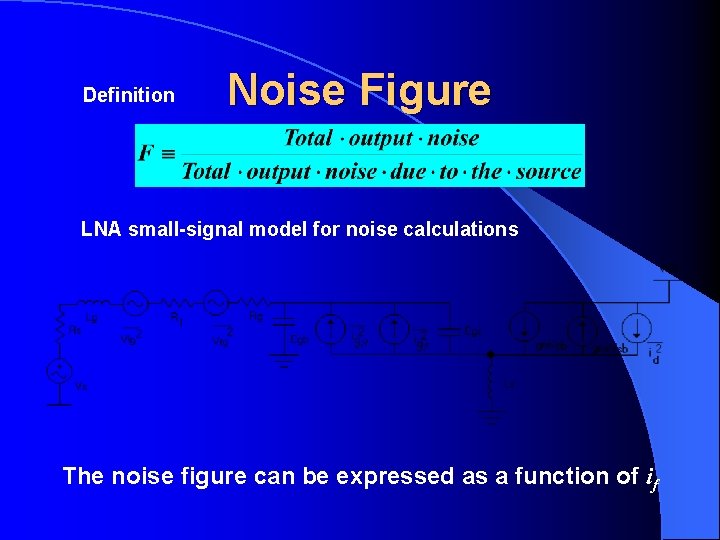

Definition Noise Figure LNA small-signal model for noise calculations The noise figure can be expressed as a function of if

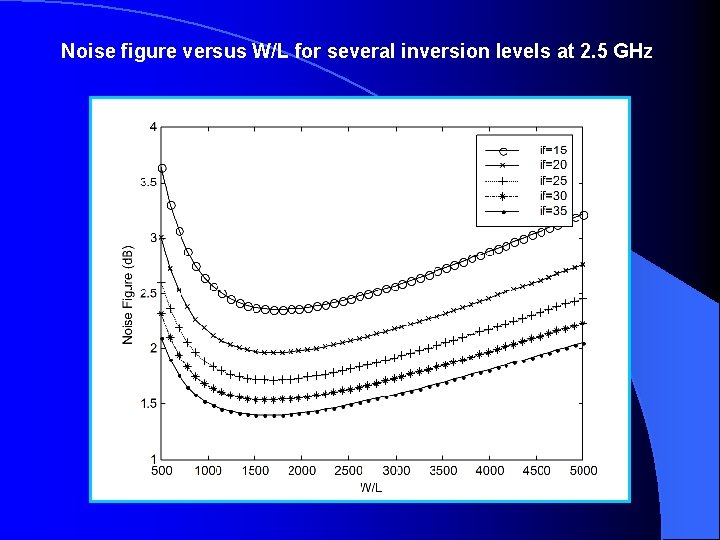

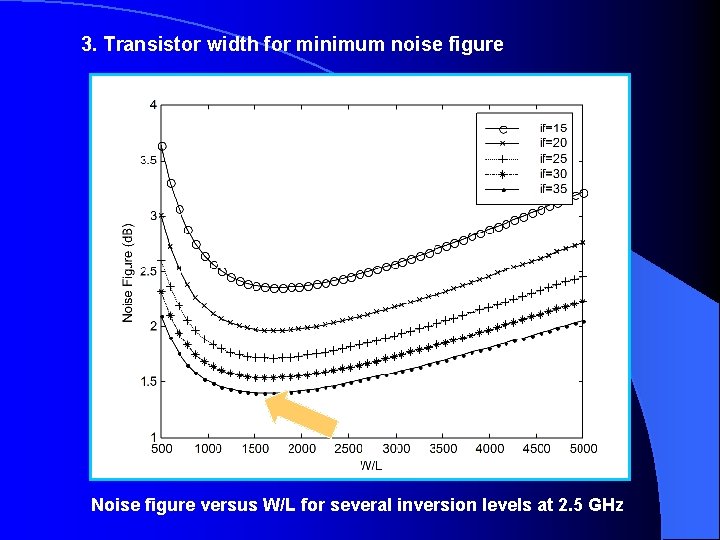

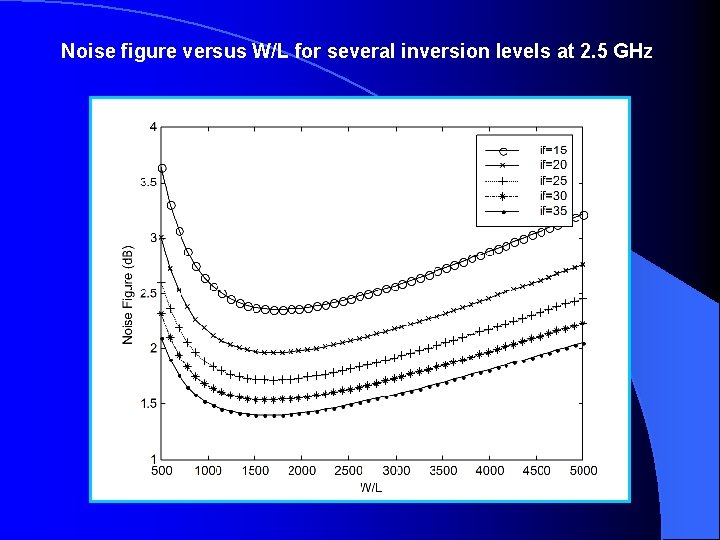

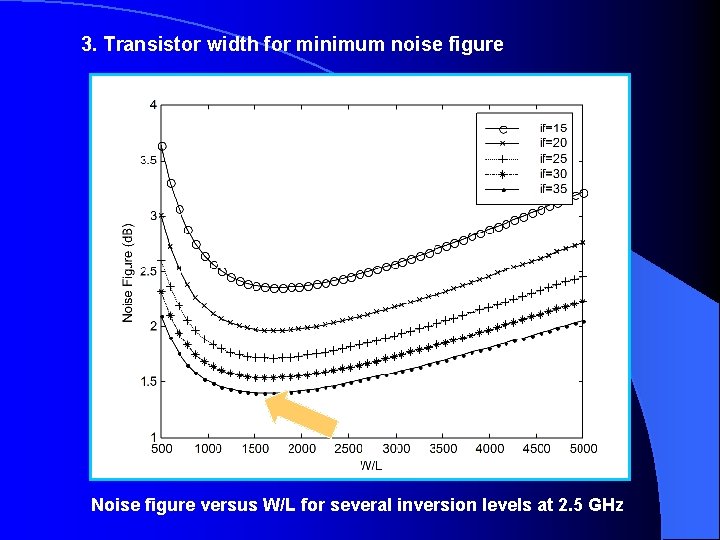

Noise figure versus W/L for several inversion levels at 2. 5 GHz

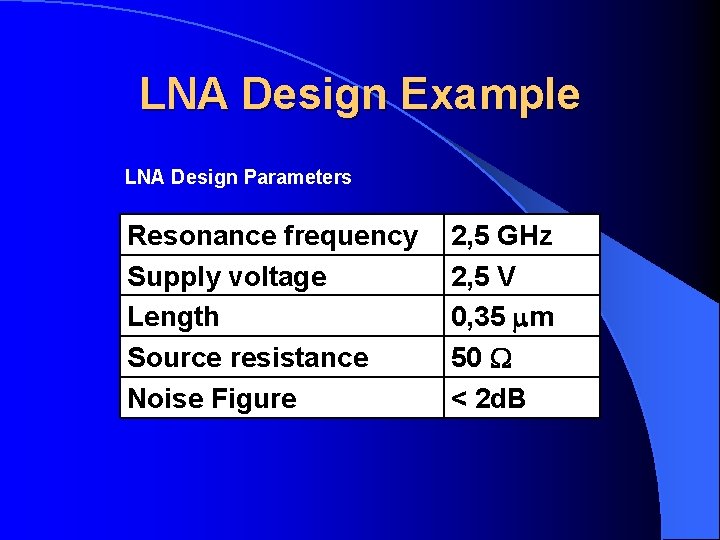

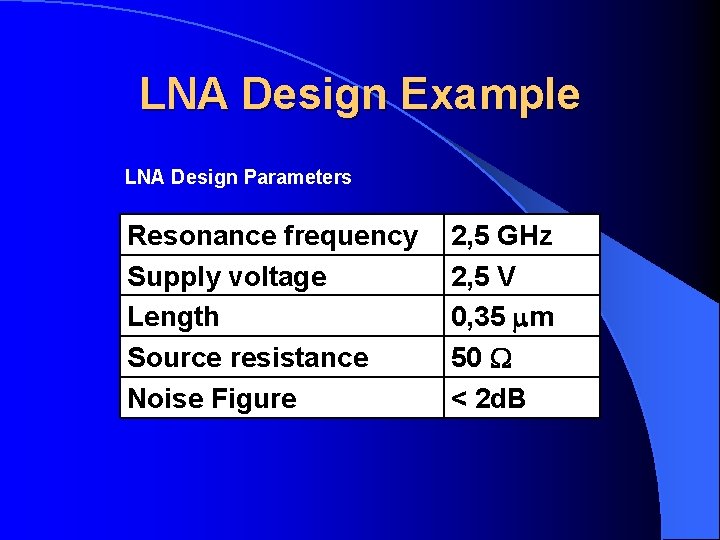

LNA Design Example LNA Design Parameters Resonance frequency Supply voltage Length Source resistance Noise Figure 2, 5 GHz 2, 5 V 0, 35 m 50 < 2 d. B

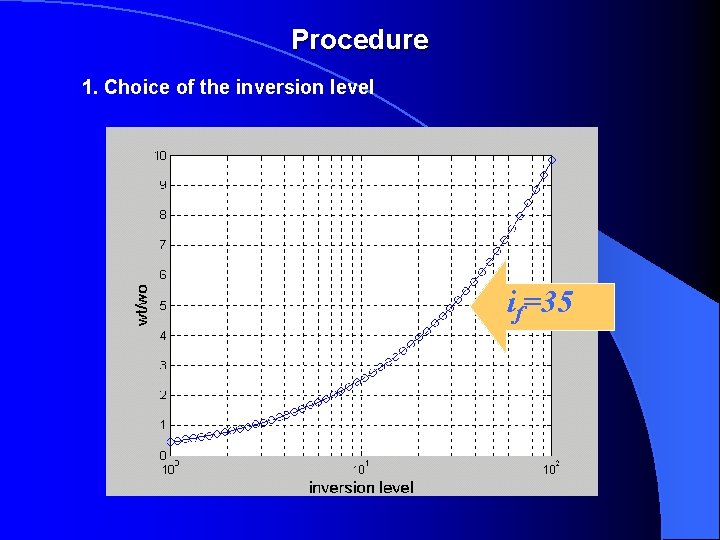

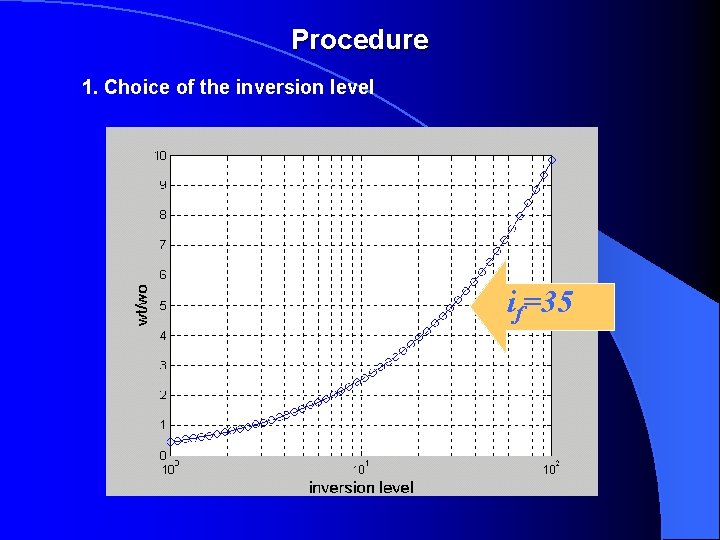

Procedure 1. Choice of the inversion level if=35

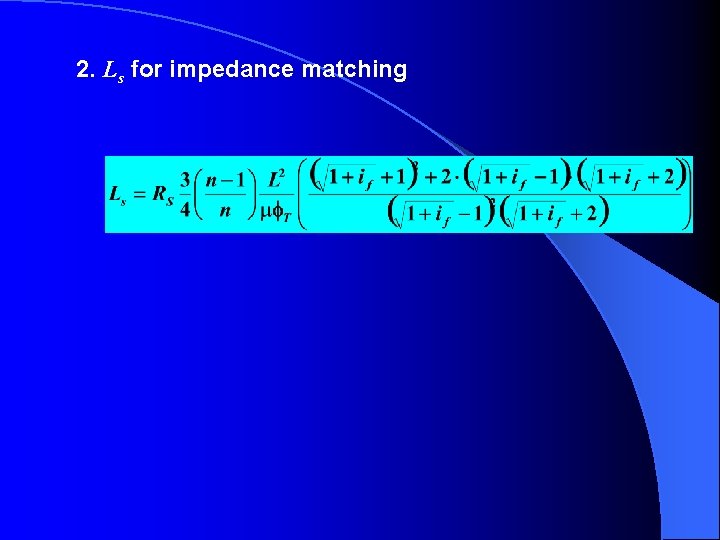

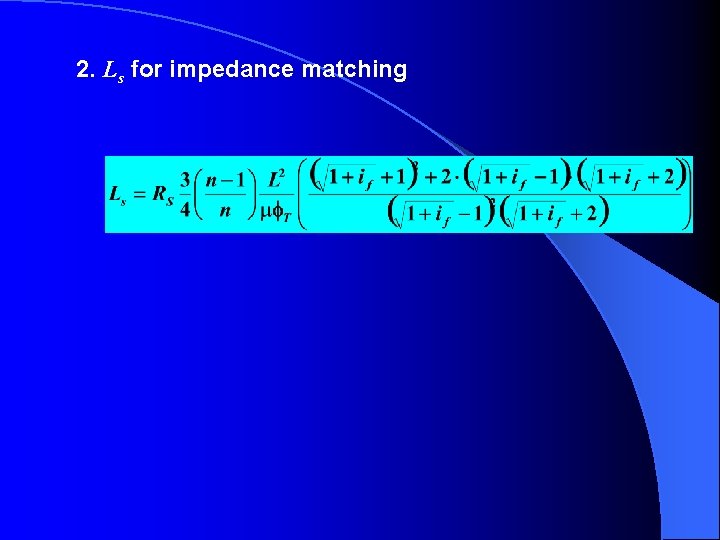

2. Ls for impedance matching

3. Transistor width for minimum noise figure Noise figure versus W/L for several inversion levels at 2. 5 GHz

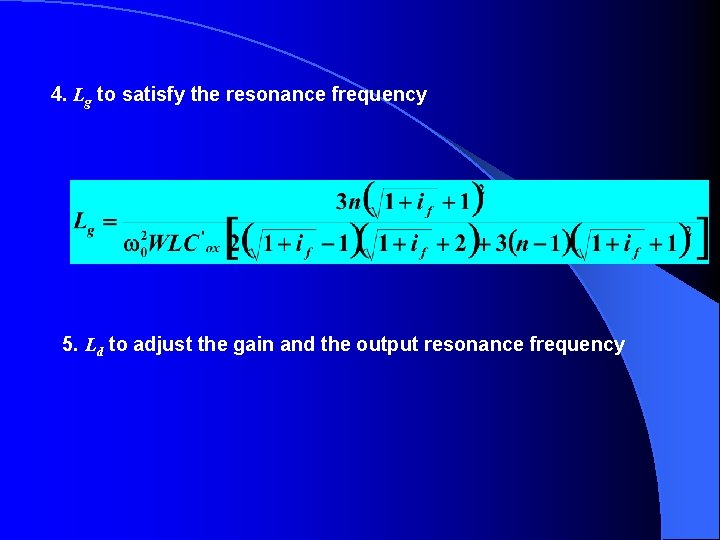

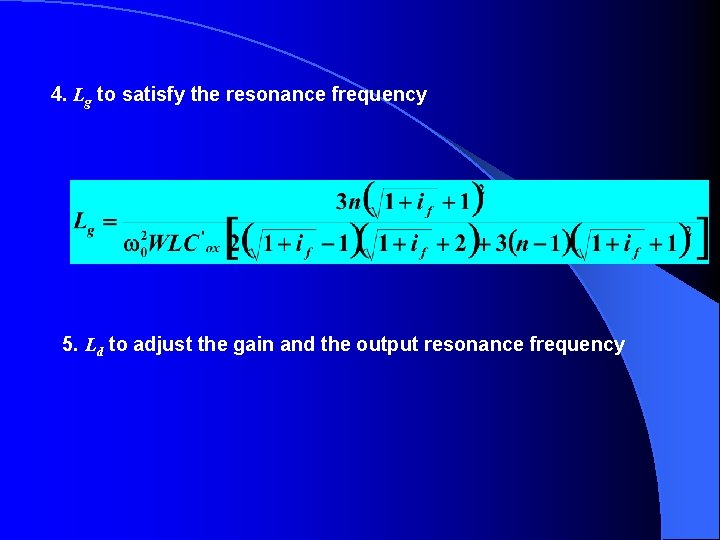

4. Lg to satisfy the resonance frequency 5. Ld to adjust the gain and the output resonance frequency

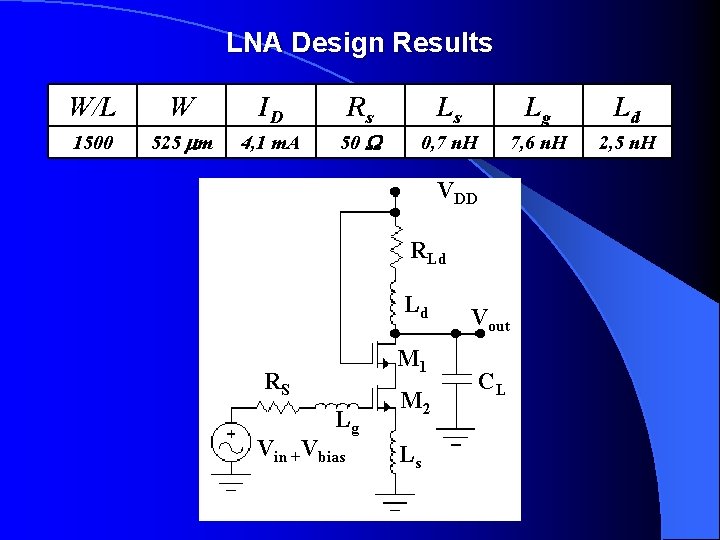

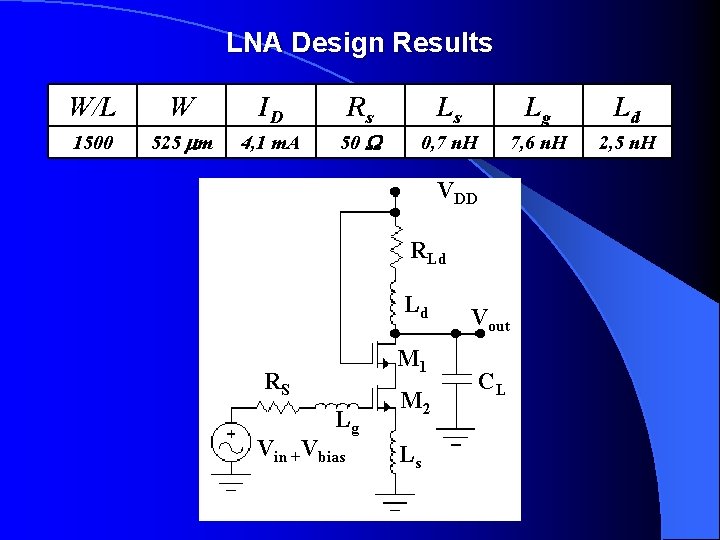

LNA Design Results W/L W ID Rs Ls Lg Ld 1500 525 m 4, 1 m. A 50 0, 7 n. H 7, 6 n. H 2, 5 n. H VDD RLd Ld M 1 RS Lg Vin +Vbias M 2 Ls Vout CL

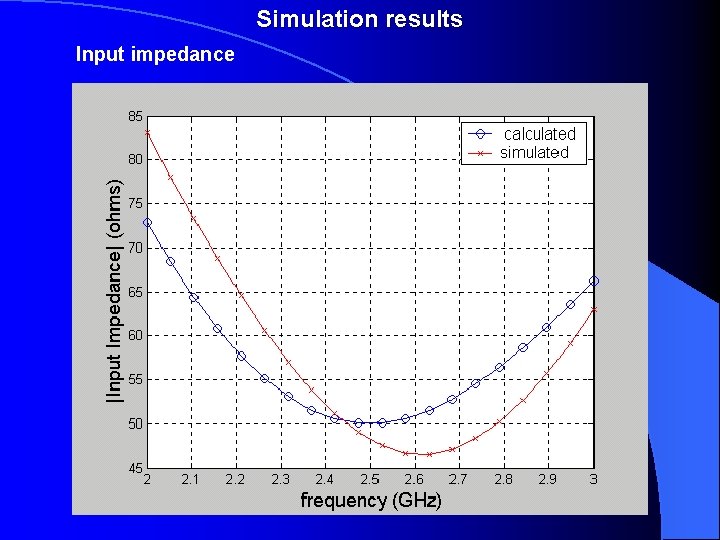

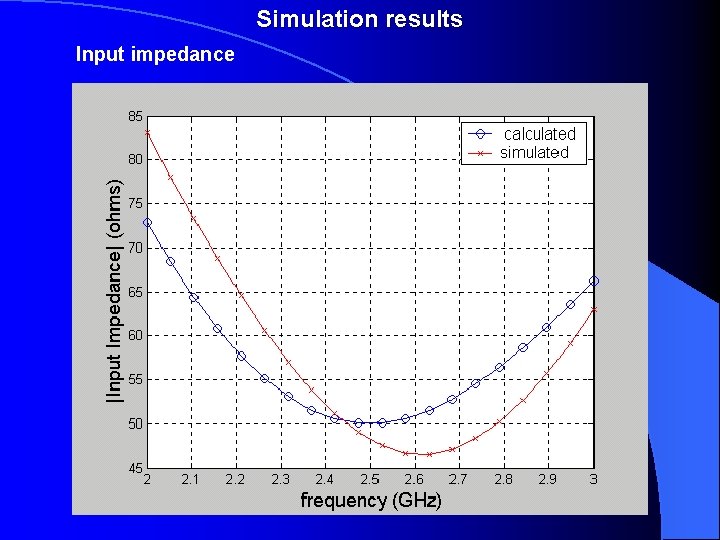

Simulation results Input impedance

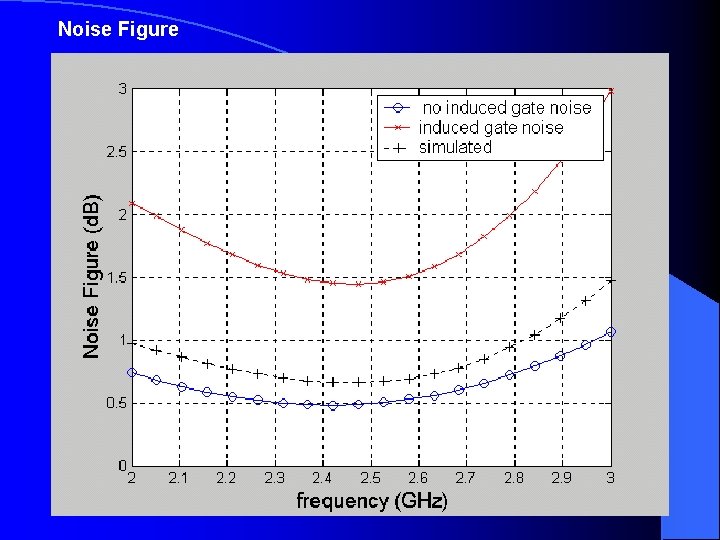

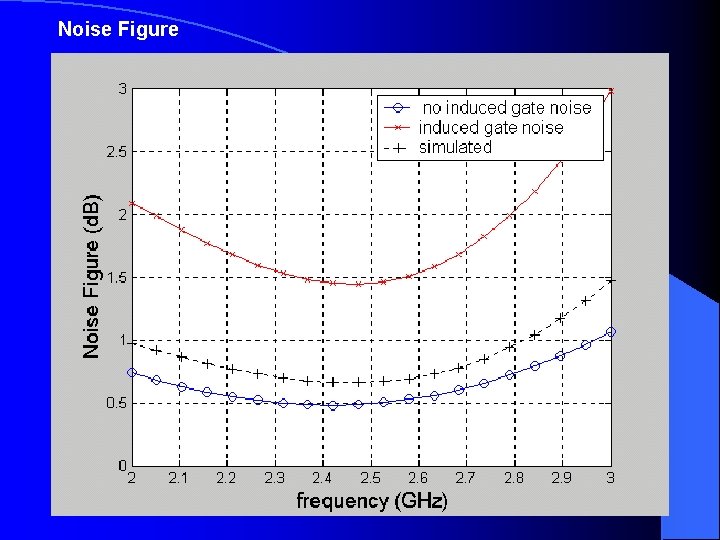

Noise Figure

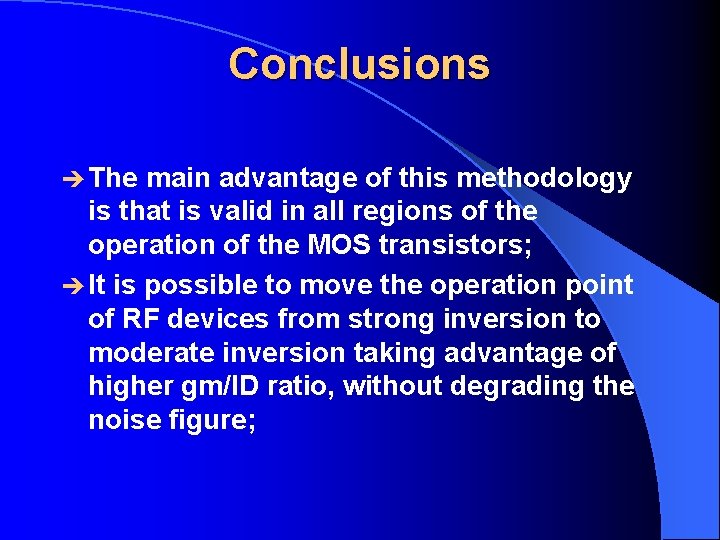

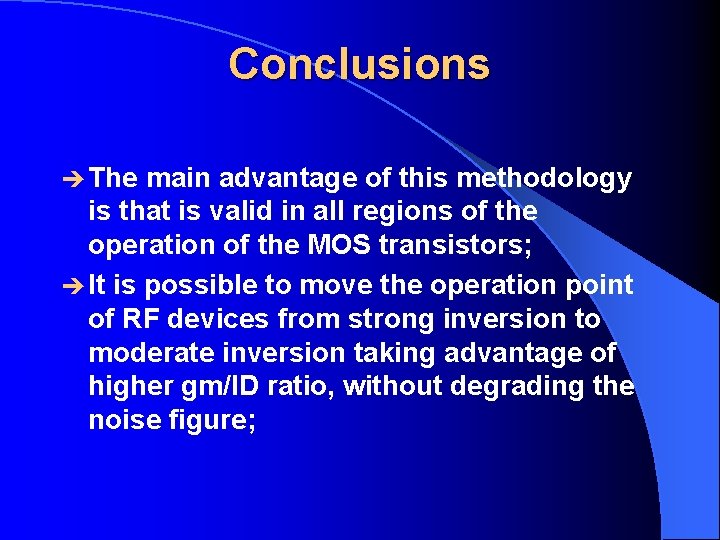

Conclusions è The main advantage of this methodology is that is valid in all regions of the operation of the MOS transistors; è It is possible to move the operation point of RF devices from strong inversion to moderate inversion taking advantage of higher gm/ID ratio, without degrading the noise figure;