Design of High Performance Pattern Matching Engine Through

- Slides: 23

Design of High Performance Pattern Matching Engine Through Compact Deterministic Finite Automata Authors: Piyachon, P. Yan Luo Publisher: DAC 2008 45 th ACM, June 8 -13, 2008, Anaheim, California, USA. Present: Chia-Ming , Chuang Date: 11, 26, 2008 Department of Computer Science and Information Engineering National Cheng Kung University, Taiwan R. O. C. 1 1

Outline l l l 1. Introduction 2. Proposed schemes 3. Architecture 4. Experiments 5. Conclusion 2 2

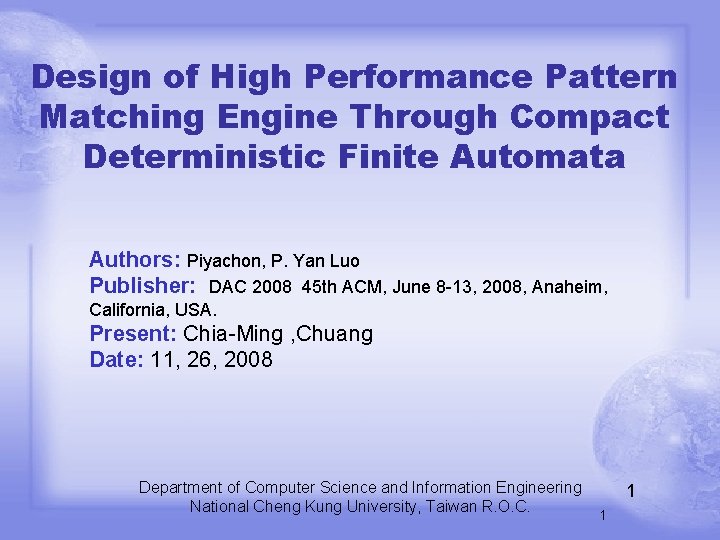

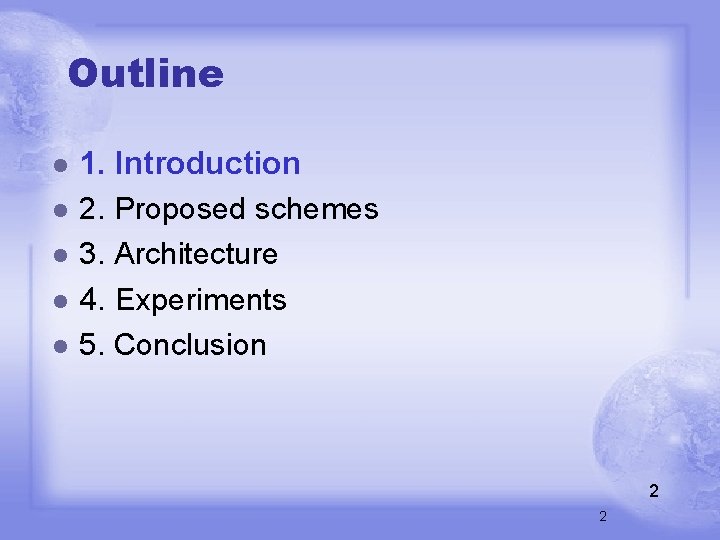

Introduction (1/5) 3 3

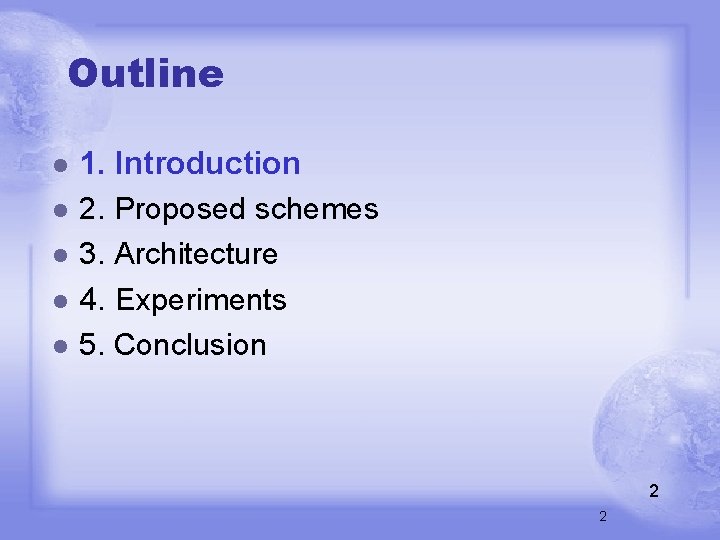

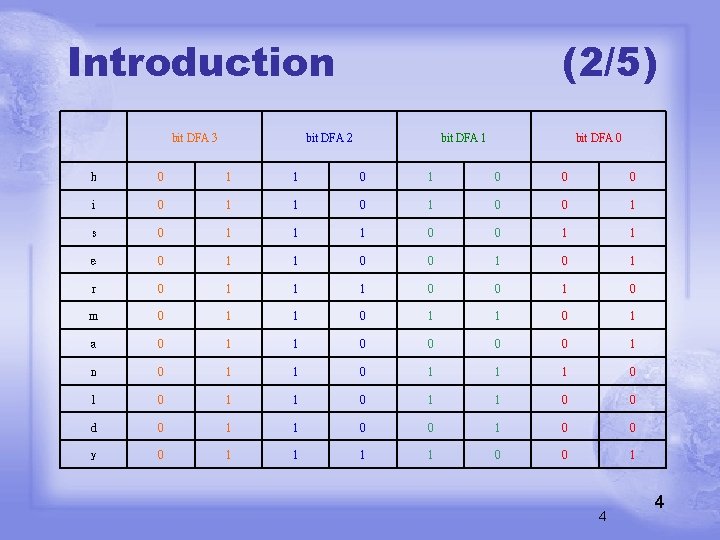

Introduction bit DFA 3 (2/5) bit DFA 2 bit DFA 1 bit DFA 0 h 0 1 1 0 0 0 i 0 1 1 0 0 1 s 0 1 1 1 0 0 1 1 e 0 1 1 0 0 1 r 0 1 1 1 0 0 1 0 m 0 1 1 0 1 a 0 1 1 0 0 1 n 0 1 1 1 0 l 0 1 1 0 0 d 0 1 1 0 0 y 0 1 1 0 0 1 4 4

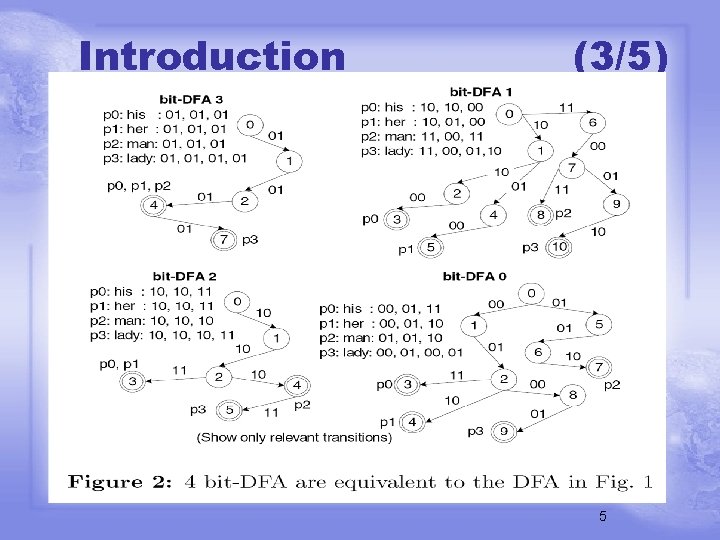

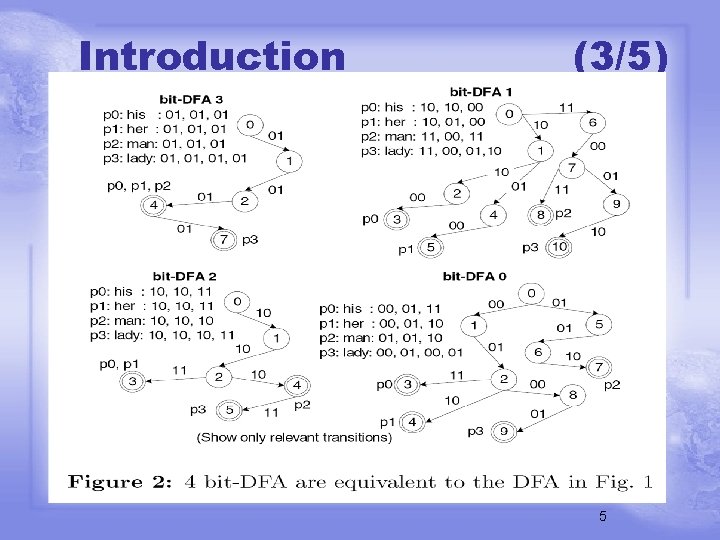

Introduction (3/5) 5

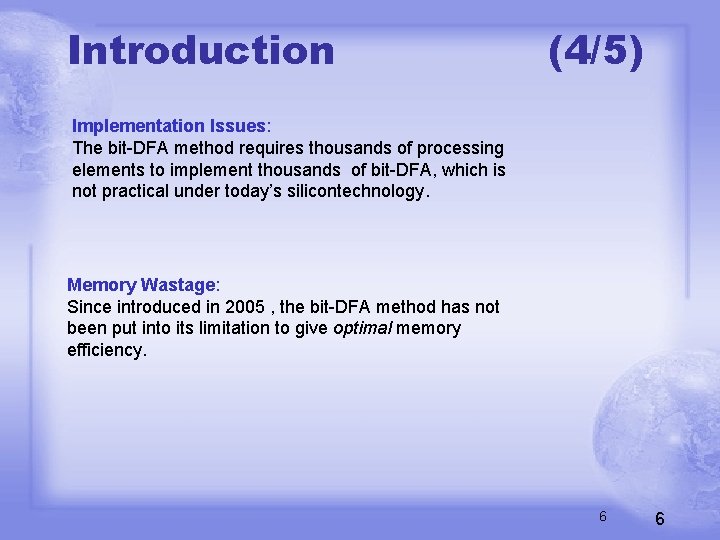

Introduction (4/5) Implementation Issues: The bit-DFA method requires thousands of processing elements to implement thousands of bit-DFA, which is not practical under today’s silicontechnology. Memory Wastage: Since introduced in 2005 , the bit-DFA method has not been put into its limitation to give optimal memory efficiency. 6 6

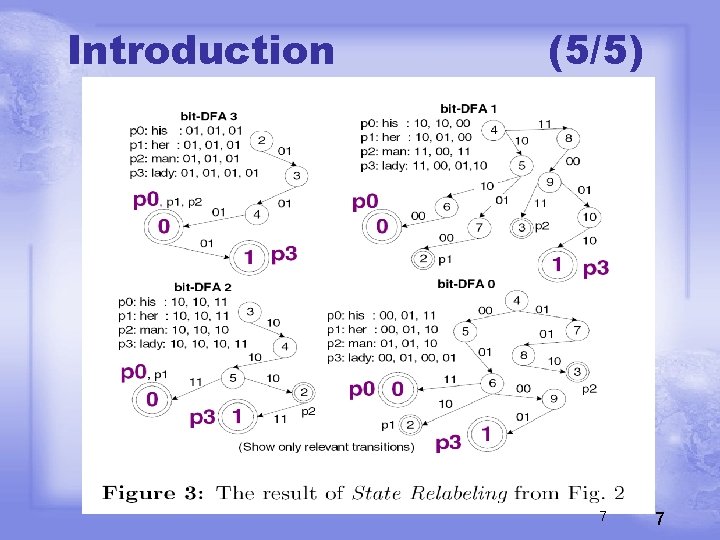

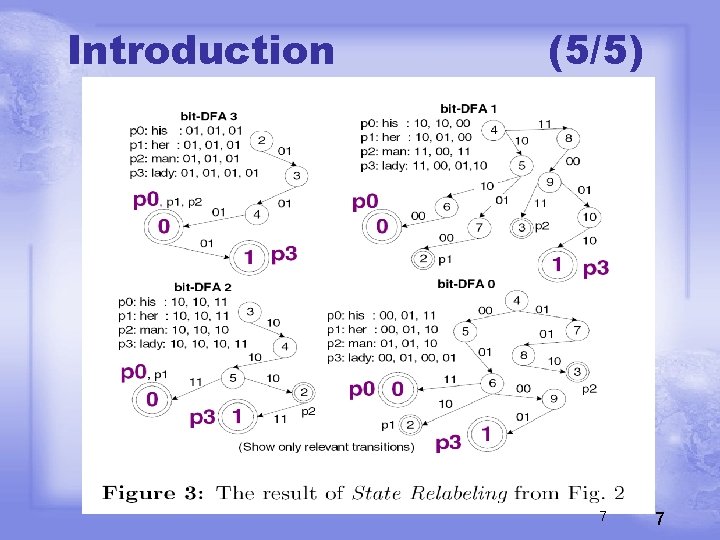

Introduction (5/5) 7 7

Outline l l l 1. Introduction 2. Proposed schemes 3. Architecture 4. Experiments 5. Conclusion 7 8

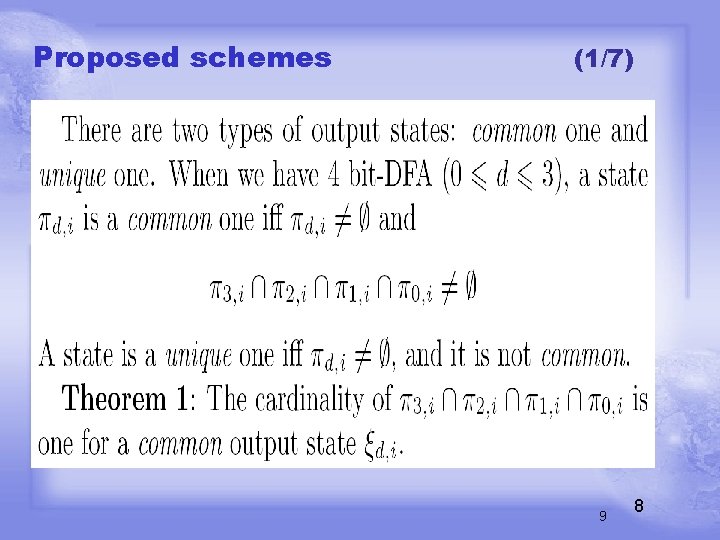

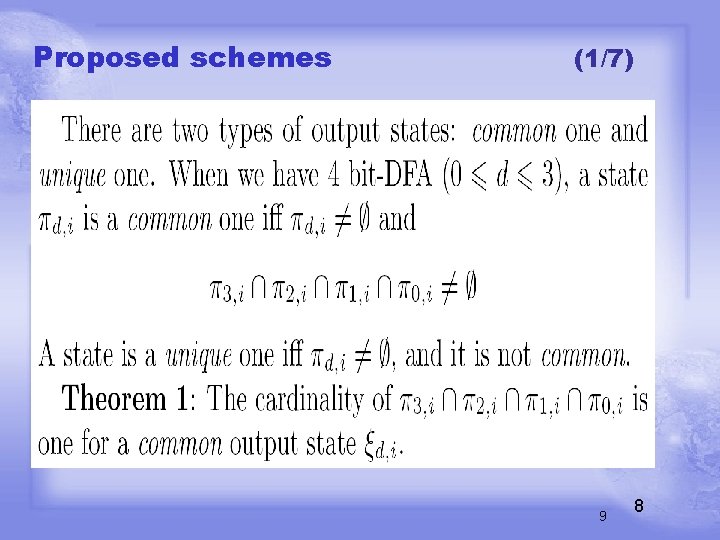

Proposed schemes (1/7) 9 8

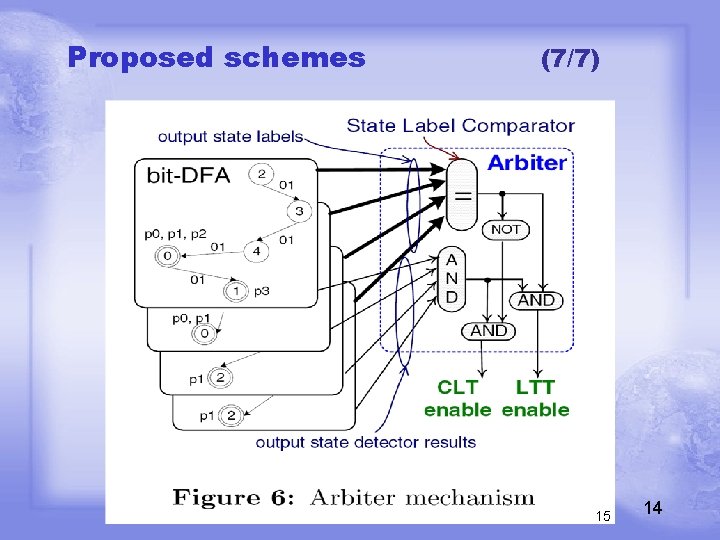

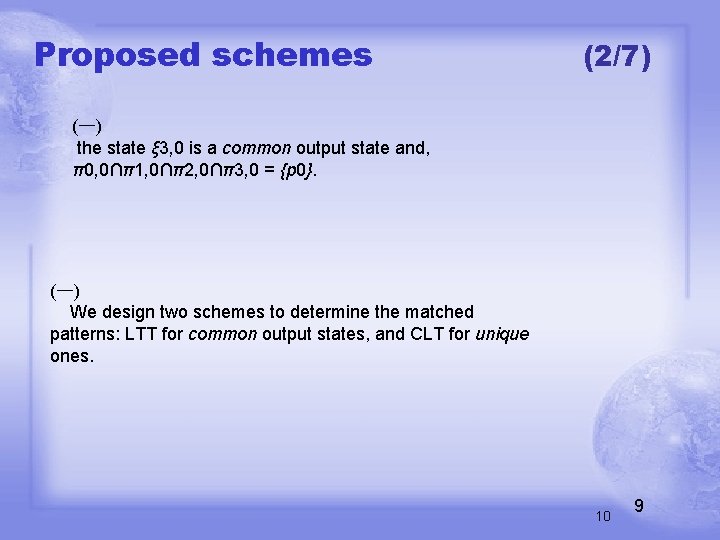

Proposed schemes (2/7) (一) the state ξ 3, 0 is a common output state and, π0, 0∩π1, 0∩π2, 0∩π3, 0 = {p 0}. (一) We design two schemes to determine the matched patterns: LTT for common output states, and CLT for unique ones. 10 9

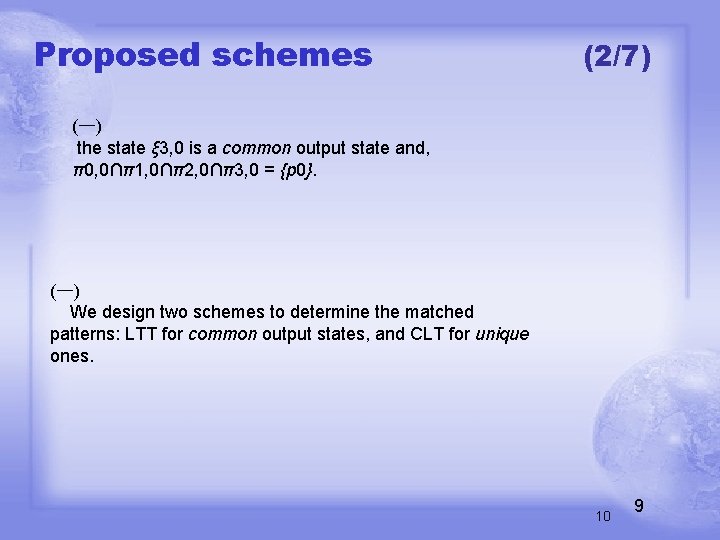

Proposed schemes (3/7) 11 10

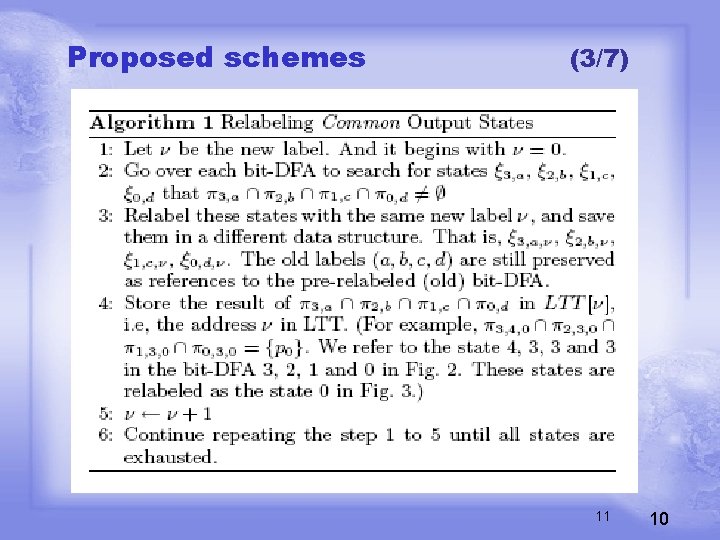

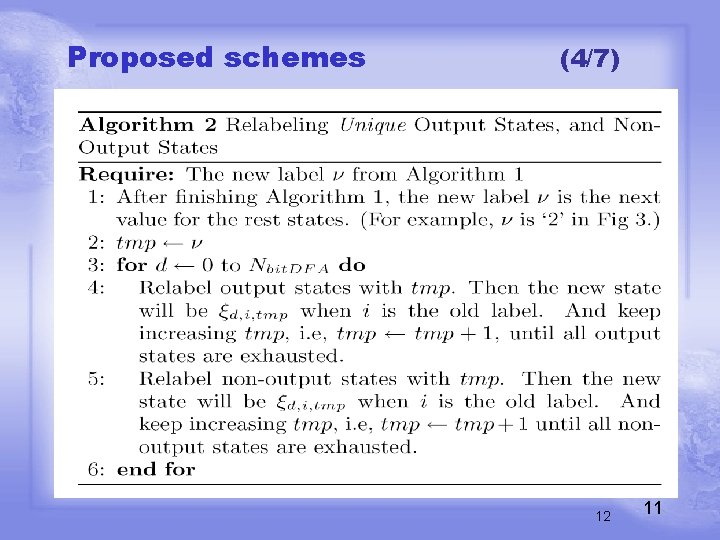

Proposed schemes (4/7) 12 11

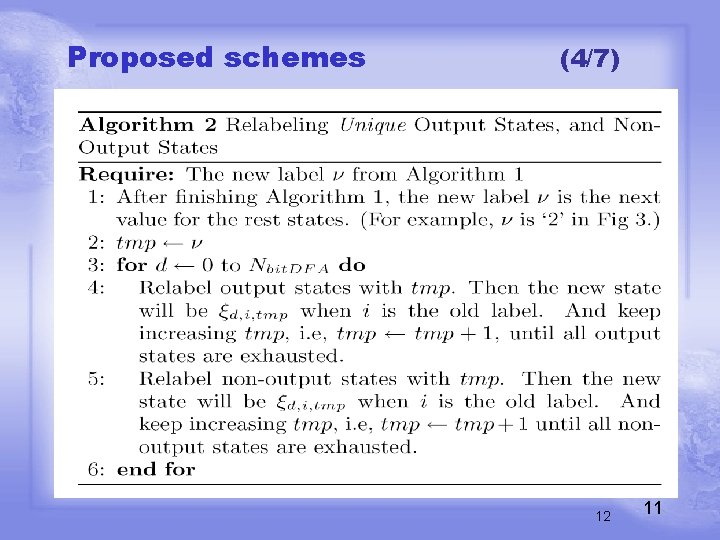

Proposed schemes (5/7) 13 12

Proposed schemes (6/7) 14 13

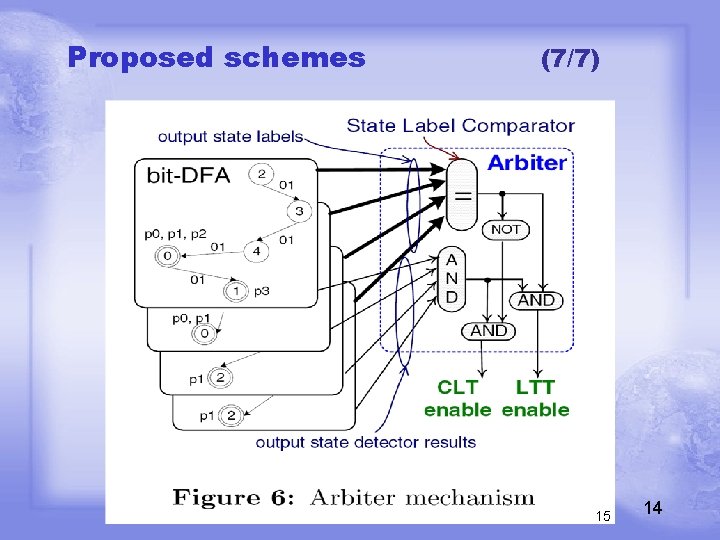

Proposed schemes (7/7) 15 14

Outline l l l 1. Introduction 2. Proposed schemes 3. Architecture 4. Experiments 5. Conclusion 15 16

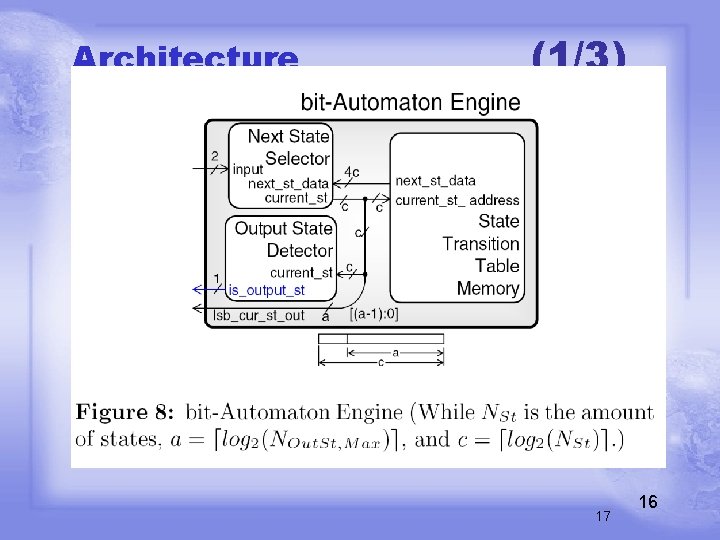

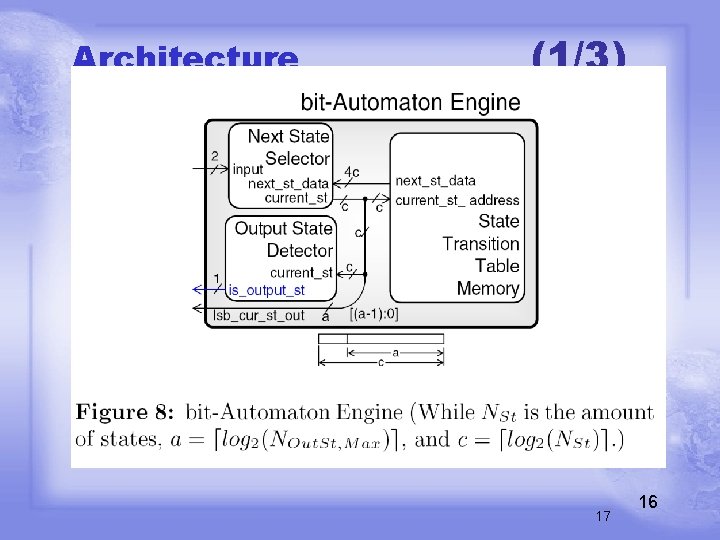

Architecture (1/3) 17 16

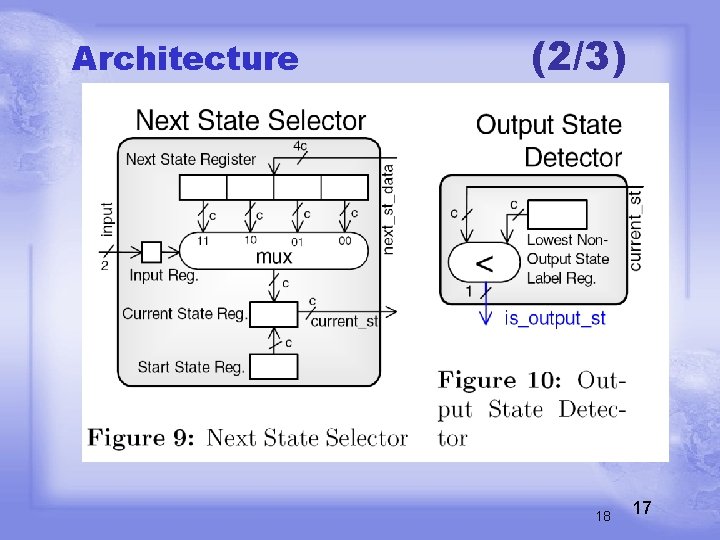

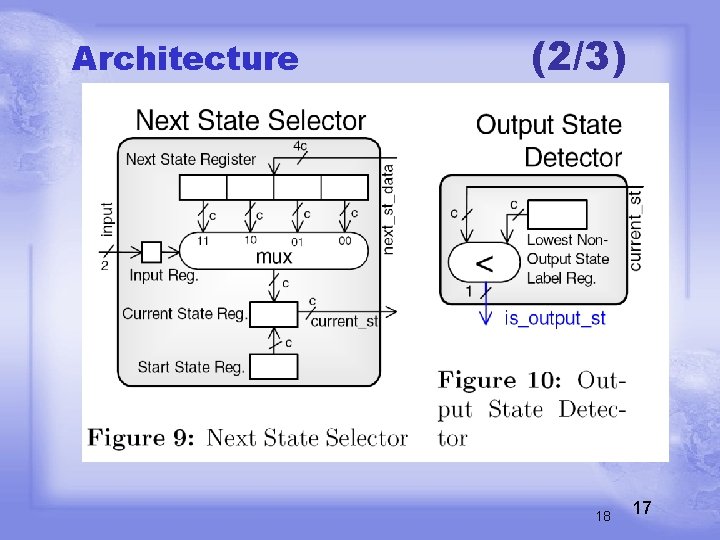

Architecture (2/3) 18 17

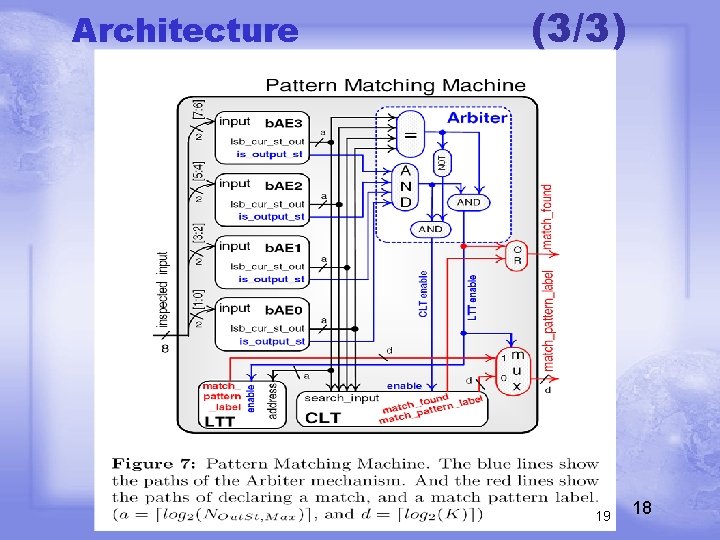

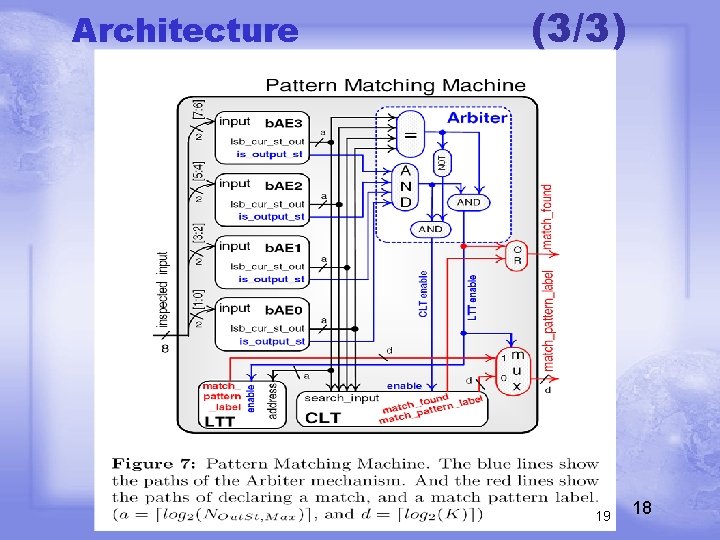

Architecture (3/3) 19 18

Outline l l l 1. Introduction 2. Proposed schemes 3. Architecture 4. Experiments 5. Conclusion 19 20

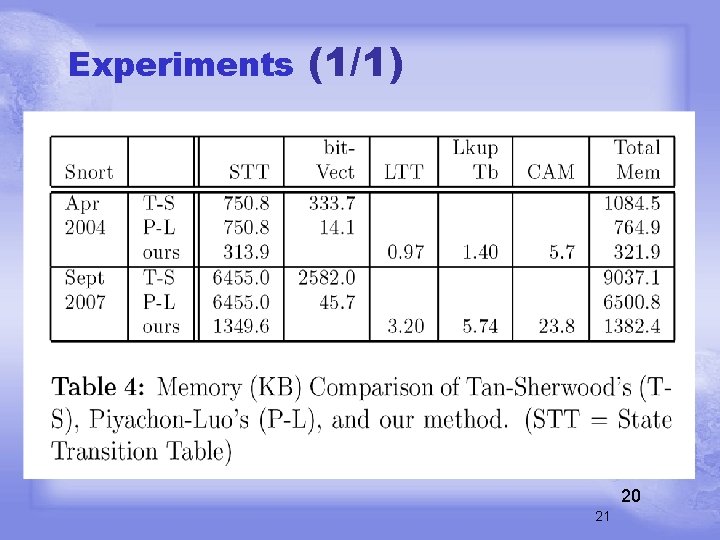

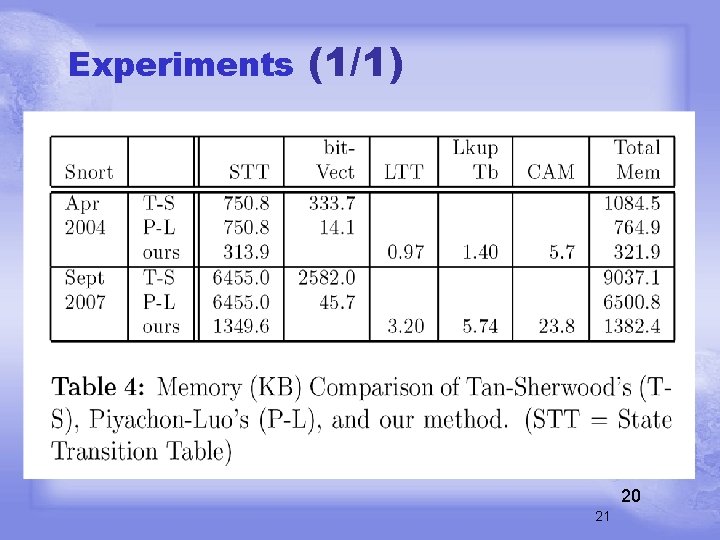

Experiments (1/1) 20 21

Outline l l l 1. Introduction 2. Proposed schemes 3. Architecture 4. Experiments 5. Conclusion 21 22

Conclusion (1/1) (ㄧ) We proposed using Label Translation Table and CAM-based Lookup Table methods to tackle the problems. The proposed schemes reduces the usage by up to 85% (二) We present the architecture that realizes our proposed methods. The architecture suits for both ASIC and FPGA implementation as well as multi-core system 22 23