Design of a Single Event Effect Mitigation Technique

- Slides: 20

Design of a ‘Single Event Effect’ Mitigation Technique for Reconfigurable Architectures SAJID BALOCH Supervisory Team Prof. Dr. T. Arslan 1, 2 Dr. Adrian Stoica 3 Baloch 1 MAPLD 2005/1024 -L

ACRONYMES – – – Baloch SEU (Single Event Effect) SET (Single Event Transient) SEB (Single Event Burnout) SEL (Single Event Latch-up) Cfg (Configuration) EDAC (Error Detection and Correction) So. C (System on Chip) FPGA (Field Programmable Gate Array) DEU (Double Event Upset) TEU (Triple Event Upset ) MEU (Multiple Event Upsets) 2 MAPLD 2005/1024 -L

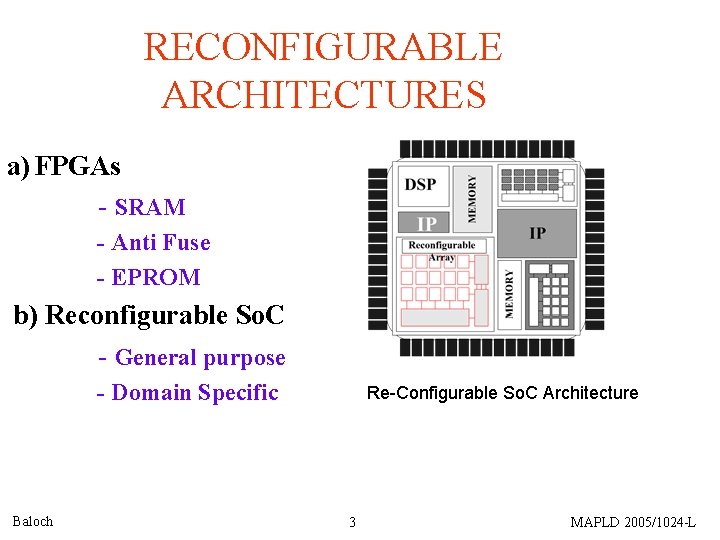

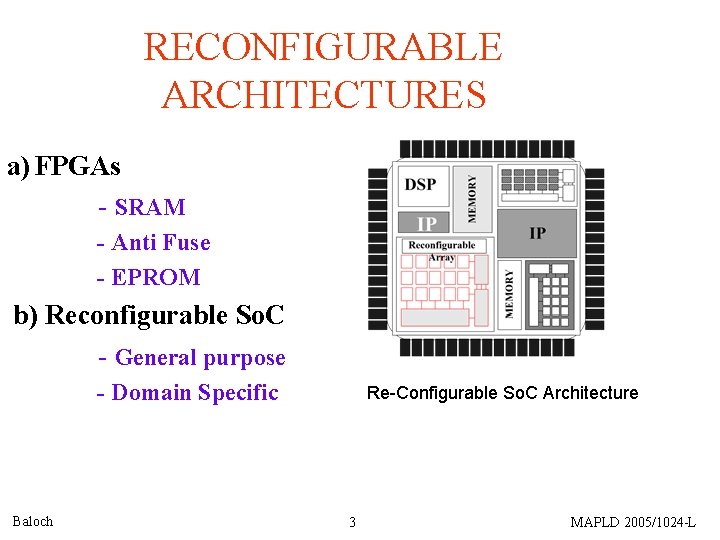

RECONFIGURABLE ARCHITECTURES a) FPGAs - SRAM - Anti Fuse - EPROM b) Reconfigurable So. C - General purpose - Domain Specific Baloch Re-Configurable So. C Architecture 3 MAPLD 2005/1024 -L

RADIATION EFFECTS RE-CONFIGURABLE ARCHITECTURES – PERMANANT FAULTS (due to SEL, SEB etc) – TEMPORARY FAULTS (due to SEU etc) Baloch 4 MAPLD 2005/1024 -L

SEU MITIGATION TECHNIQUES a) HARDWARE REDUNDANCY - Dual Modular Redundancy (DMR) - Triple Modular Redundancy (TMR) - EDAC Codes - Process Technology b) TIME REDUNDANCY c) COMBINATION (Hardware & Time) Baloch 5 MAPLD 2005/1024 -L

Radiation Hardening SEU EFFECTS • TRANSIENT FAULTS (Data Memory etc) • PERMANANT FAULTS (Cfg. Memory) Baloch 6 MAPLD 2005/1024 -L

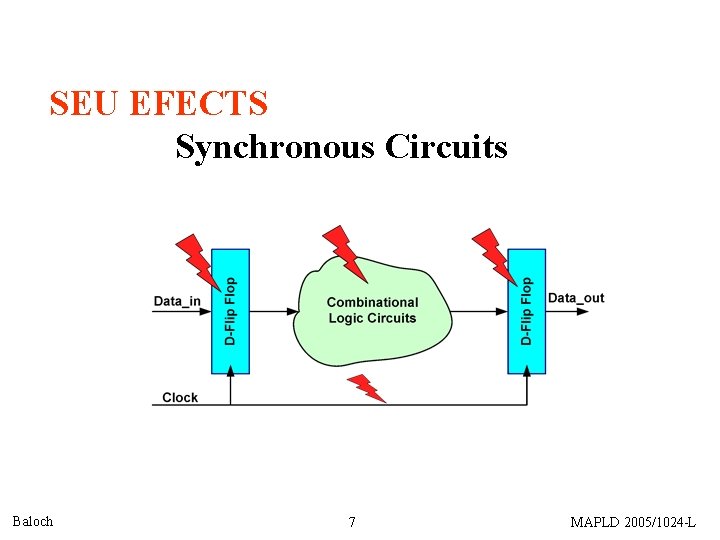

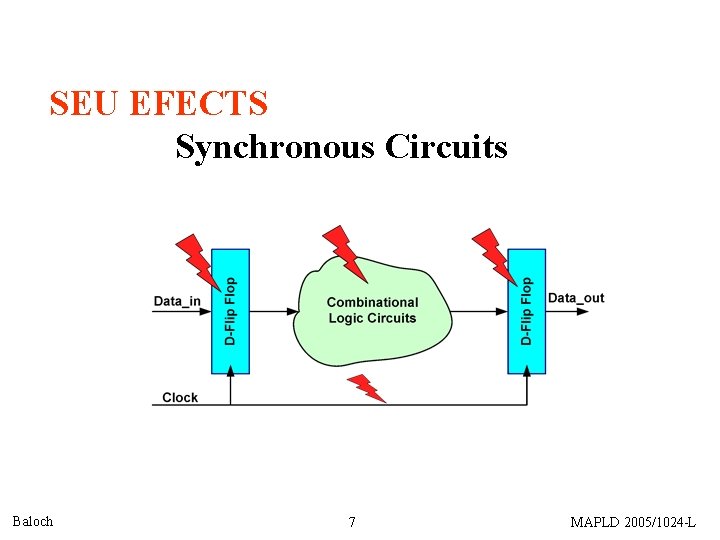

SEU EFECTS Synchronous Circuits Baloch 7 MAPLD 2005/1024 -L

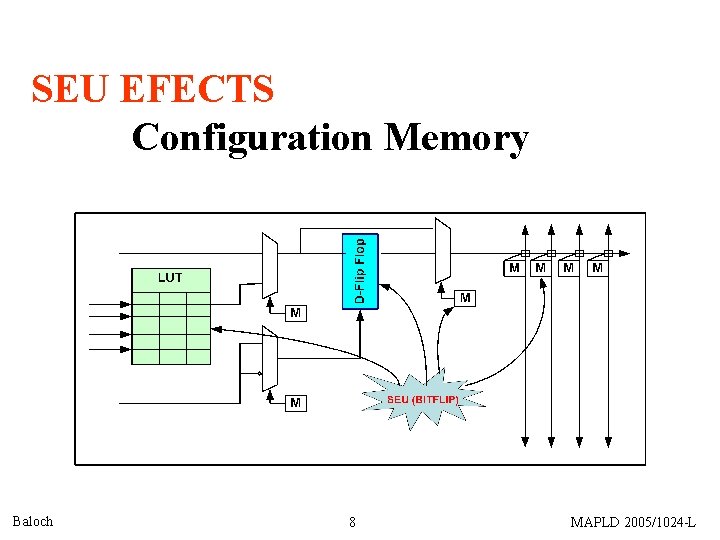

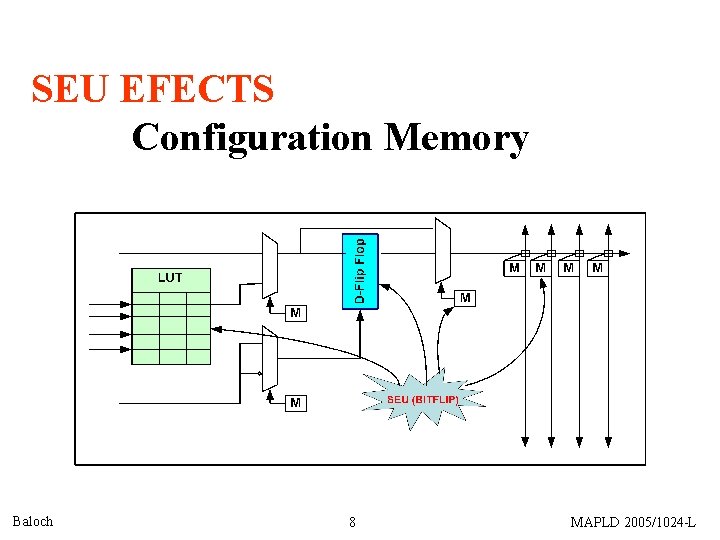

SEU EFECTS Configuration Memory Baloch 8 MAPLD 2005/1024 -L

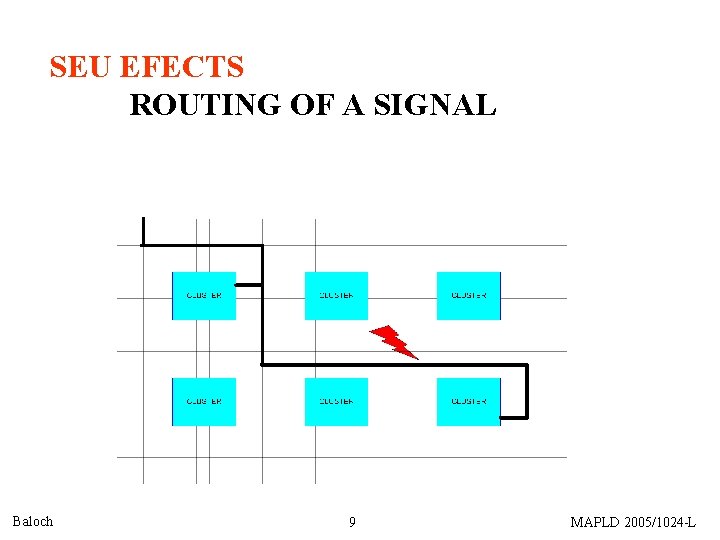

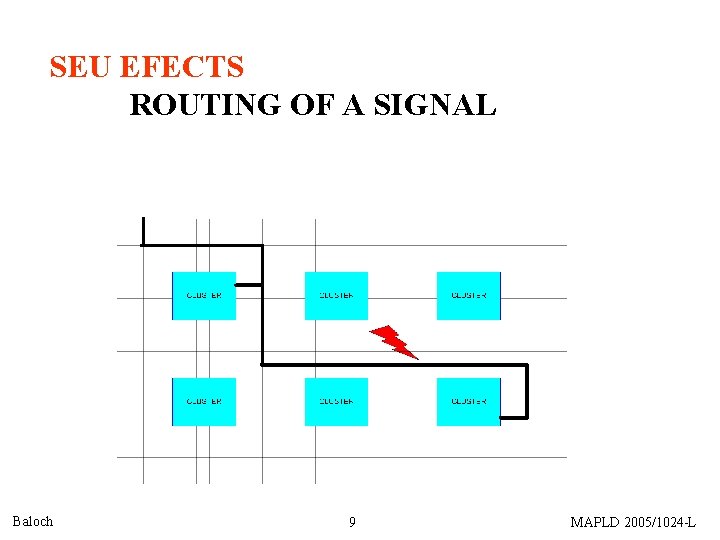

SEU EFECTS ROUTING OF A SIGNAL Baloch 9 MAPLD 2005/1024 -L

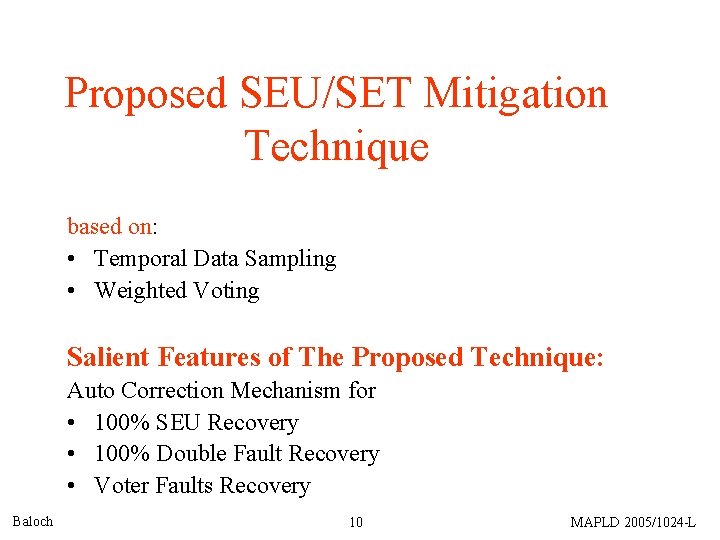

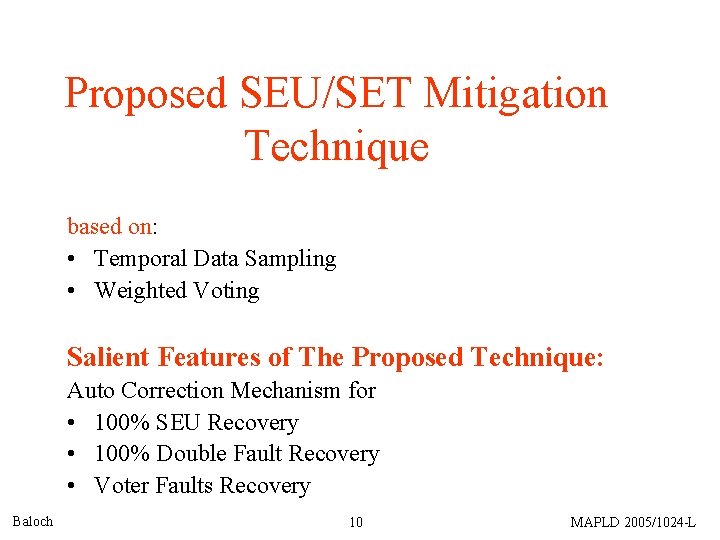

Proposed SEU/SET Mitigation Technique based on: • Temporal Data Sampling • Weighted Voting Salient Features of The Proposed Technique: Auto Correction Mechanism for • 100% SEU Recovery • 100% Double Fault Recovery • Voter Faults Recovery Baloch 10 MAPLD 2005/1024 -L

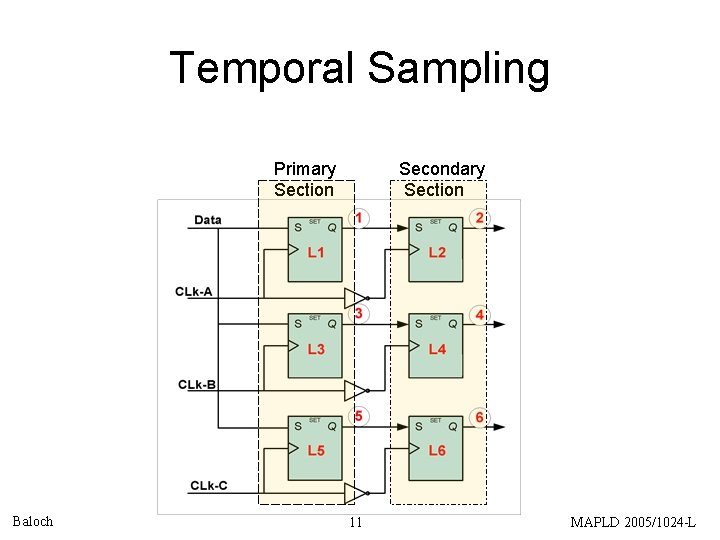

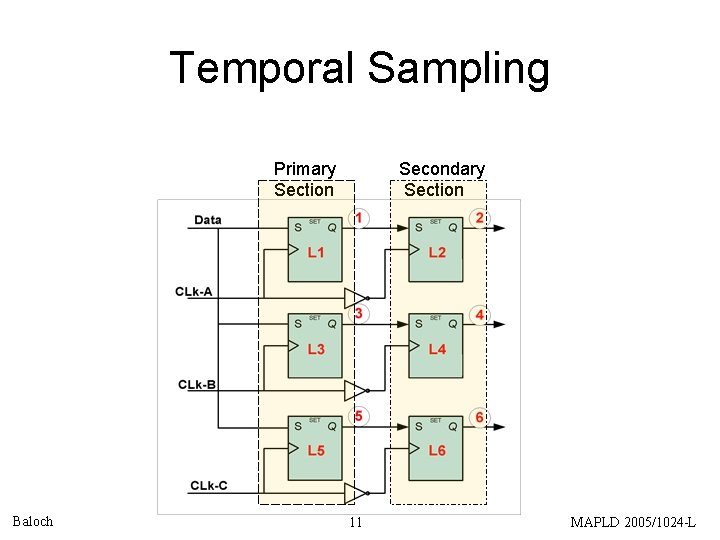

Temporal Sampling Primary Section Baloch Secondary Section 11 MAPLD 2005/1024 -L

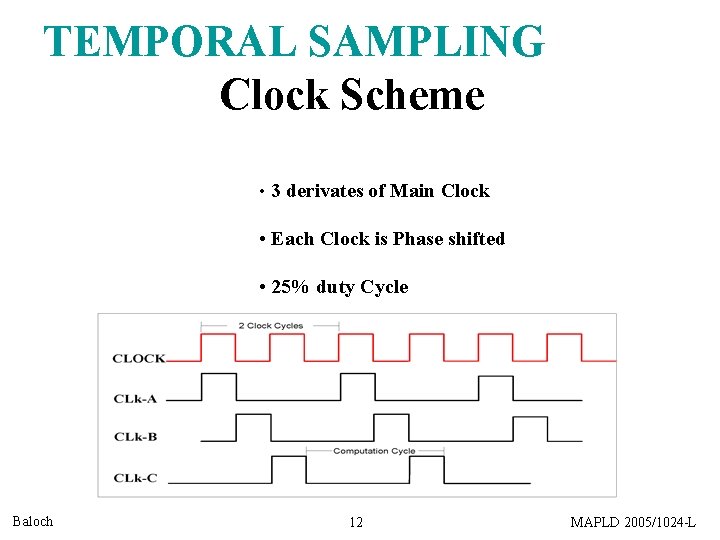

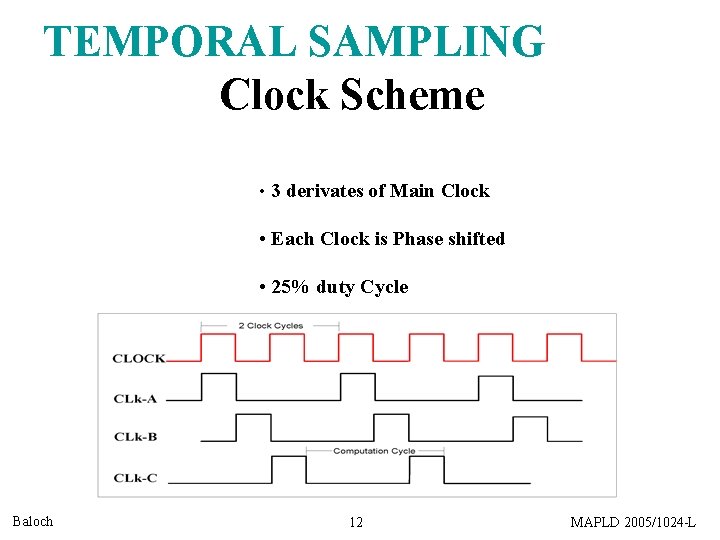

TEMPORAL SAMPLING Clock Scheme • 3 derivates of Main Clock • Each Clock is Phase shifted • 25% duty Cycle Baloch 12 MAPLD 2005/1024 -L

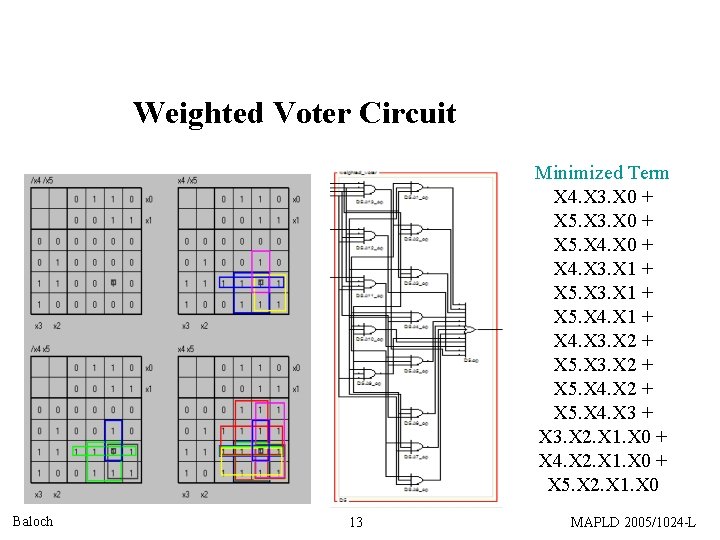

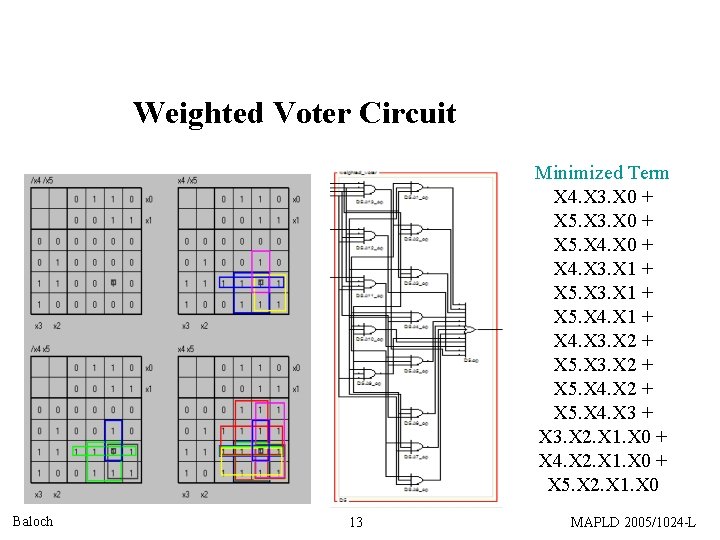

Weighted Voter Circuit Minimized Term X 4. X 3. X 0 + X 5. X 4. X 0 + X 4. X 3. X 1 + X 5. X 4. X 1 + X 4. X 3. X 2 + X 5. X 4. X 3 + X 3. X 2. X 1. X 0 + X 4. X 2. X 1. X 0 + X 5. X 2. X 1. X 0 Baloch 13 MAPLD 2005/1024 -L

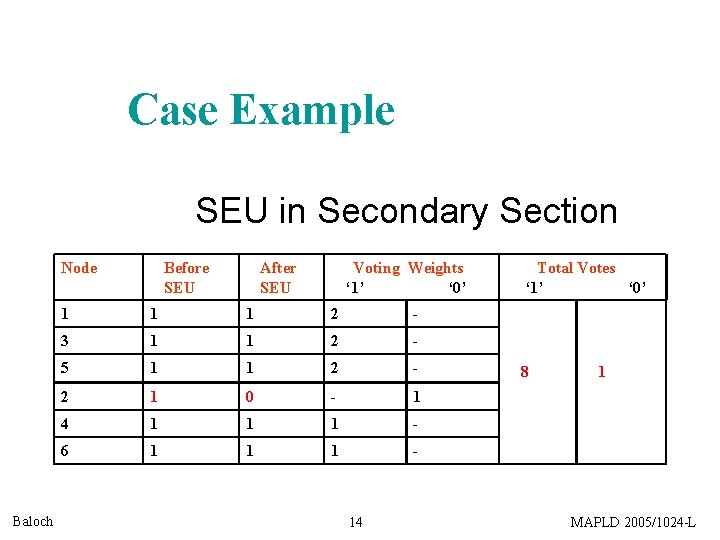

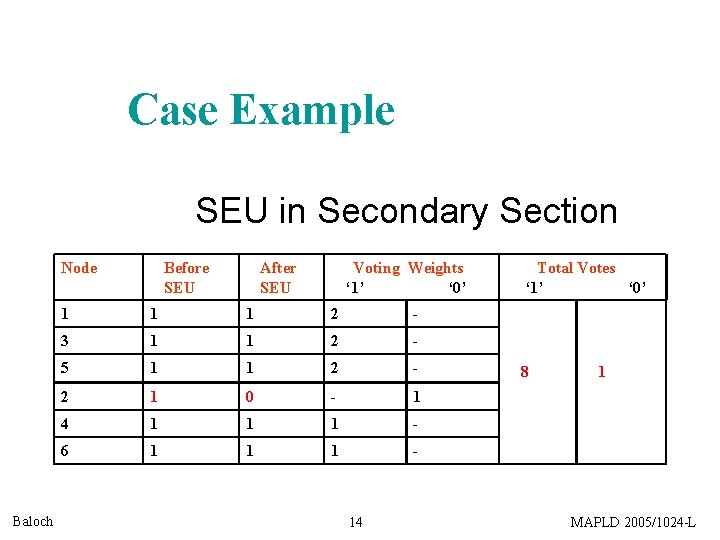

Case Example SEU in Secondary Section Node Baloch Before SEU After SEU Voting Weights ‘ 1’ ‘ 0’ 1 1 1 2 - 3 1 1 2 - 5 1 1 2 - 2 1 0 - 1 4 1 1 1 - 6 1 1 1 - 14 Total Votes ‘ 1’ ‘ 0’ 8 1 MAPLD 2005/1024 -L

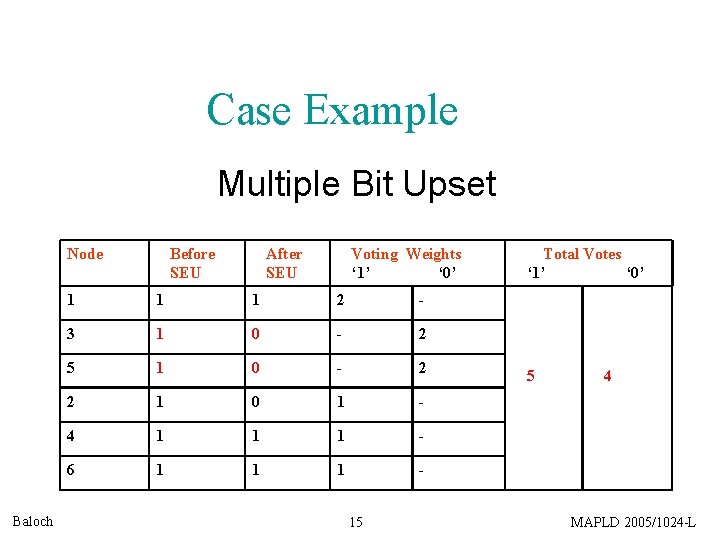

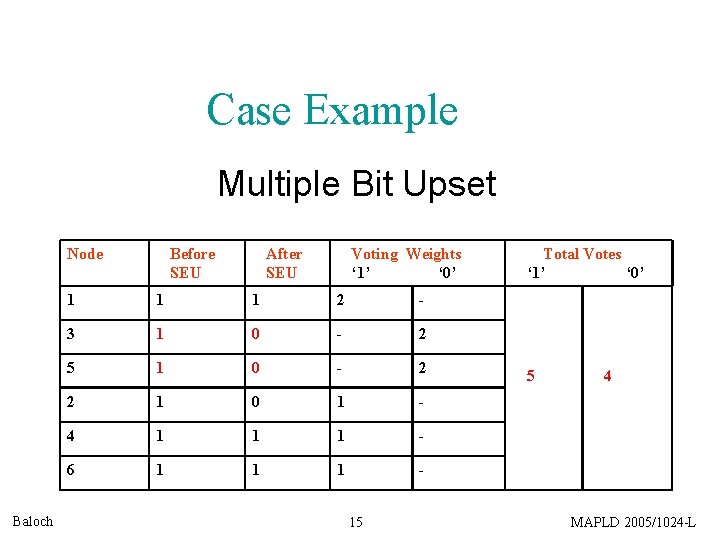

Case Example Multiple Bit Upset Node Baloch Before SEU After SEU Voting Weights ‘ 1’ ‘ 0’ 1 1 1 2 - 3 1 0 - 2 5 1 0 - 2 2 1 0 1 - 4 1 1 1 - 6 1 15 Total Votes ‘ 1’ ‘ 0’ 5 4 MAPLD 2005/1024 -L

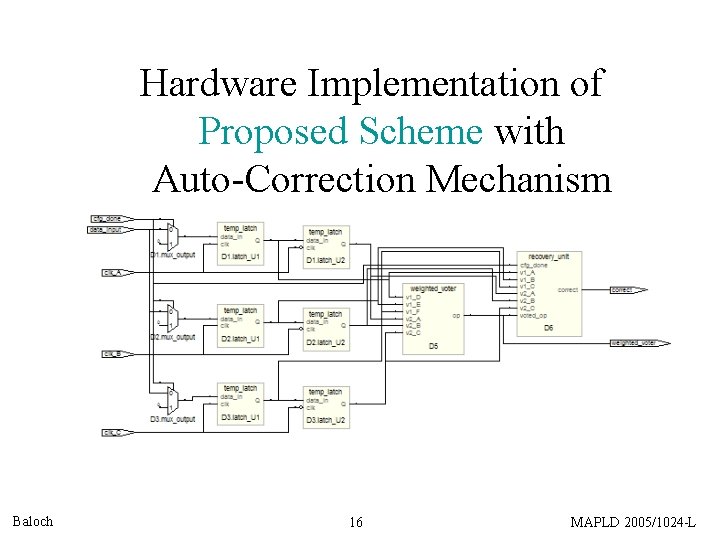

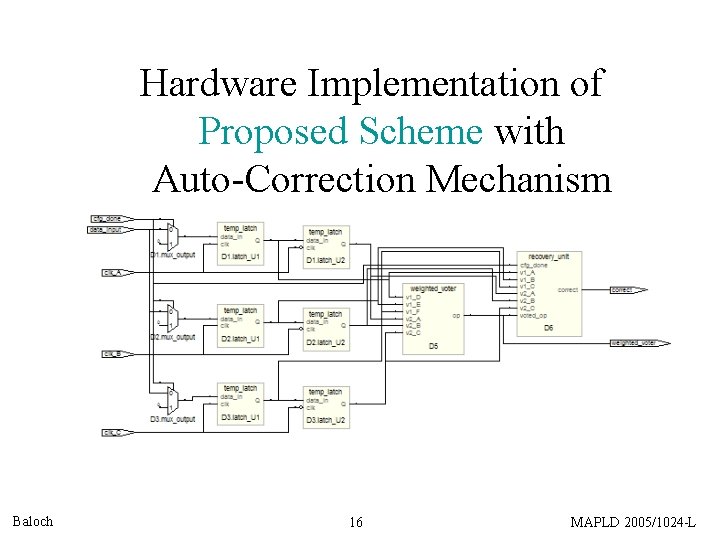

Hardware Implementation of Proposed Scheme with Auto-Correction Mechanism Baloch 16 MAPLD 2005/1024 -L

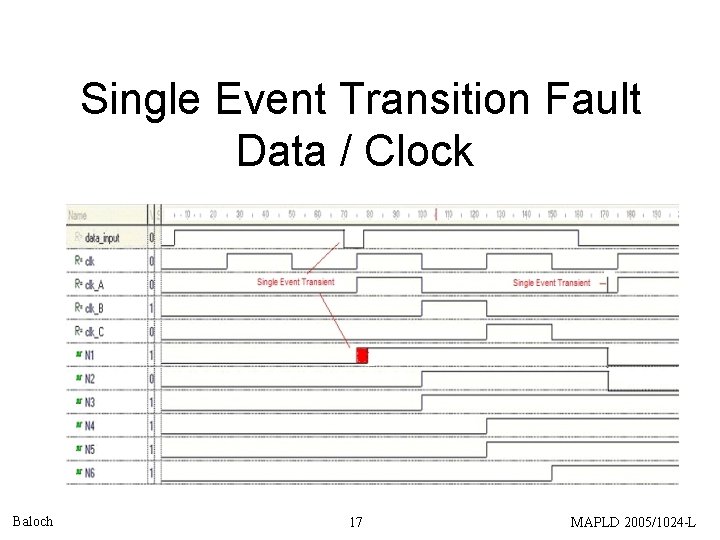

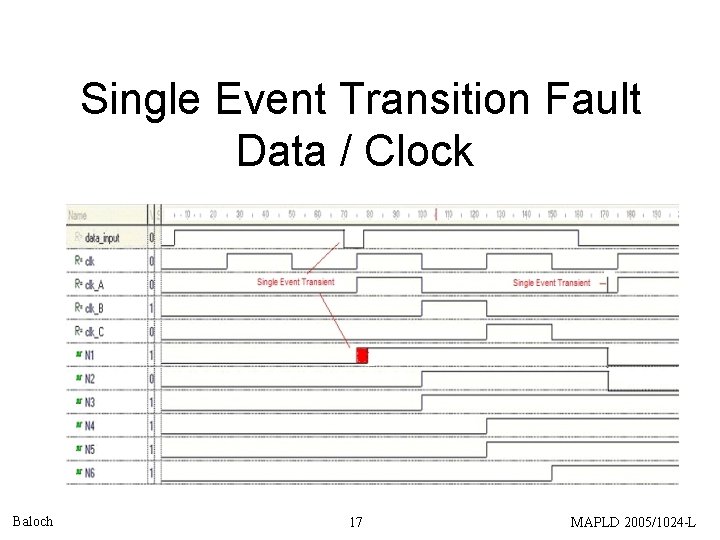

Single Event Transition Fault Data / Clock Baloch 17 MAPLD 2005/1024 -L

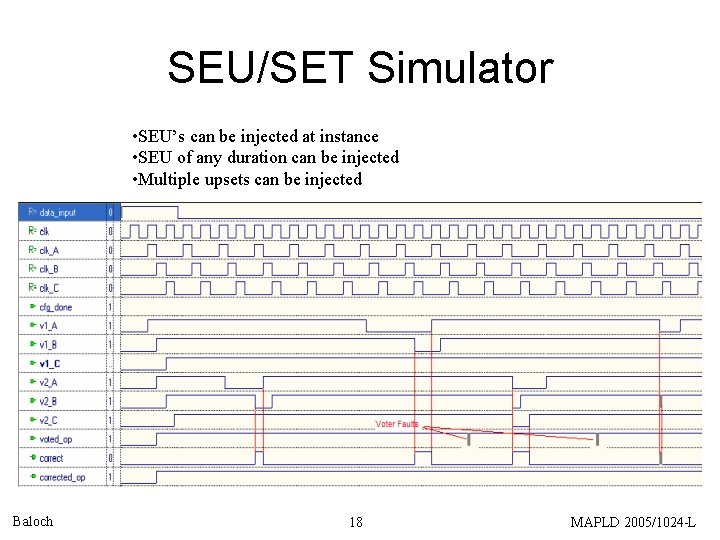

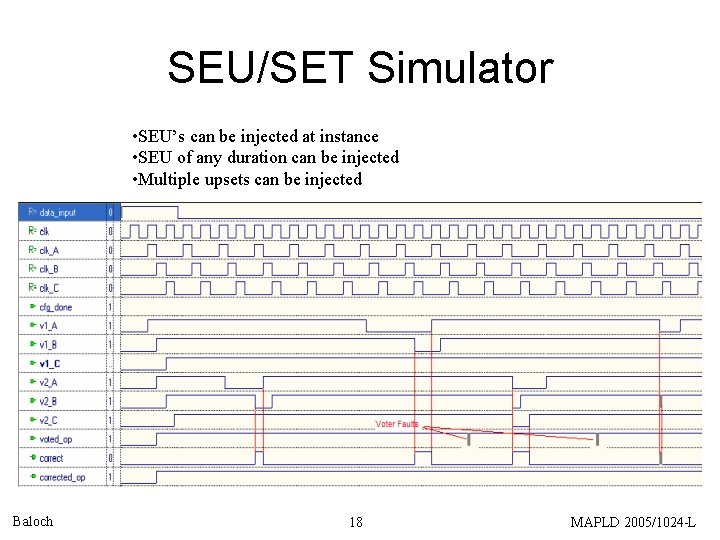

SEU/SET Simulator • SEU’s can be injected at instance • SEU of any duration can be injected • Multiple upsets can be injected Baloch 18 MAPLD 2005/1024 -L

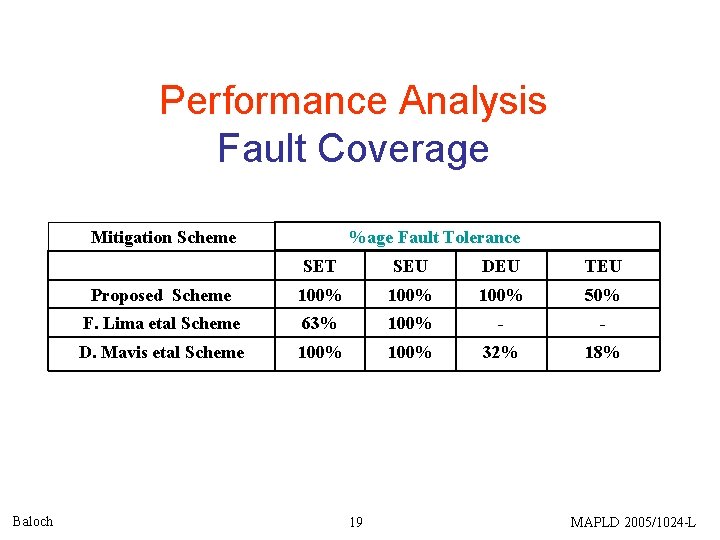

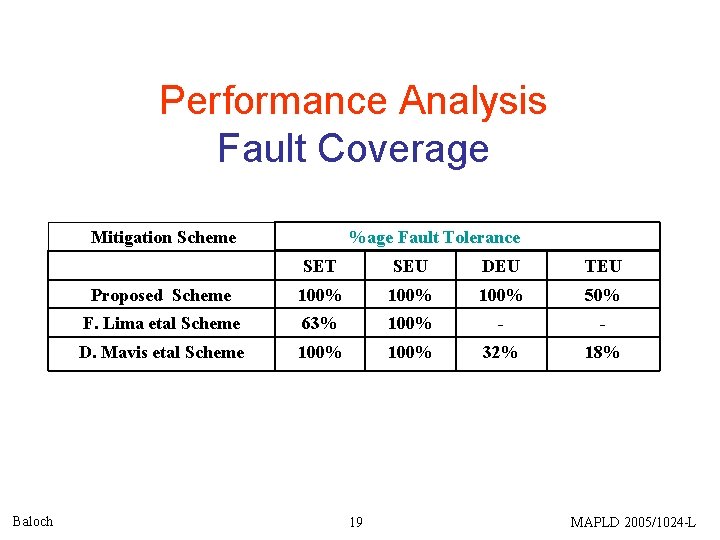

Performance Analysis Fault Coverage Mitigation Scheme Baloch %age Fault Tolerance SET SEU DEU TEU Proposed Scheme 100% 50% F. Lima etal Scheme 63% 100% - - D. Mavis etal Scheme 100% 32% 18% 19 MAPLD 2005/1024 -L

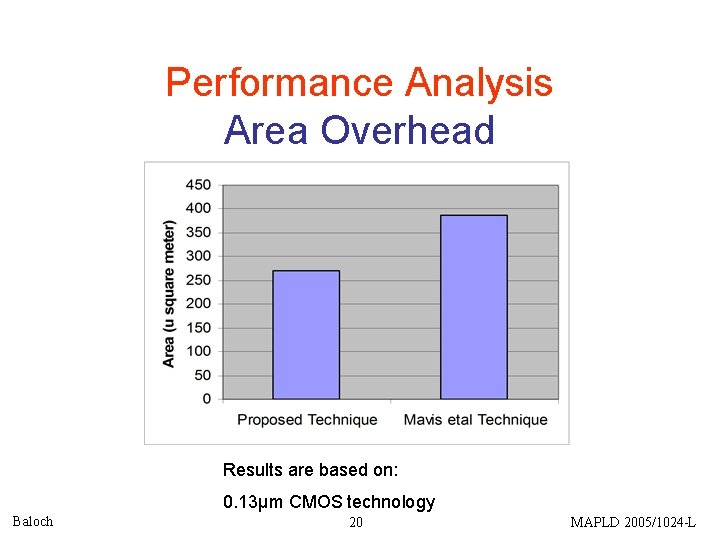

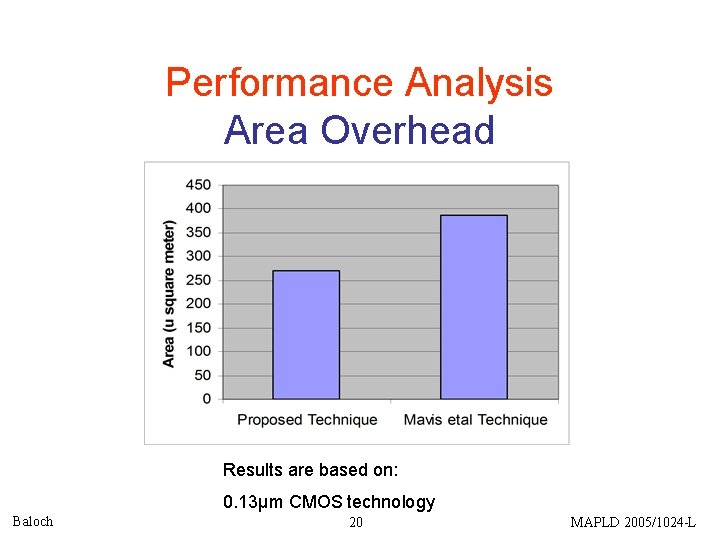

Performance Analysis Area Overhead Results are based on: 0. 13µm CMOS technology Baloch 20 MAPLD 2005/1024 -L