Design Entry Schematic Capture and VHDL ENG 2410

- Slides: 25

Design Entry: Schematic Capture and VHDL ENG 2410: Digital Design Week #4

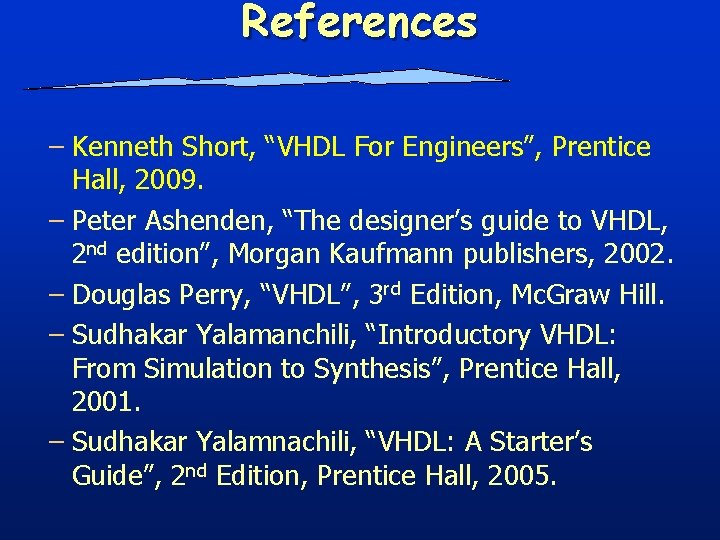

References – Kenneth Short, “VHDL For Engineers”, Prentice Hall, 2009. – Peter Ashenden, “The designer’s guide to VHDL, 2 nd edition”, Morgan Kaufmann publishers, 2002. – Douglas Perry, “VHDL”, 3 rd Edition, Mc. Graw Hill. – Sudhakar Yalamanchili, “Introductory VHDL: From Simulation to Synthesis”, Prentice Hall, 2001. – Sudhakar Yalamnachili, “VHDL: A Starter’s Guide”, 2 nd Edition, Prentice Hall, 2005.

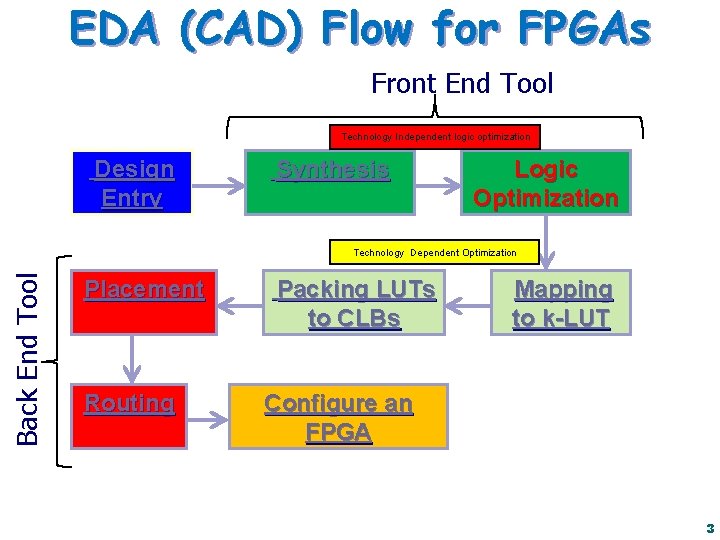

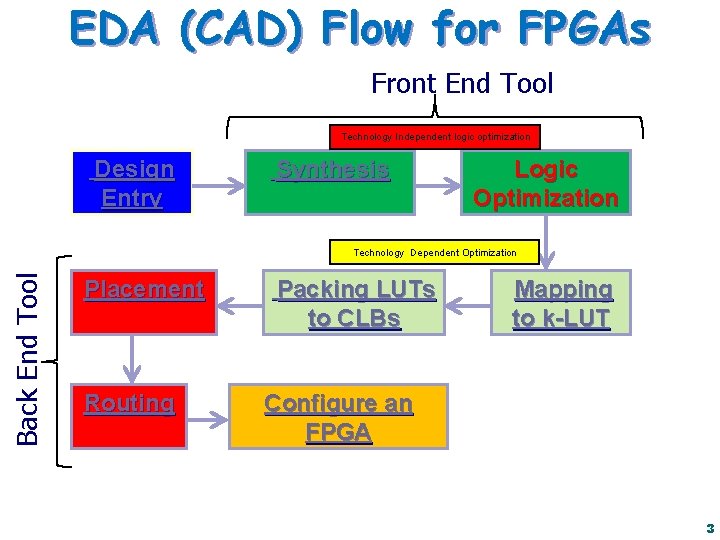

EDA (CAD) Flow for FPGAs Front End Tool Technology Independent logic optimization Design Entry Synthesis Logic Optimization Back End Tool Technology Dependent Optimization Placement Routing Packing LUTs to CLBs Mapping to k-LUT Configure an FPGA 3

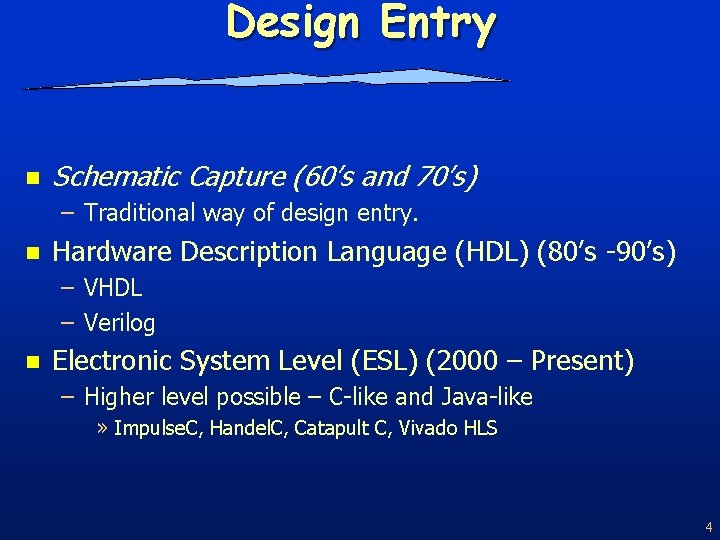

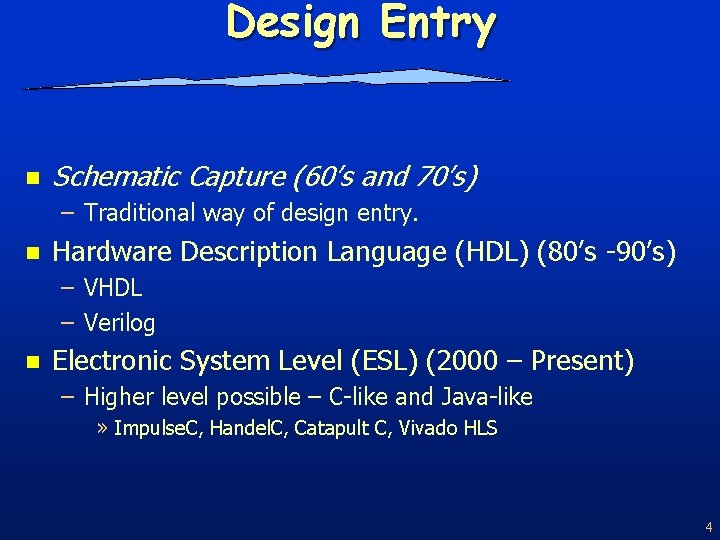

Design Entry n Schematic Capture (60’s and 70’s) – Traditional way of design entry. n Hardware Description Language (HDL) (80’s -90’s) – VHDL – Verilog n Electronic System Level (ESL) (2000 – Present) – Higher level possible – C-like and Java-like » Impulse. C, Handel. C, Catapult C, Vivado HLS 4

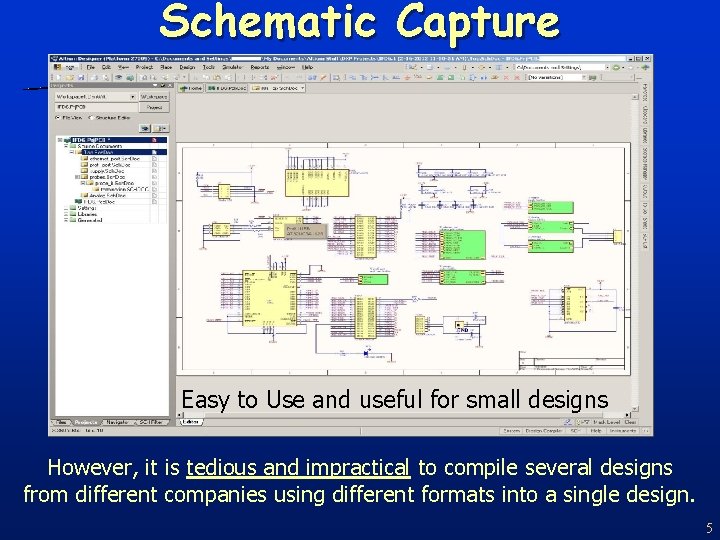

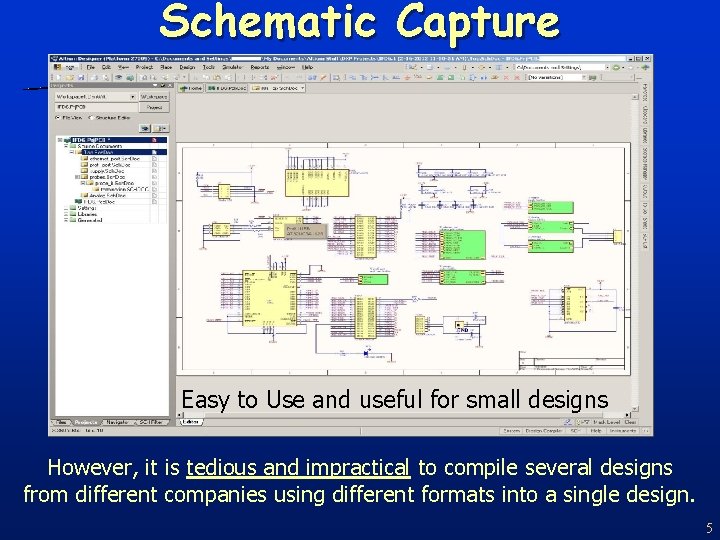

Schematic Capture Easy to Use and useful for small designs However, it is tedious and impractical to compile several designs from different companies using different formats into a single design. 5

What is HDL? Hardware Description Languages (HDLs) are languages used to q q Documentation (model), Communicate the design to others, Simulate (verify), and synthesize digital circuits and systems. 6

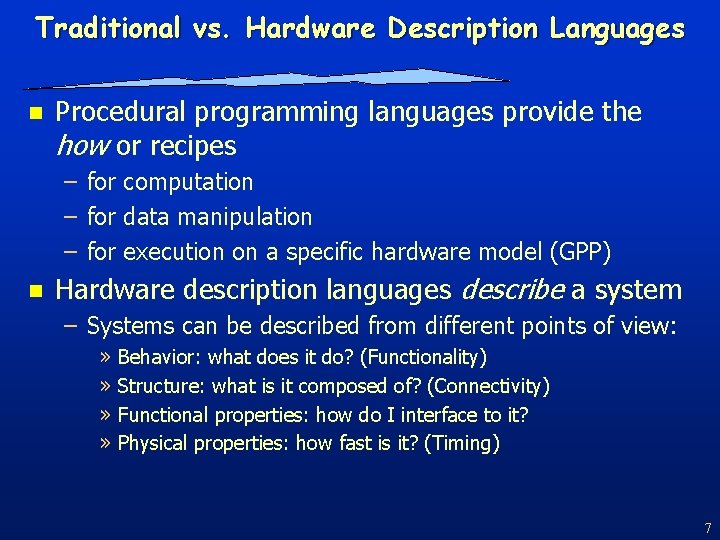

Traditional vs. Hardware Description Languages n Procedural programming languages provide the how or recipes – for computation – for data manipulation – for execution on a specific hardware model (GPP) n Hardware description languages describe a system – Systems can be described from different points of view: » » Behavior: what does it do? (Functionality) Structure: what is it composed of? (Connectivity) Functional properties: how do I interface to it? Physical properties: how fast is it? (Timing) 7

VHDL: Introduction • VHDL is an acronym for “VHSIC Hardware Description Language”. • VHSIC is an acronym for “Very High Speed Integrated Circuits” program. It was a US government sponsored program that was responsible for developing a standard HDL. • VHDL supports modeling and simulation of digital systems at various levels of design abstraction. 8

Basic Modeling

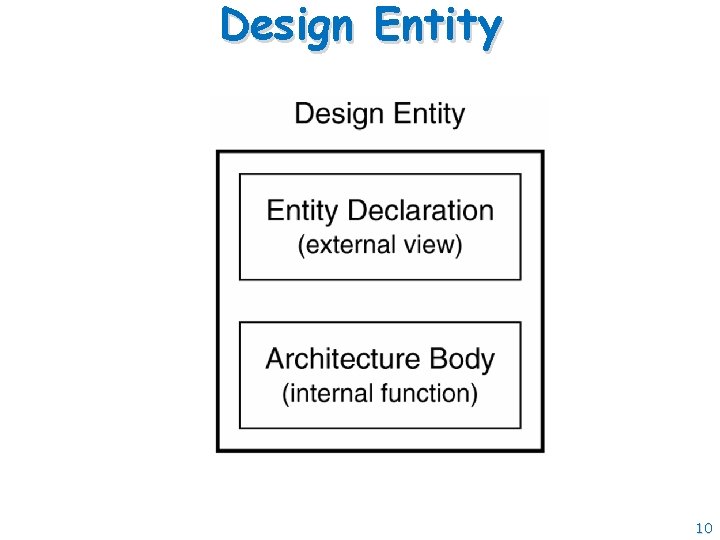

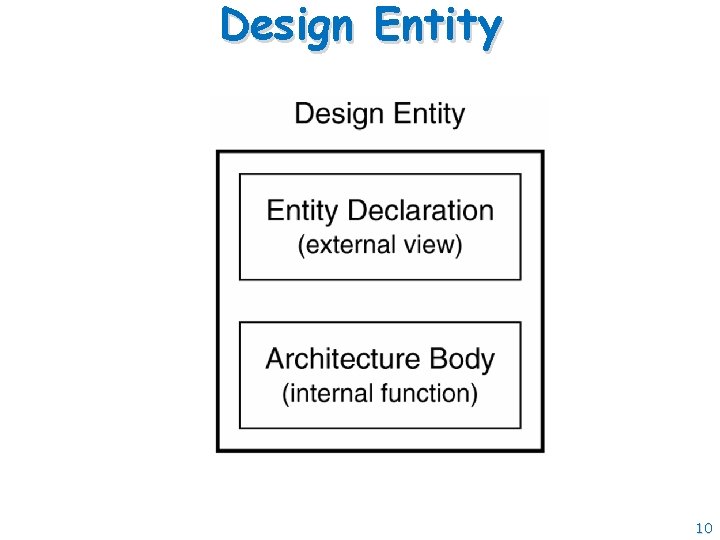

Design Entity 10

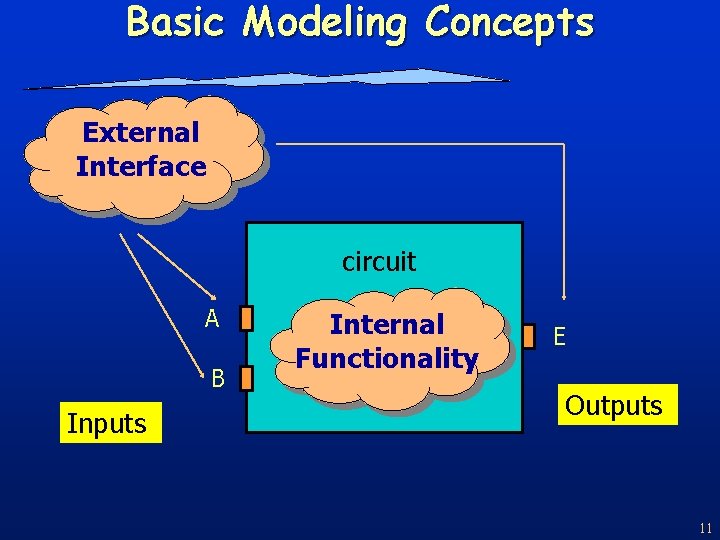

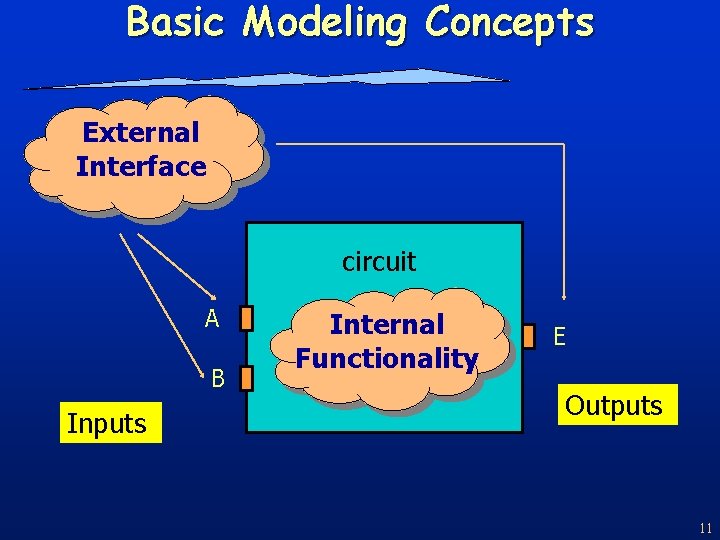

Basic Modeling Concepts External Interface circuit A B Inputs Internal Functionality E Outputs 11

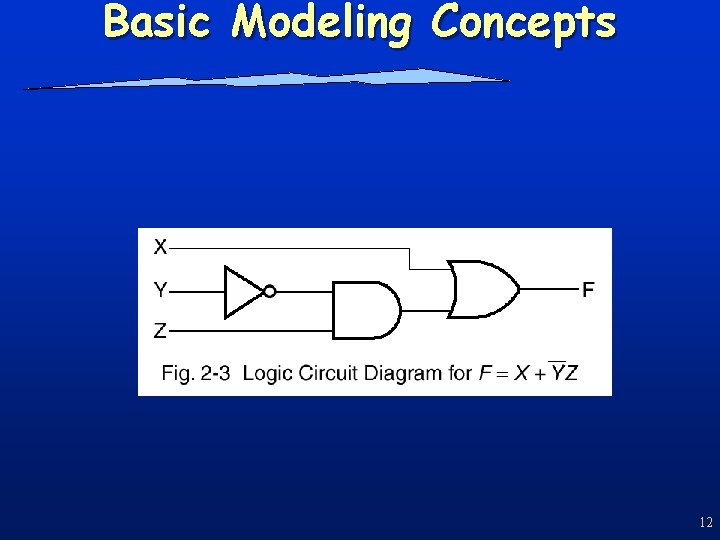

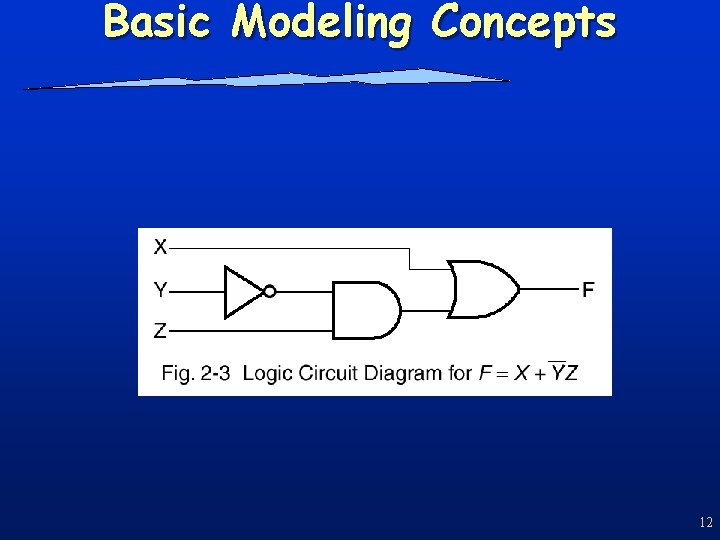

Basic Modeling Concepts 12

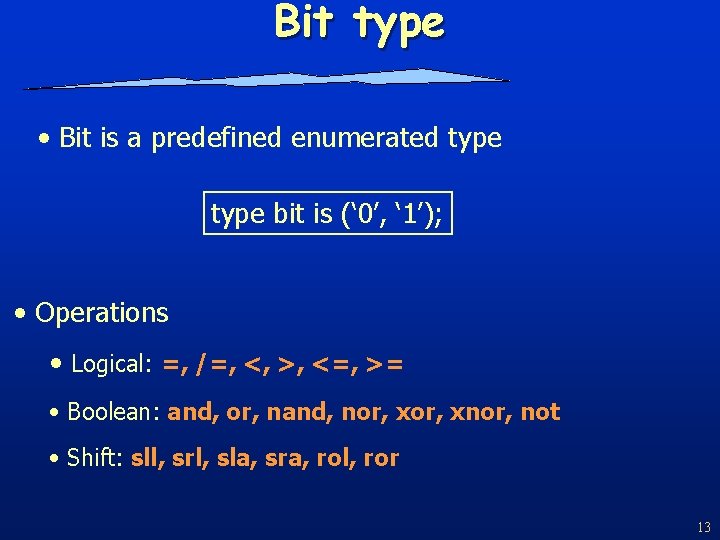

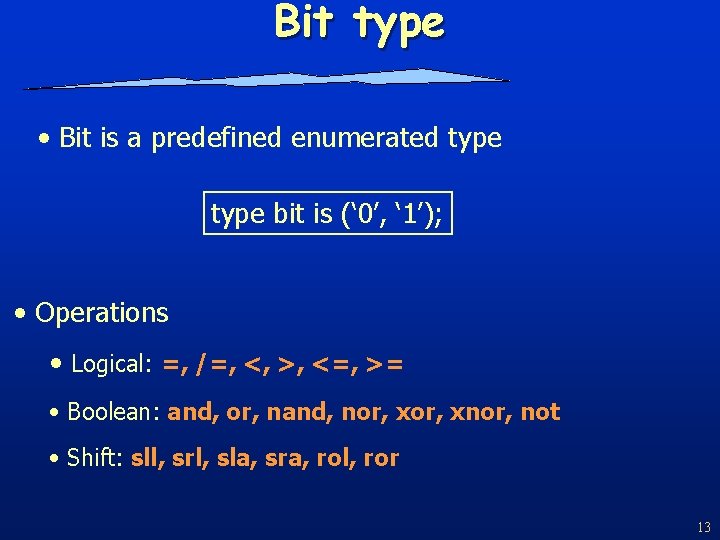

Bit type • Bit is a predefined enumerated type bit is (‘ 0’, ‘ 1’); • Operations • Logical: =, /=, <, >, <=, >= • Boolean: and, or, nand, nor, xnor, not • Shift: sll, srl, sla, sra, rol, ror 13

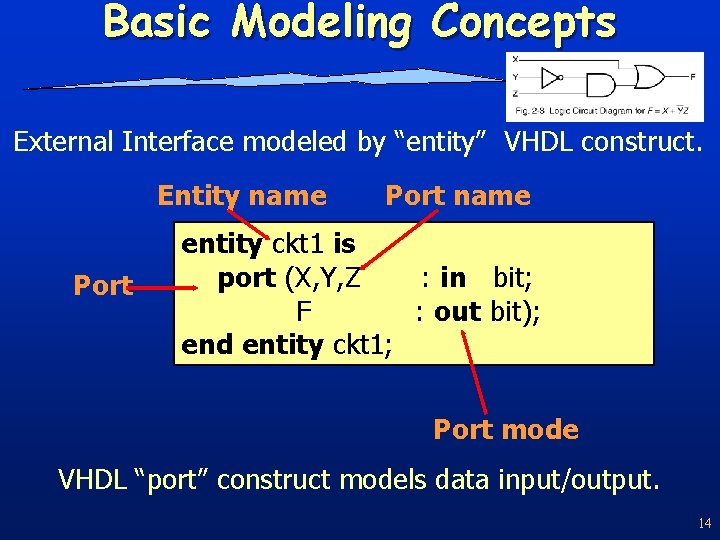

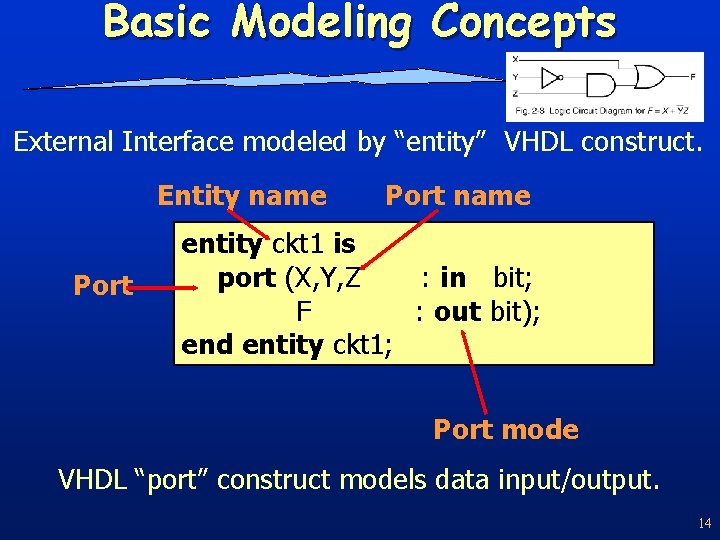

Basic Modeling Concepts External Interface modeled by “entity” VHDL construct. Entity name Port name entity ckt 1 is port (X, Y, Z : in bit; F : out bit); end entity ckt 1; Port mode VHDL “port” construct models data input/output. 14

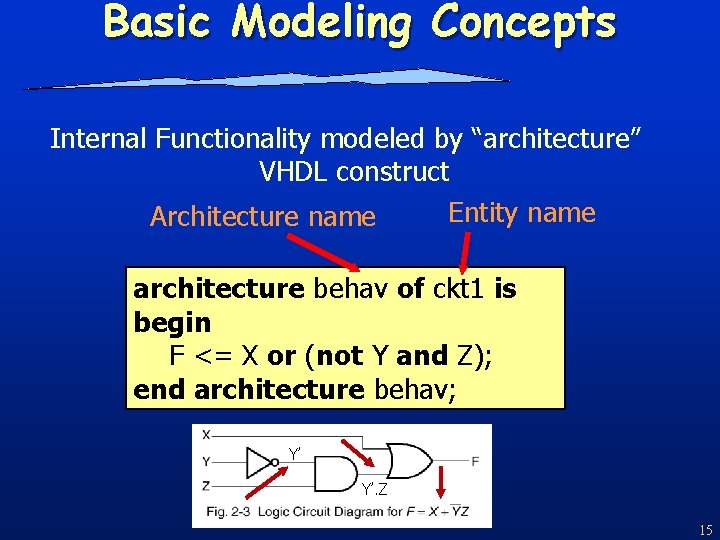

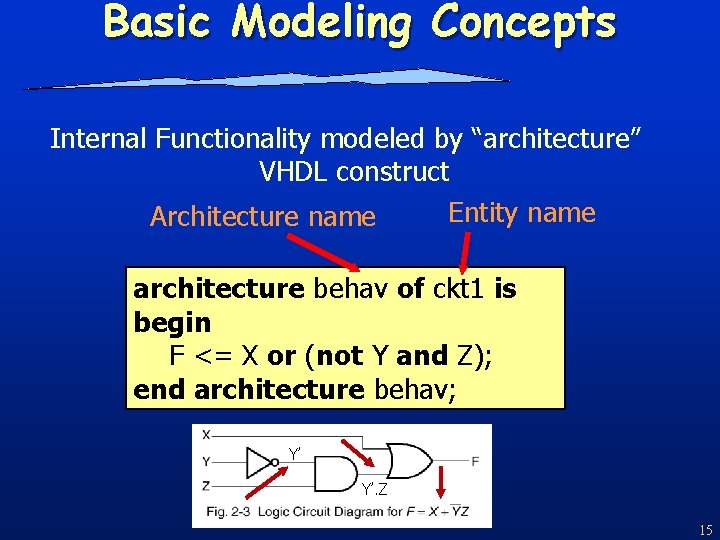

Basic Modeling Concepts Internal Functionality modeled by “architecture” VHDL construct Entity name Architecture name architecture behav of ckt 1 is begin F <= X or (not Y and Z); end architecture behav; Y’ Y’. Z 15

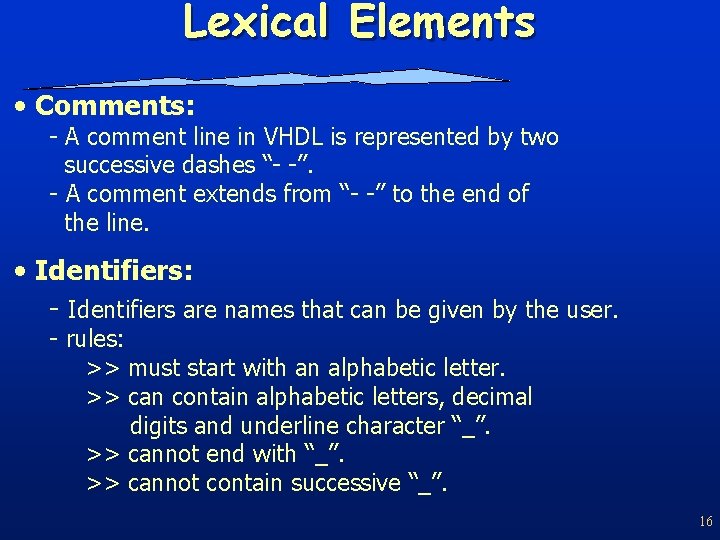

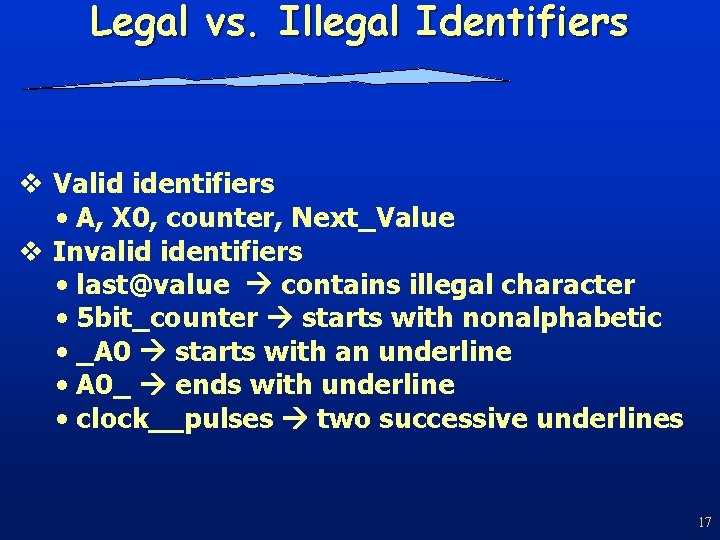

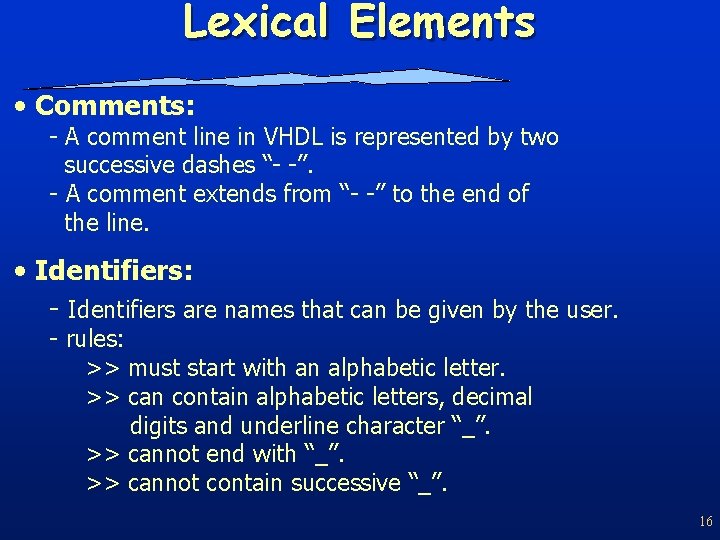

Lexical Elements • Comments: - A comment line in VHDL is represented by two successive dashes “- -”. - A comment extends from “- -” to the end of the line. • Identifiers: - Identifiers are names that can be given by the user. - rules: >> must start with an alphabetic letter. >> can contain alphabetic letters, decimal digits and underline character “_”. >> cannot end with “_”. >> cannot contain successive “_”. 16

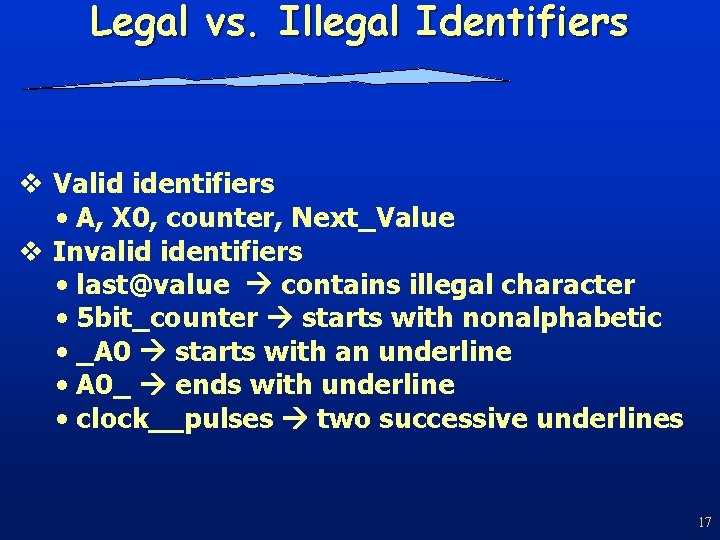

Legal vs. Illegal Identifiers v Valid identifiers • A, X 0, counter, Next_Value v Invalid identifiers • last@value contains illegal character • 5 bit_counter starts with nonalphabetic • _A 0 starts with an underline • A 0_ ends with underline • clock__pulses two successive underlines 17

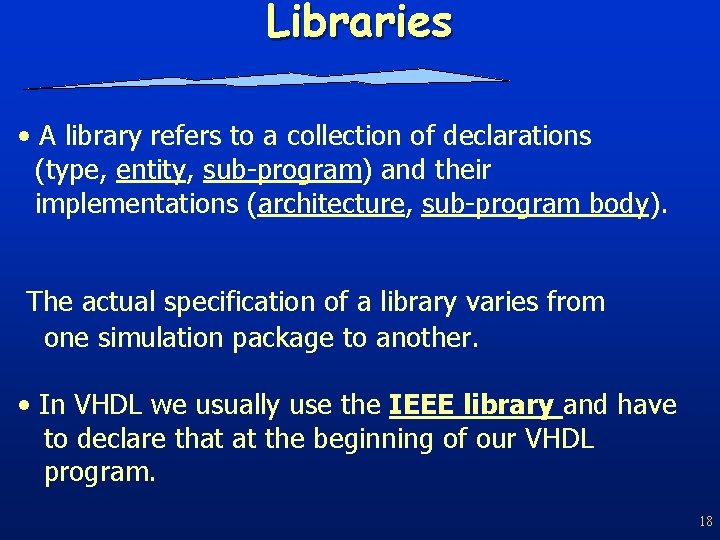

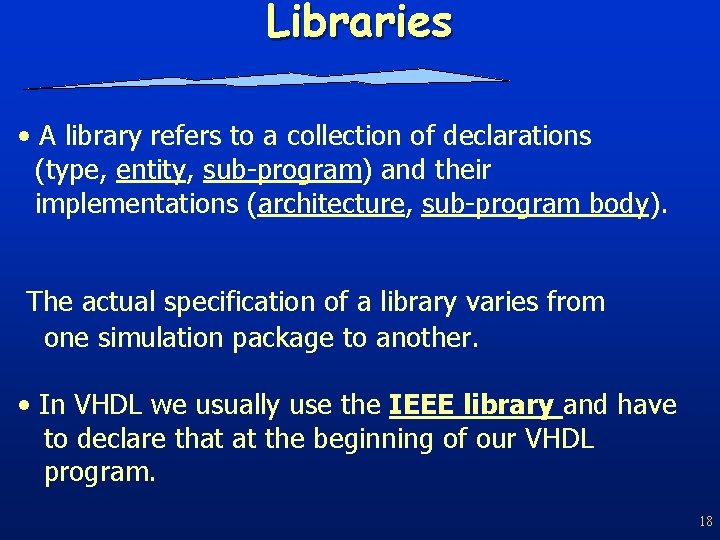

Libraries • A library refers to a collection of declarations (type, entity, sub-program) and their implementations (architecture, sub-program body). The actual specification of a library varies from one simulation package to another. • In VHDL we usually use the IEEE library and have to declare that at the beginning of our VHDL program. 18

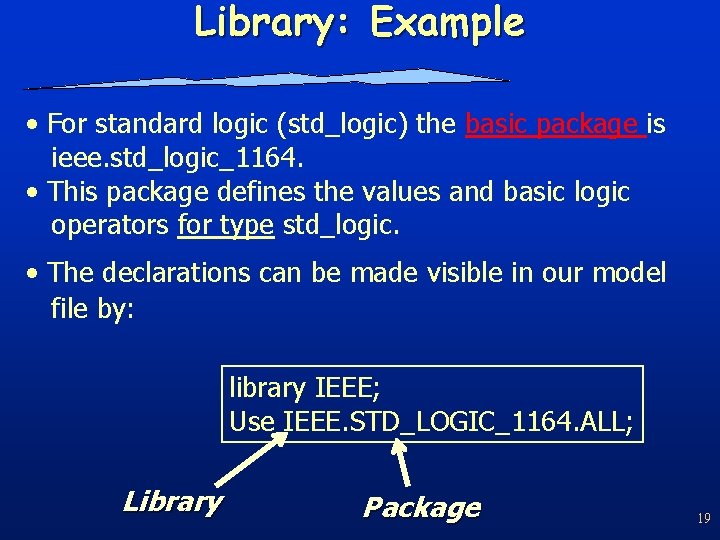

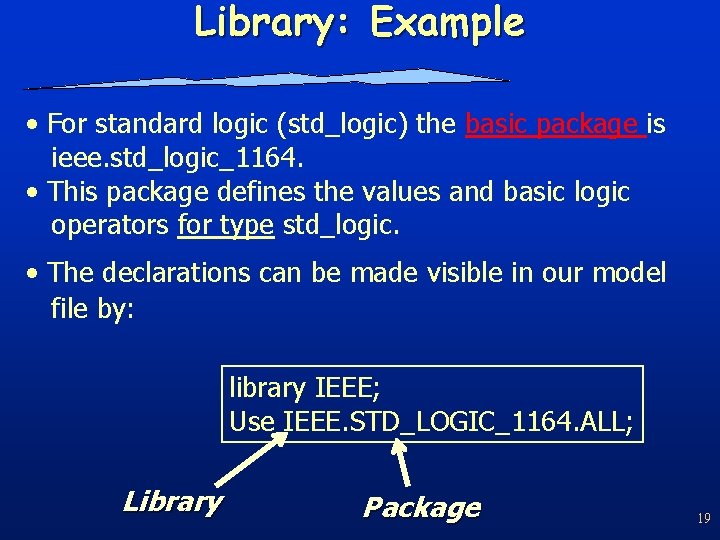

Library: Example • For standard logic (std_logic) the basic package is ieee. std_logic_1164. • This package defines the values and basic logic operators for type std_logic. • The declarations can be made visible in our model file by: library IEEE; Use IEEE. STD_LOGIC_1164. ALL; Library Package 19

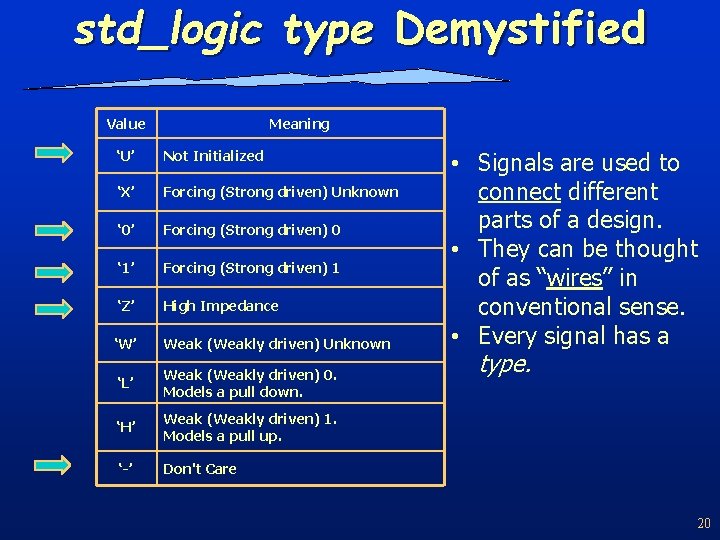

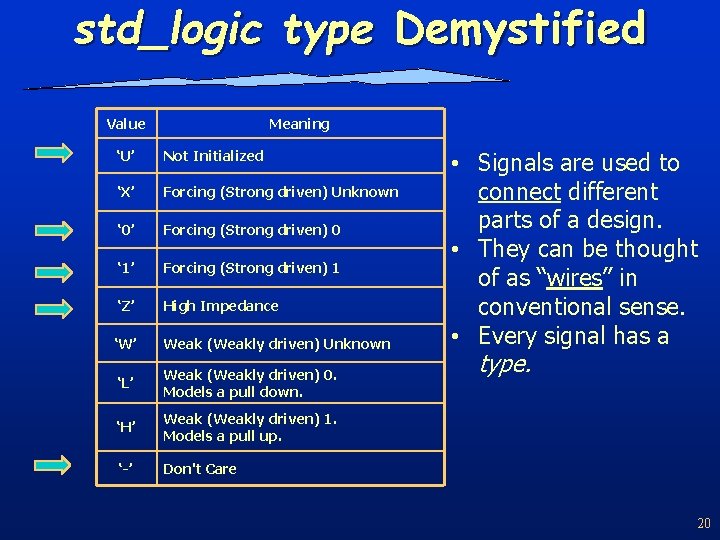

std_logic type Demystified Value Meaning ‘U’ Not Initialized ‘X’ Forcing (Strong driven) Unknown ‘ 0’ Forcing (Strong driven) 0 ‘ 1’ Forcing (Strong driven) 1 ‘Z’ High Impedance ‘W’ Weak (Weakly driven) Unknown ‘L’ Weak (Weakly driven) 0. Models a pull down. ‘H’ Weak (Weakly driven) 1. Models a pull up. ‘-’ Don't Care • Signals are used to connect different parts of a design. • They can be thought of as “wires” in conventional sense. • Every signal has a type. 20

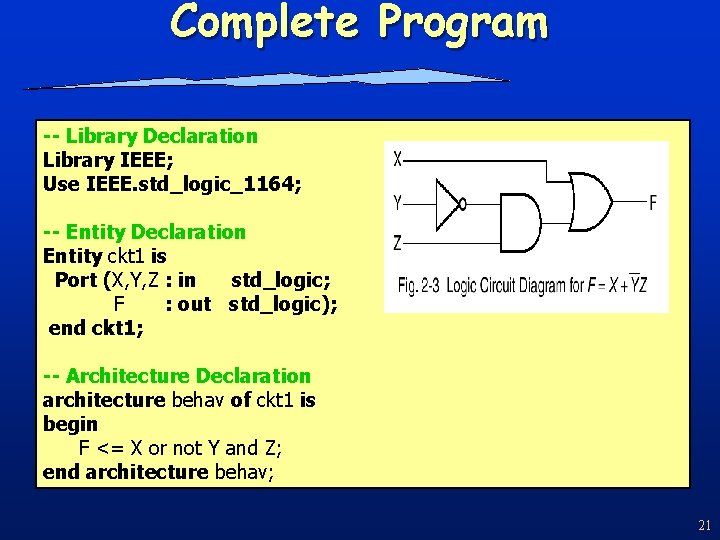

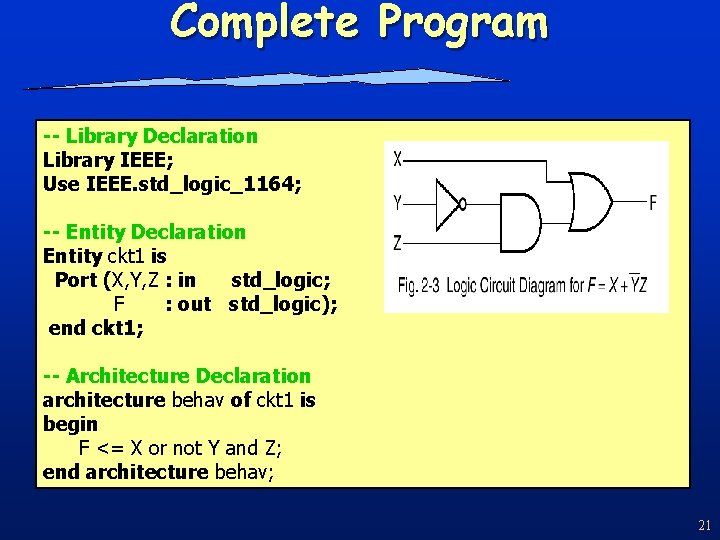

Complete Program -- Library Declaration Library IEEE; Use IEEE. std_logic_1164; -- Entity Declaration Entity ckt 1 is Port (X, Y, Z : in std_logic; F : out std_logic); end ckt 1; -- Architecture Declaration architecture behav of ckt 1 is begin F <= X or not Y and Z; end architecture behav; 21

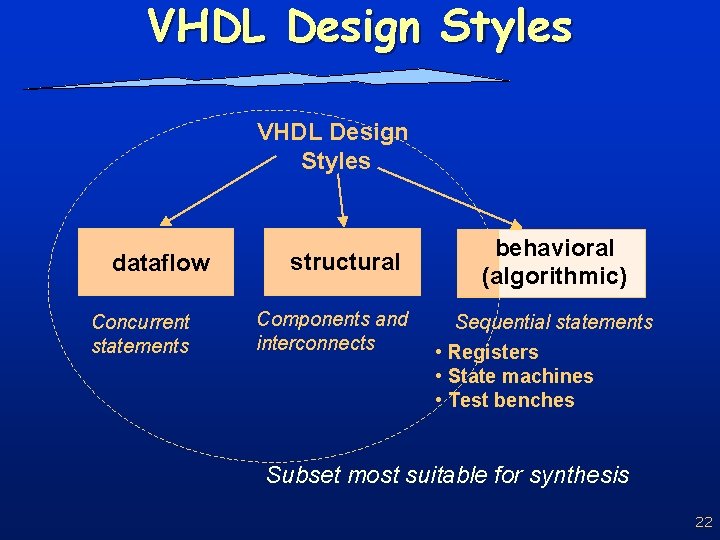

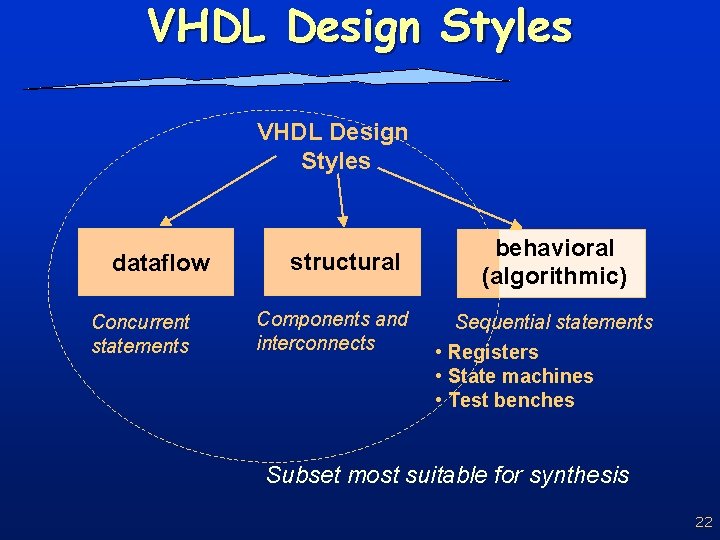

VHDL Design Styles dataflow Concurrent statements structural Components and interconnects behavioral (algorithmic) Sequential statements • Registers • State machines • Test benches Subset most suitable for synthesis 22

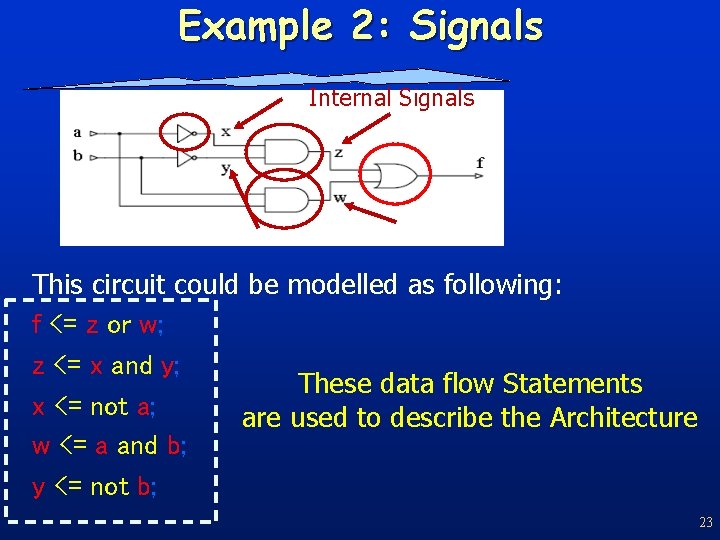

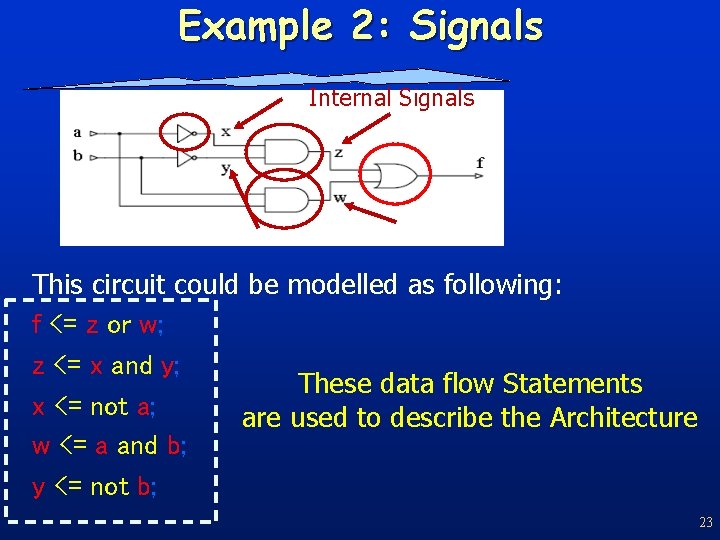

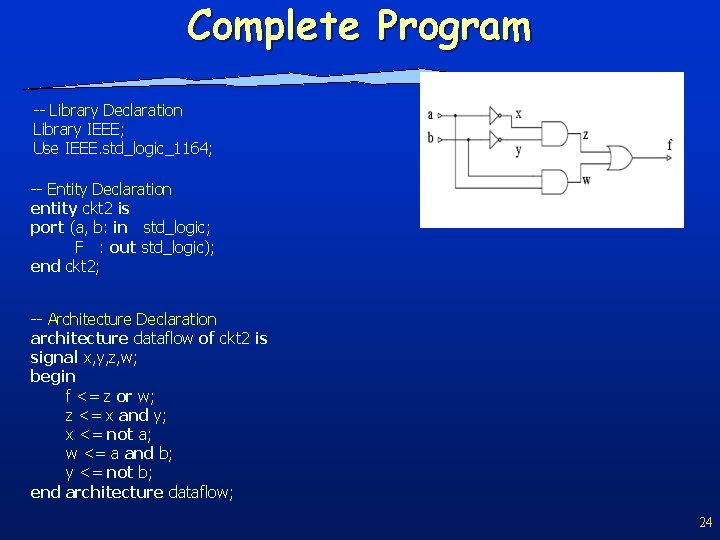

Example 2: Signals Internal Signals This circuit could be modelled as following: f <= z or w; z <= x and y; These data flow Statements x <= not a; are used to describe the Architecture w <= a and b; y <= not b; 23

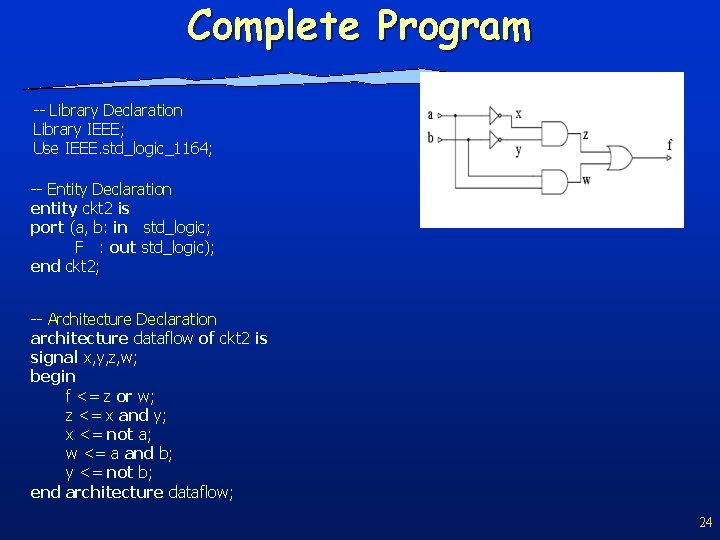

Complete Program -- Library Declaration Library IEEE; Use IEEE. std_logic_1164; -- Entity Declaration entity ckt 2 is port (a, b: in std_logic; F : out std_logic); end ckt 2; -- Architecture Declaration architecture dataflow of ckt 2 is signal x, y, z, w; begin f <= z or w; z <= x and y; x <= not a; w <= a and b; y <= not b; end architecture dataflow; 24

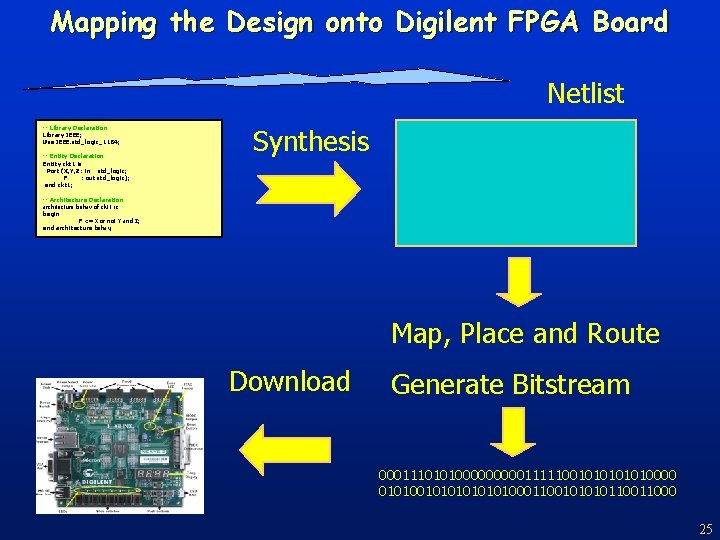

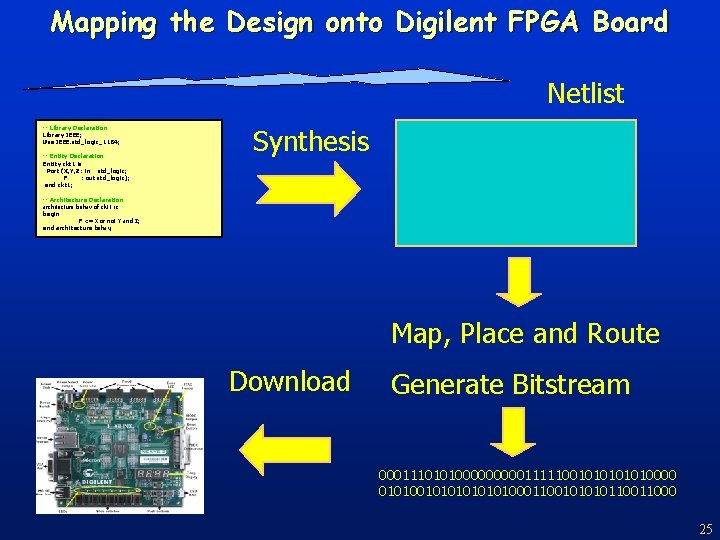

Mapping the Design onto Digilent FPGA Board Netlist -- Library Declaration Library IEEE; Use IEEE. std_logic_1164; -- Entity Declaration Entity ckt 1 is Port (X, Y, Z : in std_logic; F : out std_logic); end ckt 1; Synthesis -- Architecture Declaration architecture behav of ckt 1 is begin F <= X or not Y and Z; end architecture behav; Map, Place and Route Download Generate Bitstream 0001110101000001111100101010000 01010101000110010110011000 25