Design e Signal Processing in Hard Disk Drives

![SOC DSP : requisiti [1] q Assicurare la affidabilita dei dati § MTBF di SOC DSP : requisiti [1] q Assicurare la affidabilita dei dati § MTBF di](https://slidetodoc.com/presentation_image_h2/ad3e517fd68ebb1b9fefe588c27ba017/image-7.jpg)

![SOC DSP : requisiti [2] q Usa tecnologia avanzata, ma standard § § Nessun SOC DSP : requisiti [2] q Usa tecnologia avanzata, ma standard § § Nessun](https://slidetodoc.com/presentation_image_h2/ad3e517fd68ebb1b9fefe588c27ba017/image-8.jpg)

![Cosa proponiamo [1] 1. Microprogrammed servo sequencer modello di architettura a microcontrollore dedicata, atto Cosa proponiamo [1] 1. Microprogrammed servo sequencer modello di architettura a microcontrollore dedicata, atto](https://slidetodoc.com/presentation_image_h2/ad3e517fd68ebb1b9fefe588c27ba017/image-11.jpg)

![Cosa proponiamo [2] 1. Caratterizzazione sperimentale degli eventi errore di un drive e proiezione Cosa proponiamo [2] 1. Caratterizzazione sperimentale degli eventi errore di un drive e proiezione](https://slidetodoc.com/presentation_image_h2/ad3e517fd68ebb1b9fefe588c27ba017/image-12.jpg)

- Slides: 12

Design e Signal Processing in Hard Disk Drives ST Microelectronics – DSD Castelletto {angelo. dati, mariasilvia. ratto}@st. com COMPUTER PERIPHERAL GROUP

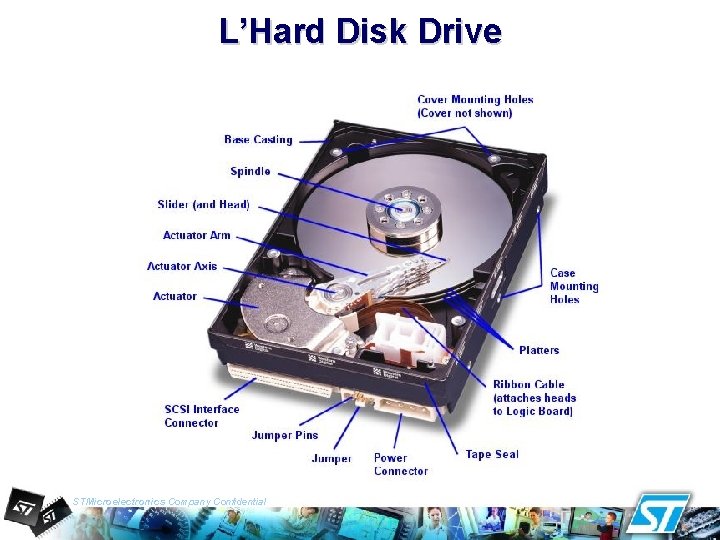

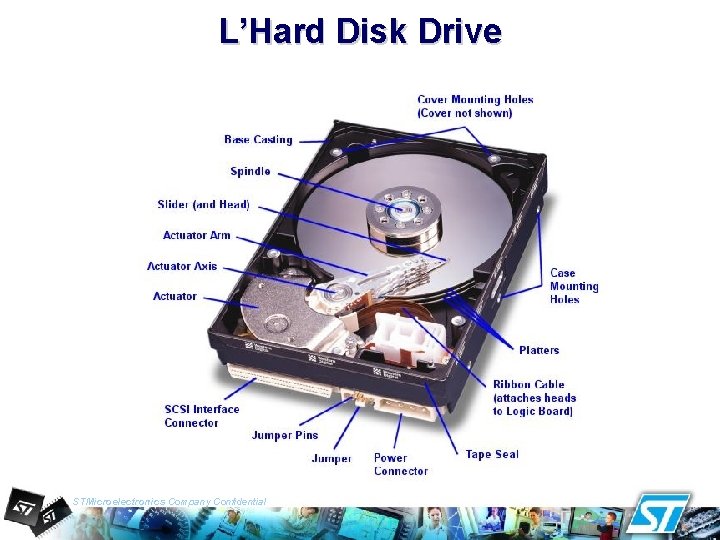

L’Hard Disk Drive STMicroelectronics Company Confidential

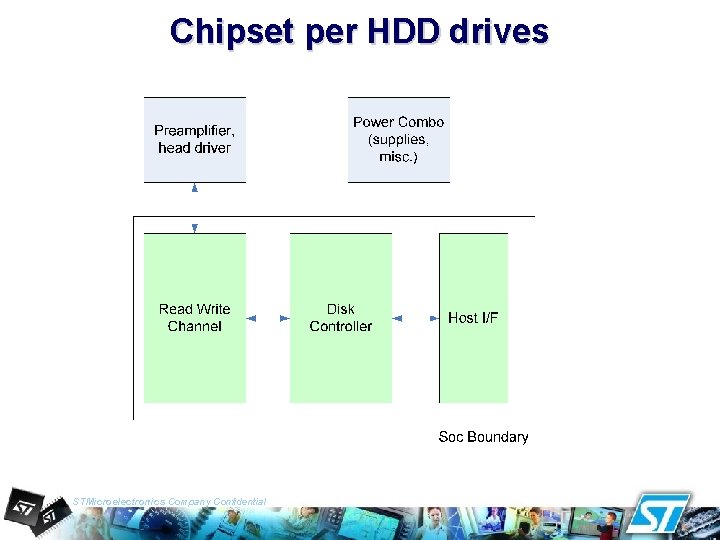

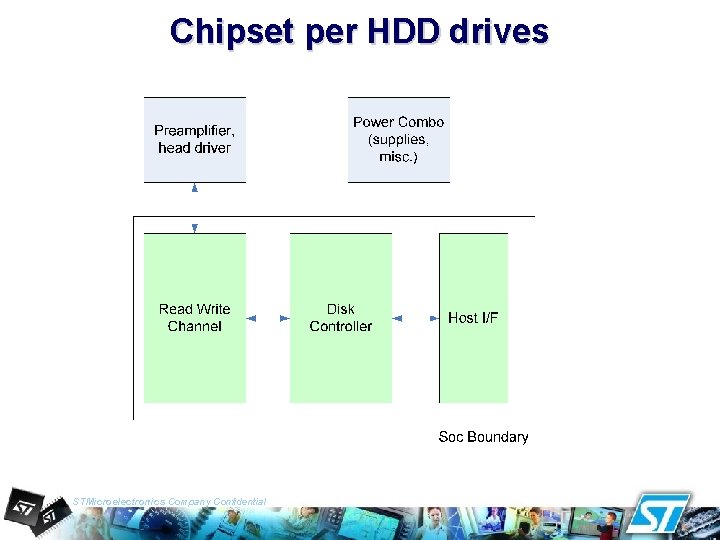

Chipset per HDD drives STMicroelectronics Company Confidential

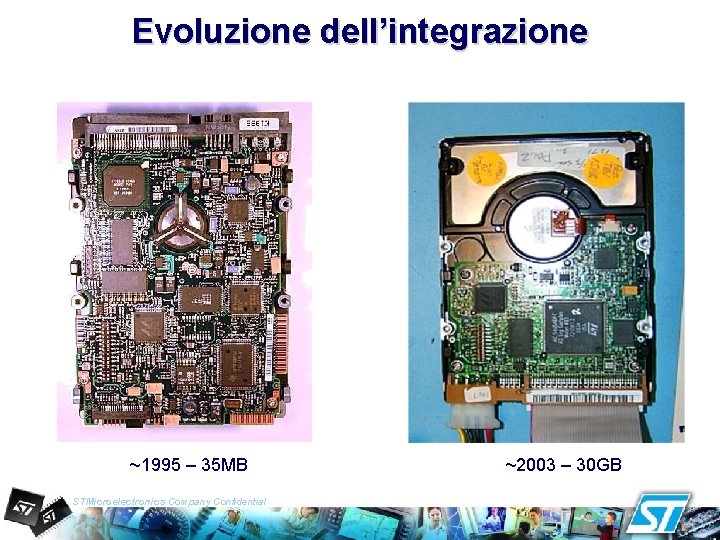

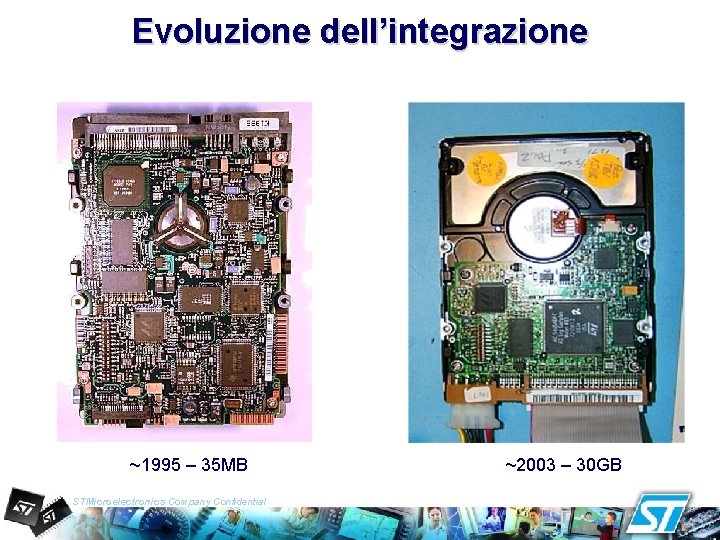

Evoluzione dell’integrazione ~1995 – 35 MB STMicroelectronics Company Confidential ~2003 – 30 GB

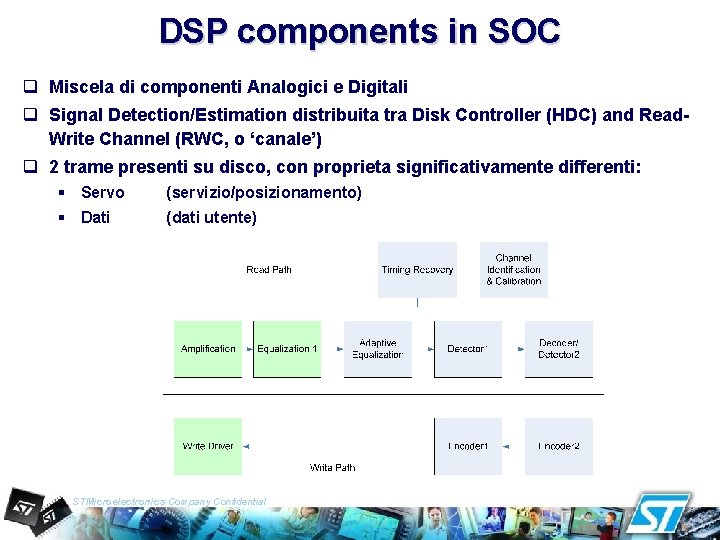

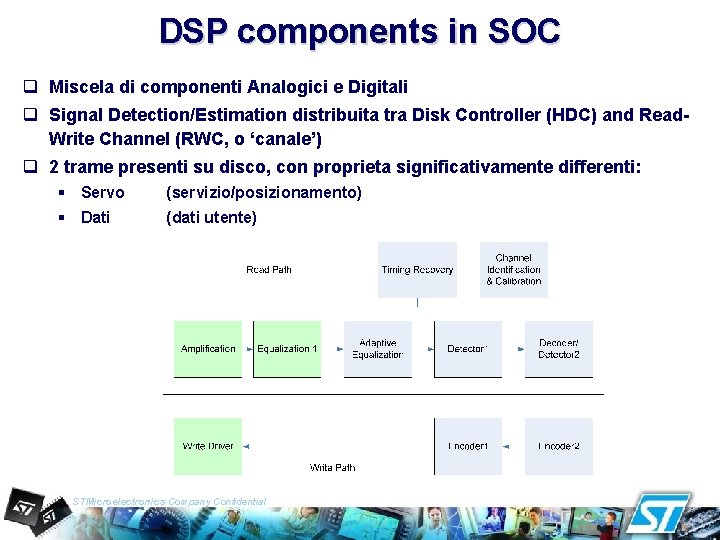

DSP components in SOC q Miscela di componenti Analogici e Digitali q Signal Detection/Estimation distribuita tra Disk Controller (HDC) and Read. Write Channel (RWC, o ‘canale’) q 2 trame presenti su disco, con proprieta significativamente differenti: § Servo (servizio/posizionamento) § Dati (dati utente) STMicroelectronics Company Confidential

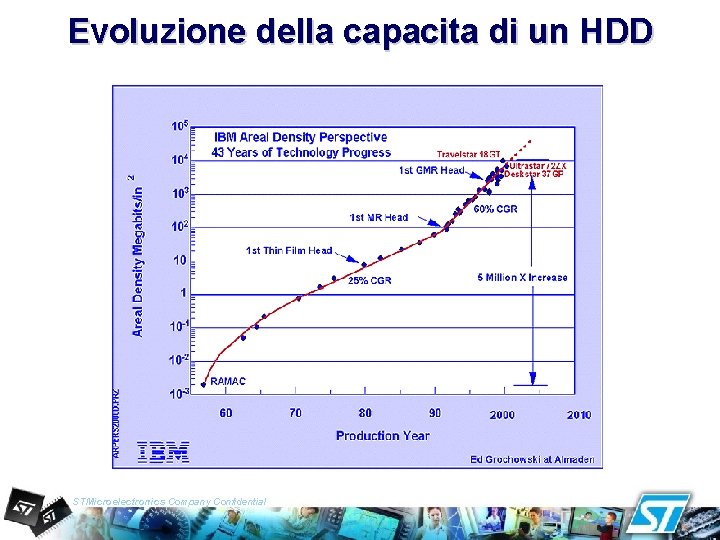

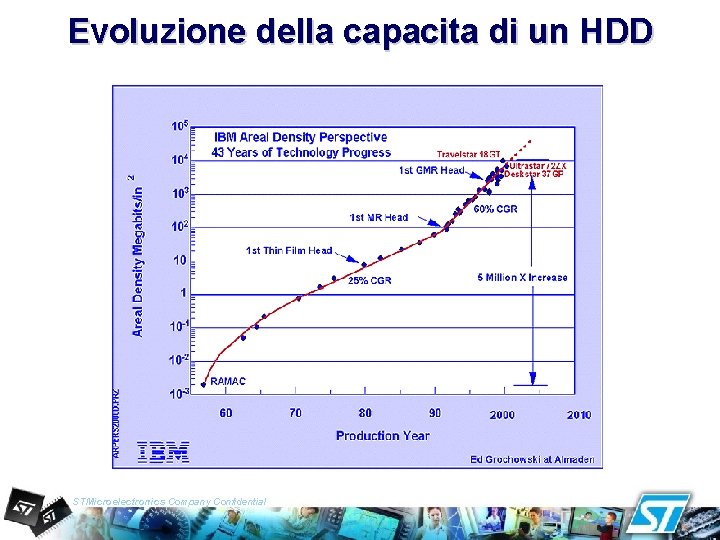

Evoluzione della capacita di un HDD STMicroelectronics Company Confidential

![SOC DSP requisiti 1 q Assicurare la affidabilita dei dati MTBF di SOC DSP : requisiti [1] q Assicurare la affidabilita dei dati § MTBF di](https://slidetodoc.com/presentation_image_h2/ad3e517fd68ebb1b9fefe588c27ba017/image-7.jpg)

SOC DSP : requisiti [1] q Assicurare la affidabilita dei dati § MTBF di 5 -10 y, 50% power cycle q Supportare la crescita di areal-density § ~30%/y q Supportare la crescita in transfer rate § Attualmente uno dei piu’ veloci ‘problemi’ di DSP, ~20% crescita /anno q Ciclo di produzione breve § Meno di 1 anno – ‘efficiente’ nel design ed architettura. STMicroelectronics Company Confidential

![SOC DSP requisiti 2 q Usa tecnologia avanzata ma standard Nessun SOC DSP : requisiti [2] q Usa tecnologia avanzata, ma standard § § Nessun](https://slidetodoc.com/presentation_image_h2/ad3e517fd68ebb1b9fefe588c27ba017/image-8.jpg)

SOC DSP : requisiti [2] q Usa tecnologia avanzata, ma standard § § Nessun ‘trucco’ da tecnologia militare Piena Resa, costi di produzione da consumer; Nessuna ridondanza 2006 – 90 nm production q Deve (sor)passare scenari di test consolidati nell’industria § Win. Bench (…) q Nessuna sofisticata procedura firmware q Supportare piattaforme multiple § Handheld e Enterprise servers con lo stesso dispositivo STMicroelectronics Company Confidential

Read Write Channel in ST-Castelletto q ST e’ uno delle 3 sole compagnie in produzione con un HDC SOC § Tecnologia alla portata di <10 compagnie nell’industria dei semiconduttori q E’ il solo produttore Europeo § Gli altri 2 sono in USA q Il Know-How di base e’ in Italia, a Castelletto § 14+ anni di storia § Gruppo in espansione (~30% nel 2005 -2006) q 50+ tra designer analogici, digitali, sistema a Castelletto § Resto del sistema & supporto: >200 persone tra US, EU, Asia STMicroelectronics Company Confidential

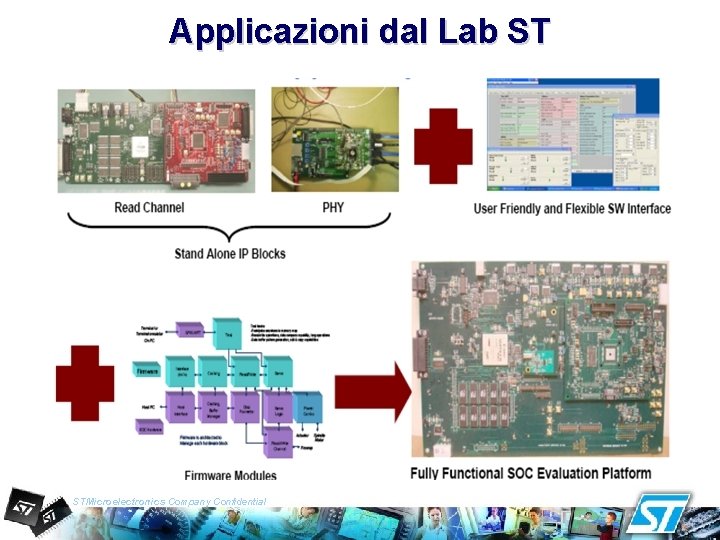

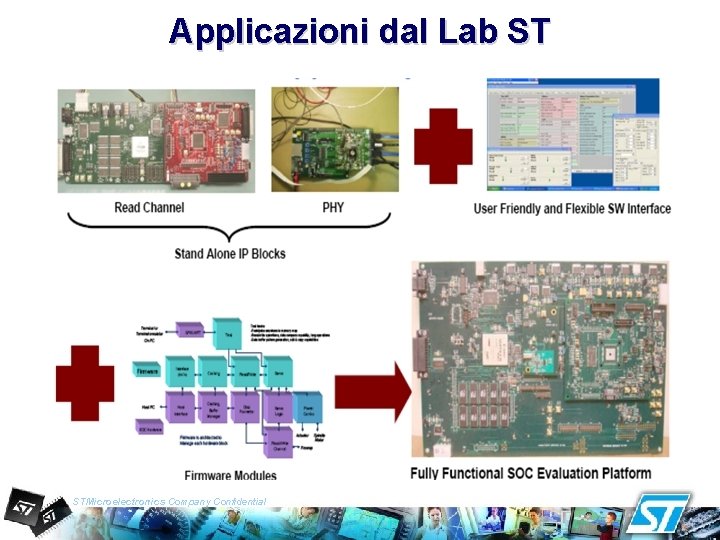

Applicazioni dal Lab ST STMicroelectronics Company Confidential

![Cosa proponiamo 1 1 Microprogrammed servo sequencer modello di architettura a microcontrollore dedicata atto Cosa proponiamo [1] 1. Microprogrammed servo sequencer modello di architettura a microcontrollore dedicata, atto](https://slidetodoc.com/presentation_image_h2/ad3e517fd68ebb1b9fefe588c27ba017/image-11.jpg)

Cosa proponiamo [1] 1. Microprogrammed servo sequencer modello di architettura a microcontrollore dedicata, atto a realizzare la logica di controllo del sottosistema servo di un canale per hard disk 2. Test. Plan Verification Coverage Realizzazione di strumenti automatici per il tracciamento di attività legate alla verifica 3. Strategie di Progettazione Self-Checking per la Sintesi di Circuiti Digitali Individuare la migliore Strategia per la sintesi di circuiti sequenziali sincroni in grado di soddisfare i requisiti di “Concurrent Error Detection” (CED) 4. Studio e realizzazione di tecniche di “Voltage Margining for Power saving” per l’applicazione R/W channel Comparazione tra “Fixed Voltage power” e “Closed loop Voltage” STMicroelectronics Company Confidential

![Cosa proponiamo 2 1 Caratterizzazione sperimentale degli eventi errore di un drive e proiezione Cosa proponiamo [2] 1. Caratterizzazione sperimentale degli eventi errore di un drive e proiezione](https://slidetodoc.com/presentation_image_h2/ad3e517fd68ebb1b9fefe588c27ba017/image-12.jpg)

Cosa proponiamo [2] 1. Caratterizzazione sperimentale degli eventi errore di un drive e proiezione dell'efficienza di uno schema di error correction code in funzione della lunghezza del simbolo (10 o 12 bit). 2. Caratterizzazione di un simulatore veloce di eventi errore di un drive per la verifica delle prestazioni di schemi a correzione d'errore. 3. Caratterizzazione dei burst di errore di un sistema DFE finalizzato alla timing recovery della trama di un ricevitore per Hard Disk Drive, e loro impatto sulle prestazioni di loss of lock del sistema. STMicroelectronics Company Confidential