DESIGN CONSTRAINT ANALYSIS Team 6 System Block Diagram

DESIGN CONSTRAINT ANALYSIS Team 6

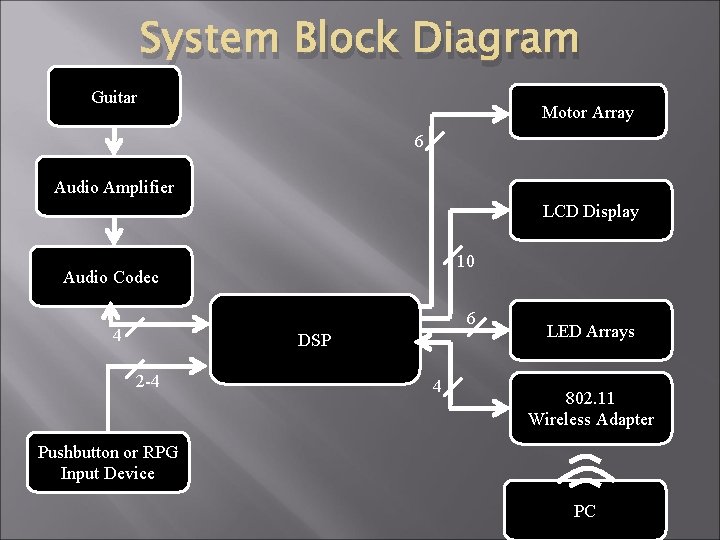

System Block Diagram Guitar Motor Array 6 Audio Amplifier LCD Display 10 Audio Codec 6 4 DSP 2 -4 4 LED Arrays 802. 11 Wireless Adapter Pushbutton or RPG Input Device PC

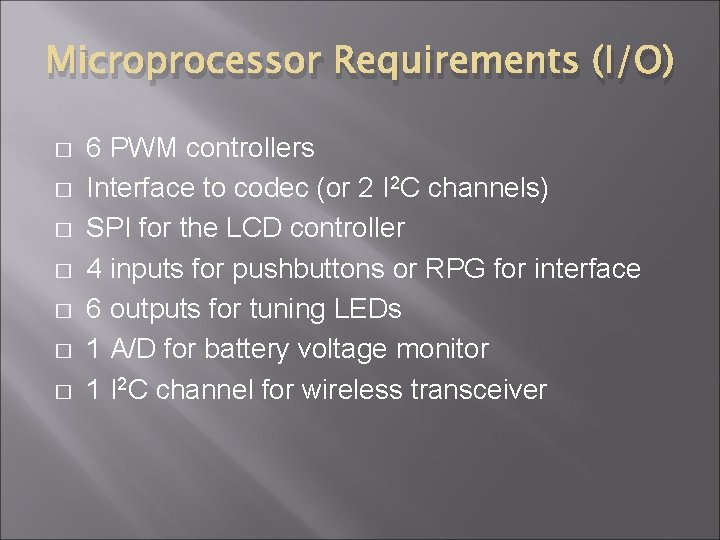

Microprocessor Requirements (I/O) � � � � 6 PWM controllers Interface to codec (or 2 I 2 C channels) SPI for the LCD controller 4 inputs for pushbuttons or RPG for interface 6 outputs for tuning LEDs 1 A/D for battery voltage monitor 1 I 2 C channel for wireless transceiver

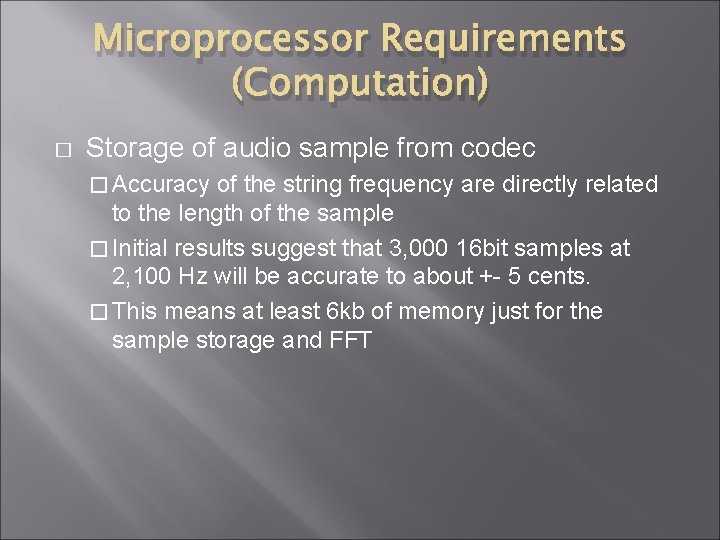

Microprocessor Requirements (Computation) � Storage of audio sample from codec � Accuracy of the string frequency are directly related to the length of the sample � Initial results suggest that 3, 000 16 bit samples at 2, 100 Hz will be accurate to about +- 5 cents. � This means at least 6 kb of memory just for the sample storage and FFT

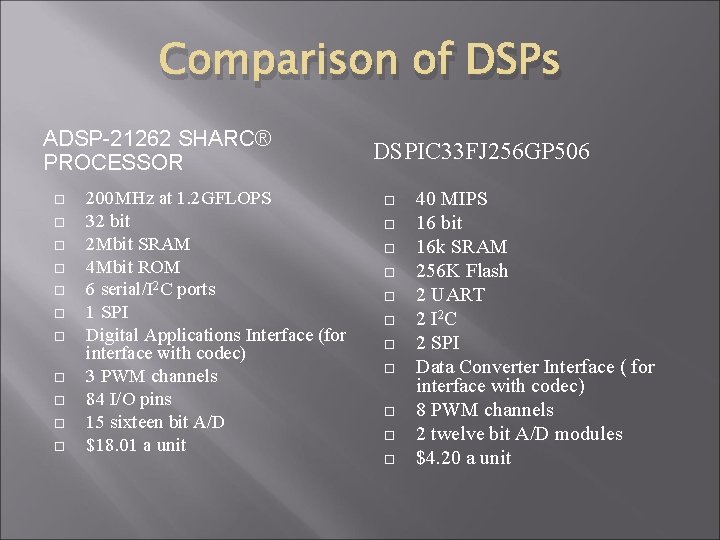

Comparison of DSPs ADSP-21262 SHARC® PROCESSOR DSPIC 33 FJ 256 GP 506

Comparison of DSPs ADSP-21262 SHARC® PROCESSOR 200 MHz at 1. 2 GFLOPS 32 bit 2 Mbit SRAM 4 Mbit ROM 6 serial/I 2 C ports 1 SPI Digital Applications Interface (for interface with codec) 3 PWM channels 84 I/O pins 15 sixteen bit A/D $18. 01 a unit DSPIC 33 FJ 256 GP 506 40 MIPS 16 bit 16 k SRAM 256 K Flash 2 UART 2 I 2 C 2 SPI Data Converter Interface ( for interface with codec) 8 PWM channels 2 twelve bit A/D modules $4. 20 a unit

Comparison of DSPs � � � We chose the ds. PIC 33 FJ 256 GP 506. Powerful enough to perform required calculations Enough PWM channels for motors Requires minimal external hardware Team has experience with PIC architecture and development environment

- Slides: 7