Design Considerations in CLBs for Deep SubMicron Technologies

Design Considerations in CLBs for Deep Sub-Micron Technologies Louis Alarcón Octavian Florescu

Motivation As technology scales… – The effects due to process variations will become more pronounced. • Regular structures are needed to mitigate these effects. – Leakage will increase as the VTH are scaled. • Low leakage architectures will be needed to control stand-by power.

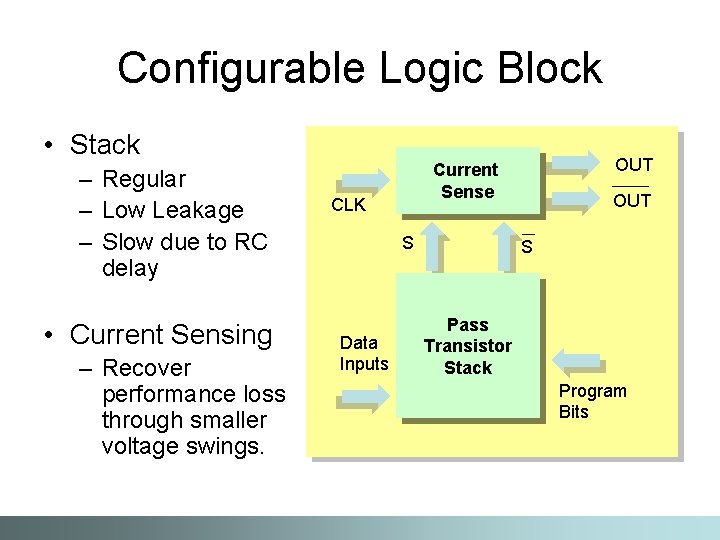

Configurable Logic Block • Stack – Regular – Low Leakage – Slow due to RC delay • Current Sensing – Recover performance loss through smaller voltage swings. CLK S Data Inputs OUT Current Sense OUT S Pass Transistor Stack Program Bits

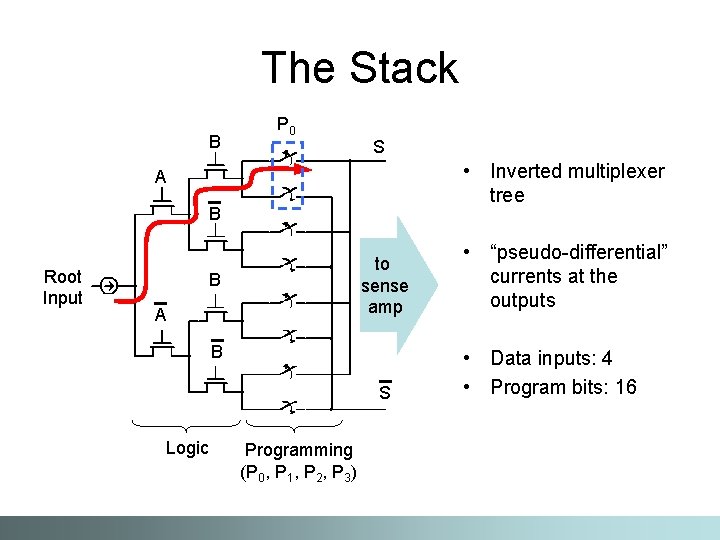

The Stack B P 0 S • Inverted multiplexer tree A B Root Input to sense amp B A B S Logic Programming (P 0, P 1, P 2, P 3) • “pseudo-differential” currents at the outputs • Data inputs: 4 • Program bits: 16

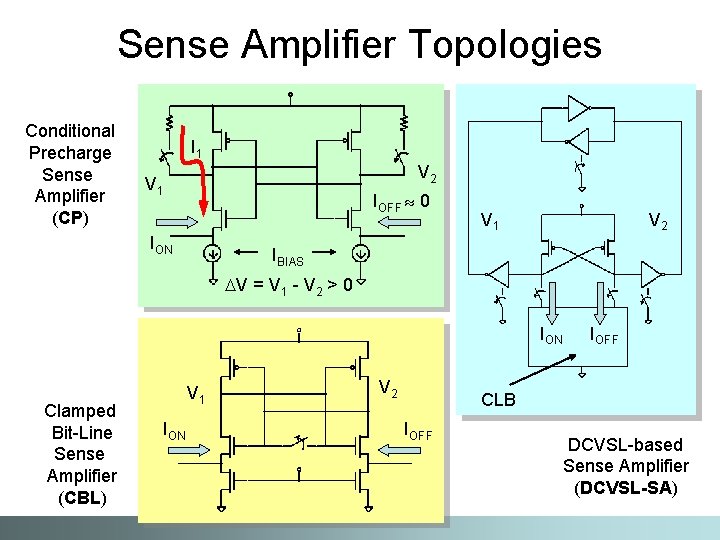

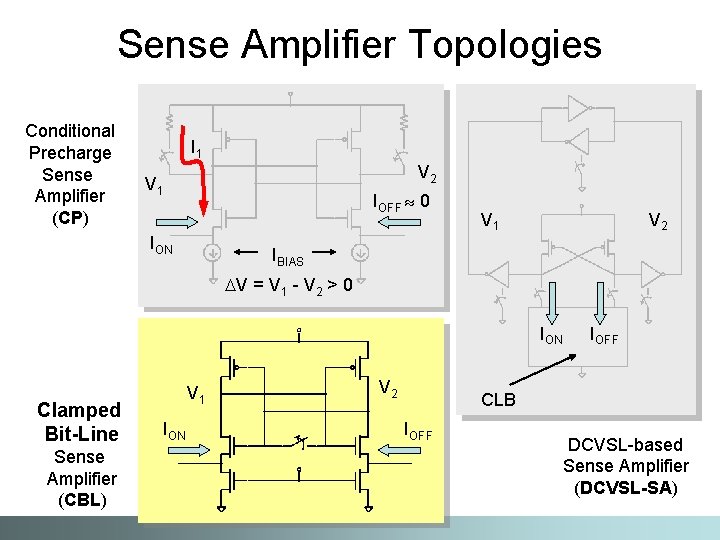

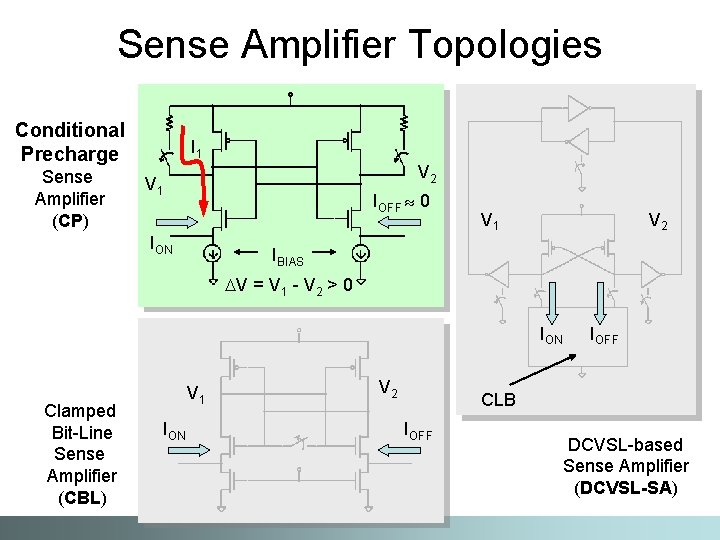

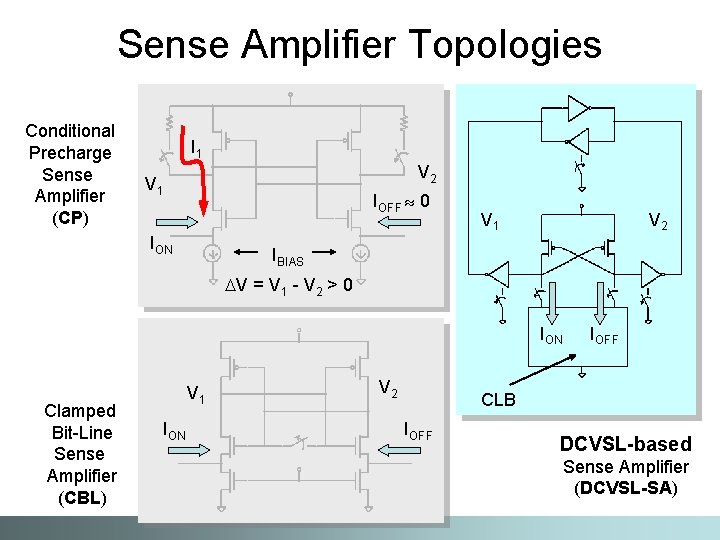

Sense Amplifier Topologies Conditional Precharge Sense Amplifier (CP) I 1 V 2 V 1 IOFF 0 ION V 1 V 2 IBIAS V = V 1 - V 2 > 0 ION Clamped Bit-Line Sense Amplifier (CBL) V 1 ION V 2 IOFF CLB IOFF DCVSL-based Sense Amplifier (DCVSL-SA)

Sense Amplifier Topologies Conditional Precharge Sense Amplifier (CP) I 1 V 2 V 1 IOFF 0 ION V 1 V 2 IBIAS V = V 1 - V 2 > 0 ION Clamped Bit-Line Sense Amplifier (CBL) V 1 ION V 2 IOFF CLB IOFF DCVSL-based Sense Amplifier (DCVSL-SA)

Sense Amplifier Topologies Conditional Precharge Sense Amplifier (CP) I 1 V 2 V 1 IOFF 0 ION V 1 V 2 IBIAS V = V 1 - V 2 > 0 ION Clamped Bit-Line Sense Amplifier (CBL) V 1 ION V 2 IOFF CLB IOFF DCVSL-based Sense Amplifier (DCVSL-SA)

Sense Amplifier Topologies Conditional Precharge Sense Amplifier (CP) I 1 V 2 V 1 IOFF 0 ION V 1 V 2 IBIAS V = V 1 - V 2 > 0 ION Clamped Bit-Line Sense Amplifier (CBL) V 1 ION V 2 IOFF CLB IOFF DCVSL-based Sense Amplifier (DCVSL-SA)

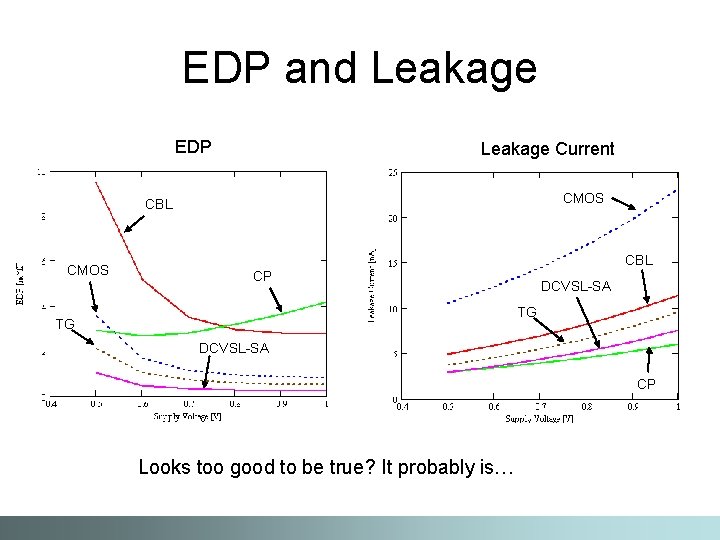

EDP and Leakage EDP Leakage Current CMOS CBL CP DCVSL-SA TG TG DCVSL-SA CP Looks too good to be true? It probably is…

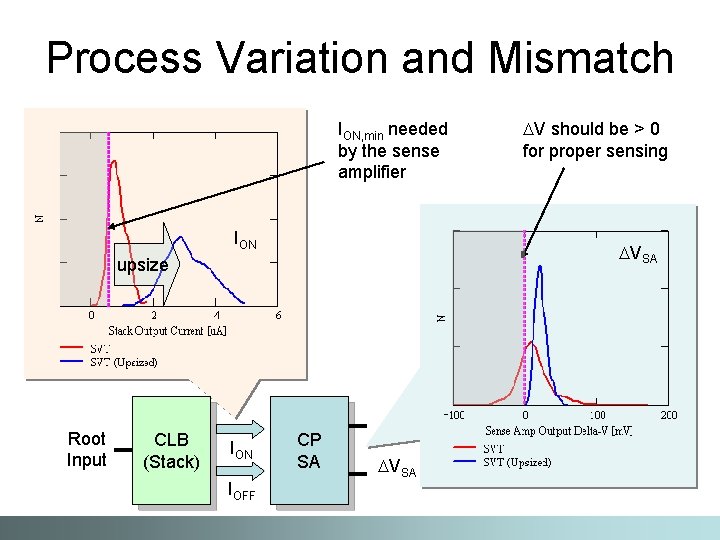

Process Variation and Mismatch ION, min needed by the sense amplifier ION VSA upsize Root Input CLB (Stack) ION IOFF V should be > 0 for proper sensing CP SA VSA

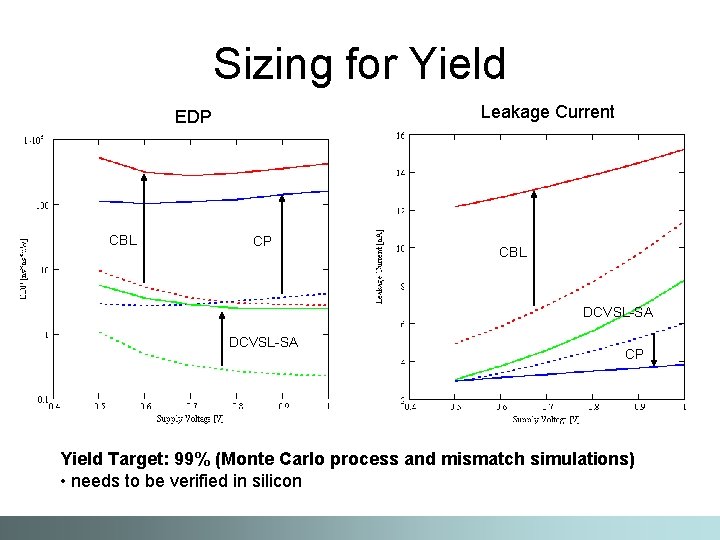

Sizing for Yield Leakage Current EDP CBL CP CBL DCVSL-SA CP Yield Target: 99% (Monte Carlo process and mismatch simulations) • needs to be verified in silicon

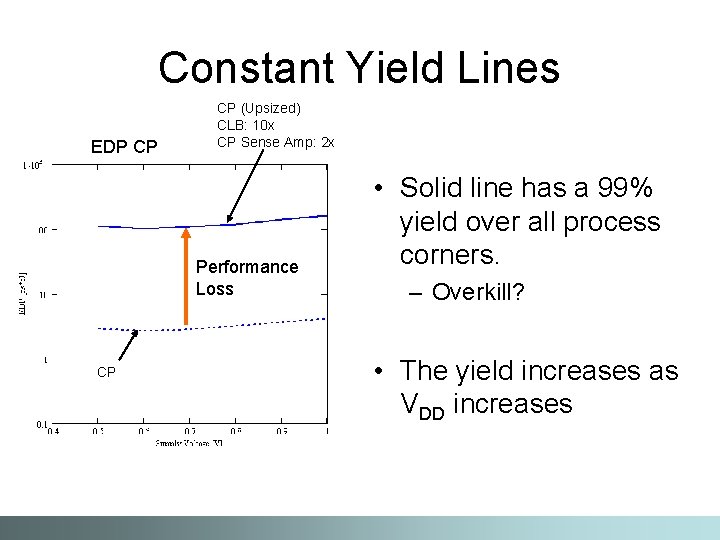

Constant Yield Lines EDP CP CP (Upsized) CLB: 10 x CP Sense Amp: 2 x Performance Loss CP • Solid line has a 99% yield over all process corners. – Overkill? • The yield increases as VDD increases

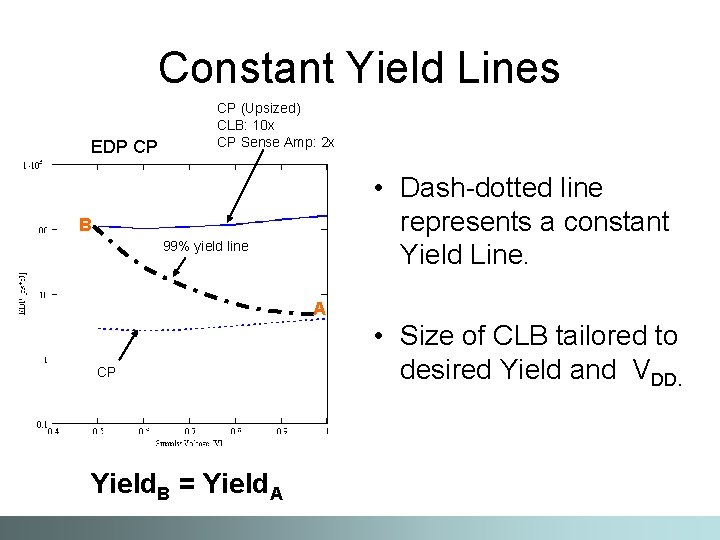

Constant Yield Lines EDP CP CP (Upsized) CLB: 10 x CP Sense Amp: 2 x • Dash-dotted line represents a constant Yield Line. B 99% yield line A CP Yield. B = Yield. A • Size of CLB tailored to desired Yield and VDD.

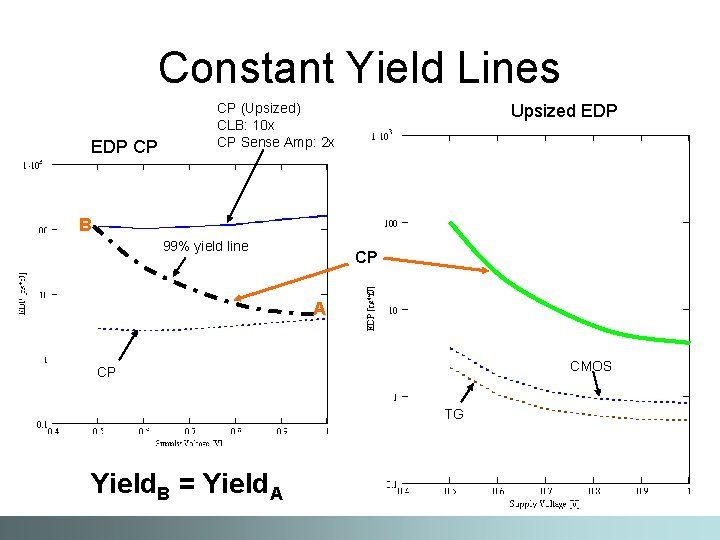

Constant Yield Lines EDP CP CP (Upsized) CLB: 10 x CP Sense Amp: 2 x Upsized EDP B 99% yield line CP A CMOS CP TG Yield. B = Yield. A

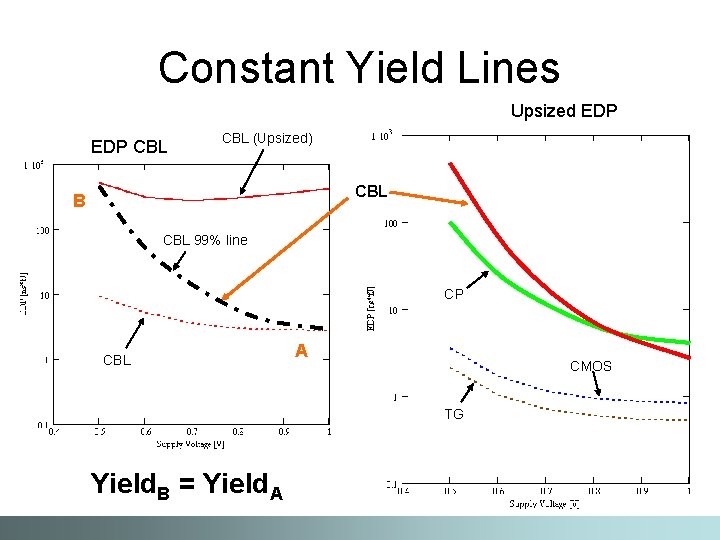

Constant Yield Lines Upsized EDP CBL (Upsized) CBL B CBL 99% line CP CBL A CMOS TG Yield. B = Yield. A

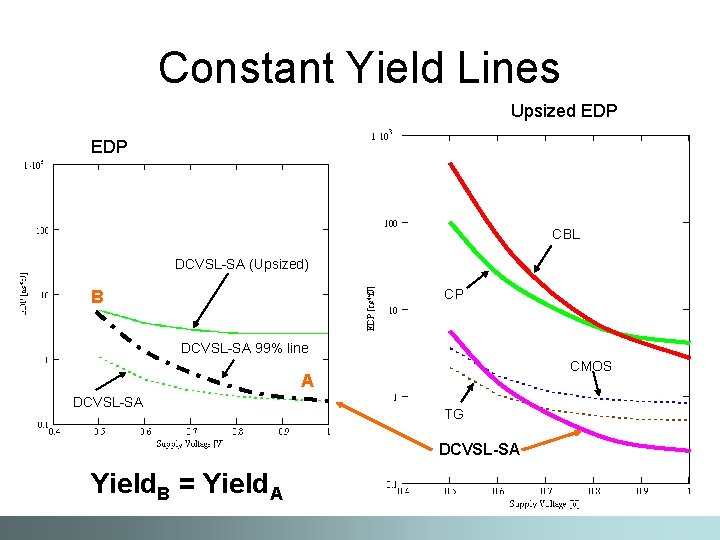

Constant Yield Lines Upsized EDP CBL DCVSL-SA (Upsized) CP B DCVSL-SA 99% line CMOS A DCVSL-SA TG DCVSL-SA Yield. B = Yield. A

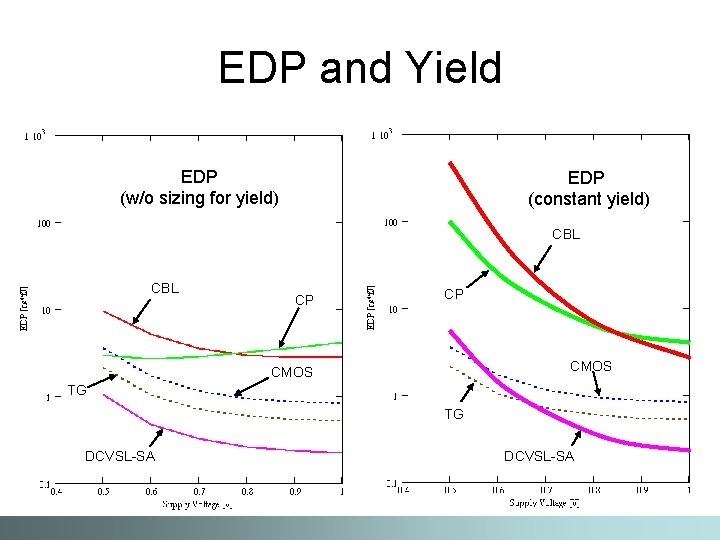

EDP and Yield EDP (w/o sizing for yield) EDP (constant yield) CBL CP CP CMOS TG TG DCVSL-SA

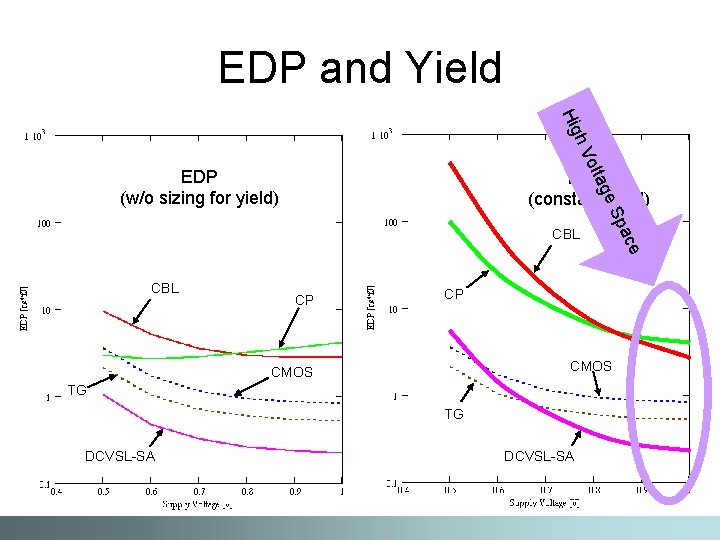

EDP and Yield olta h. V Hig EDP (w/o sizing for yield) ge EDP (constant yield) CP CP CMOS TG TG DCVSL-SA ace CBL Sp CBL

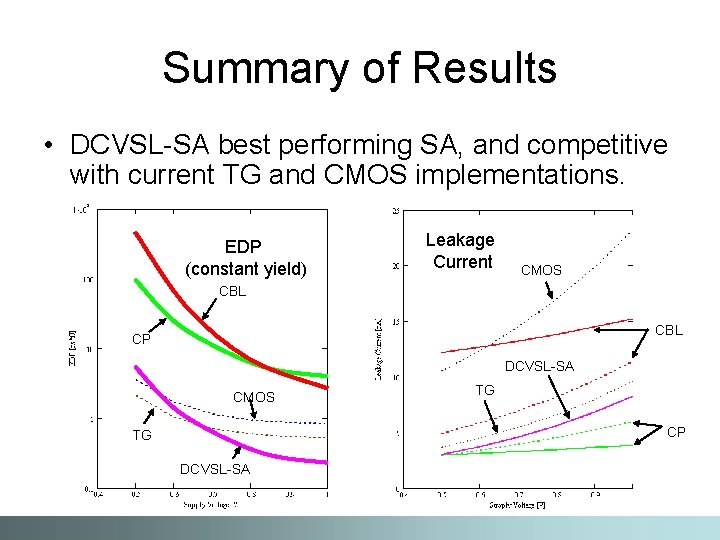

Summary of Results • DCVSL-SA best performing SA, and competitive with current TG and CMOS implementations. However… Leakage • More difficult. EDP to design Current (constant yield) CMOS – Analog-like. CBL design process • Less versatile CBL CP – Mandatory latch at the output – DVS CMOS • Higher design risk TG – 6 unacceptable DCVSL-SA TG CP

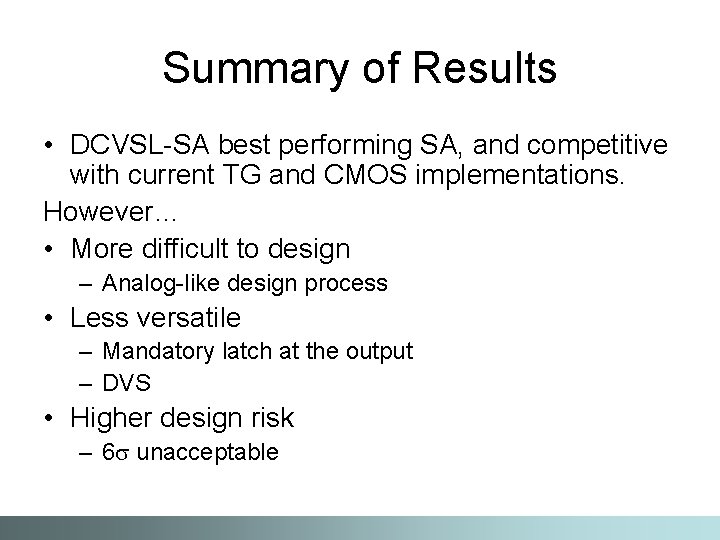

Summary of Results • DCVSL-SA best performing SA, and competitive with current TG and CMOS implementations. However… • More difficult to design – Analog-like design process • Less versatile – Mandatory latch at the output – DVS • Higher design risk – 6 unacceptable

Sense Amplifiers in Future Technologies • Design of Sense Amplifiers in the future will become more challenging. – Impact of process variations will become more pronounced – VDD will continue to scale • VSA/VDD increases • VTH/VDD increases • The useful design space will be limited. – Low leakage environments – High voltage, low energy space

Thank you

Design Considerations in CLBs for Deep Sub-Micron Technologies Louis Alarcon Octavian Florescu

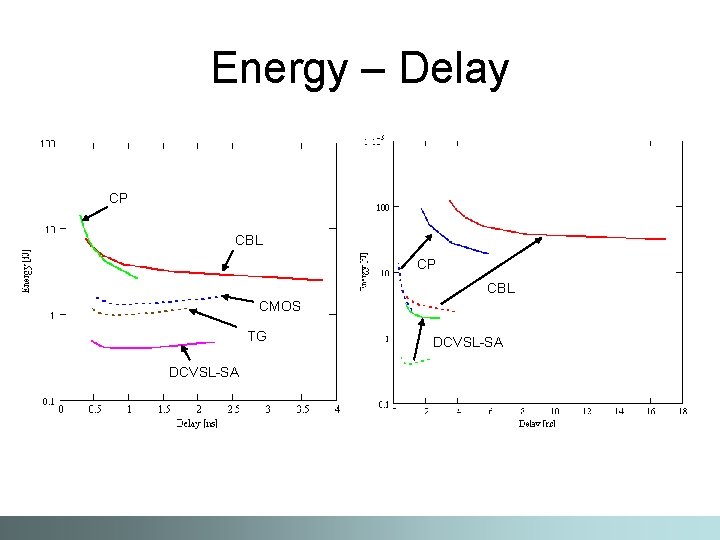

Energy – Delay CP CBL CMOS TG DCVSL-SA

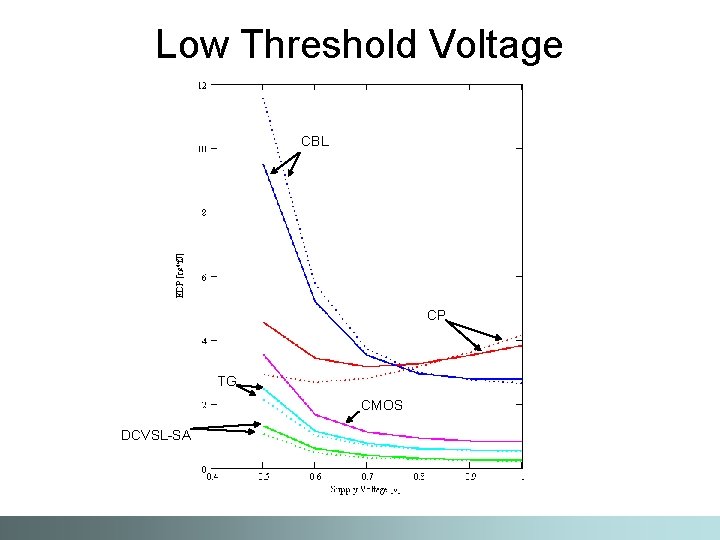

Low Threshold Voltage CBL CP TG CMOS DCVSL-SA

- Slides: 25