Design AXI Master Page 1 XILINX CONFIDENTIAL Agenda

- Slides: 21

Design AXI Master Page 1 XILINX CONFIDENTIAL.

Agenda Understanding Zynq AXI Master IP axi_user_npi Page 2 © Copyright 2012 Xilinx XILINX CONFIDENTIAL.

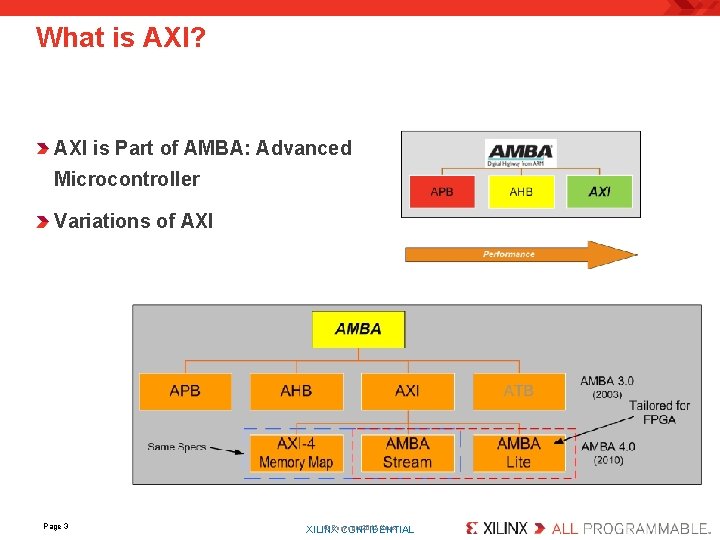

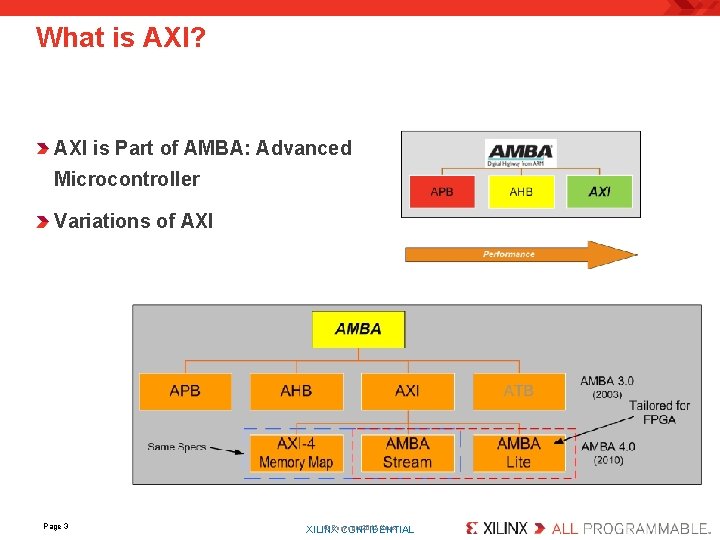

What is AXI? AXI is Part of AMBA: Advanced Microcontroller Variations of AXI Page 3 © Copyright 2012 Xilinx XILINX CONFIDENTIAL.

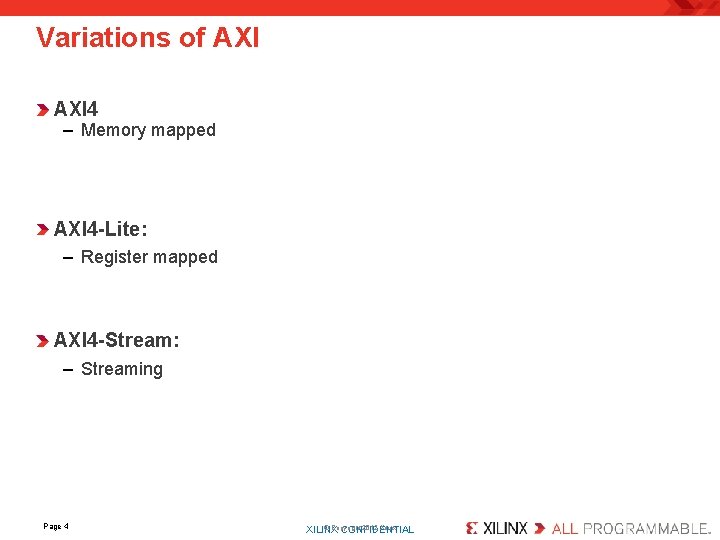

Variations of AXI 4 – Memory mapped AXI 4 -Lite: – Register mapped AXI 4 -Stream: – Streaming Page 4 © Copyright 2012 Xilinx XILINX CONFIDENTIAL.

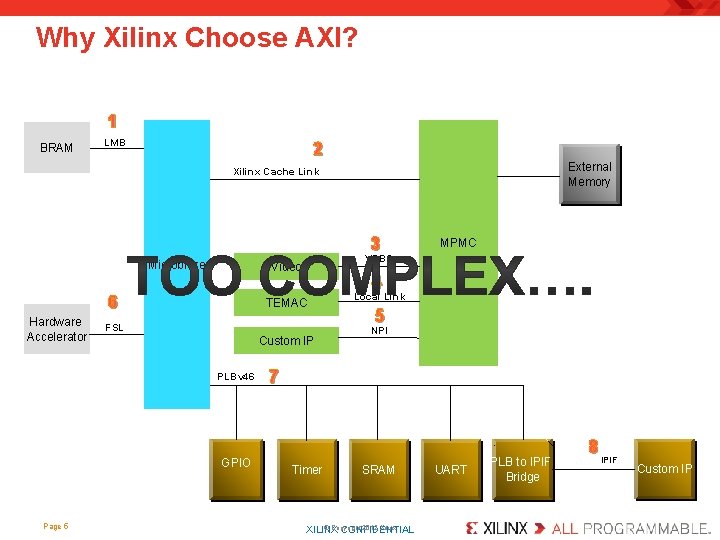

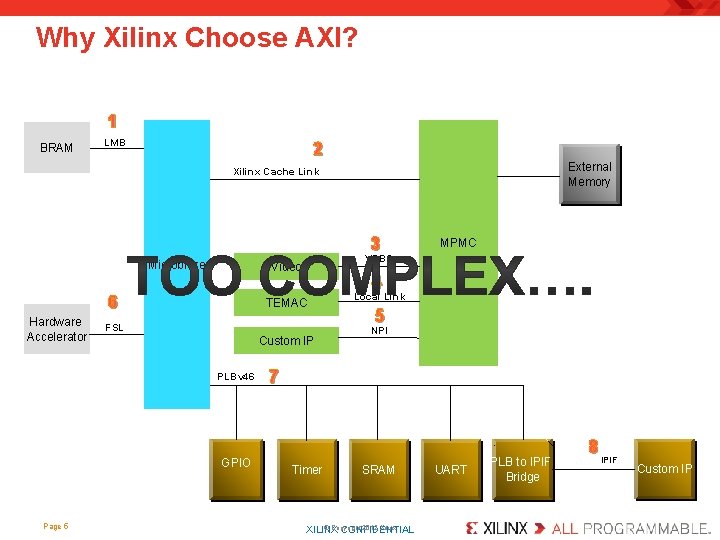

Why Xilinx Choose AXI? 1 BRAM LMB 2 External Memory Xilinx Cache Link 3 Microblaze Hardware Accelerator 4 TEMAC Local Link 5 FSL NPI Custom IP PLBv 46 GPIO Page 5 VFBC Video 6 MPMC 7 Timer SRAM © Copyright 2012 Xilinx XILINX CONFIDENTIAL. UART PLB to IPIF Bridge 8 IPIF Custom IP

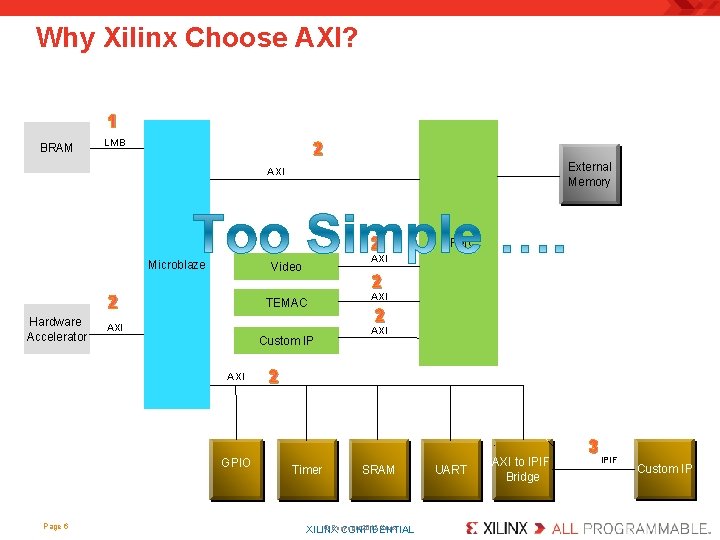

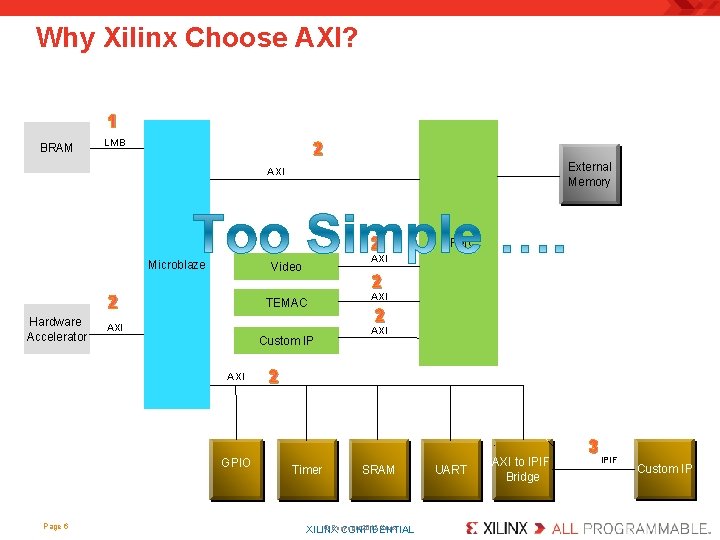

Why Xilinx Choose AXI? 1 BRAM LMB 2 External Memory AXI 2 Microblaze Hardware Accelerator 2 AXI TEMAC 2 AXI Custom IP AXI GPIO Page 6 AXI Video 2 MPMC 2 Timer SRAM © Copyright 2012 Xilinx XILINX CONFIDENTIAL. UART AXI to IPIF Bridge 3 IPIF Custom IP

AXI Protocol, Channel – Read address – Write address – Read data – Write response Page 7 © Copyright 2012 Xilinx XILINX CONFIDENTIAL.

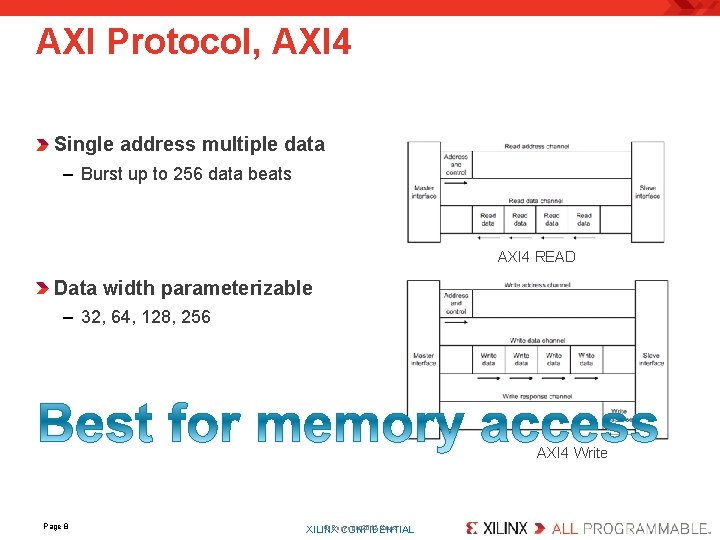

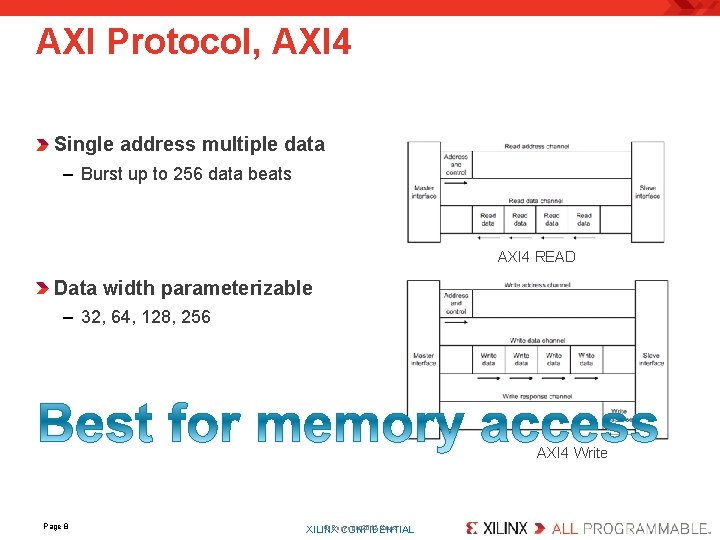

AXI Protocol, AXI 4 Single address multiple data – Burst up to 256 data beats AXI 4 READ Data width parameterizable – 32, 64, 128, 256 AXI 4 Write Page 8 © Copyright 2012 Xilinx XILINX CONFIDENTIAL.

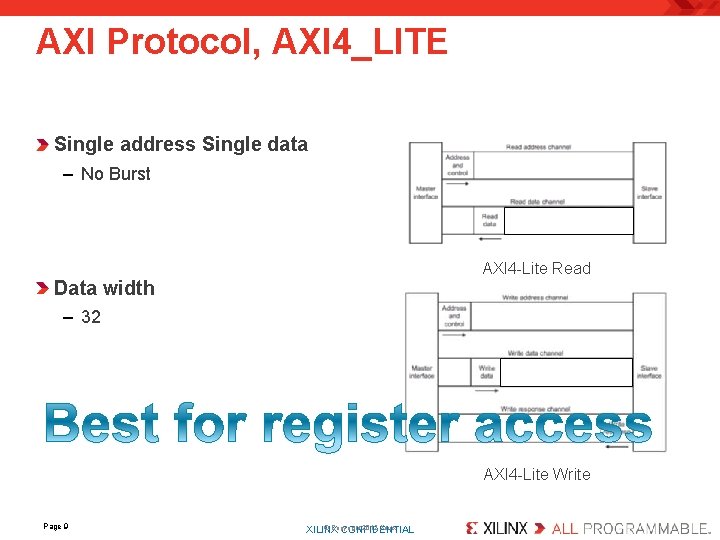

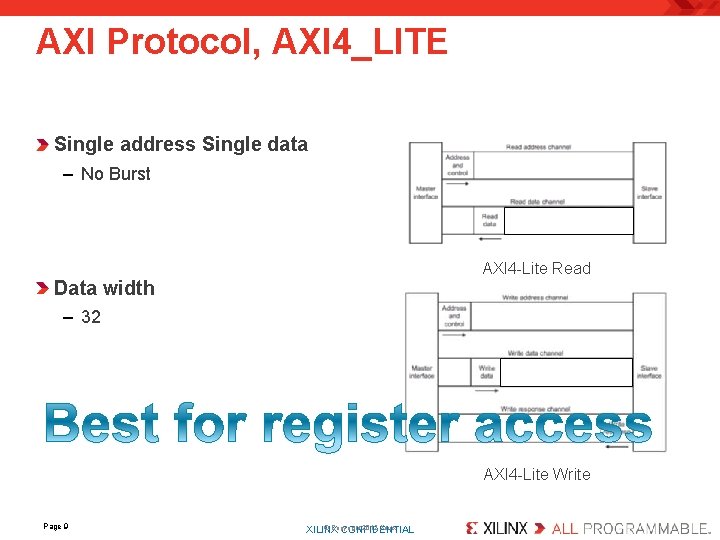

AXI Protocol, AXI 4_LITE Single address Single data – No Burst AXI 4 -Lite Read Data width – 32 AXI 4 -Lite Write Page 9 © Copyright 2012 Xilinx XILINX CONFIDENTIAL.

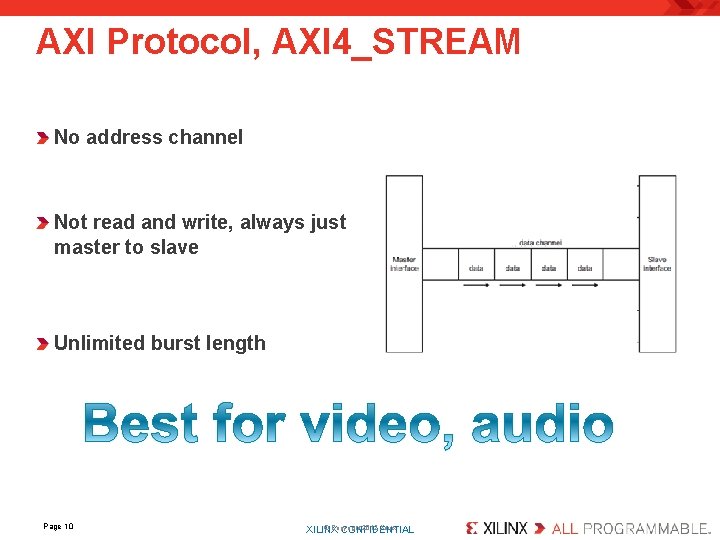

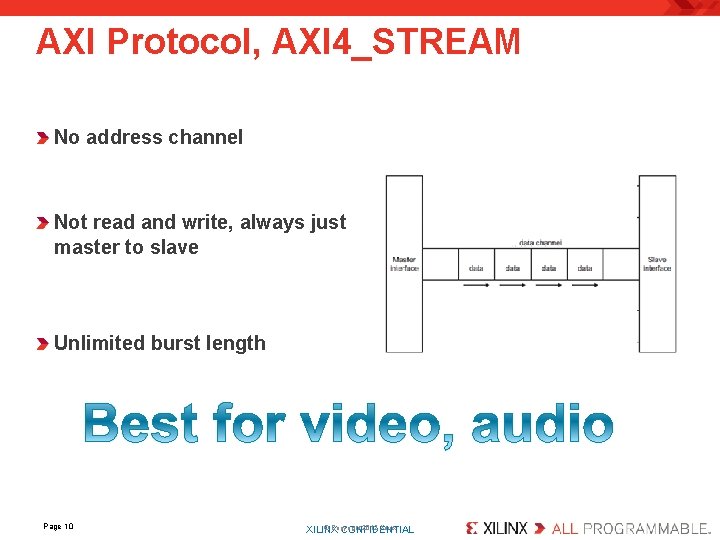

AXI Protocol, AXI 4_STREAM No address channel Not read and write, always just master to slave Unlimited burst length Page 10 © Copyright 2012 Xilinx XILINX CONFIDENTIAL.

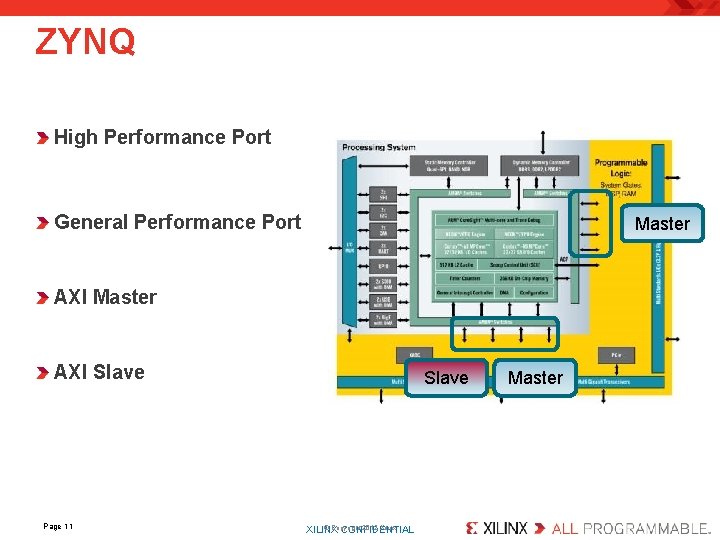

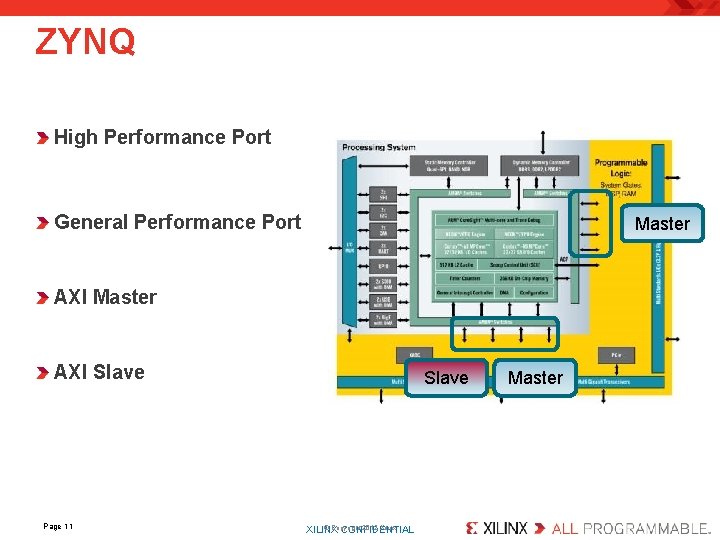

ZYNQ High Performance Port General Performance Port Master AXI Slave Page 11 Slave © Copyright 2012 Xilinx XILINX CONFIDENTIAL. Master

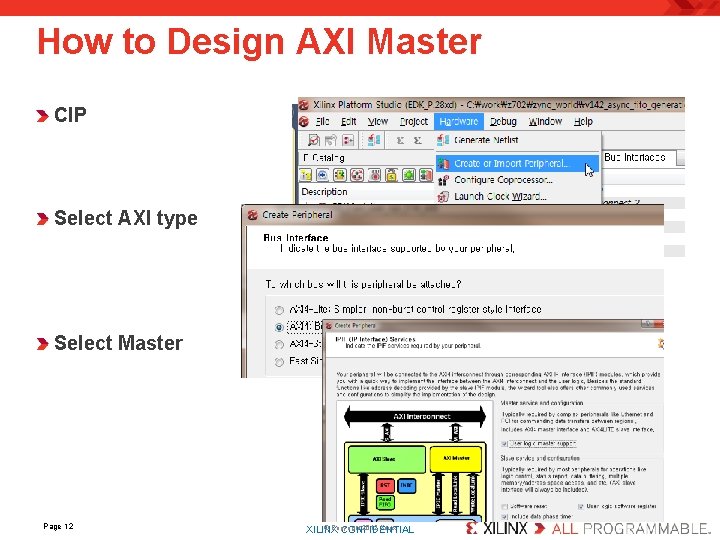

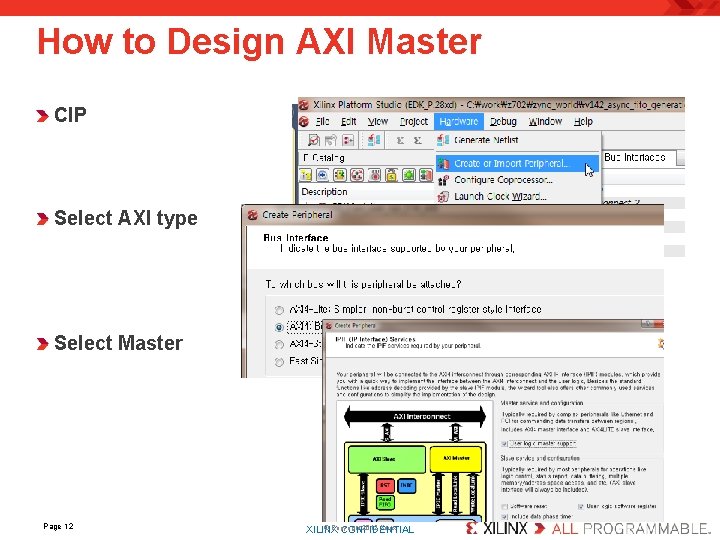

How to Design AXI Master CIP Select AXI type Select Master Page 12 © Copyright 2012 Xilinx XILINX CONFIDENTIAL.

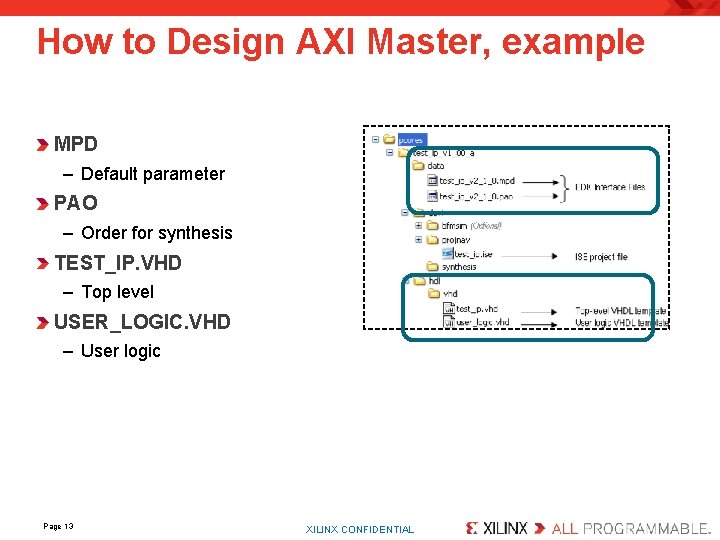

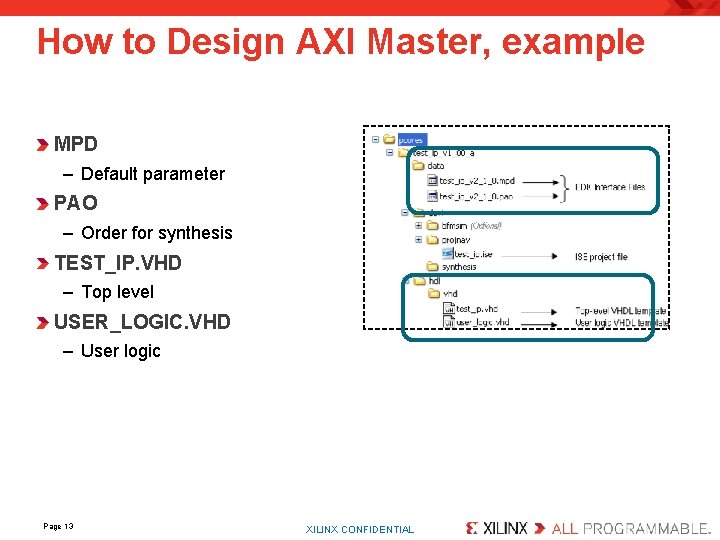

How to Design AXI Master, example MPD – Default parameter PAO – Order for synthesis TEST_IP. VHD – Top level USER_LOGIC. VHD – User logic Page 13 XILINX CONFIDENTIAL.

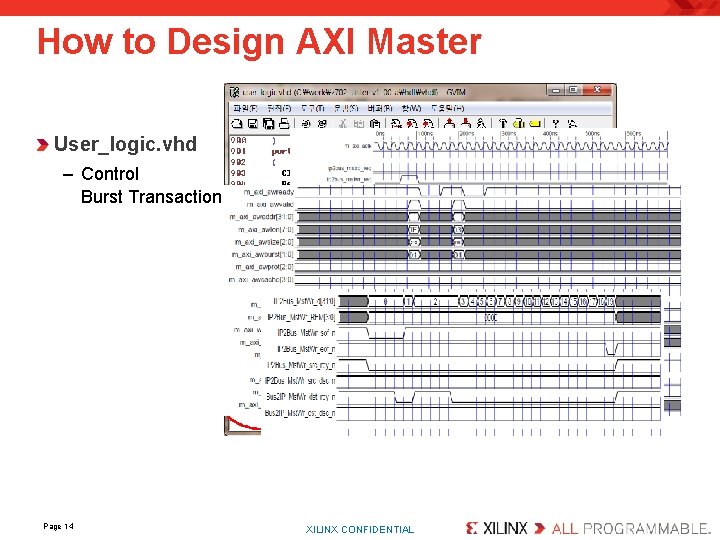

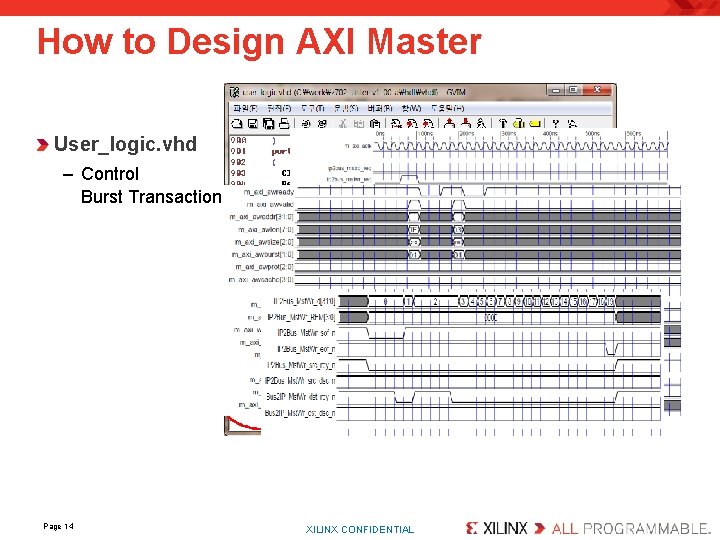

How to Design AXI Master User_logic. vhd – Control Burst Transaction Page 14 XILINX CONFIDENTIAL.

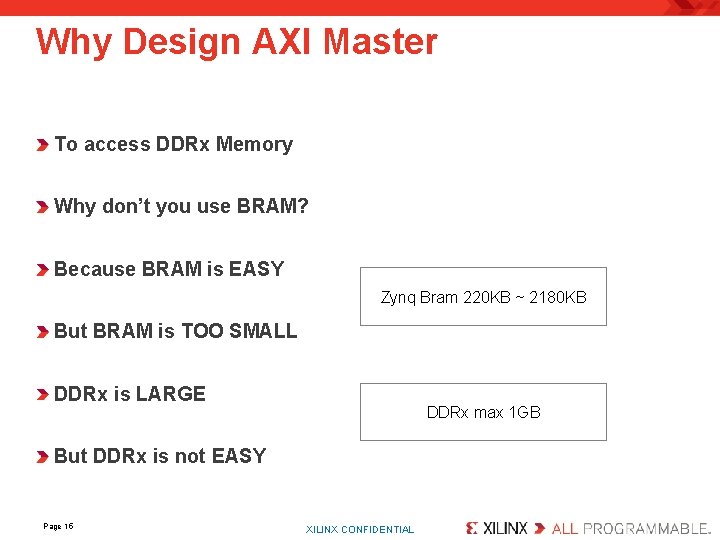

Why Design AXI Master To access DDRx Memory Why don’t you use BRAM? Because BRAM is EASY Zynq Bram 220 KB ~ 2180 KB But BRAM is TOO SMALL DDRx is LARGE DDRx max 1 GB But DDRx is not EASY Page 15 XILINX CONFIDENTIAL.

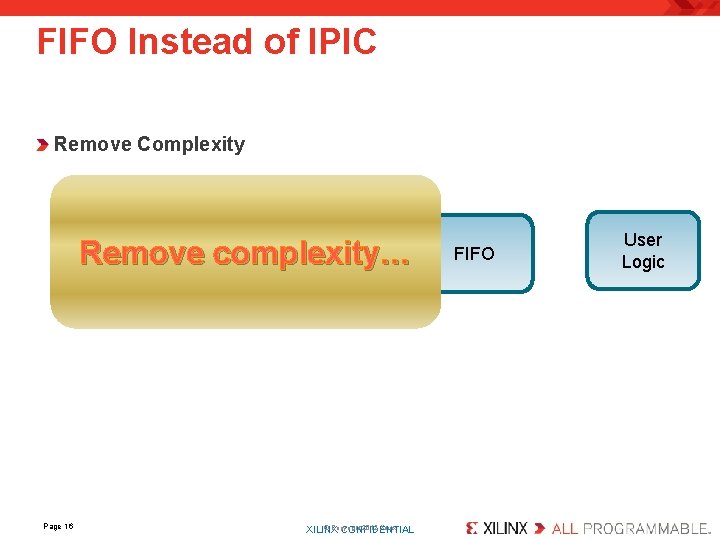

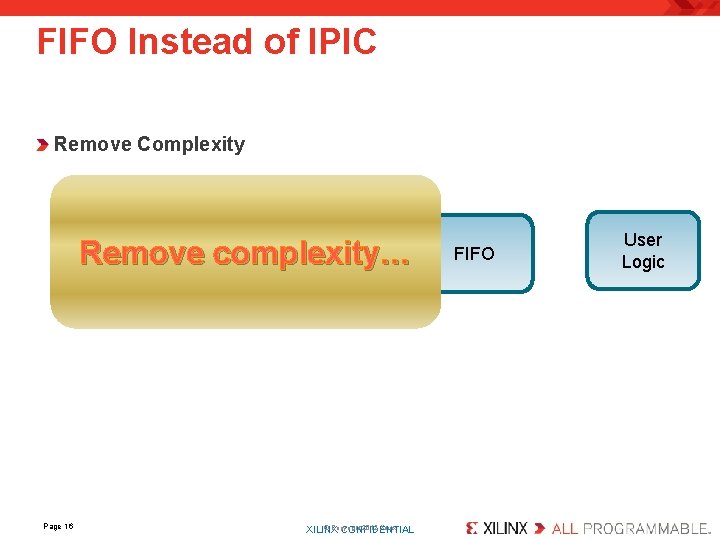

FIFO Instead of IPIC Remove Complexity IPIC & State Machine Remove complexity… DDRx Page 16 © Copyright 2012 Xilinx XILINX CONFIDENTIAL. FIFO User Logic

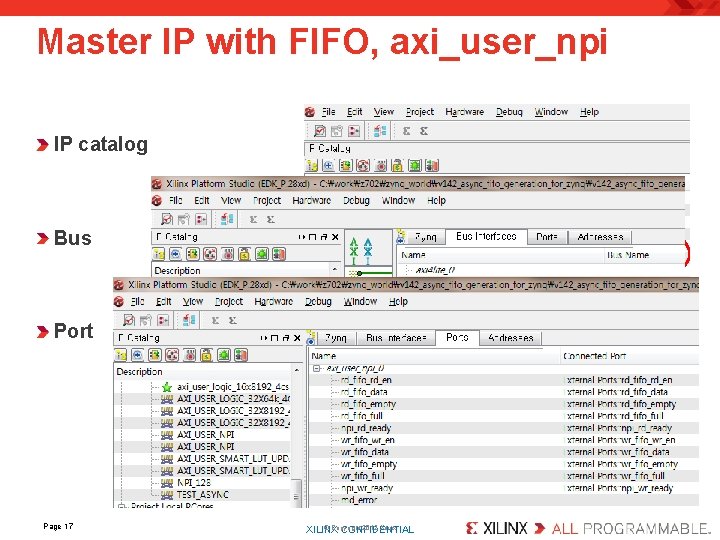

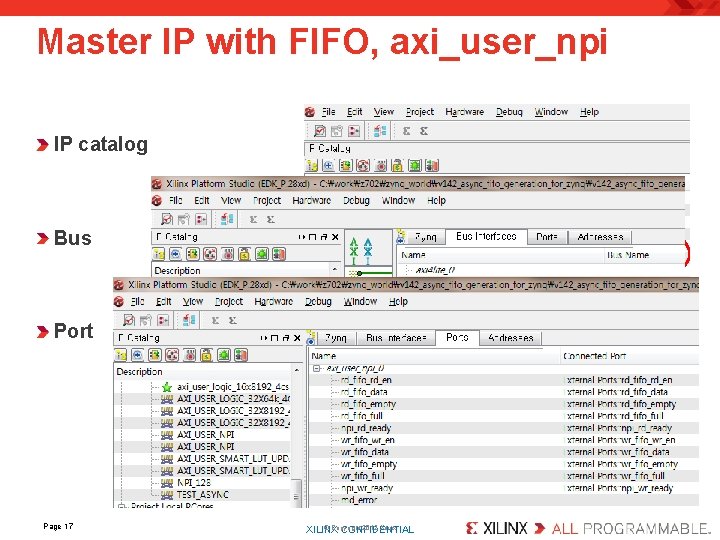

Master IP with FIFO, axi_user_npi IP catalog Bus Port Page 17 © Copyright 2012 Xilinx XILINX CONFIDENTIAL.

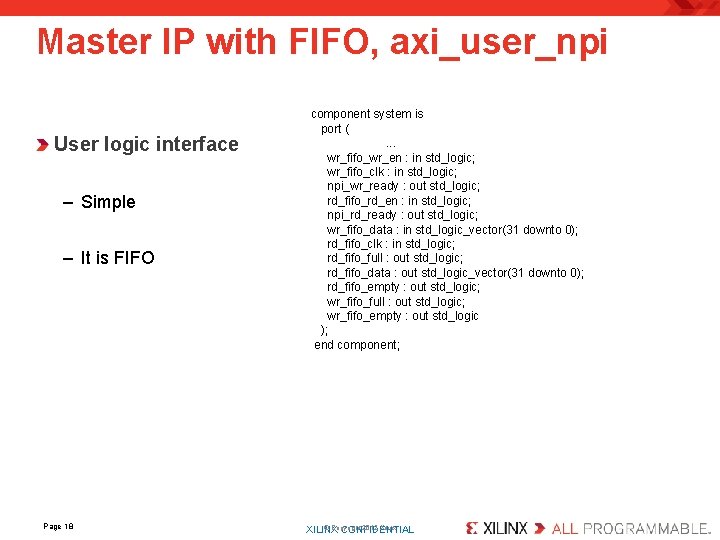

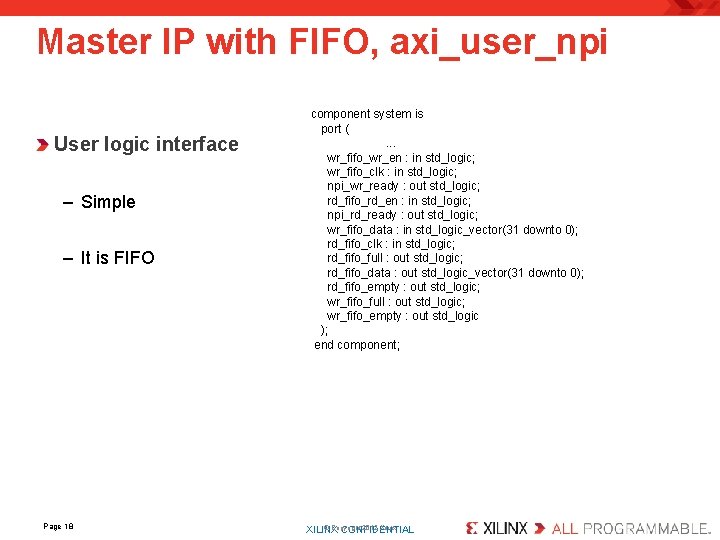

Master IP with FIFO, axi_user_npi User logic interface – Simple – It is FIFO Page 18 component system is port (. . . wr_fifo_wr_en : in std_logic; wr_fifo_clk : in std_logic; npi_wr_ready : out std_logic; rd_fifo_rd_en : in std_logic; npi_rd_ready : out std_logic; wr_fifo_data : in std_logic_vector(31 downto 0); rd_fifo_clk : in std_logic; rd_fifo_full : out std_logic; rd_fifo_data : out std_logic_vector(31 downto 0); rd_fifo_empty : out std_logic; wr_fifo_full : out std_logic; wr_fifo_empty : out std_logic ); end component; © Copyright 2012 Xilinx XILINX CONFIDENTIAL.

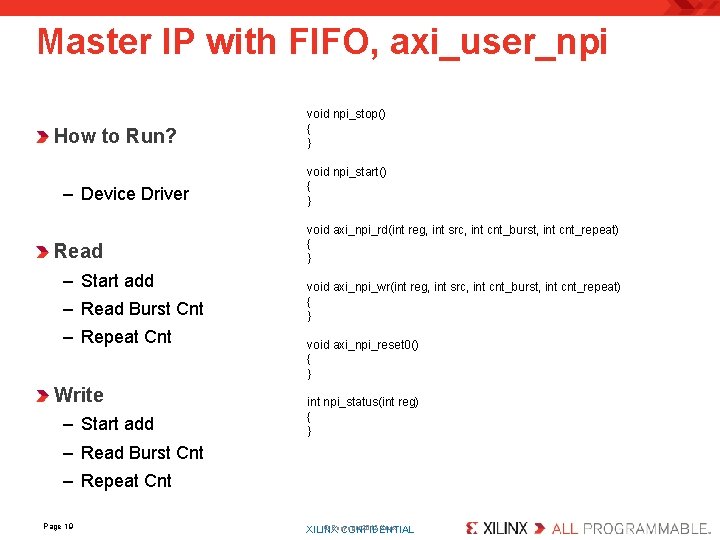

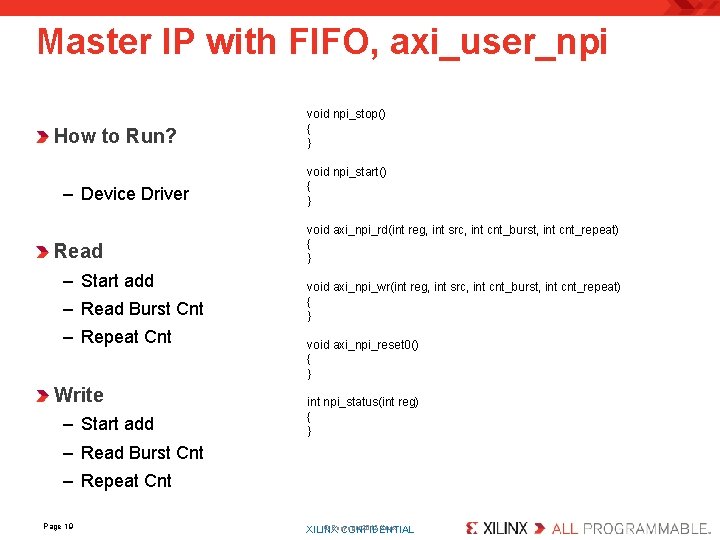

Master IP with FIFO, axi_user_npi How to Run? – Device Driver Read – Start add – Read Burst Cnt – Repeat Cnt Write – Start add void npi_stop() { } void npi_start() { } void axi_npi_rd(int reg, int src, int cnt_burst, int cnt_repeat) { } void axi_npi_wr(int reg, int src, int cnt_burst, int cnt_repeat) { } void axi_npi_reset 0() { } int npi_status(int reg) { } – Read Burst Cnt – Repeat Cnt Page 19 © Copyright 2012 Xilinx XILINX CONFIDENTIAL.

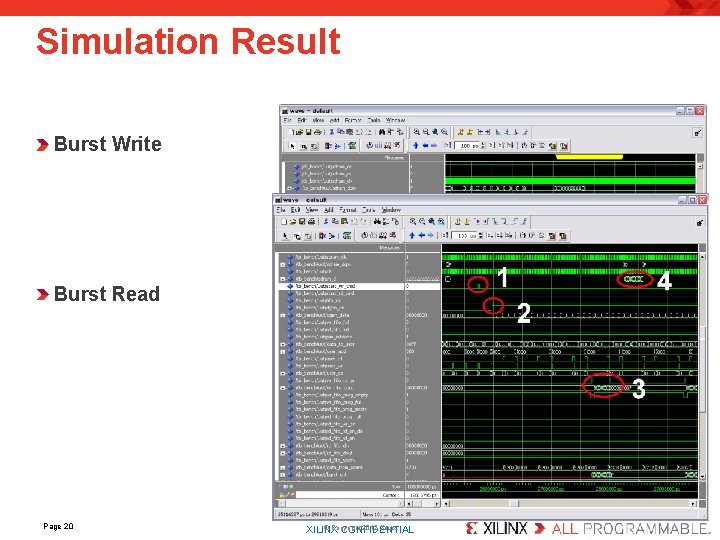

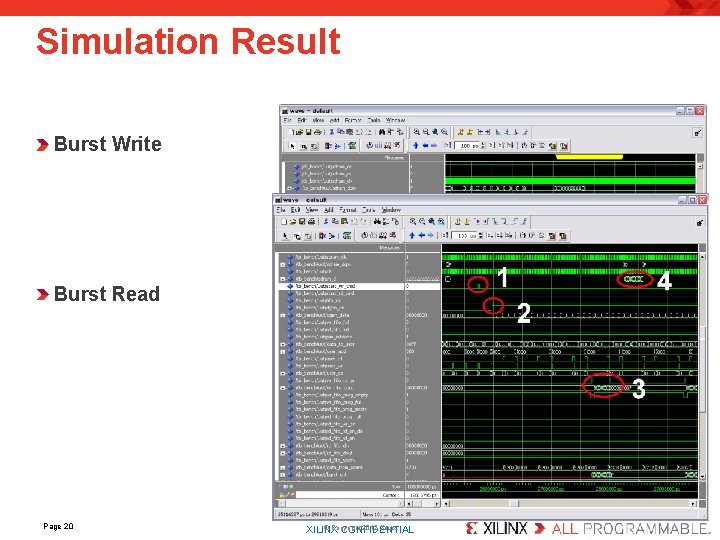

Simulation Result Burst Write Burst Read Page 20 © Copyright 2012 Xilinx XILINX CONFIDENTIAL.

Q&A Page 21 © Copyright 2012 Xilinx XILINX CONFIDENTIAL.