Design and Implementation of VLSI Systems EN 0160

- Slides: 14

Design and Implementation of VLSI Systems (EN 0160) Lecture 27: Datapath Subsystems 1/3 Prof. Sherief Reda Division of Engineering, Brown University Spring 2007 [sources: Weste/Addison Wesley – Rabaey/Pearson] S. Reda EN 160 SP’ 07

Project update • Phase I: Turn your standard cells to Mike today. Mike will iterate with you for the next couple of days and distribute the library file/report on Wednesday April 11. • Phase 2: Write precisely the interface (input/output) of your module in the CPU and write in plain english or pseudo-code what your module should do/output for different input combinations. Turn this in to Brian by Monday (April 16). Brian will verify everything and distribute the report on April 18. S. Reda EN 160 SP’ 07

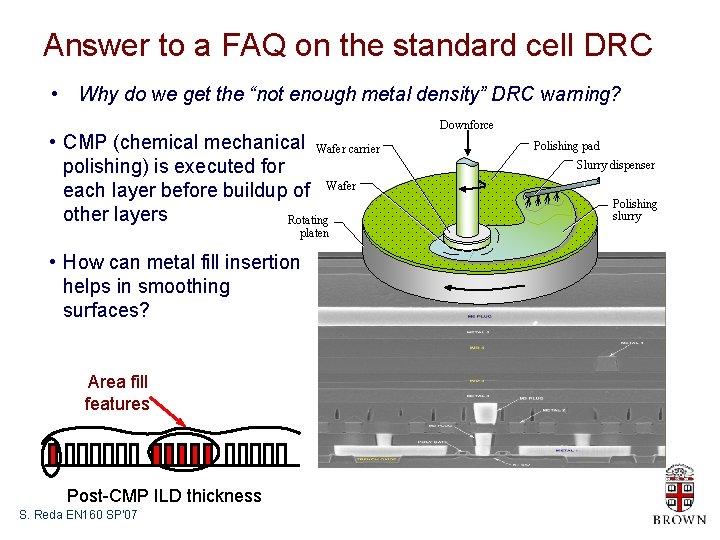

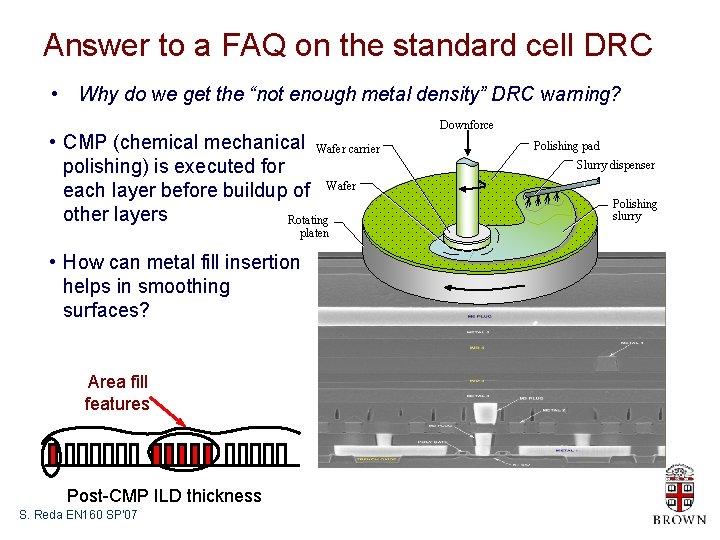

Answer to a FAQ on the standard cell DRC • Why do we get the “not enough metal density” DRC warning? • CMP (chemical mechanical Wafer carrier polishing) is executed for each layer before buildup of Wafer other layers Rotating platen • How can metal fill insertion helps in smoothing surfaces? Area fill features Post-CMP ILD thickness S. Reda EN 160 SP’ 07 Downforce Polishing pad Slurry dispenser Polishing slurry

Adders • Addition is the most commonly used arithmetic operation • It is often the speed limiting element • Careful optimization of the adder is of the utmost importance • Optimization can be carried out at the circuit or logic level S. Reda EN 160 SP’ 07

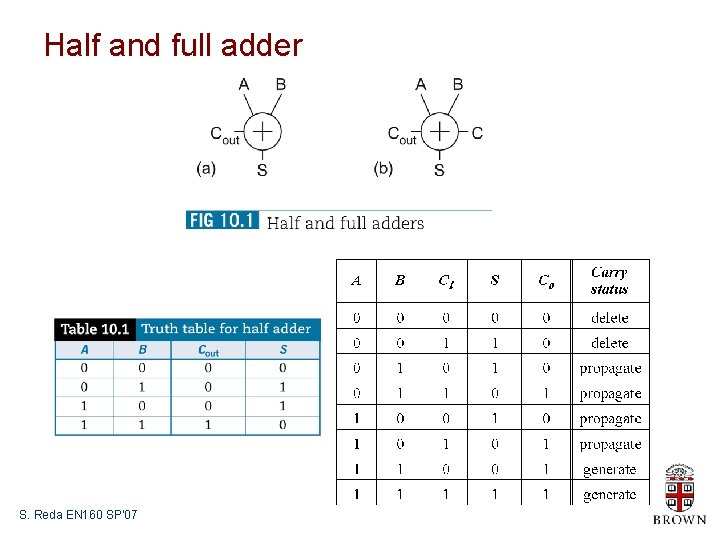

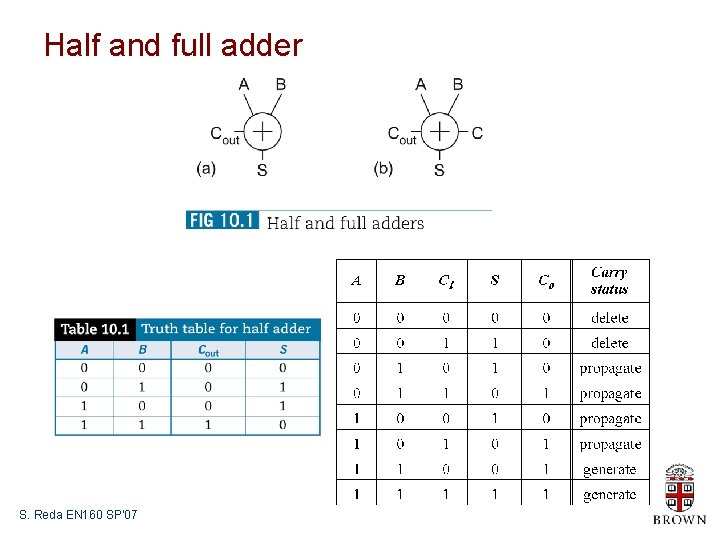

Half and full adder S. Reda EN 160 SP’ 07

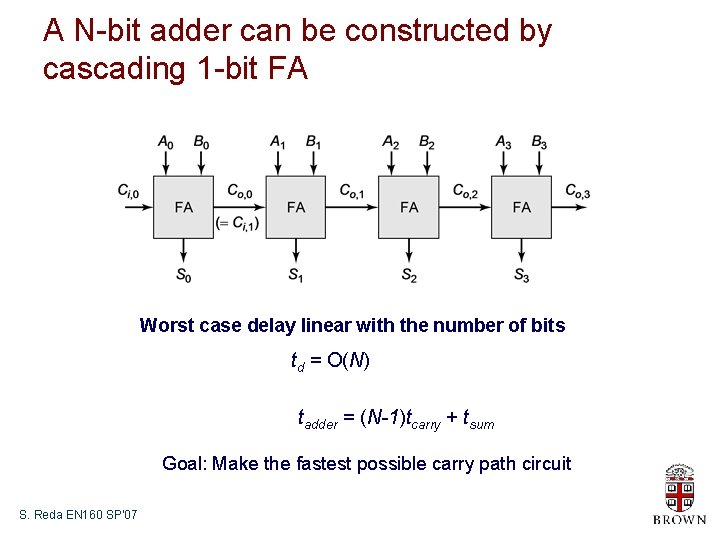

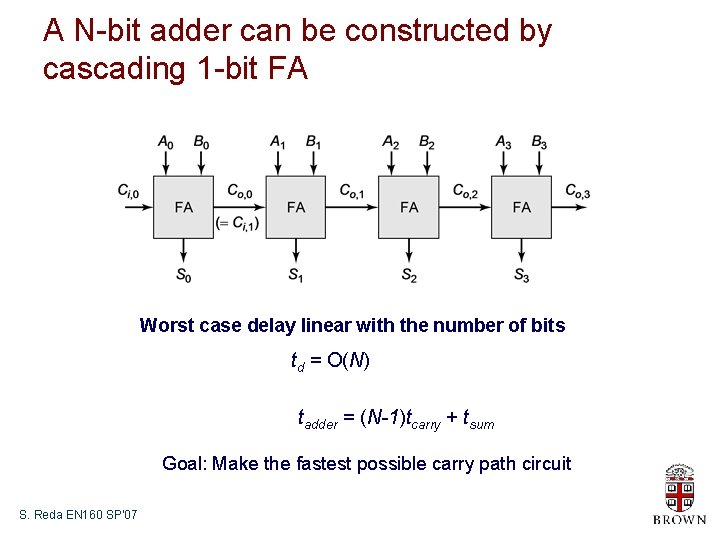

A N-bit adder can be constructed by cascading 1 -bit FA Worst case delay linear with the number of bits td = O(N) tadder = (N-1)tcarry + tsum Goal: Make the fastest possible carry path circuit S. Reda EN 160 SP’ 07

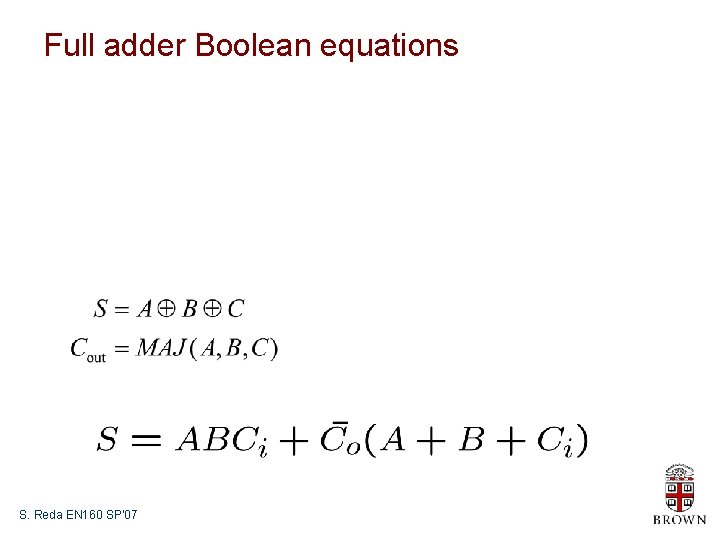

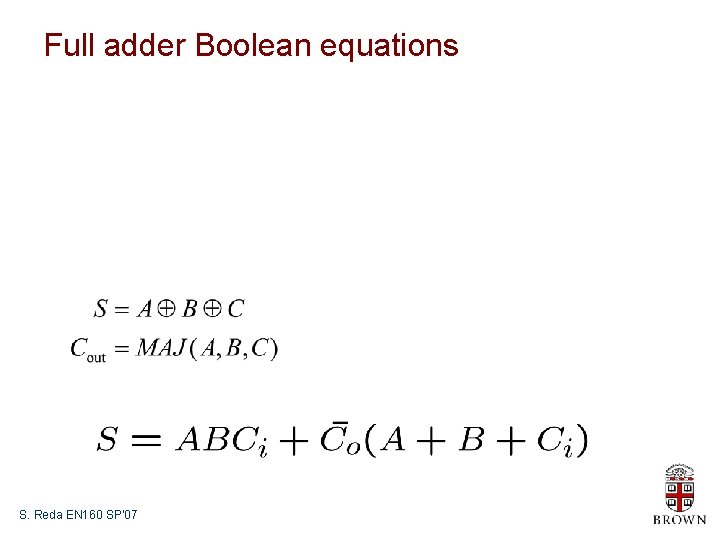

Full adder Boolean equations S. Reda EN 160 SP’ 07

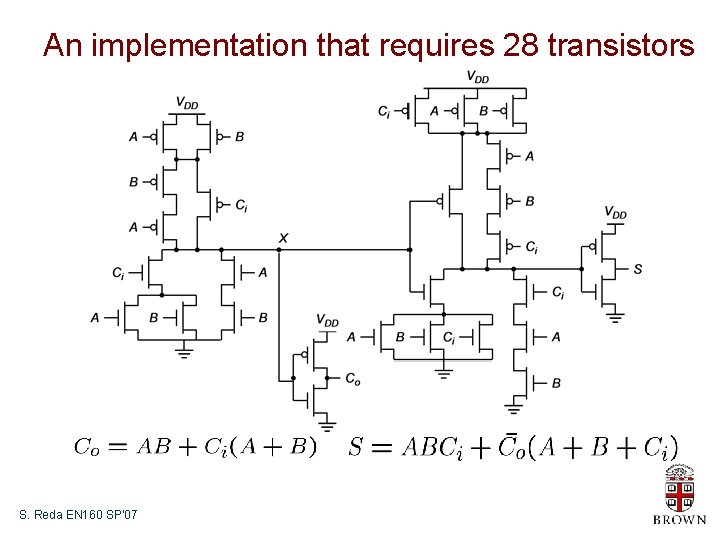

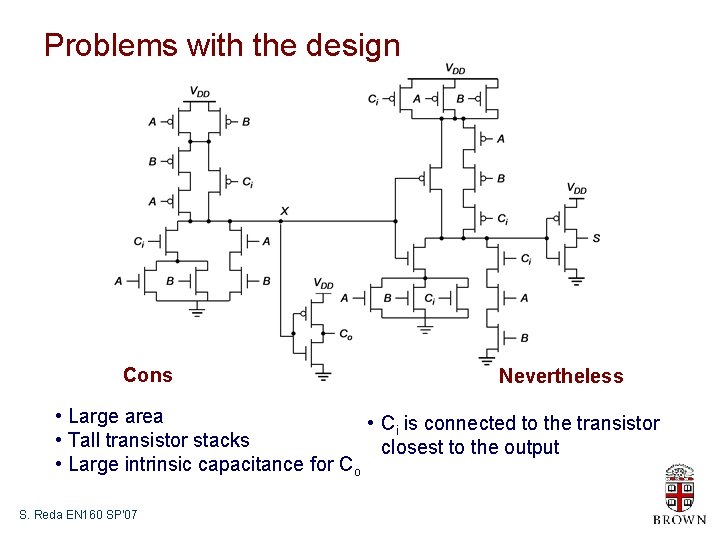

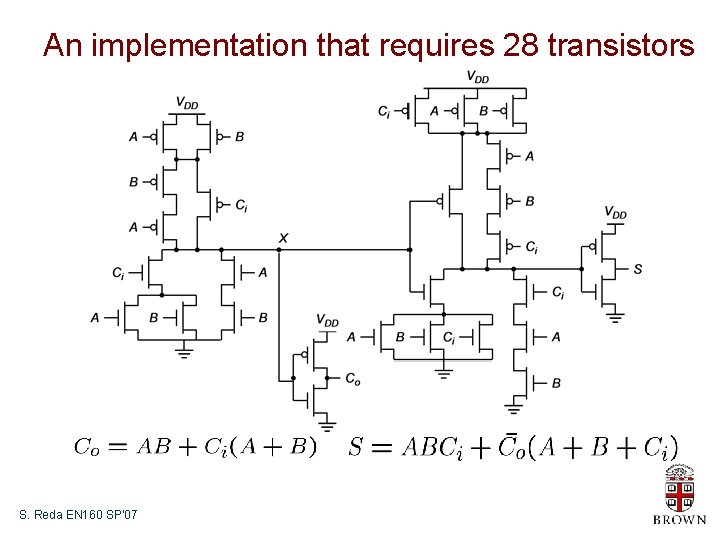

An implementation that requires 28 transistors S. Reda EN 160 SP’ 07

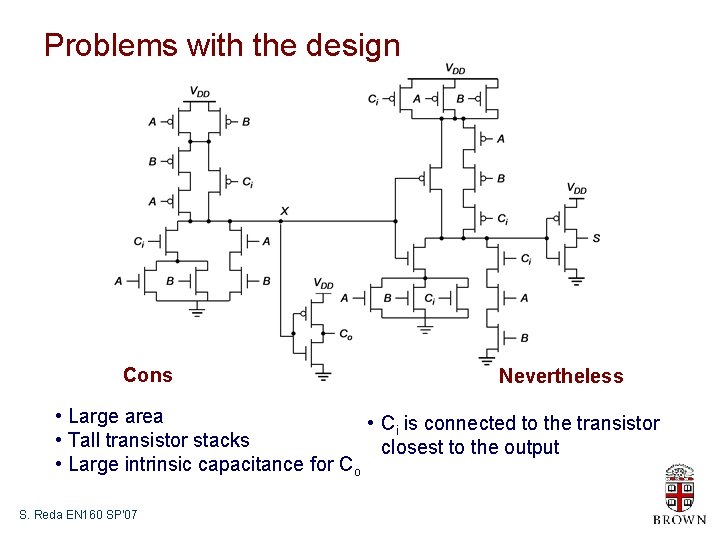

Problems with the design Cons Nevertheless • Large area • Ci is connected to the transistor • Tall transistor stacks closest to the output • Large intrinsic capacitance for Co S. Reda EN 160 SP’ 07

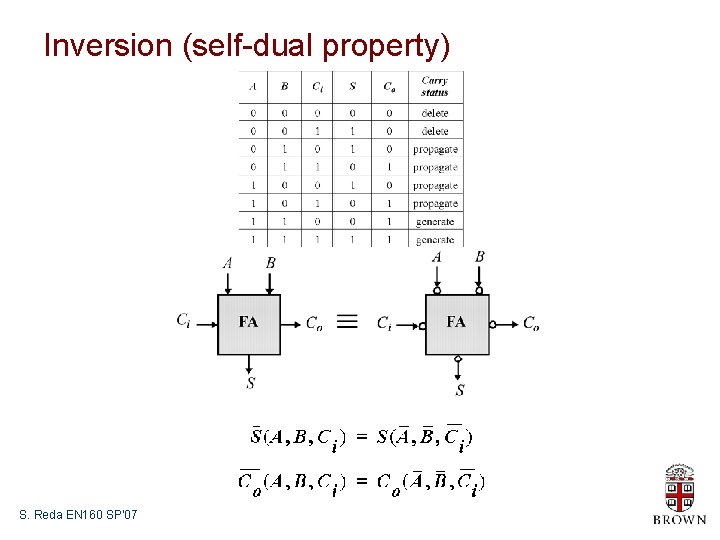

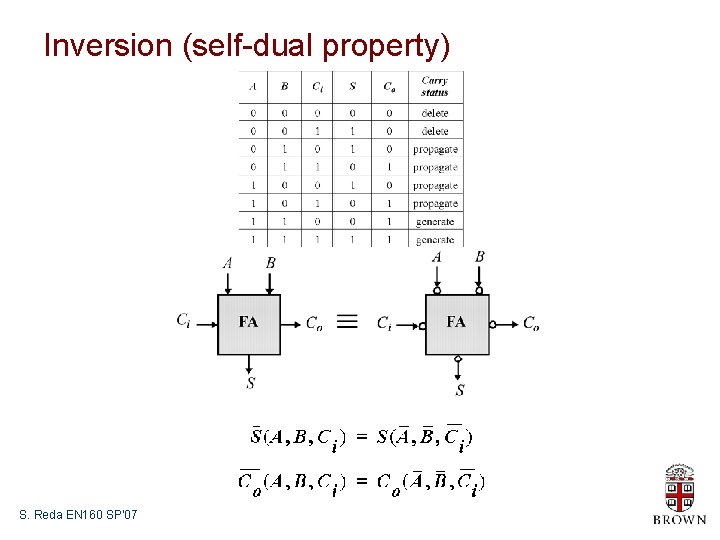

Inversion (self-dual property) S. Reda EN 160 SP’ 07

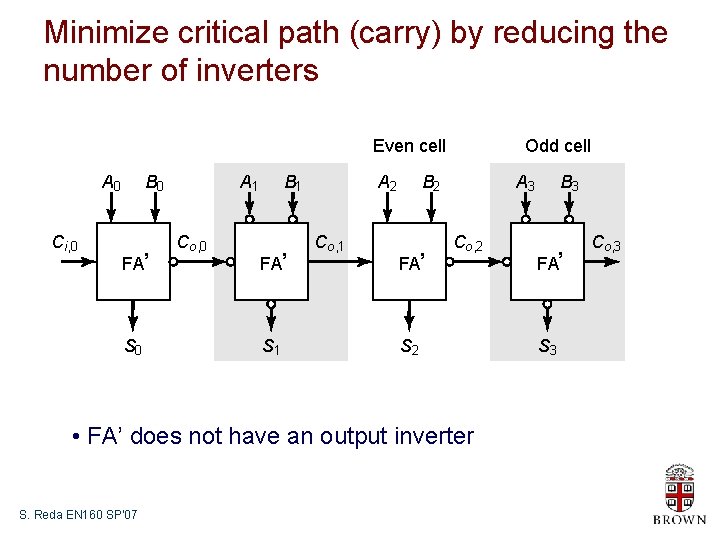

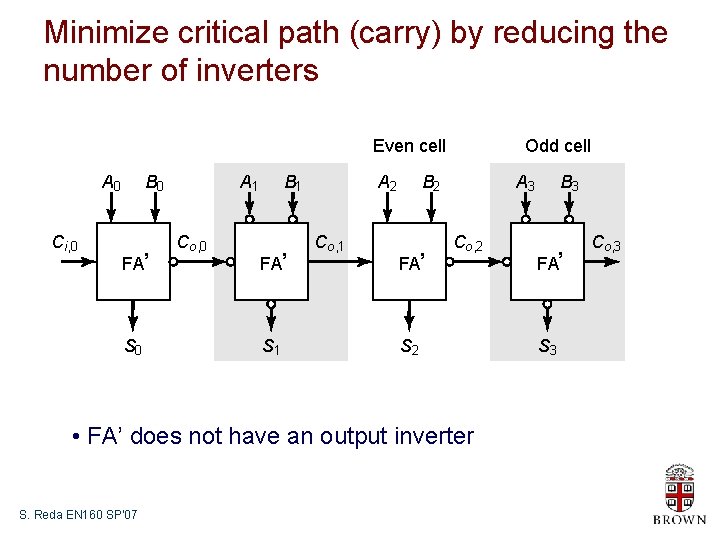

Minimize critical path (carry) by reducing the number of inverters Even cell A 0 Ci, 0 B 0 , FA S 0 A 1 Co, 0 B 1 , FA S 1 A 2 Co, 1 Odd cell B 2 , FA A 3 Co, 2 S 2 • FA’ does not have an output inverter S. Reda EN 160 SP’ 07 B 3 , FA S 3 Co, 3

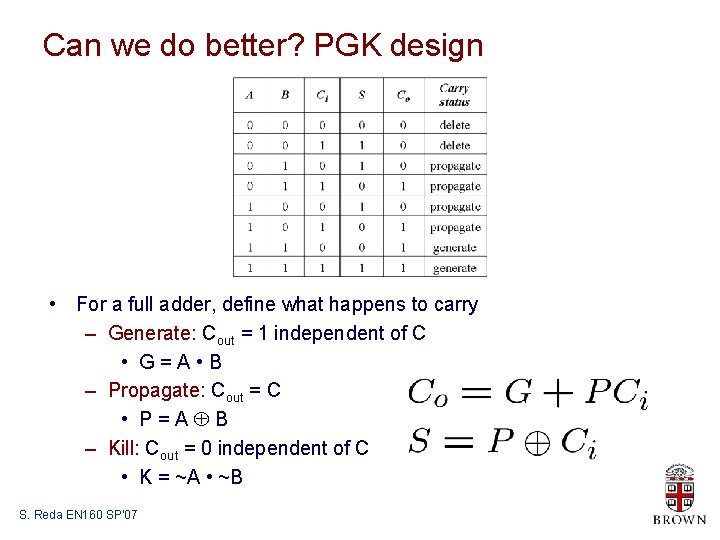

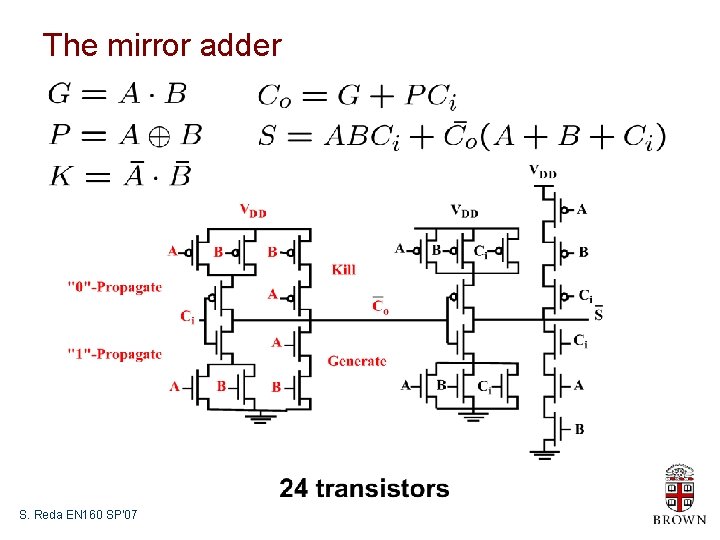

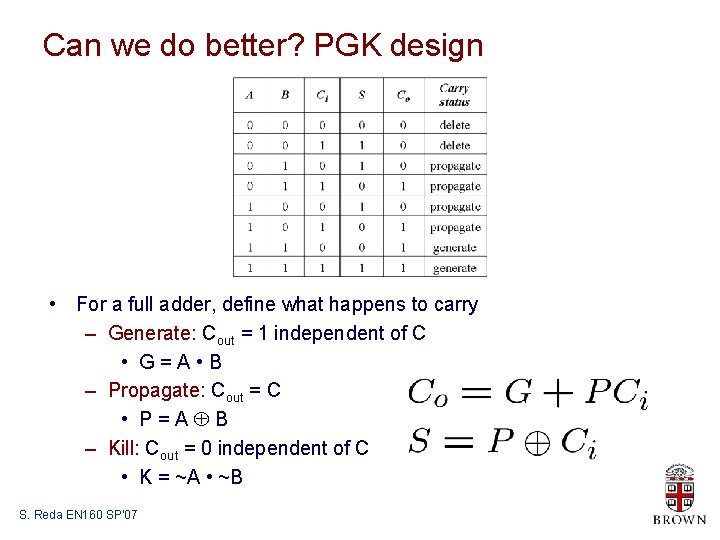

Can we do better? PGK design • For a full adder, define what happens to carry – Generate: Cout = 1 independent of C • G=A • B – Propagate: Cout = C • P=A B – Kill: Cout = 0 independent of C • K = ~A • ~B S. Reda EN 160 SP’ 07

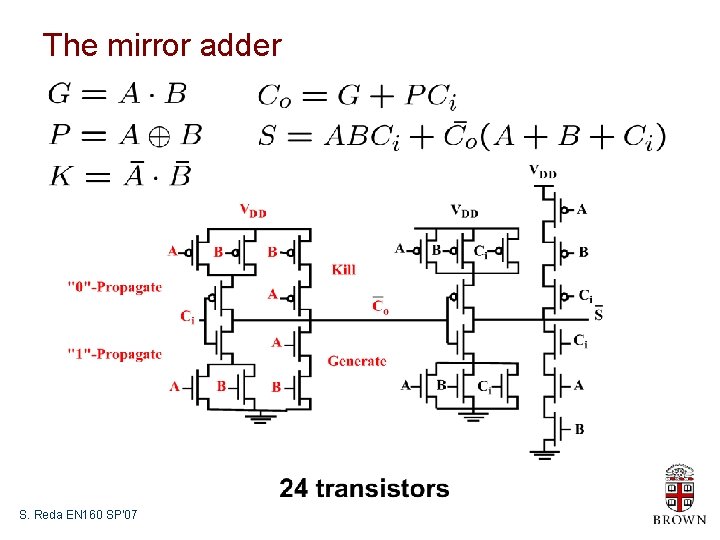

The mirror adder S. Reda EN 160 SP’ 07

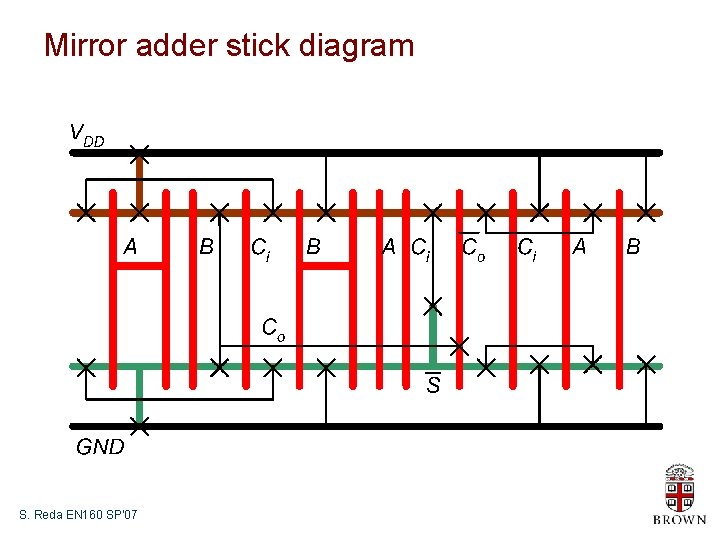

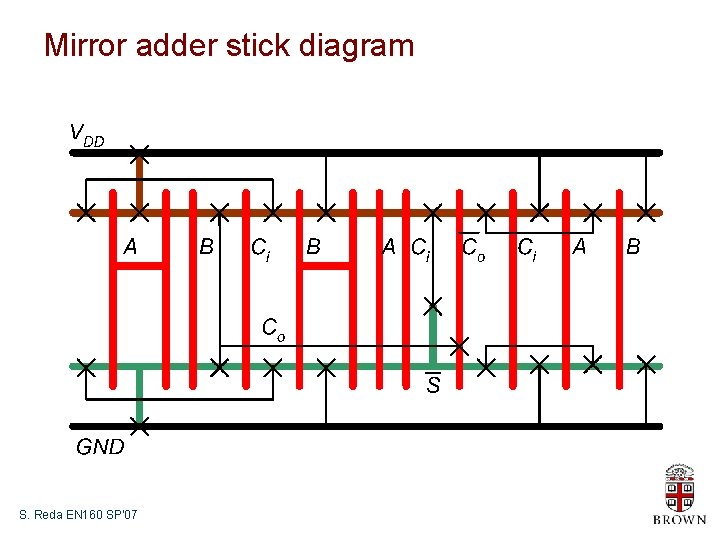

Mirror adder stick diagram S. Reda EN 160 SP’ 07