Design and implementation of a motion coprocessor for

- Slides: 29

Design and implementation of a motion coprocessor for the MERITE beacon D. Faura, O. Romain, K. Hachicha and P. Garda SYEL group Laboratoire des Instruments et Systèmes d’Ile de France, LISIF Université Pierre et Marie Curie FRANCE

Out line 1. 2. 3. 4. 5. 6. Introduction The goal Architecture of the beacon Implementation Experimental Results Conclusion

1. Introduction n Recent progress in the fields of : ¨ Processing n Electronic implementation ¨ So. C, SIP, … ¨ Wireless n architecture telecommunication Bluetooth, Wifi, Home RF, … ¨ Ad Hoc networks Design of new generation of autonomous Systems

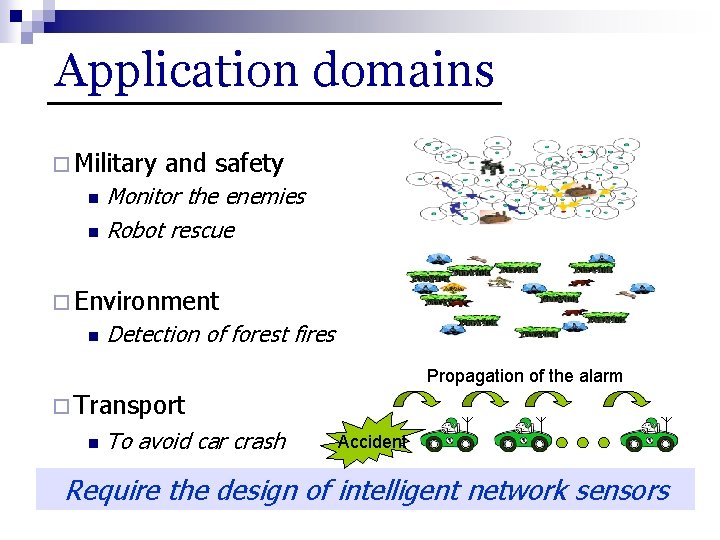

Application domains ¨ Military and safety Monitor the enemies n Robot rescue n ¨ Environment n Detection of forest fires Propagation of the alarm ¨ Transport n To avoid car crash Accident Require the design of intelligent network sensors

2. Goal n To propose and model a new architecture of an intelligent wireless beacon for sensor networks applications To detect and transmit an alarm ¨ To distinguish between a false and a true alarm ¨ n To design an electronic implementation ¨ n To test and verify the behaviour of the beacon in a real conditions To integrate ¨ To make an AMS System-On-Chip (RFVSo. C Project)

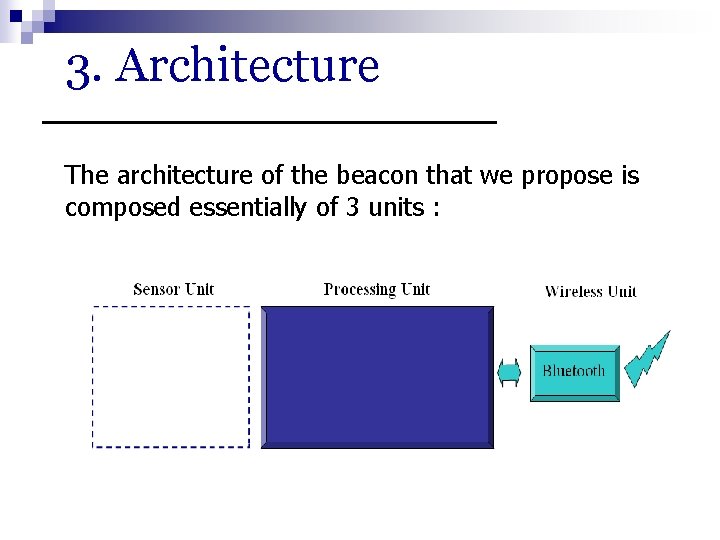

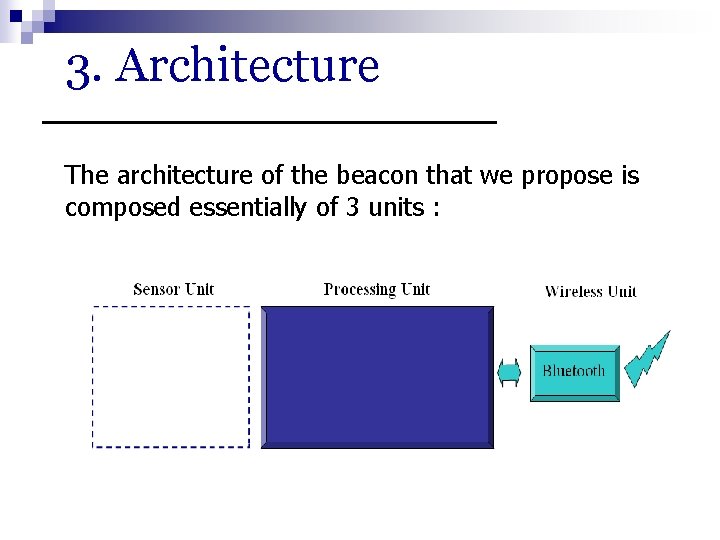

3. Architecture The architecture of the beacon that we propose is composed essentially of 3 units :

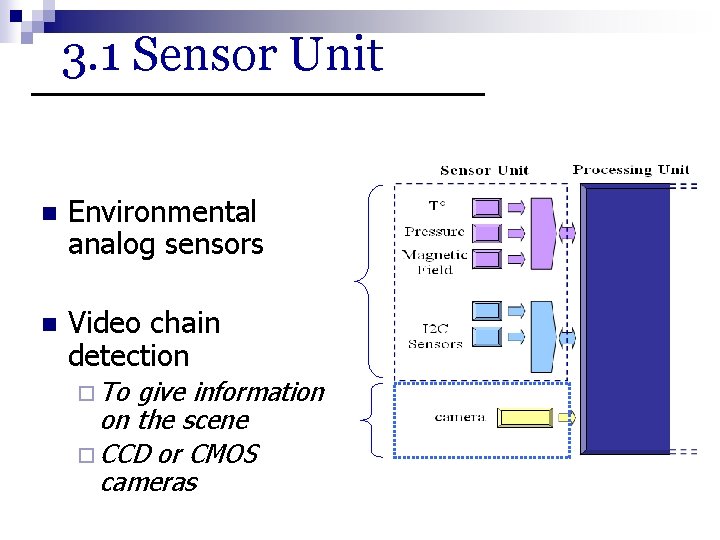

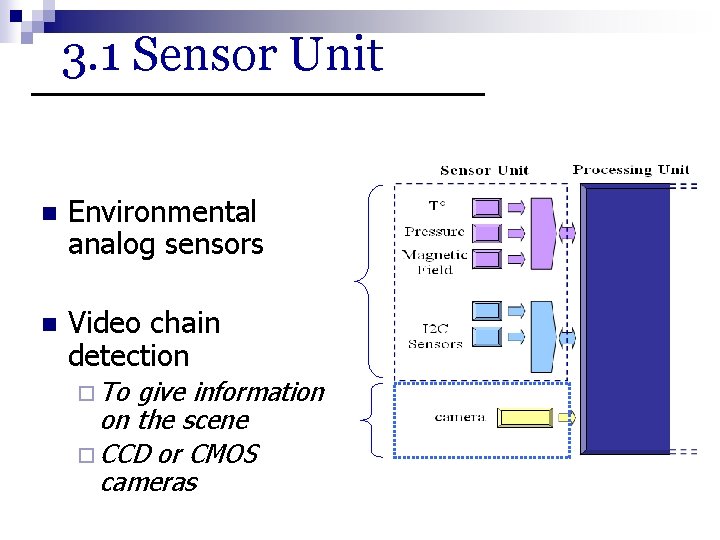

3. 1 Sensor Unit n Environmental analog sensors n Video chain detection ¨ To give information on the scene ¨ CCD or CMOS cameras

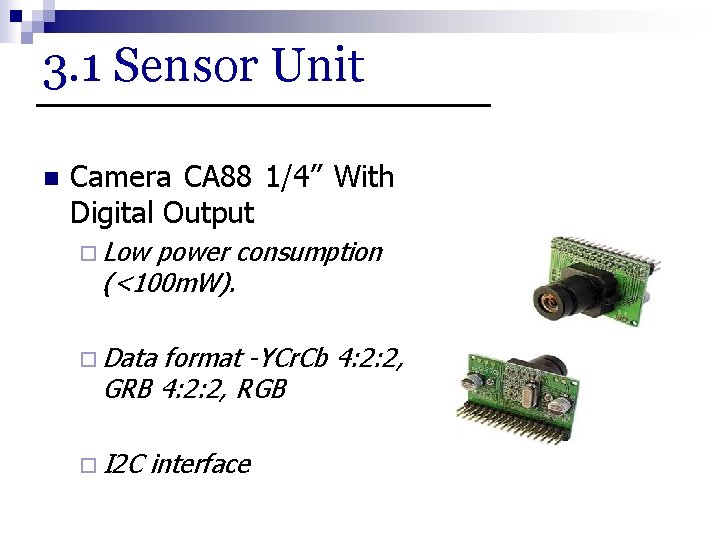

3. 1 Sensor Unit n Camera CA 88 1/4” With Digital Output ¨ Low power consumption (<100 m. W). ¨ Data format -YCr. Cb 4: 2: 2, GRB 4: 2: 2, RGB ¨ I 2 C interface

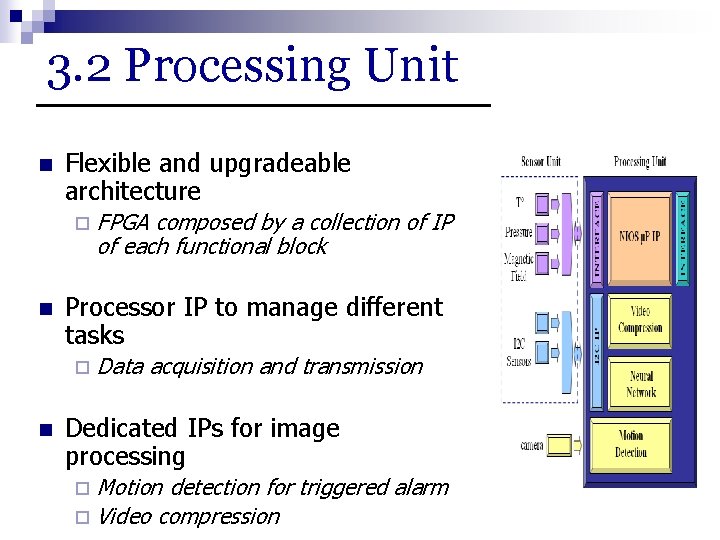

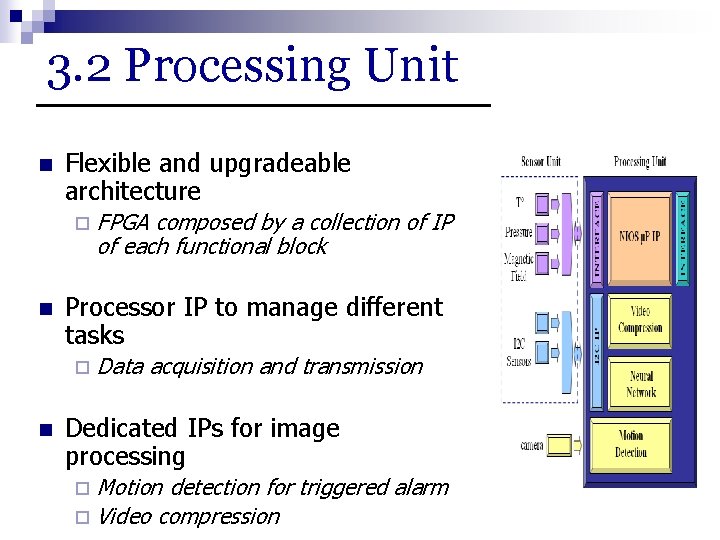

3. 2 Processing Unit n Flexible and upgradeable architecture ¨ n Processor IP to manage different tasks ¨ n FPGA composed by a collection of IP of each functional block Data acquisition and transmission Dedicated IPs for image processing Motion detection for triggered alarm ¨ Video compression ¨

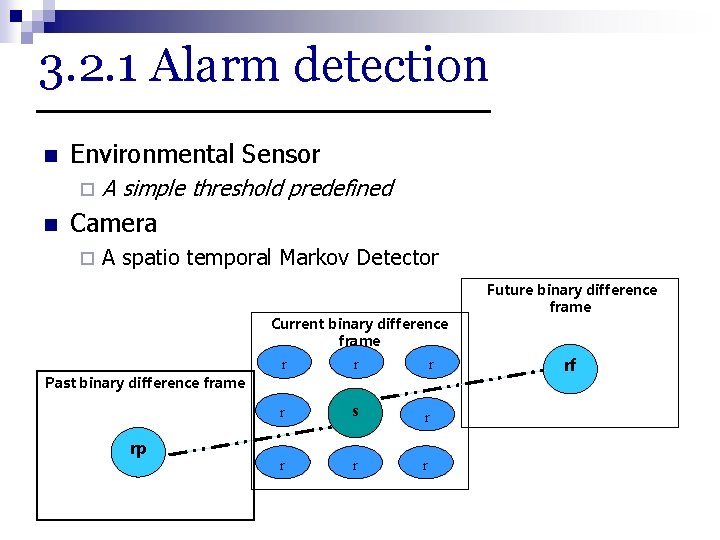

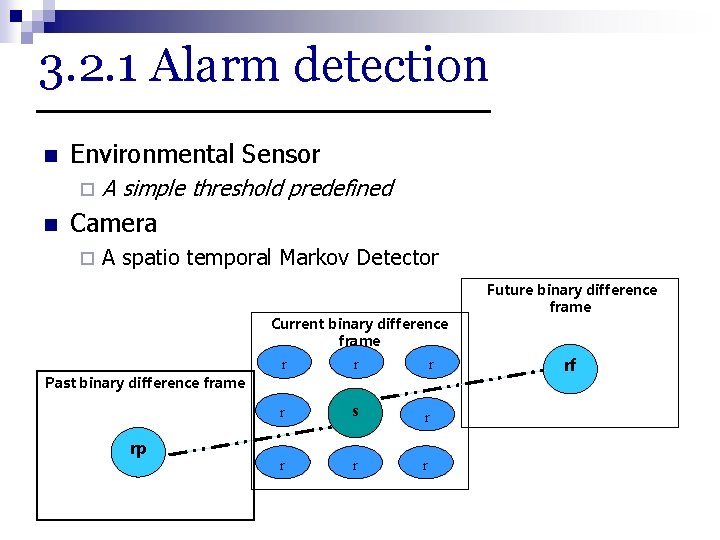

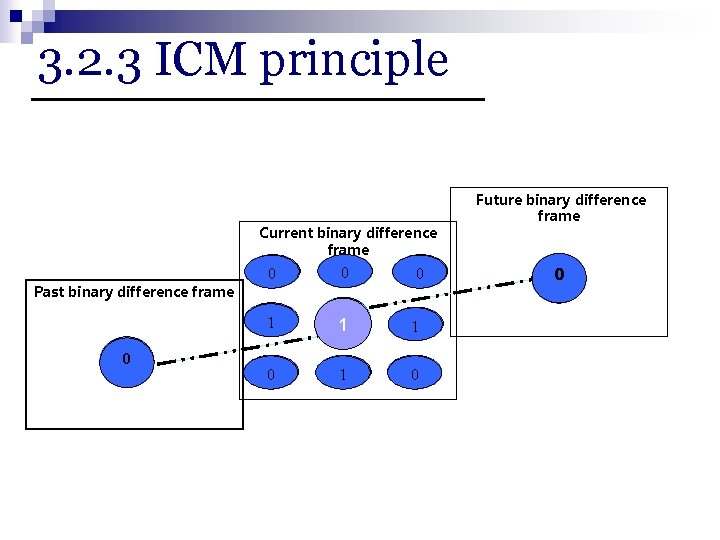

3. 2. 1 Alarm detection n Environmental Sensor ¨ n A simple threshold predefined Camera ¨ A spatio temporal Markov Detector Current binary difference frame r r s r r Past binary difference frame rp Future binary difference frame rf

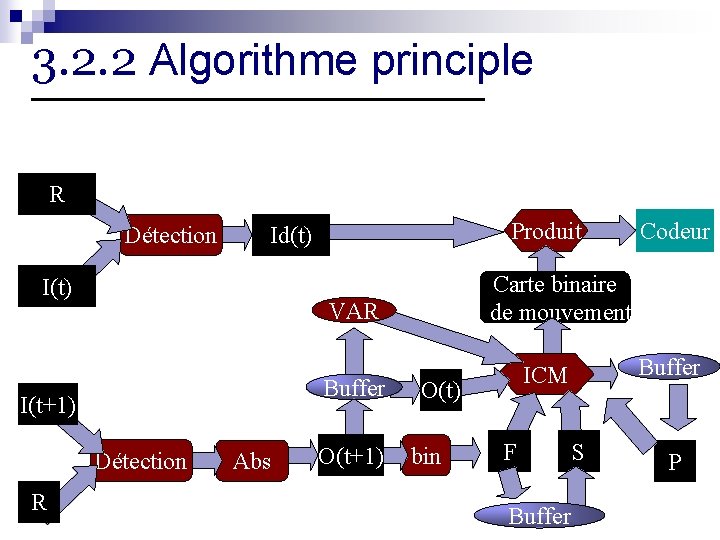

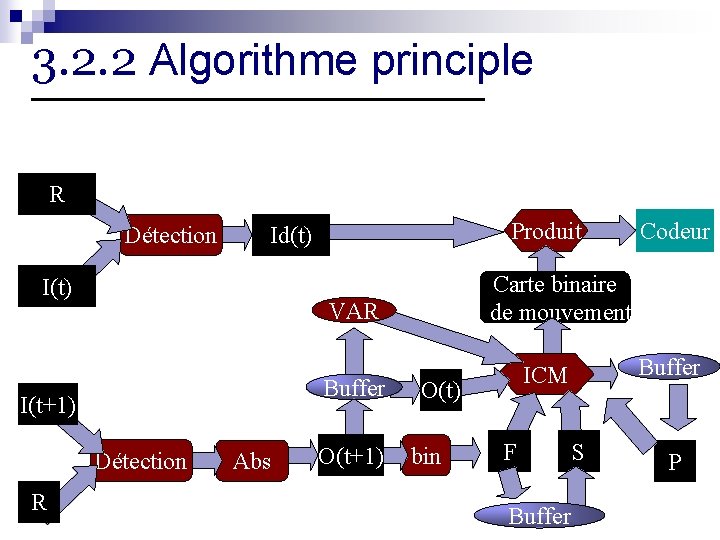

3. 2. 2 Algorithme principle R Détection I(t) Buffer Détection Abs O(t+1) Codeur Carte binaire de mouvement VAR I(t+1) R Produit Id(t) O(t) bin Buffer ICM F Buffer S P

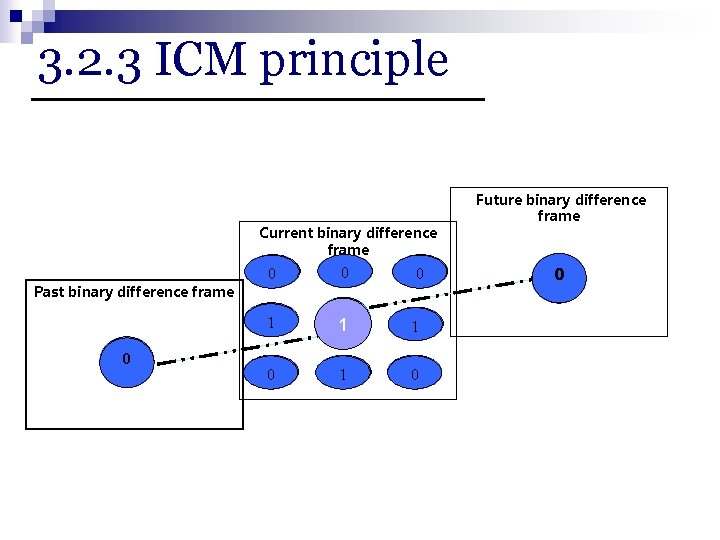

3. 2. 3 ICM principle Current binary difference frame Past binary difference frame rp 0 0 r 0 r 0 r 1 r 0 s 1 1 r 0 r Future binary difference frame 0 rf

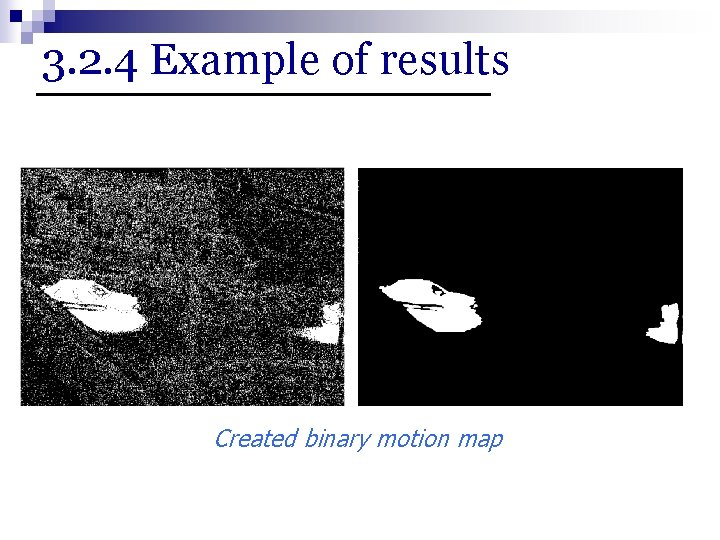

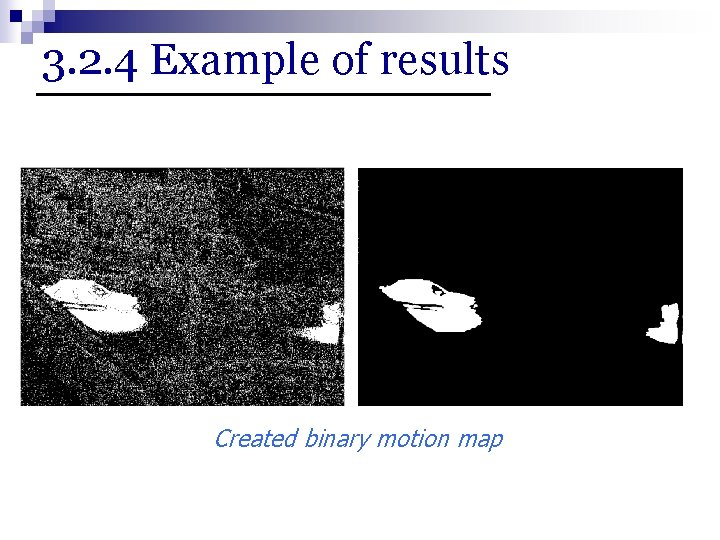

3. 2. 4 Example of results Created binary motion map

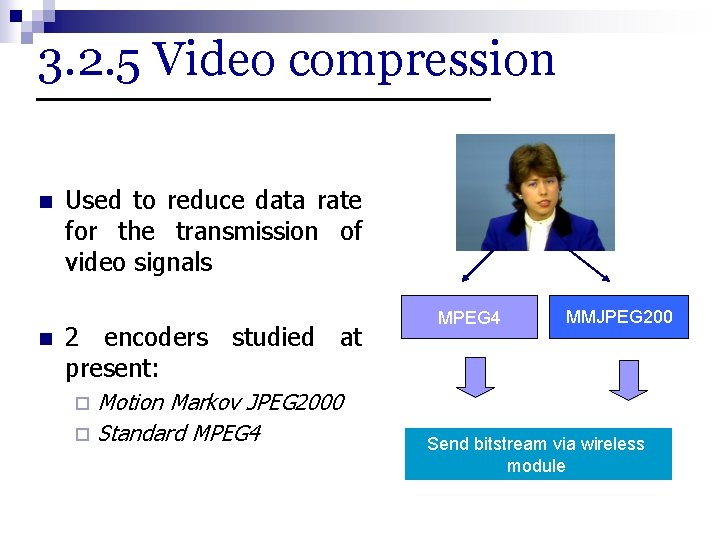

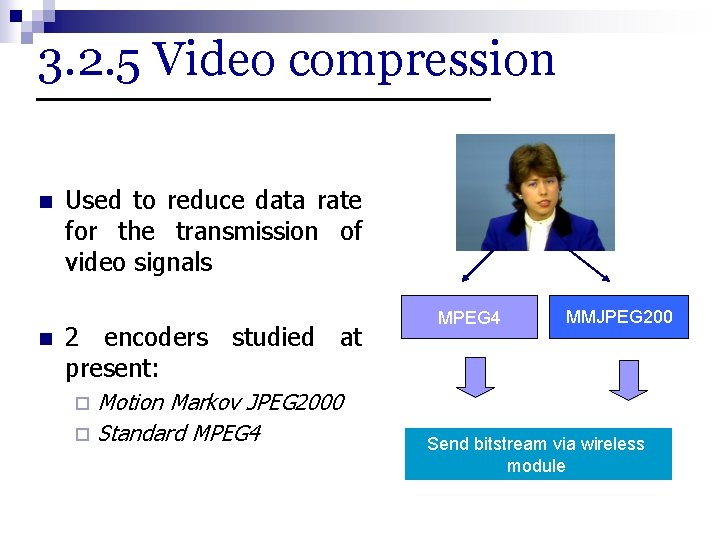

3. 2. 5 Video compression n n Used to reduce data rate for the transmission of video signals 2 encoders studied at present: Motion Markov JPEG 2000 ¨ Standard MPEG 4 MMJPEG 200 ¨ Send bitstream via wireless module

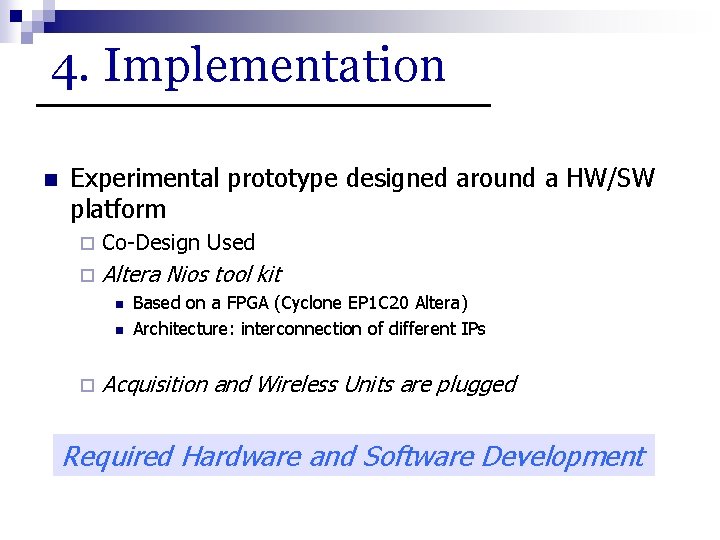

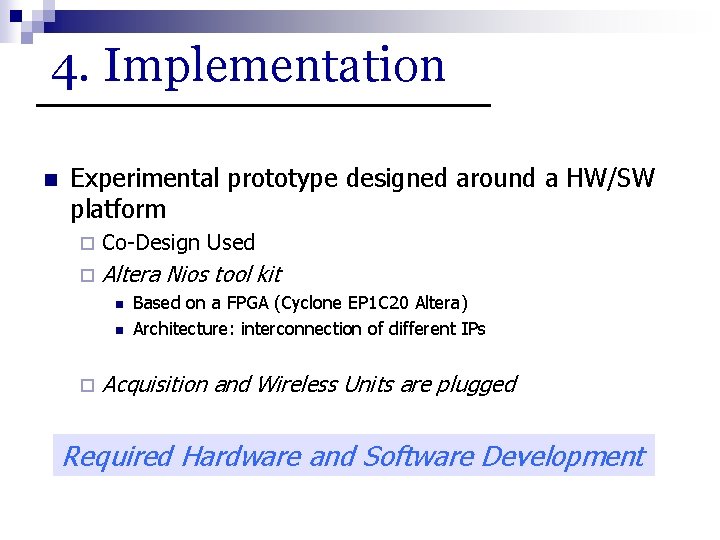

4. Implementation n Experimental prototype designed around a HW/SW platform ¨ Co-Design Used ¨ Altera Nios tool kit n n ¨ Based on a FPGA (Cyclone EP 1 C 20 Altera) Architecture: interconnection of different IPs Acquisition and Wireless Units are plugged Required Hardware and Software Development

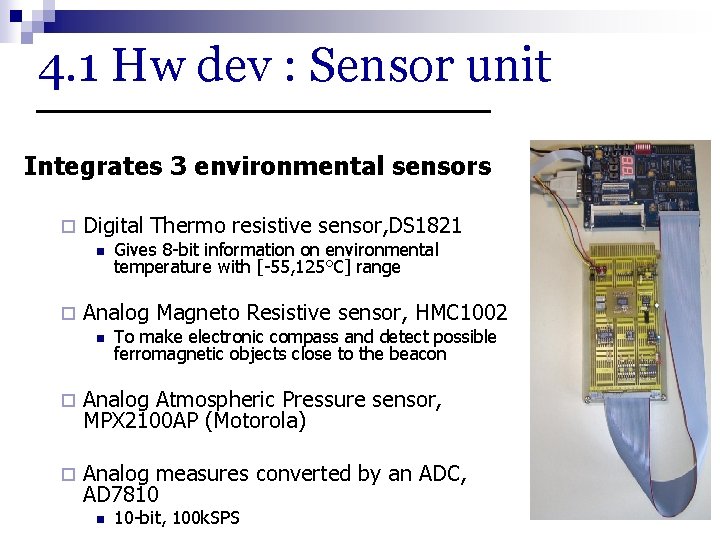

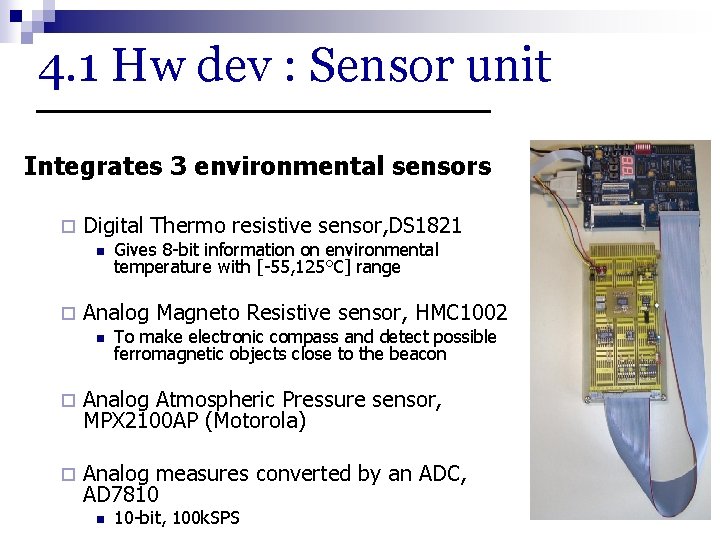

4. 1 Hw dev : Sensor unit Integrates 3 environmental sensors ¨ Digital Thermo resistive sensor, DS 1821 n ¨ Gives 8 -bit information on environmental temperature with [-55, 125°C] range Analog Magneto Resistive sensor, HMC 1002 n To make electronic compass and detect possible ferromagnetic objects close to the beacon ¨ Analog Atmospheric Pressure sensor, MPX 2100 AP (Motorola) ¨ Analog measures converted by an ADC, AD 7810 n 10 -bit, 100 k. SPS

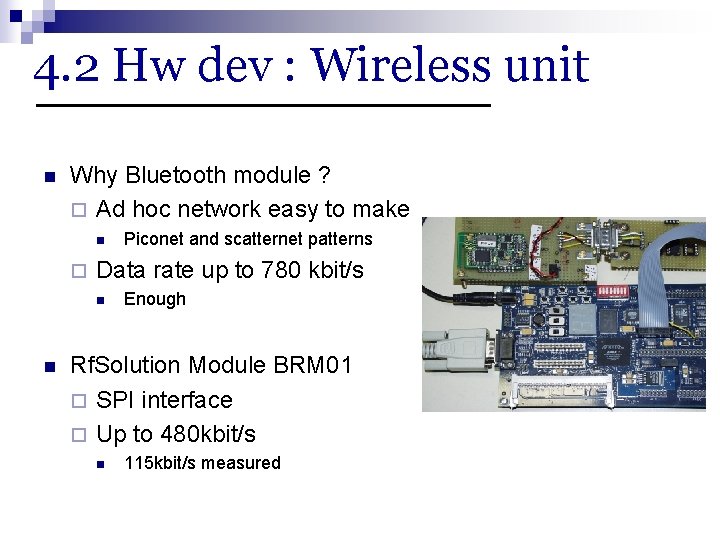

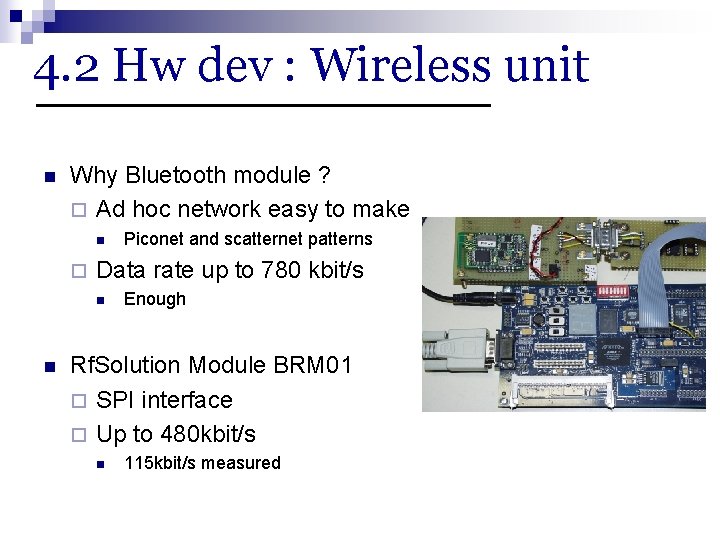

4. 2 Hw dev : Wireless unit n Why Bluetooth module ? ¨ Ad hoc network easy to make n ¨ Data rate up to 780 kbit/s n n Piconet and scatternet patterns Enough Rf. Solution Module BRM 01 ¨ SPI interface ¨ Up to 480 kbit/s n 115 kbit/s measured

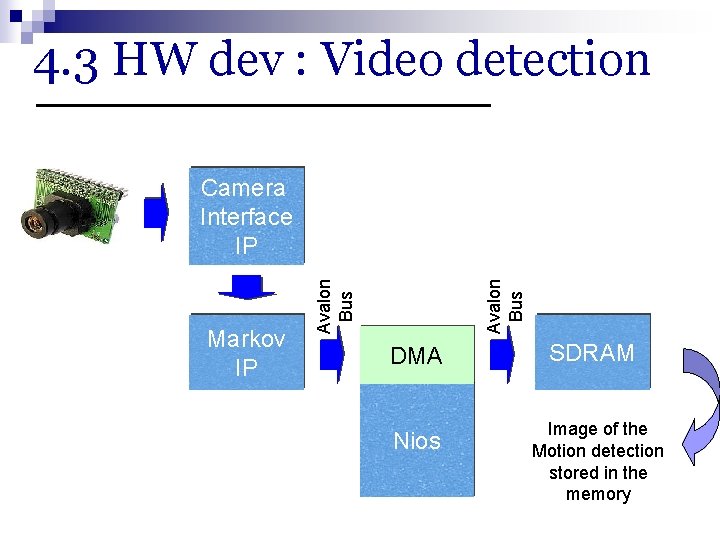

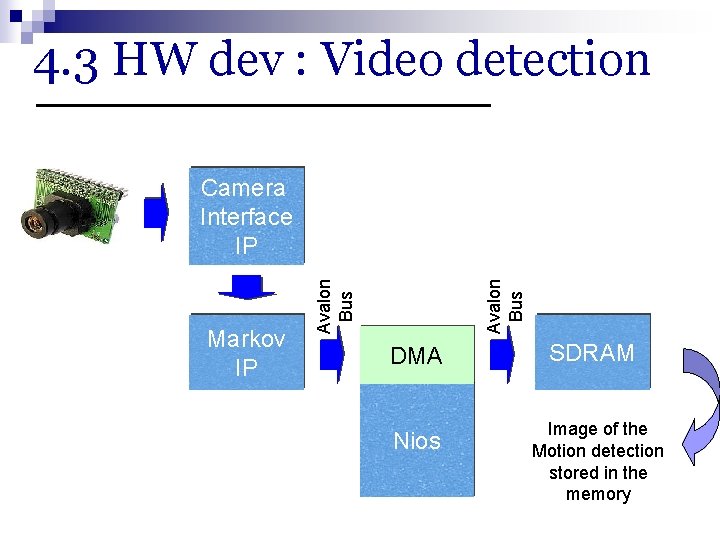

4. 3 HW dev : Video detection Avalon Bus Markov IP Avalon Bus Camera Interface IP DMA Nios SDRAM Image of the Motion detection stored in the memory

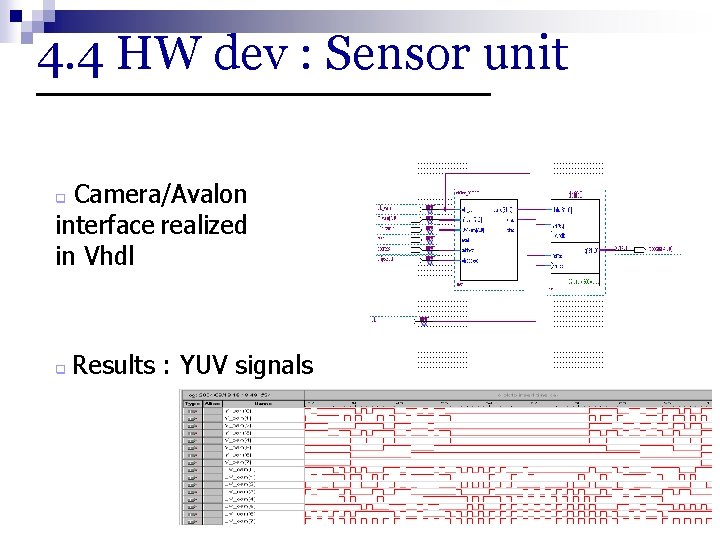

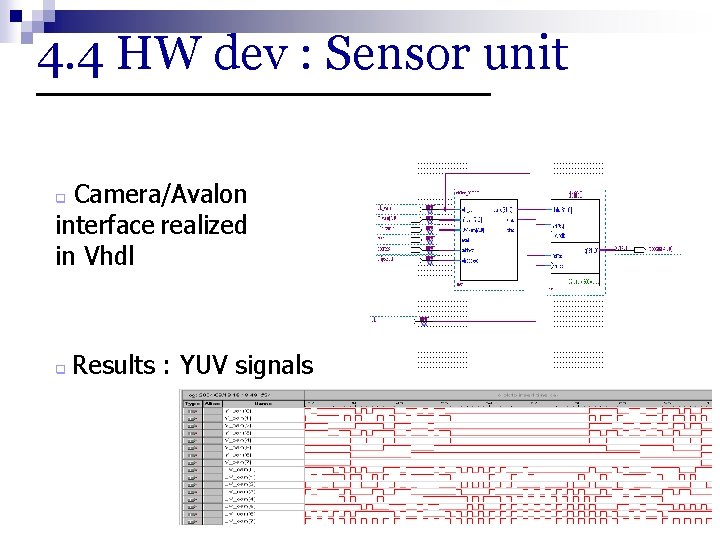

4. 4 HW dev : Sensor unit Camera/Avalon interface realized in Vhdl q q Results : YUV signals

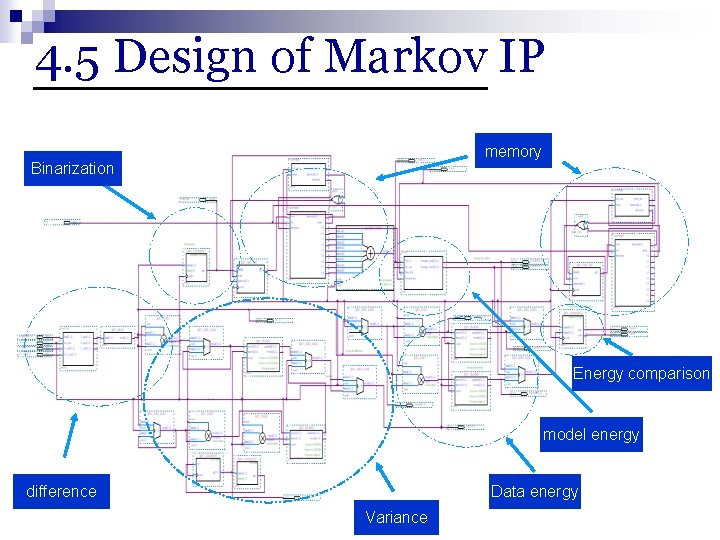

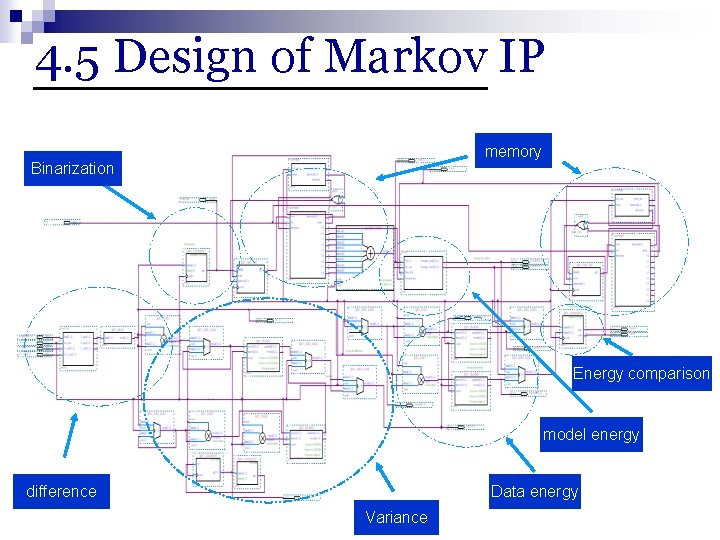

4. 5 Design of Markov IP memory Binarization Energy comparison model energy difference Data energy Variance

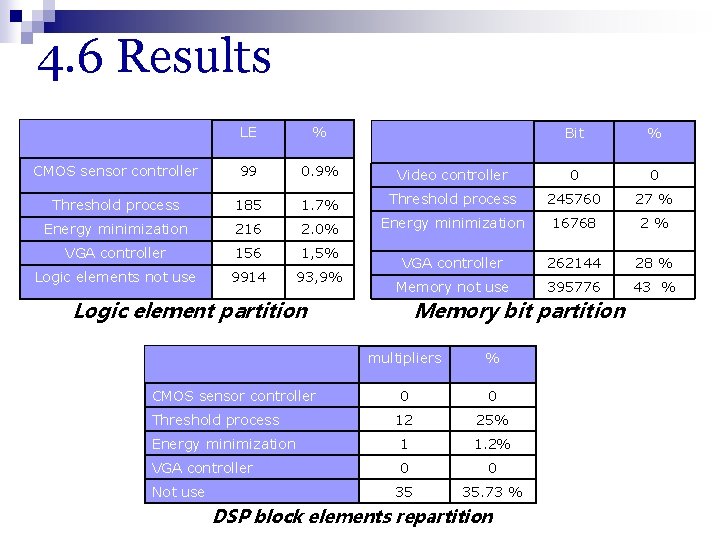

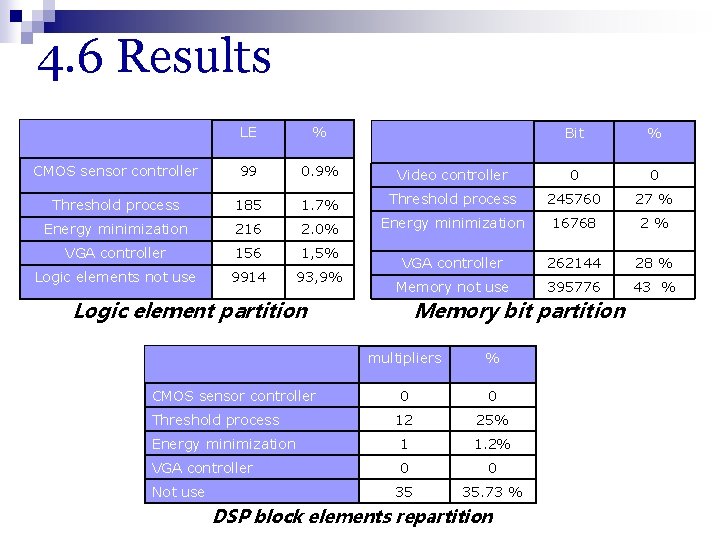

4. 6 Results LE % CMOS sensor controller 99 0. 9% Threshold process 185 Energy minimization Bit % Video controller 0 0 1. 7% Threshold process 245760 27 % 216 2. 0% Energy minimization 16768 2% VGA controller 156 1, 5% Logic elements not use 9914 93, 9% VGA controller 262144 28 % Memory not use 395776 43 % Logic element partition Memory bit partition multipliers % 0 0 12 25% Energy minimization 1 1. 2% VGA controller 0 0 35 35. 73 % CMOS sensor controller Threshold process Not use DSP block elements repartition

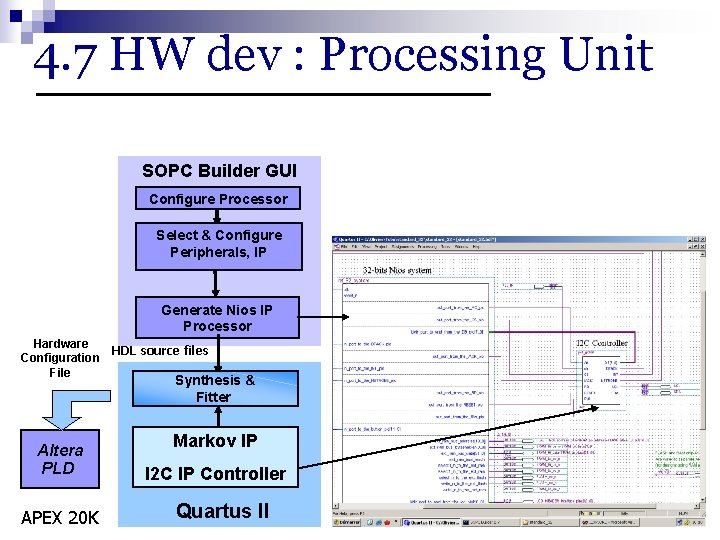

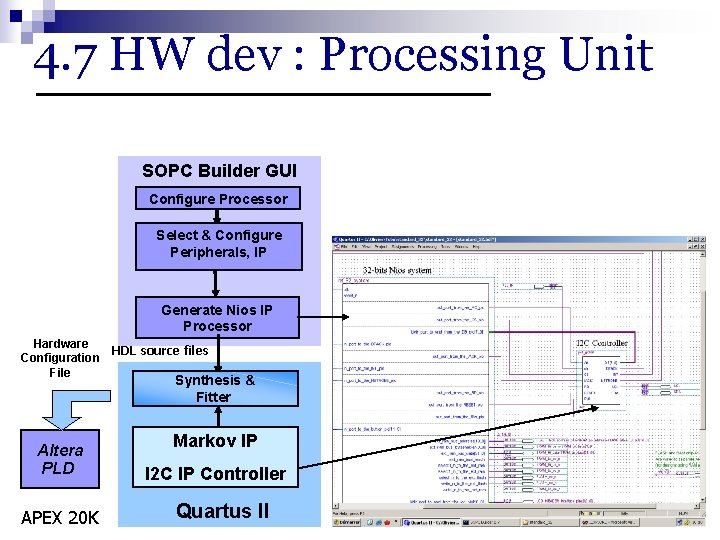

4. 7 HW dev : Processing Unit SOPC Builder GUI Configure Processor Select & Configure Peripherals, IP Generate Nios IP Processor Hardware Configuration File Altera PLD APEX 20 K HDL source files Synthesis & Fitter Markov IP I 2 C IP Controller Quartus II

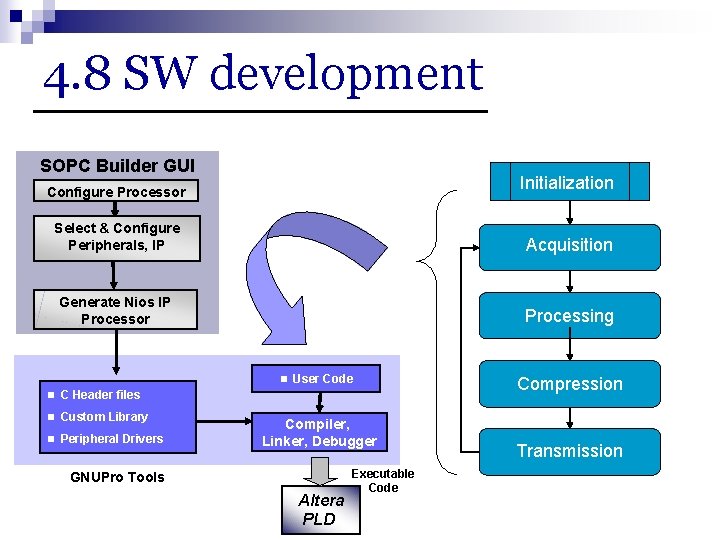

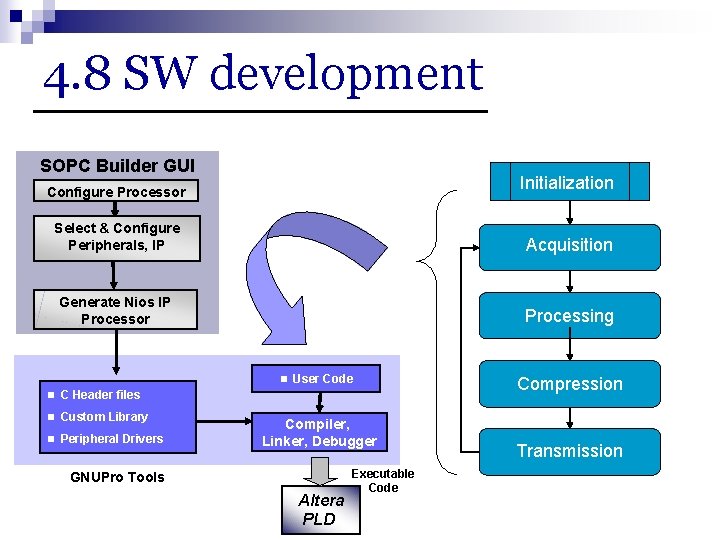

4. 8 SW development SOPC Builder GUI Initialization Configure Processor Select & Configure Peripherals, IP Acquisition Generate Nios IP Processor Processing n n C Header files n Custom Library n Peripheral Drivers User Code Compiler, Linker, Debugger GNUPro Tools Altera PLD Executable Code Compression Transmission

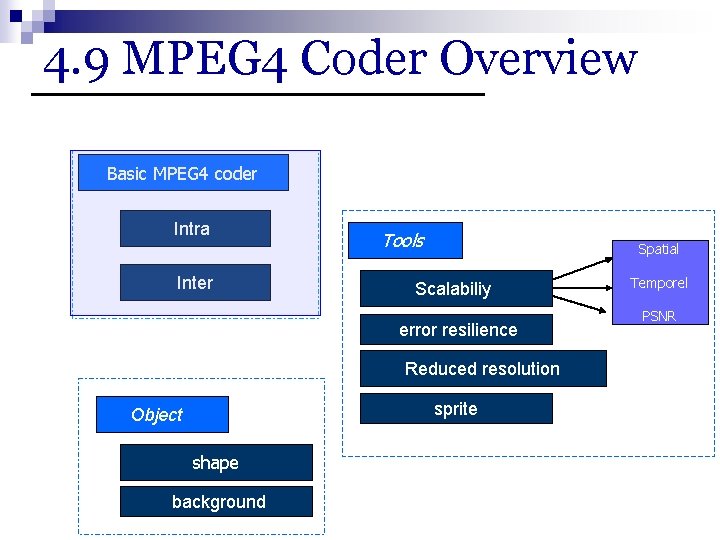

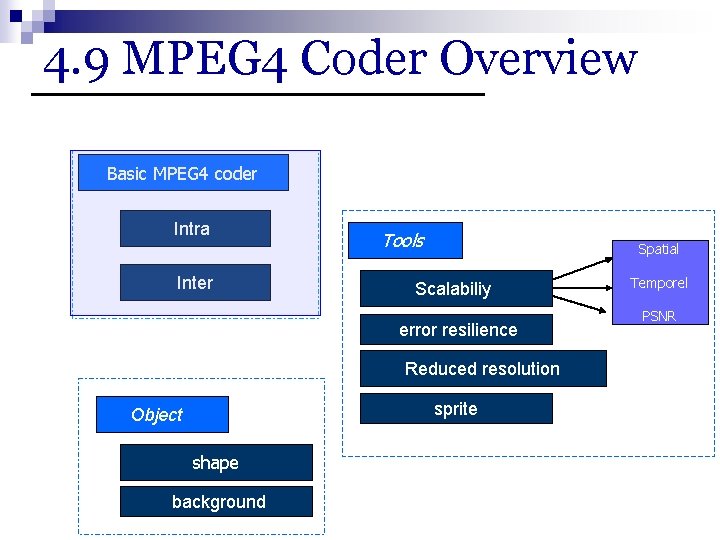

4. 9 MPEG 4 Coder Overview Basic MPEG 4 coder Intra Inter Tools Spatial Scalabiliy error resilience Reduced resolution sprite Object shape background Temporel PSNR

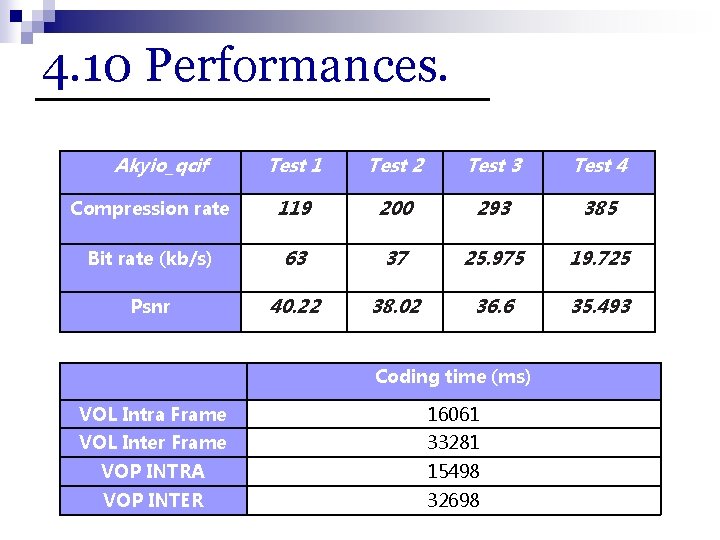

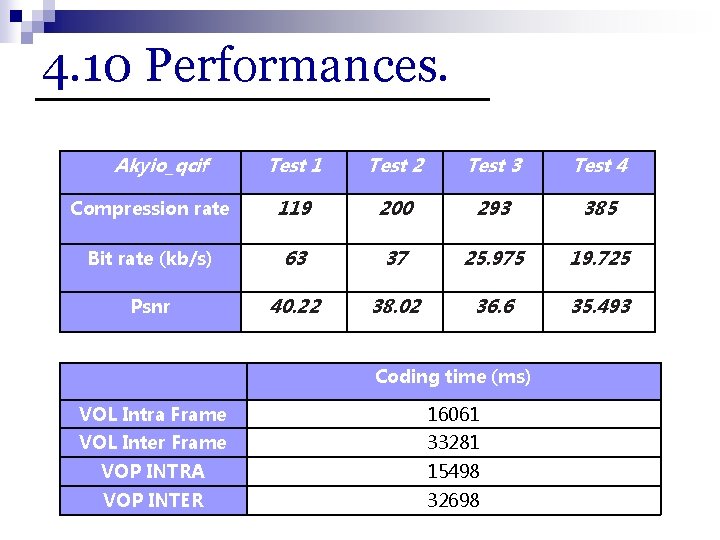

4. 10 Performances. Akyio_qcif Test 1 Test 2 Test 3 Test 4 Compression rate 119 200 293 385 Bit rate (kb/s) 63 37 25. 975 19. 725 Psnr 40. 22 38. 02 36. 6 35. 493 Coding time (ms) VOL Intra Frame 16061 VOL Inter Frame 33281 VOP INTRA 15498 VOP INTER 32698

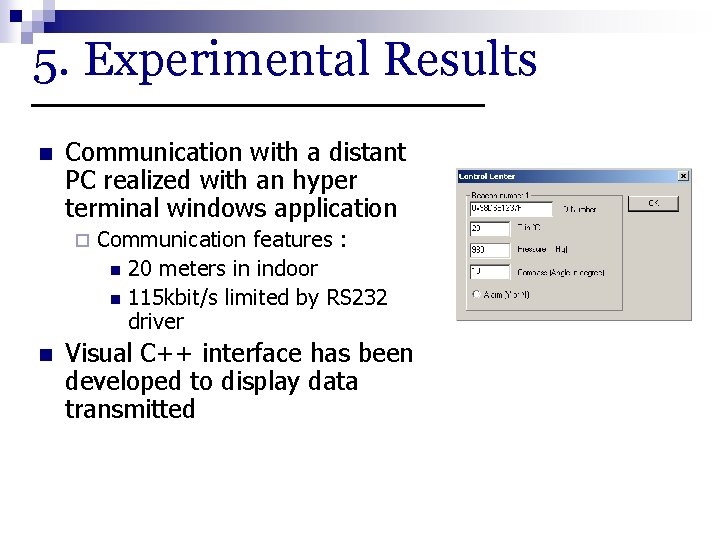

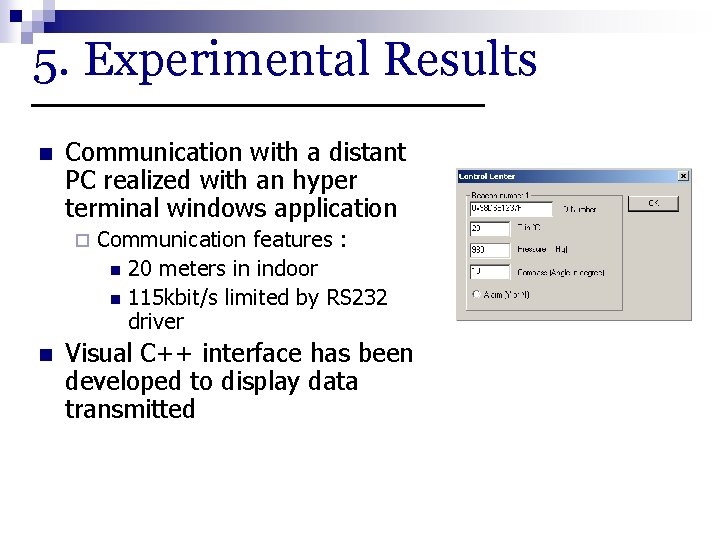

5. Experimental Results n Communication with a distant PC realized with an hyper terminal windows application ¨ n Communication features : n 20 meters in indoor n 115 kbit/s limited by RS 232 driver Visual C++ interface has been developed to display data transmitted

5. 1 Experimental Results

6. Conclusion we have introduced n the architecture of an intelligent beacon for wireless sensor networks n first implementation : MERITE with following features Markov (HW) detector ¨ MPEG 4 (SW) compressor ¨ Wireless compression ¨

The End Thanks you for your attention