Design and Analysis of RealTime Software REal TIme

- Slides: 18

Design and Analysis of Real-Time Software REal TIme System Laboratory Scuola Superiore S. Anna G. Lipari E. Bini Ericsson Lab Italia C. Vitucci

Outline n Introduction to RT embedded systems n n n characteristics problems state of the art RT system research at Retis Lab Goal of this research n n Methodology Phases

Goal of this research n Methodology for the design and analysis of Real-Time Embedded applications to be used in all phases of development

Starting Point n Real Time embedded applications n n n n car controller hand-held computers cellular phone next generation cellular phones (UMTS) wearable computers etc. The target application n telecommunication control board

RT embedded applications n Limited resources n n n memory CPU speed power consumption Dedicated HW Temporal constraints n n Applications must react to external environment in a timely manner Internal constraints (buffer size, interrupt handling, etc. )

RT design and analysis n Support temporal determinism: n providing kernel-level services • priority-based schedulers • bounded delay on system calls n providing tools for off-line analysis • a tool for specification in a formal (or semi-formal) language • a tool for timing analysis • a tool for testing

Application model n Application n A task can be activated n n n on a single processor there are low-level control tasks (driver ATM etc. ) and high-level control tasks (signaling) need to verify the temporal constraints on every task/activity periodically (time driven) by external events (event driven) Tasks communicate through messages

RTOS and HW n OSE Delta n n n currently used in Ericsson for developing software for RT embedded applications based on a message passing communication mechanism HW n n n usually, a single processor board many different processor can be used performance strongly depends on the HW

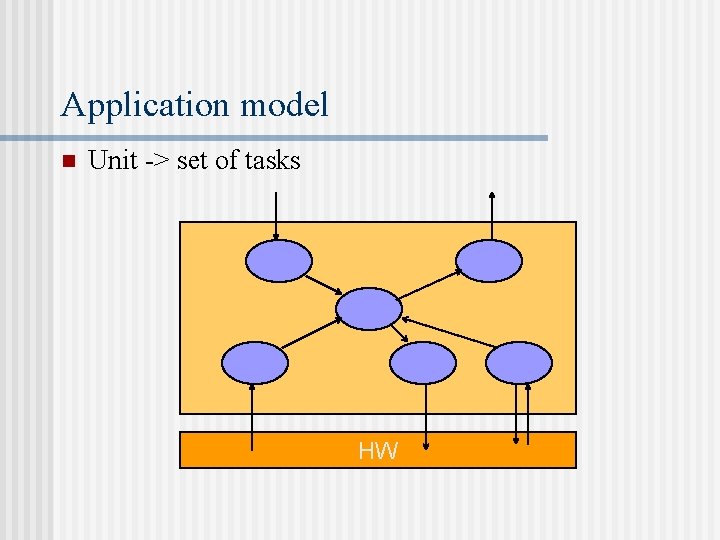

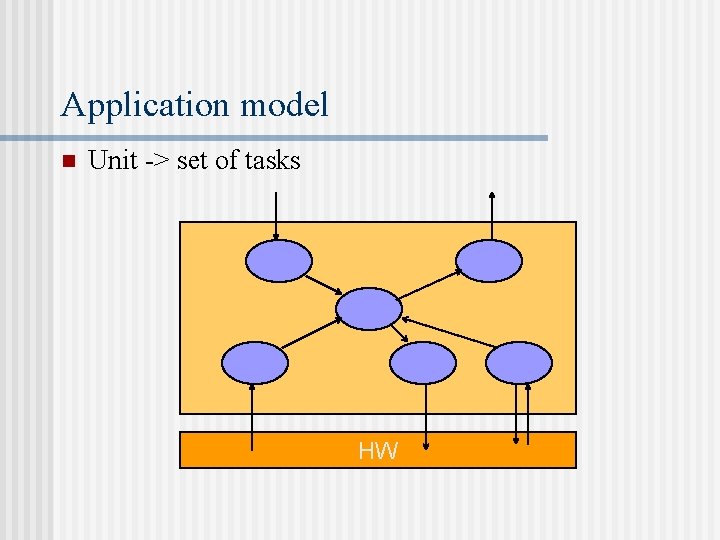

Application model n Unit -> set of tasks HW

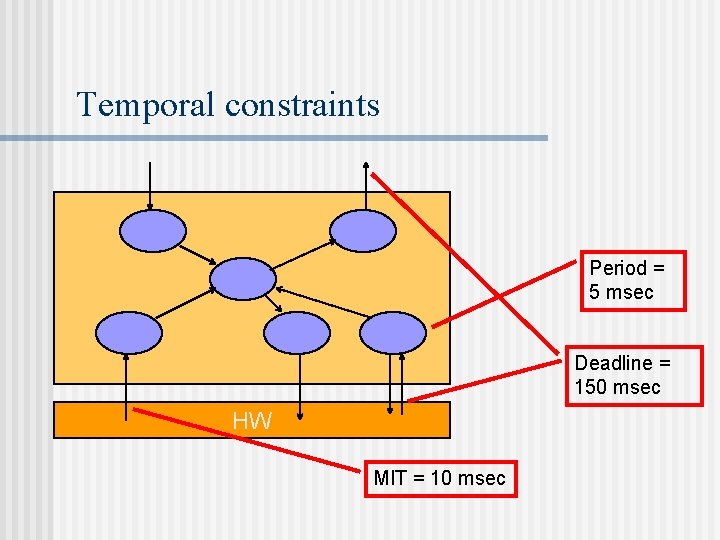

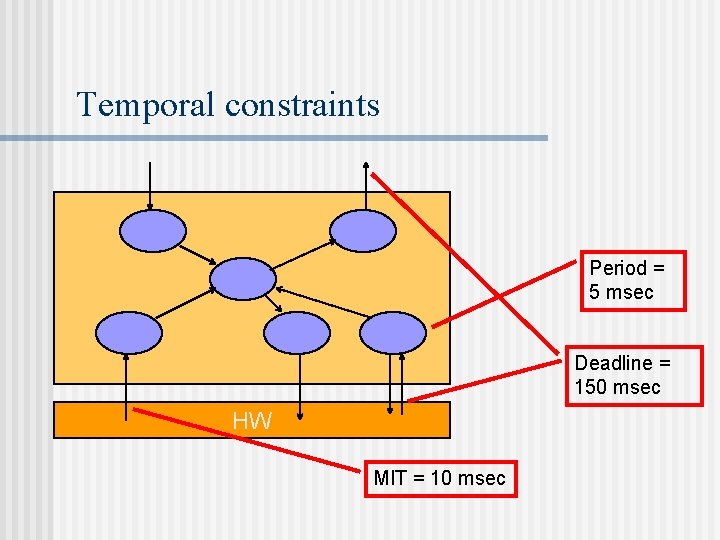

Temporal constraints Period = 5 msec Deadline = 150 msec HW MIT = 10 msec

State of the art n In the engineering practice n n no a-priori timing analysis is done low-level control tasks are directly coded in C or assembler often, the code of high-level control tasks is automatically generated by tools that do not consider temporal constraints temporal constraint are verified only during the testing phase

State of the art n RT Analysis n RT research focused on time-driven control applications • schedulability conditions for periodic task sets n n Few research papers on RT analysis of reactive (event driven) systems Commercial tools: Time Wiz n n Rate Monotonic analysis non-std notation for specification

State of the art: RT notations n Existing notations n n n UML is a good candidate notation A preliminary proposal to OMG for a standard RT extension to UML has been made in Aug. 2000 n n HRT-HOOD (used in aerospace applications) ROOM (from Object Time, now Rational Software) Not suitable for our purposes proponents: Time. Sys, I-Logix, Rational Software, etc. http: //www. omg. org/meetings/schedule/UML_Profile_for_Scheduling_RFP. html

Problems n Few tools integrate specification and analysis n n The greatest problem is to estimate the worst case computation time of every activity n n n Time Wiz of Time. Sys is one of the few strongly depends on the HW existing tools cover a narrow range of HW configurations There is the need for a tool that covers the entire development cycle n n at design time, with a proper RT notation after development, with a RT analysis

Summary n Many different tools n n for RT-analysis (Time Wiz) for RT specification (Rational Rose RT) for WCET analysis (VCC) no easy-to-use off-the-shelf solution n there is the need to integrate different of technologies n specification of RT systems n RT analysis n WCET computation n etc.

Research at Retis Lab n ASI project n n Intecs definition of a HRT-UML notation enhancing UML-nice with RT-analysis MADESS project n n n Parades, Magneti Marelli, ST microelectronics RT kernel for embedded controllers with minimal memory requirements RT kernel for multi-processor system-on-a-chip

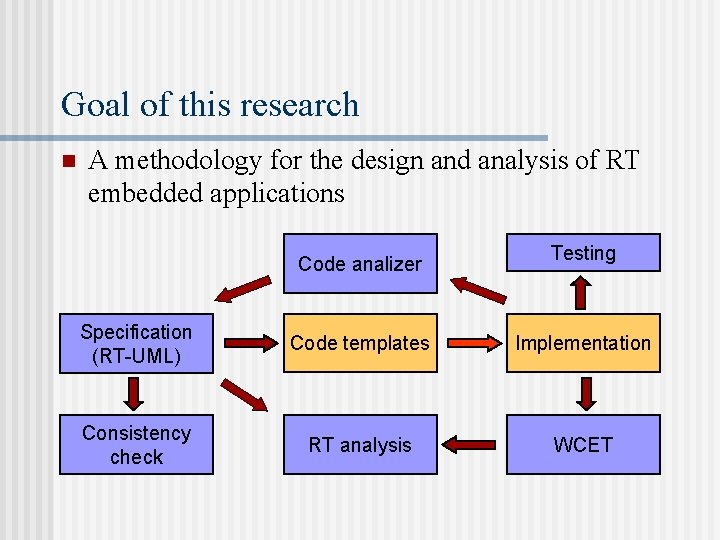

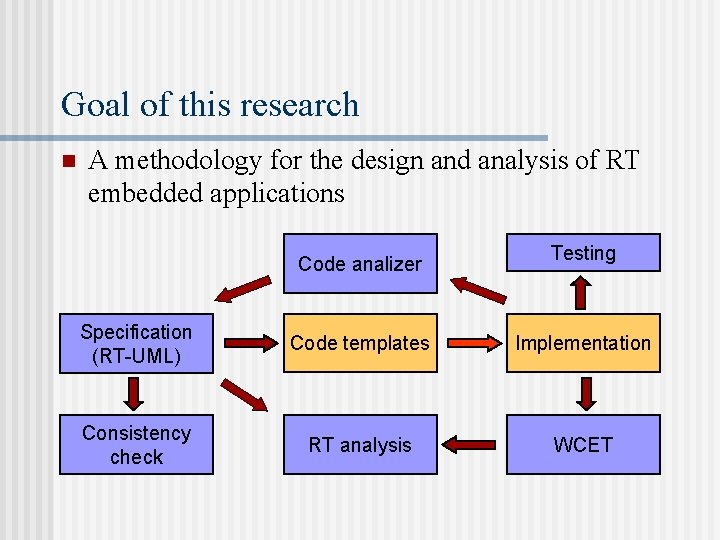

Goal of this research n A methodology for the design and analysis of RT embedded applications Code analizer Testing Specification (RT-UML) Code templates Implementation Consistency check RT analysis WCET

Phases n n n Model of a OSE-Delta process Mapping to the appropriate RT-UML notation RT analysis on the model n n consistency check timing analysis priority assignment Integrating WCET computation