Descrierea structurilor secveniale elementare Algoritmul comportamental se descrie

![module Counter (data, rst, count_en, load, up_down, clk, prs, q) ; input[15: 0] data module Counter (data, rst, count_en, load, up_down, clk, prs, q) ; input[15: 0] data](https://slidetodoc.com/presentation_image_h2/3c3abacaa1cf9722dbad64819ed9aac6/image-8.jpg)

![Ex : module Rg (d, clk, rst, load, q) ; input [3: 0] d Ex : module Rg (d, clk, rst, load, q) ; input [3: 0] d](https://slidetodoc.com/presentation_image_h2/3c3abacaa1cf9722dbad64819ed9aac6/image-18.jpg)

![Rg u 1 a[3: 0] d v[7: 4] q Rg u 3 clk rst Rg u 1 a[3: 0] d v[7: 4] q Rg u 3 clk rst](https://slidetodoc.com/presentation_image_h2/3c3abacaa1cf9722dbad64819ed9aac6/image-23.jpg)

- Slides: 25

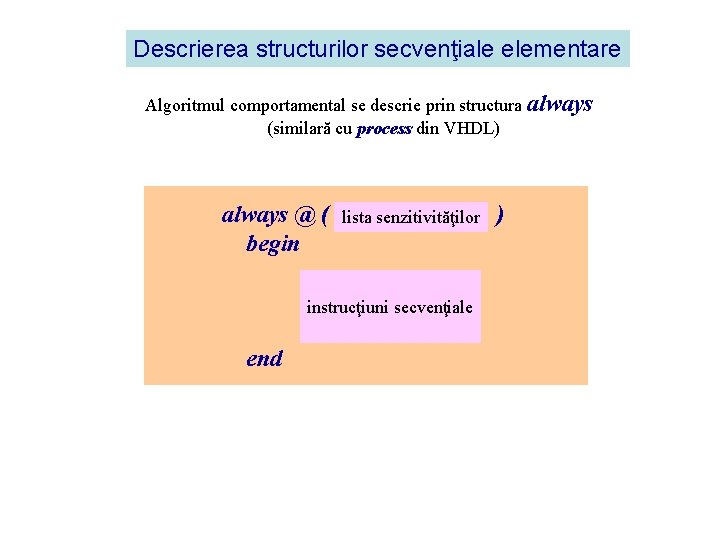

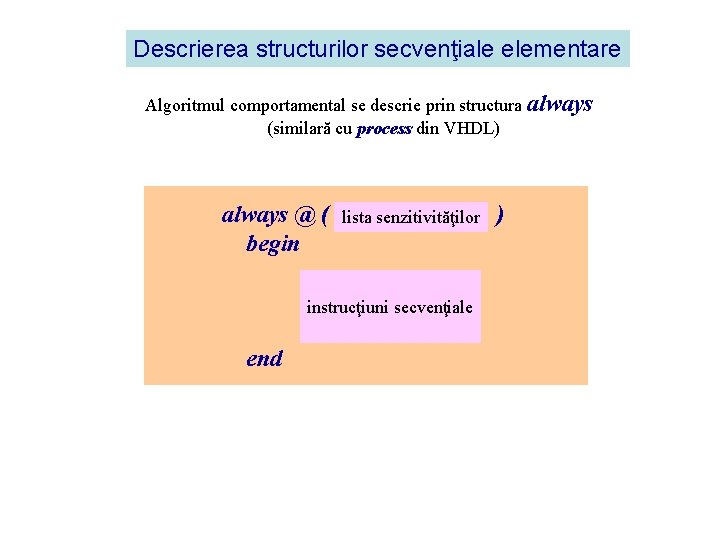

Descrierea structurilor secvenţiale elementare Algoritmul comportamental se descrie prin structura always (similară cu process din VHDL) always @ ( begin lista senzitivităţilor instrucţiuni secvenţiale end )

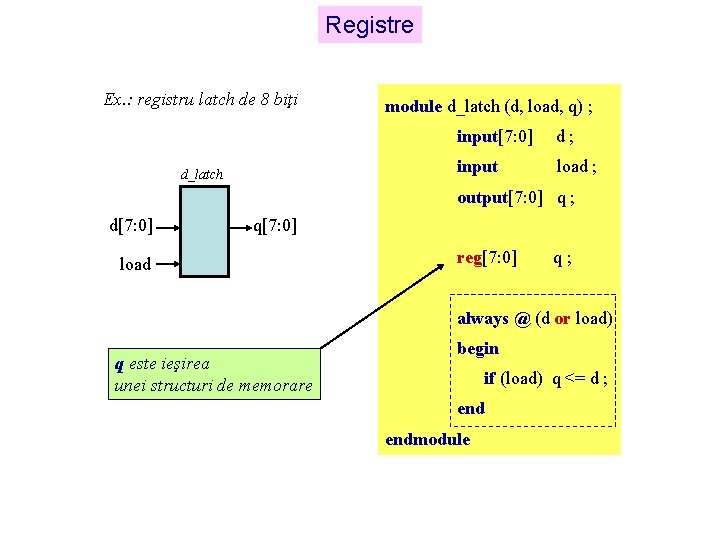

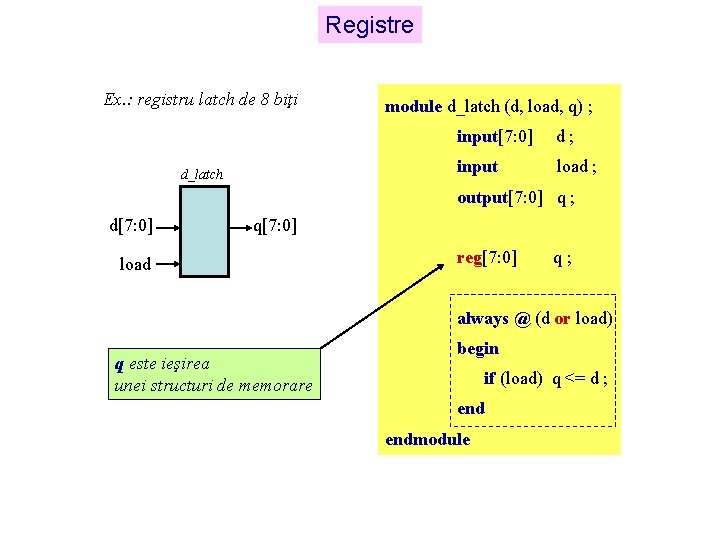

Registre Ex. : registru latch de 8 biţi d_latch module d_latch (d, load, q) ; input[7: 0] d; input load ; output[7: 0] q ; d[7: 0] q[7: 0] load reg[7: 0] q; always @ (d or load) q este ieşirea unei structuri de memorare begin if (load) q <= d ; endmodule

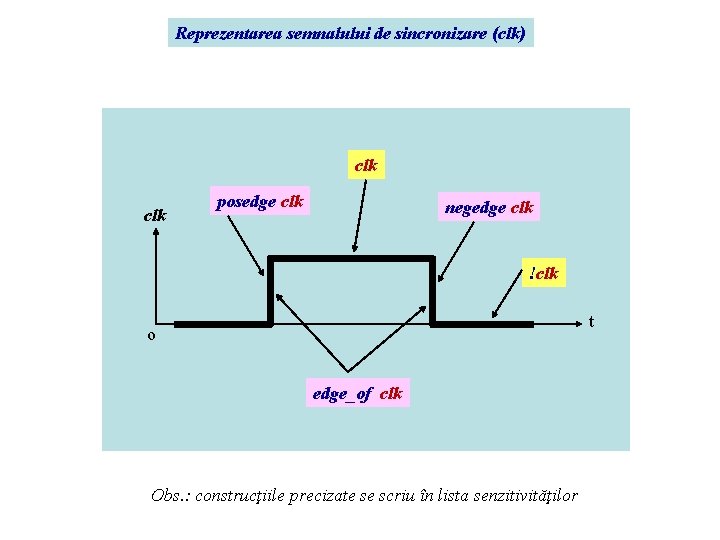

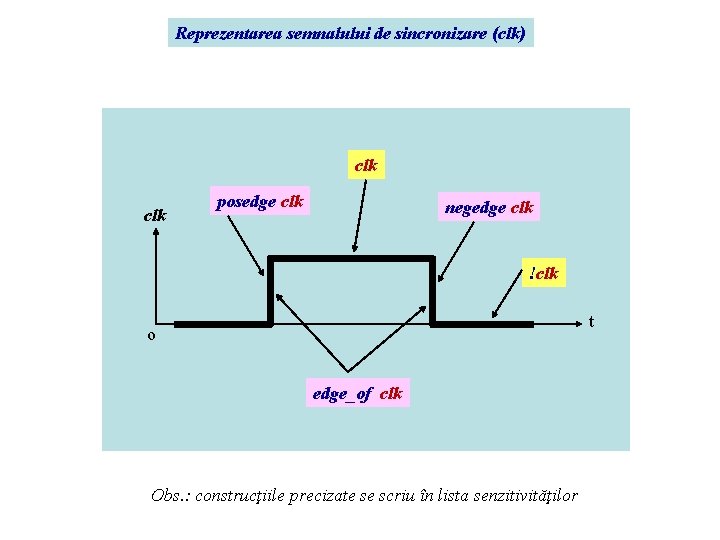

Reprezentarea semnalului de sincronizare (clk) clk posedge clk negedge clk !clk t o edge_of clk Obs. : construcţiile precizate se scriu în lista senzitivităţilor

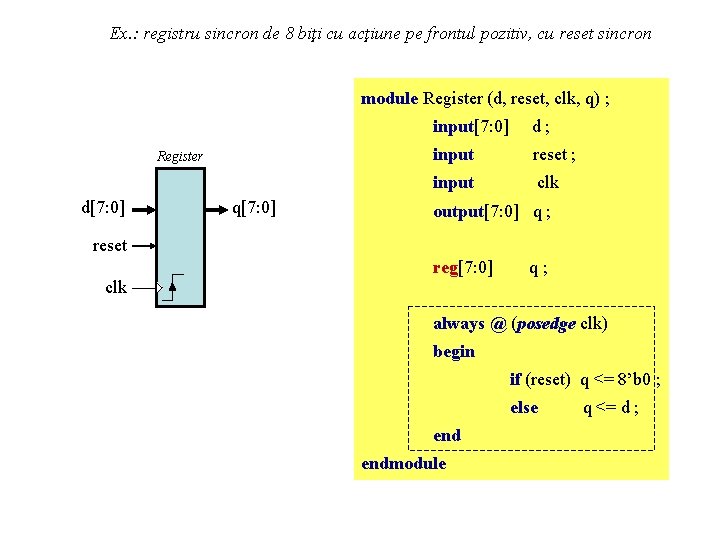

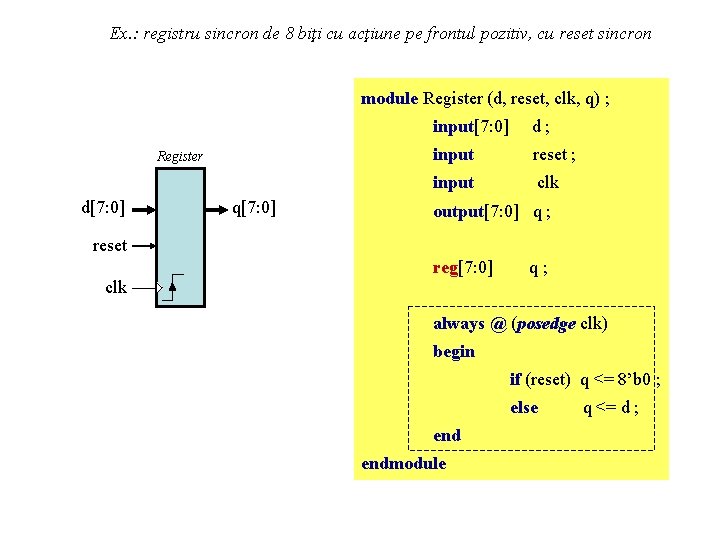

Ex. : registru sincron de 8 biţi cu acţiune pe frontul pozitiv, cu reset sincron module Register (d, reset, clk, q) ; Register d[7: 0] q[7: 0] input[7: 0] d; input reset ; input clk output[7: 0] q ; reset reg[7: 0] q; clk always @ (posedge clk) begin if (reset) q <= 8’b 0 ; else endmodule q <= d ;

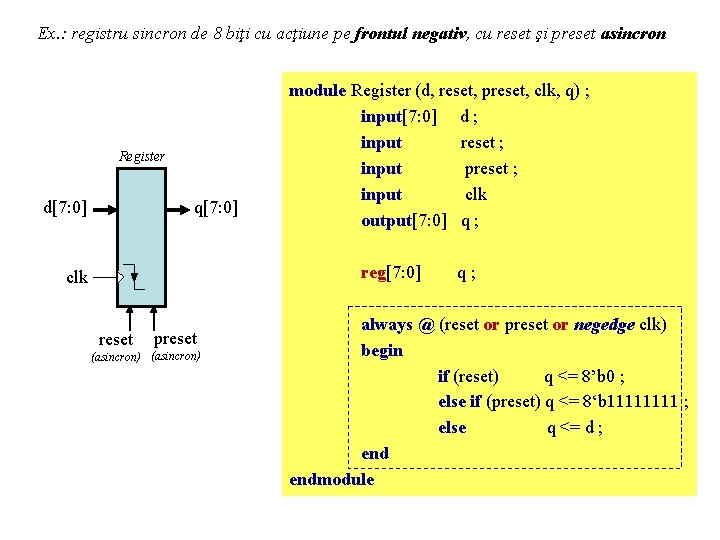

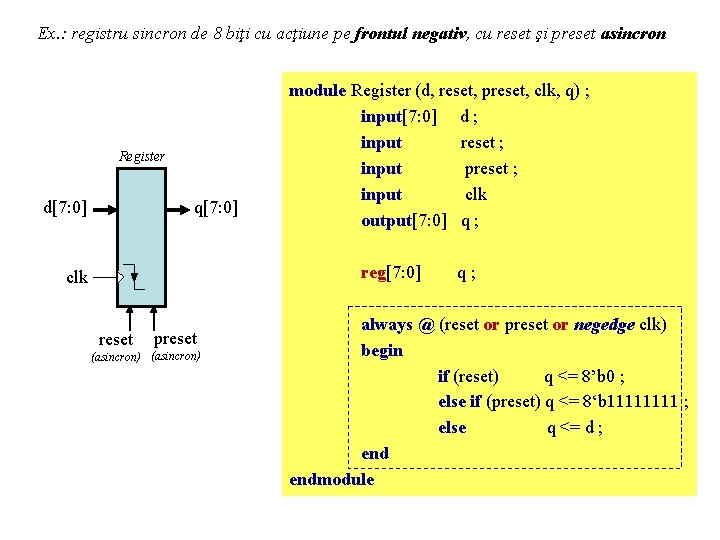

Ex. : registru sincron de 8 biţi cu acţiune pe frontul negativ, cu reset şi preset asincron Register d[7: 0] q[7: 0] module Register (d, reset, preset, clk, q) ; input[7: 0] d ; input reset ; input preset ; input clk output[7: 0] q ; reg[7: 0] clk reset preset (asincron) q; always @ (reset or preset or negedge clk) begin if (reset) q <= 8’b 0 ; else if (preset) q <= 8‘b 1111 ; else q <= d ; endmodule

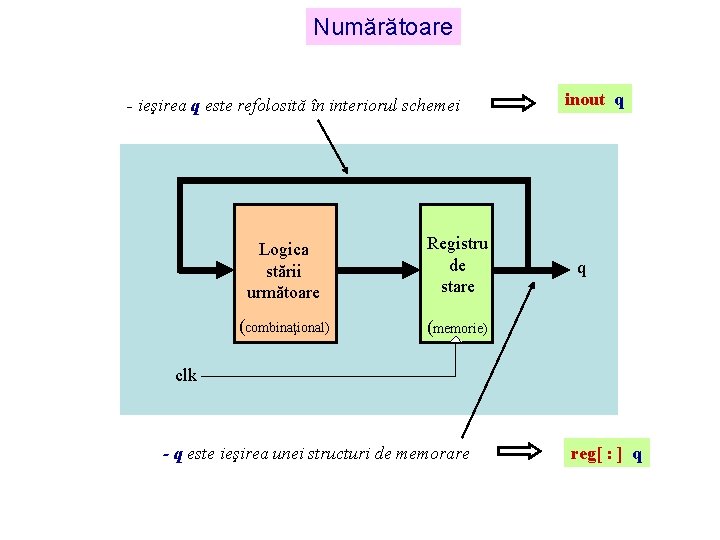

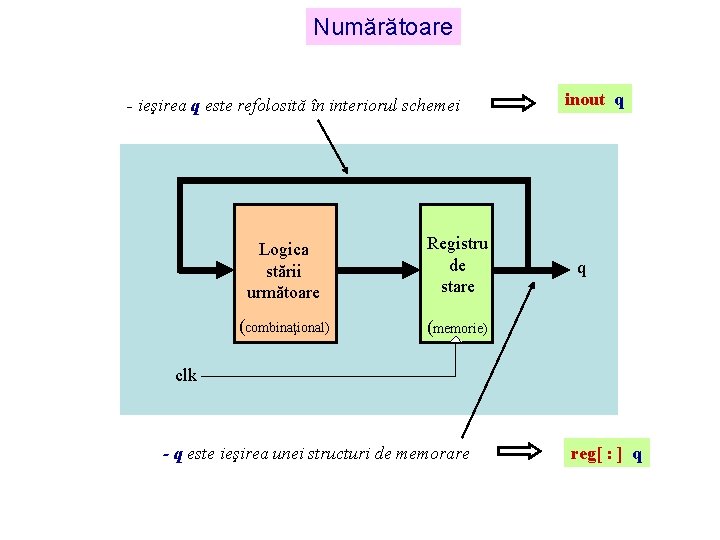

Numărătoare - ieşirea q este refolosită în interiorul schemei Logica stării următoare Registru de stare (combinaţional) (memorie) inout q q clk - q este ieşirea unei structuri de memorare reg[ : ] q

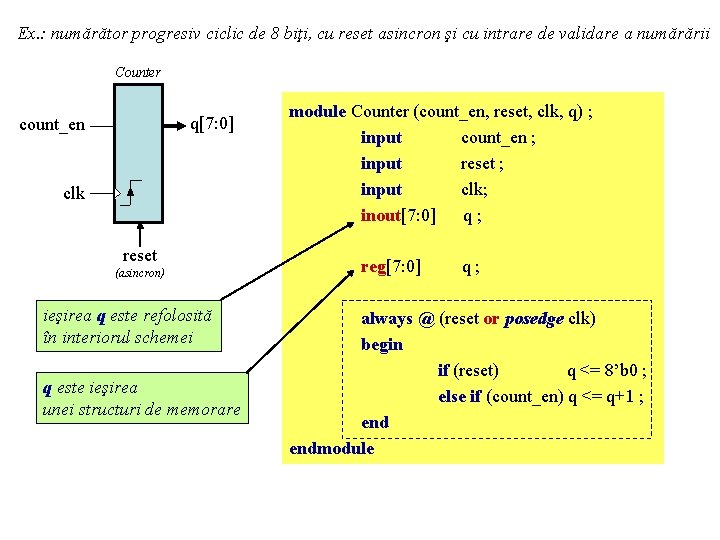

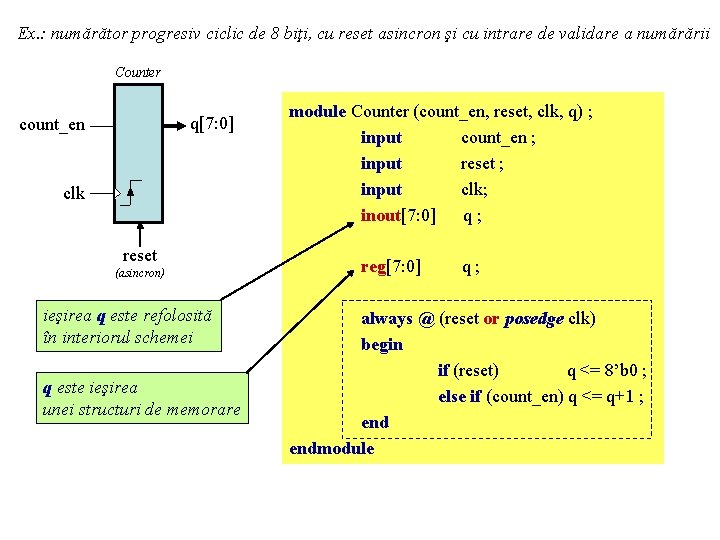

Ex. : numărător progresiv ciclic de 8 biţi, cu reset asincron şi cu intrare de validare a numărării Counter q[7: 0] count_en clk reset (asincron) ieşirea q este refolosită în interiorul schemei q este ieşirea unei structuri de memorare module Counter (count_en, reset, clk, q) ; input count_en ; input reset ; input clk; inout[7: 0] q; reg[7: 0] q; always @ (reset or posedge clk) begin if (reset) q <= 8’b 0 ; else if (count_en) q <= q+1 ; endmodule

![module Counter data rst counten load updown clk prs q input15 0 data module Counter (data, rst, count_en, load, up_down, clk, prs, q) ; input[15: 0] data](https://slidetodoc.com/presentation_image_h2/3c3abacaa1cf9722dbad64819ed9aac6/image-8.jpg)

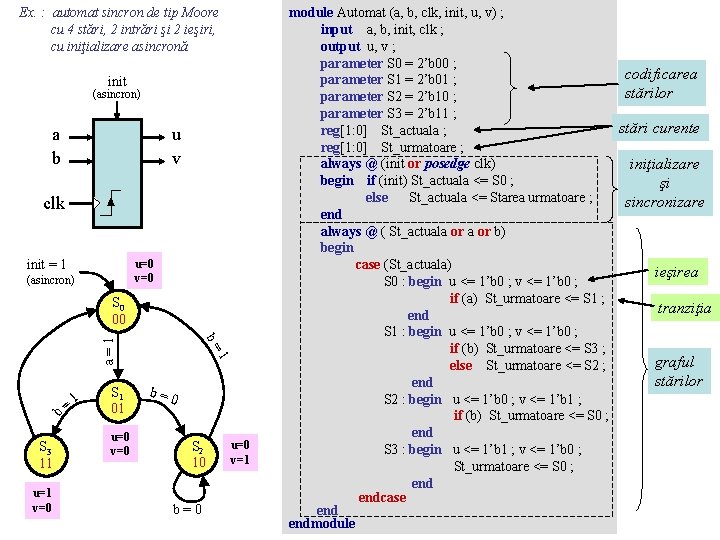

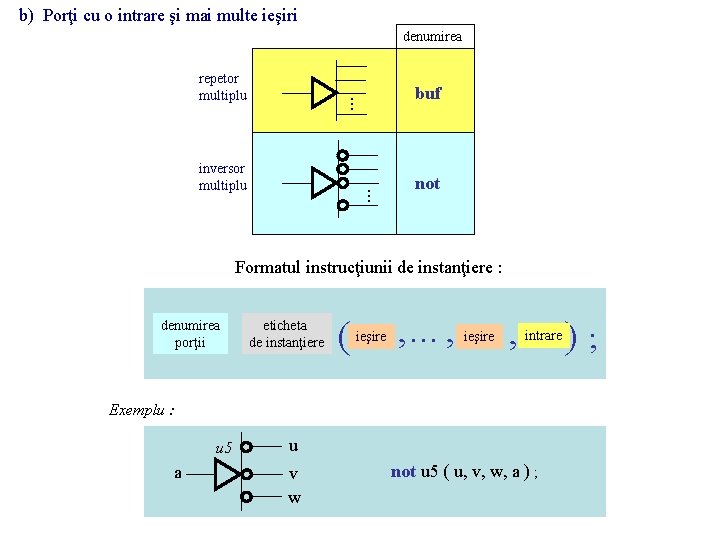

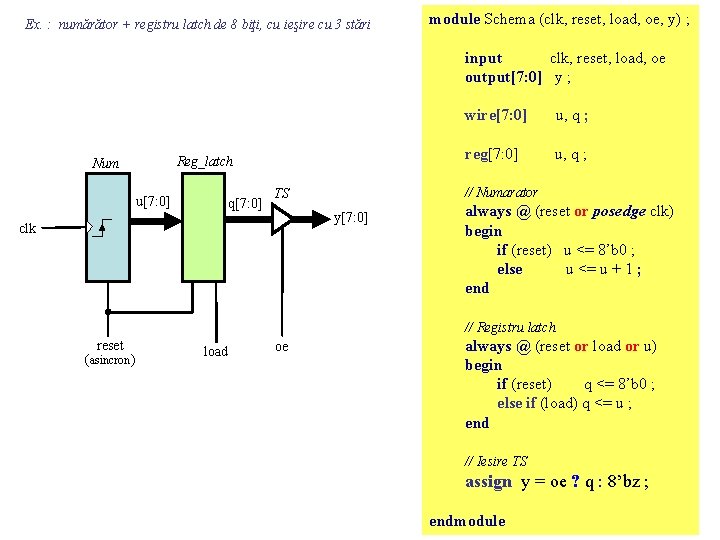

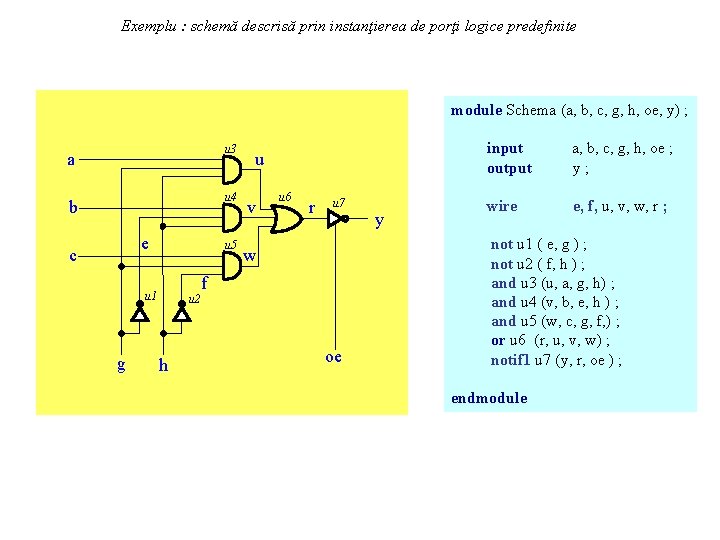

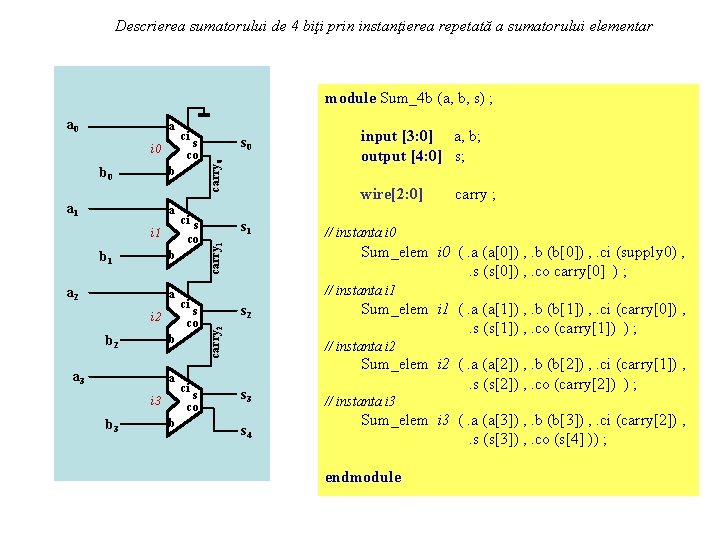

module Counter (data, rst, count_en, load, up_down, clk, prs, q) ; input[15: 0] data ; -numărare pe frontul negativ al clk input rst ; -reset sincron (rst) input count_en ; -preset asincron (prs) input load; -intrare de validare a numărării (count_en) input up_down ; -intrare de încărcare (load) a datelor (data) input clk ; -reversibil (up_down) input prs ; inout[15: 0] q; reg[15: 0] q; Counter always @ (prs or negedge clk) data[15: 0] begin q[15: 0] if (prs) q <= 16’h. FFFF ; toţi biţii 1 rst else begin count_en if (rst) q <= 16 b’ 0 ; toţi biţii 0 load else if (load) q <= data ; încarcă data else if (count_en) up_down begin if (up_down) q <= q + 1 ; numără progresiv clk else q <= q – 1 ; end numără regresiv end prs end (asincron) endmodule Ex. : numărător reversibil de 16 biţi : --------------------------

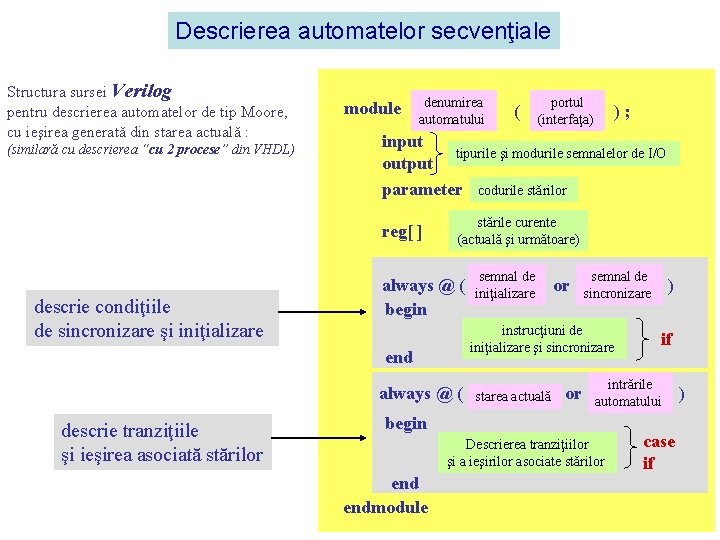

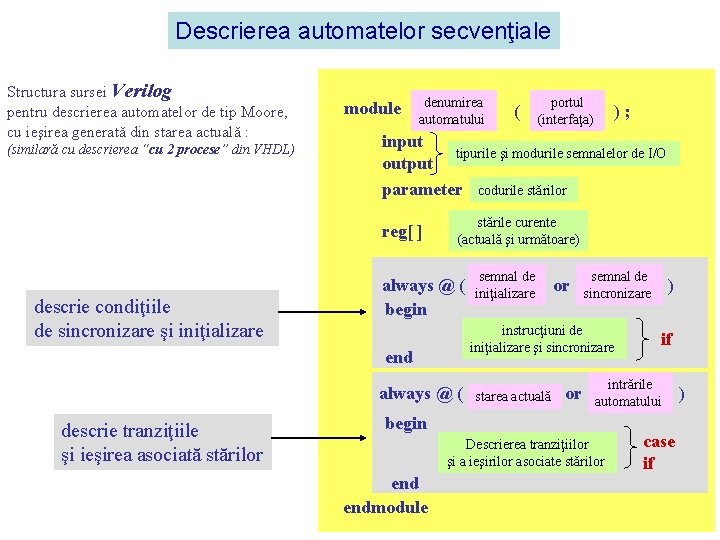

Descrierea automatelor secvenţiale Structura sursei Verilog pentru descrierea automatelor de tip Moore, cu ieşirea generată din starea actuală : (similară cu descrierea “cu 2 procese” din VHDL) module denumirea automatului ); stările curente (actuală şi următoare) always @ ( begin semnal de iniţializare or semnal de sincronizare instrucţiuni de iniţializare şi sincronizare end always @ ( descrie tranziţiile şi ieşirea asociată stărilor portul (interfaţa) input tipurile şi modurile semnalelor de I/O output parameter codurile stărilor reg[ ] descrie condiţiile de sincronizare şi iniţializare ( starea actuală or if intrările automatului begin Descrierea tranziţiilor şi a ieşirilor asociate stărilor endmodule ) case if )

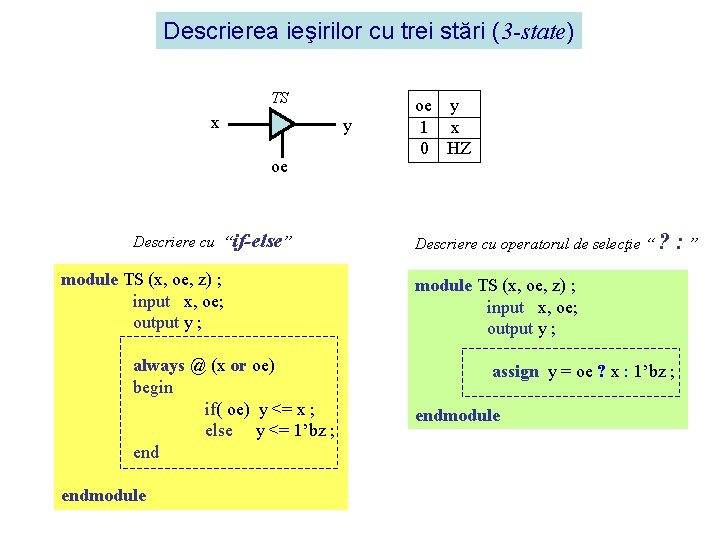

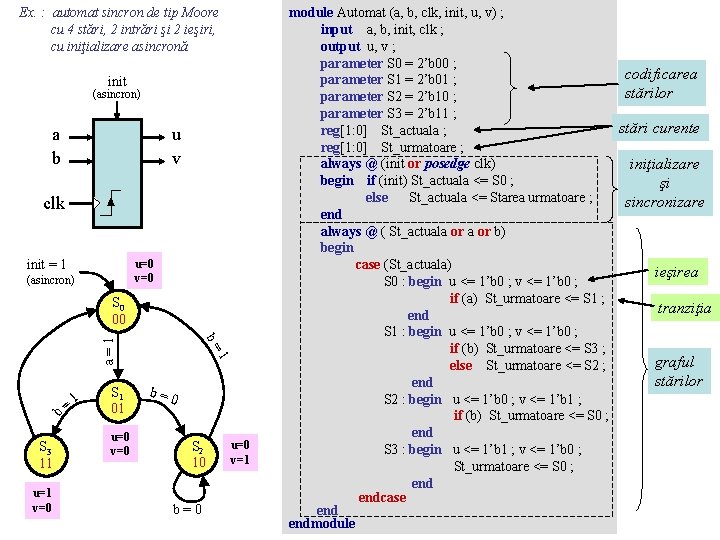

Ex. : automat sincron de tip Moore cu 4 stări, 2 intrări şi 2 ieşiri, cu iniţializare asincronă init (asincron) a b u v clk init = 1 u=0 v=0 (asincron) S 0 00 S 3 11 u=1 v=0 S 1 01 u=0 v=0 1 a=1 b= b= 1 b= 0 S 2 10 b=0 u=0 v=1 module Automat (a, b, clk, init, u, v) ; input a, b, init, clk ; output u, v ; parameter S 0 = 2’b 00 ; codificarea parameter S 1 = 2’b 01 ; stărilor parameter S 2 = 2’b 10 ; parameter S 3 = 2’b 11 ; stări curente reg[1: 0] St_actuala ; reg[1: 0] St_urmatoare ; always @ (init or posedge clk) iniţializare begin if (init) St_actuala <= S 0 ; şi else St_actuala <= Starea urmatoare ; sincronizare end always @ ( St_actuala or b) begin case (St_actuala) ieşirea S 0 : begin u <= 1’b 0 ; v <= 1’b 0 ; if (a) St_urmatoare <= S 1 ; tranziţia end S 1 : begin u <= 1’b 0 ; v <= 1’b 0 ; if (b) St_urmatoare <= S 3 ; graful else St_urmatoare <= S 2 ; stărilor end S 2 : begin u <= 1’b 0 ; v <= 1’b 1 ; if (b) St_urmatoare <= S 0 ; end S 3 : begin u <= 1’b 1 ; v <= 1’b 0 ; St_urmatoare <= S 0 ; endcase endmodule

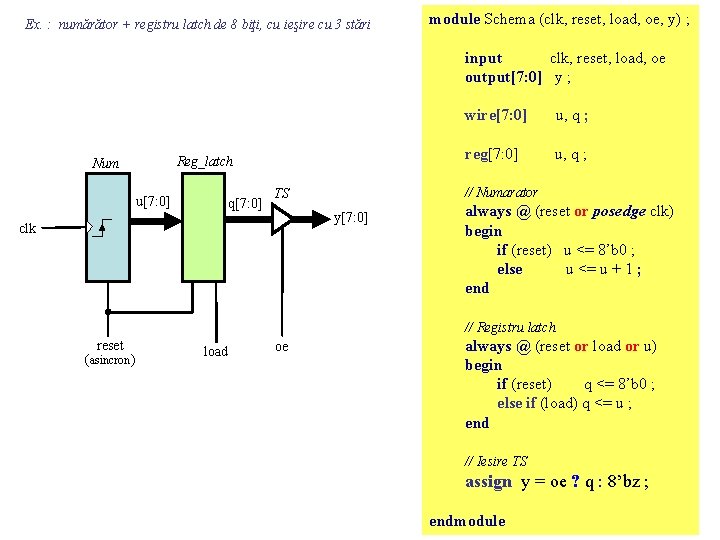

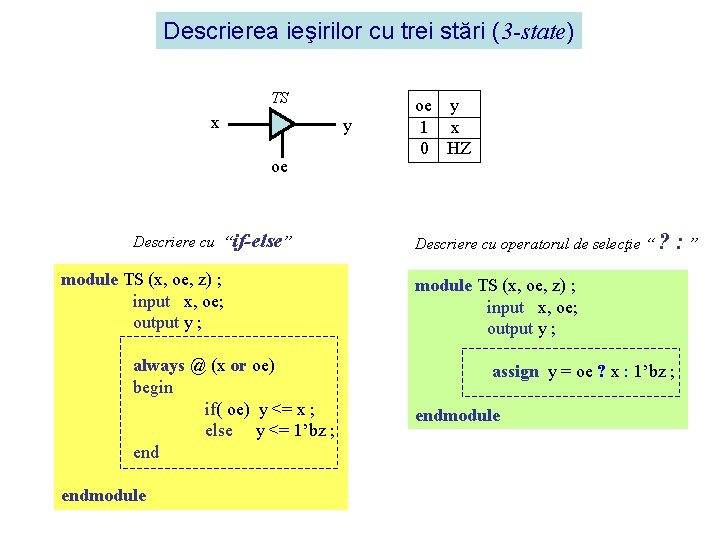

Descrierea ieşirilor cu trei stări (3 -state) TS x y oe Descriere cu “if-else” module TS (x, oe, z) ; input x, oe; output y ; always @ (x or oe) begin if( oe) y <= x ; else y <= 1’bz ; endmodule oe y 1 x 0 HZ Descriere cu operatorul de selecţie “ ? module TS (x, oe, z) ; input x, oe; output y ; assign y = oe ? x : 1’bz ; endmodule : ”

Ex. : numărător + registru latch de 8 biţi, cu ieşire cu 3 stări module Schema (clk, reset, load, oe, y) ; input clk, reset, load, oe output[7: 0] y ; Reg_latch Num u[7: 0] q[7: 0] u, q ; reg[7: 0] u, q ; // Numarator TS y[7: 0] clk wire[7: 0] always @ (reset or posedge clk) begin if (reset) u <= 8’b 0 ; else u <= u + 1 ; end // Registru latch reset (asincron) load oe always @ (reset or load or u) begin if (reset) q <= 8’b 0 ; else if (load) q <= u ; end // Iesire TS assign y = oe ? q : 8’bz ; endmodule

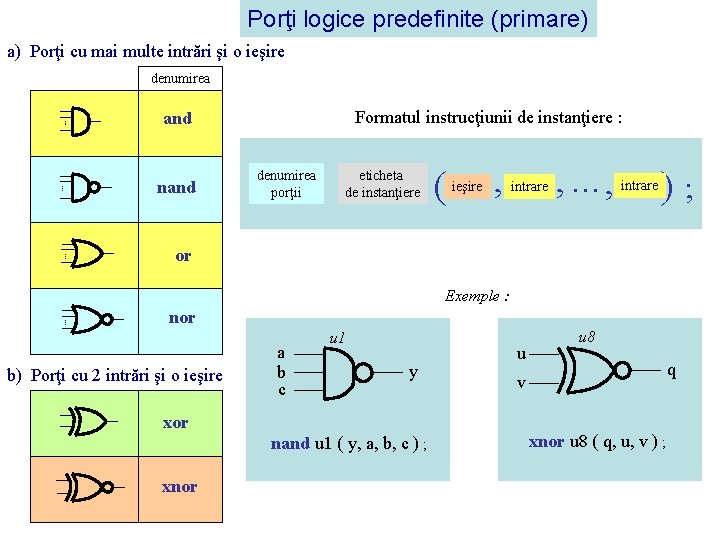

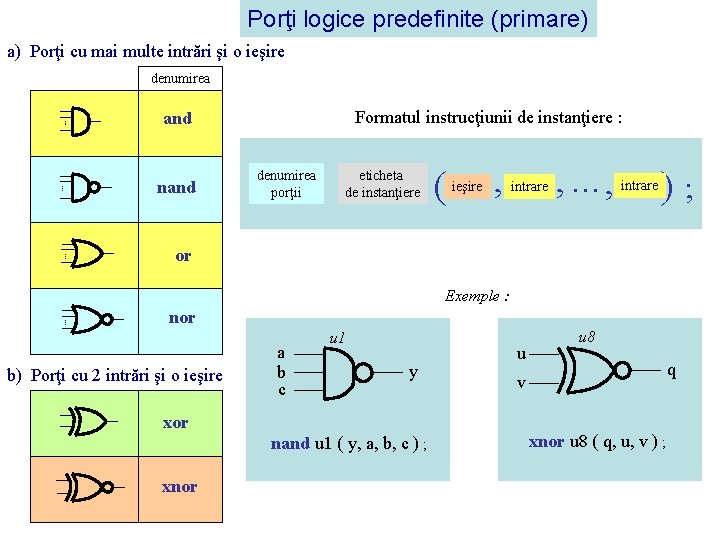

Porţi logice predefinite (primare) a) Porţi cu mai multe intrări şi o ieşire denumirea. . . nand . . . Formatul instrucţiunii de instanţiere : and denumirea porţii eticheta de instanţiere ( ieşire , intrare , . . . , intrare ); or Exemple : . . . nor b) Porţi cu 2 intrări şi o ieşire a b c u 1 y xor nand u 1 ( y, a, b, c ) ; xnor u u 8 q v xnor u 8 ( q, u, v ) ;

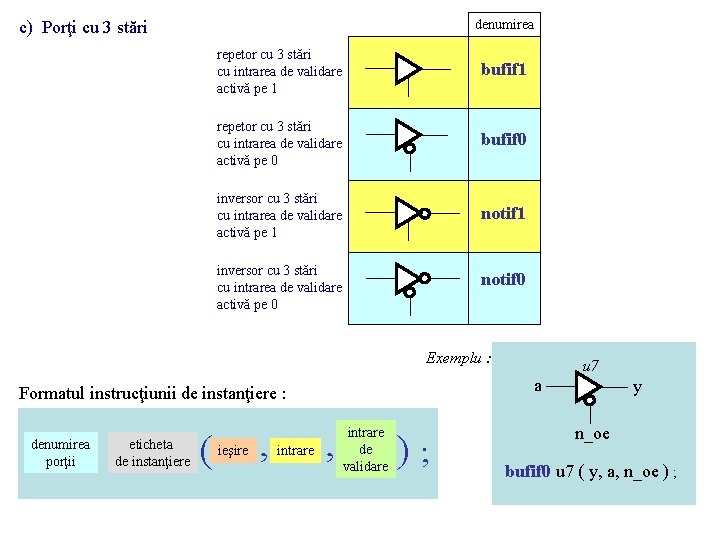

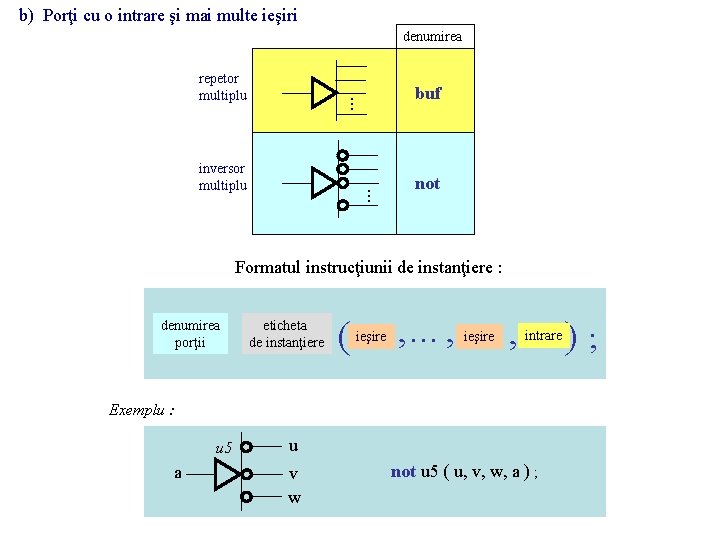

b) Porţi cu o intrare şi mai multe ieşiri denumirea repetor multiplu buf . . . inversor multiplu . . . not Formatul instrucţiunii de instanţiere : denumirea porţii eticheta de instanţiere ( ieşire , . . . , ieşire , intrare Exemplu : u 5 a u v w not u 5 ( u, v, w, a ) ; );

denumirea c) Porţi cu 3 stări repetor cu 3 stări cu intrarea de validare activă pe 1 bufif 1 repetor cu 3 stări cu intrarea de validare activă pe 0 bufif 0 inversor cu 3 stări cu intrarea de validare activă pe 1 notif 1 inversor cu 3 stări cu intrarea de validare activă pe 0 notif 0 Exemplu : a Formatul instrucţiunii de instanţiere : denumirea porţii eticheta de instanţiere ( ieşire , intrare u 7 , intrare de validare ); y n_oe bufif 0 u 7 ( y, a, n_oe ) ;

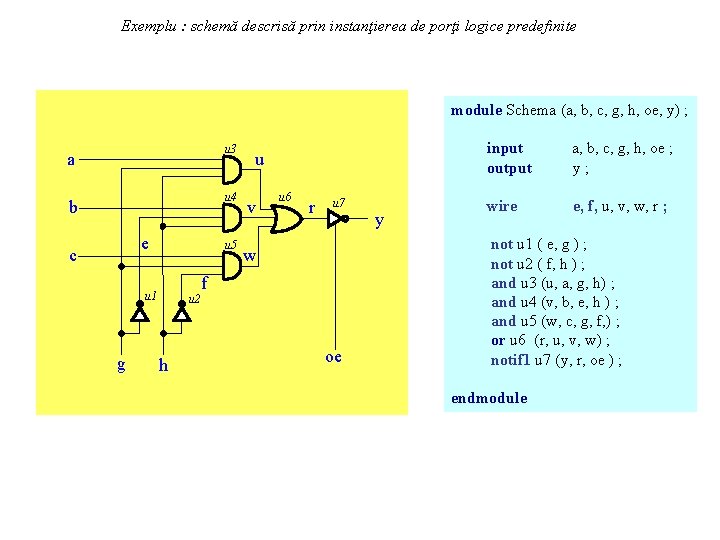

Exemplu : schemă descrisă prin instanţierea de porţi logice predefinite module Schema (a, b, c, g, h, oe, y) ; u 3 a u 4 b e c u 5 v u 6 r u 7 w f u 1 g u u 2 h oe y input output a, b, c, g, h, oe ; y; wire e, f, u, v, w, r ; not u 1 ( e, g ) ; not u 2 ( f, h ) ; and u 3 (u, a, g, h) ; and u 4 (v, b, e, h ) ; and u 5 (w, c, g, f, ) ; or u 6 (r, u, v, w) ; notif 1 u 7 (y, r, oe ) ; endmodule

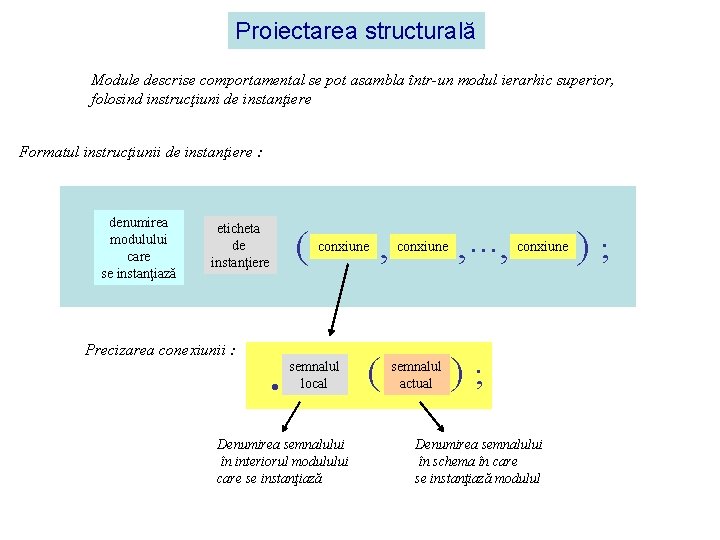

Proiectarea structurală Module descrise comportamental se pot asambla într-un modul ierarhic superior, folosind instrucţiuni de instanţiere Formatul instrucţiunii de instanţiere : denumirea modulului care se instanţiază eticheta de instanţiere Precizarea conexiunii : (. conxiune semnalul local Denumirea semnalului în interiorul modulului care se instanţiază , ( conxiune semnalul actual , . . . , conxiune ); Denumirea semnalului în schema în care se instanţiază modulul );

![Ex module Rg d clk rst load q input 3 0 d Ex : module Rg (d, clk, rst, load, q) ; input [3: 0] d](https://slidetodoc.com/presentation_image_h2/3c3abacaa1cf9722dbad64819ed9aac6/image-18.jpg)

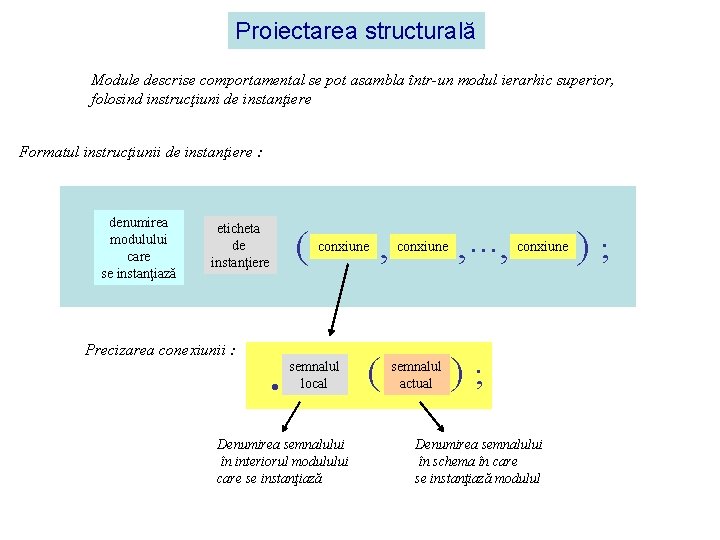

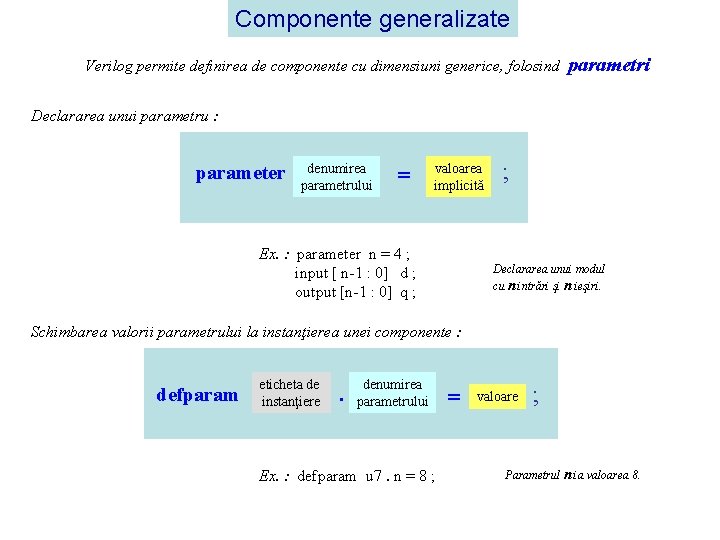

Ex : module Rg (d, clk, rst, load, q) ; input [3: 0] d ; input clk, rst, load ; Rg Rg u 1 u 2 output [3: 0] q ; u 3 TS reg [3: 0] q; v[3: 0] y w[3: 0] Descrie registrul Rg x[3: 0] p[3: 0] d q always @ (posedge clk) a begin oe clk if (rst) q <= 4 b’ 0 ; clock else if (load) q <= d ; rst load endmodule reset module TS (a, y, oe) input[3: 0] a ; load 2 load 1 enable input oe ; Descrie poarta TS output [3: 0] y ; bufif 1 TS (y, a, oe) ; endmodule Schema (x, clock, reset, load 1, load 2, enable, p) ; input [3: 0] x; input clock, reset, load 1, load 2, enable ; output [3: 0] p; wire[3: 0] v, w ; Descrie schema Rg u 1 (. d (x), . clk (clock), . rst (reset), . load (load 1), . q (v) ) ; Rg u 2 (. d (v), . clk (clock), . rst (reset), . load (load 2), . q (w) ) ; TS u 3 (. a (w), . oe (enable), . y (p) ) ; endmodule

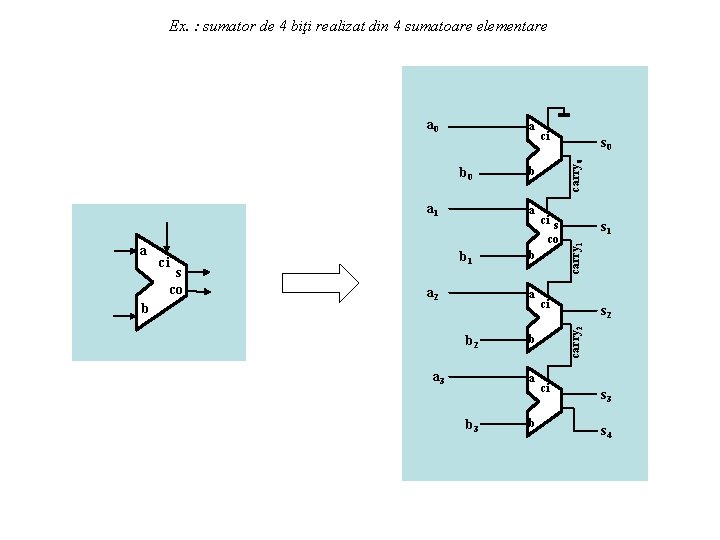

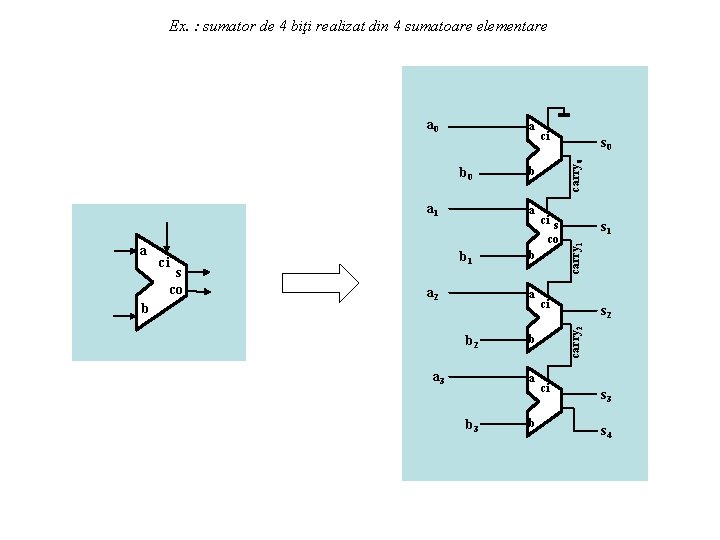

Ex. : sumator de 4 biţi realizat din 4 sumatoare elementare a 1 a b ci s co b a b 1 a 2 b a b 2 a 3 ci s co b a b 3 ci s co b ci s co s 0 carry 0 b 0 ci s co s 1 carry 1 a s 2 carry 2 a 0 s 3 s 4

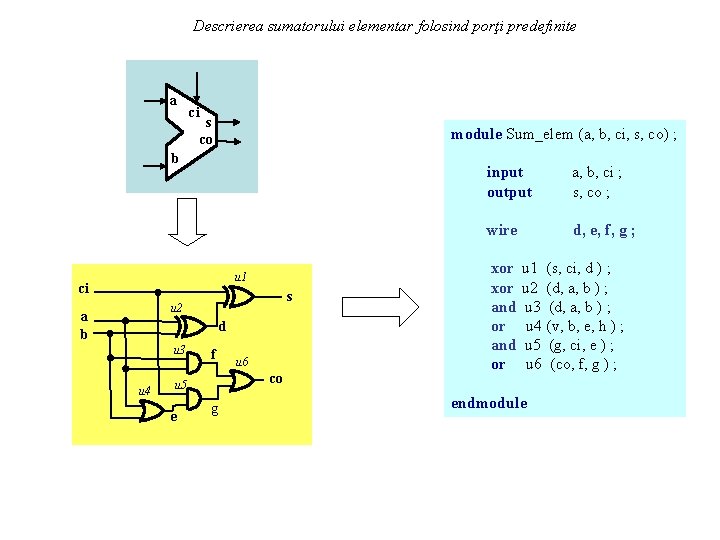

Descrierea sumatorului elementar folosind porţi predefinite a ci s co module Sum_elem (a, b, ci, s, co) ; b u 1 ci s u 2 a b d u 3 u 4 f co u 5 e u 6 g input output a, b, ci ; s, co ; wire d, e, f, g ; xor and or u 1 (s, ci, d ) ; u 2 (d, a, b ) ; u 3 (d, a, b ) ; u 4 (v, b, e, h ) ; u 5 (g, ci, e ) ; u 6 (co, f, g ) ; endmodule

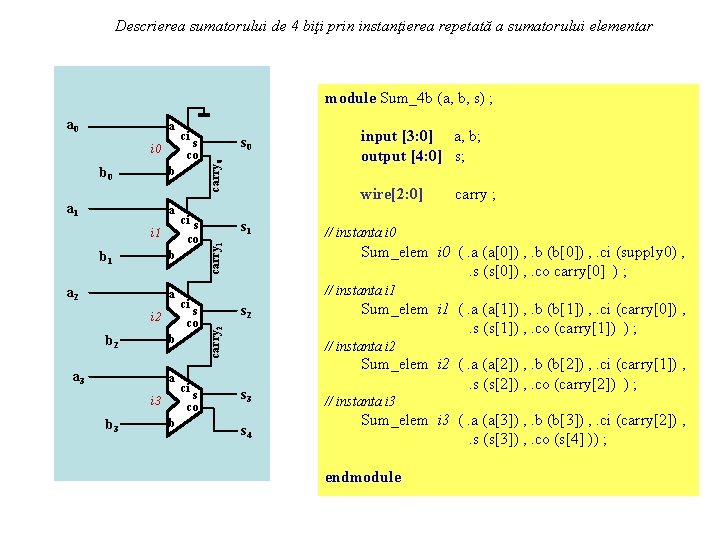

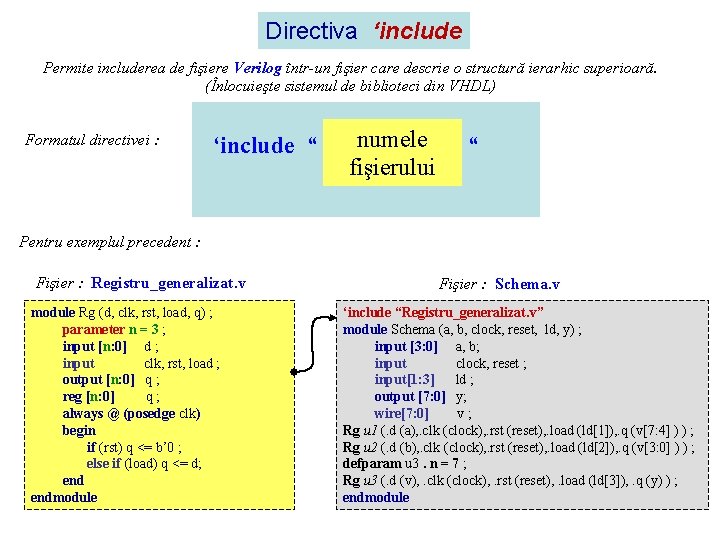

Descrierea sumatorului de 4 biţi prin instanţierea repetată a sumatorului elementar module Sum_4 b (a, b, s) ; b b 0 a 1 a i 1 b b 1 a 2 a i 2 ci s co b b 2 a 3 a i 3 b 3 ci s co b ci s co s 0 carry 0 i 0 ci s co input [3: 0] a, b; output [4: 0] s; wire[2: 0] s 1 carry 1 a carry ; // instanta i 0 Sum_elem i 0 (. a (a[0]) , . b (b[0]) , . ci (supply 0) , . s (s[0]) , . co carry[0] ) ; // instanta i 1 s 2 carry 2 a 0 Sum_elem i 1 (. a (a[1]) , . b (b[1]) , . ci (carry[0]) , . s (s[1]) , . co (carry[1]) ) ; // instanta i 2 s 3 s 4 Sum_elem i 2 (. a (a[2]) , . b (b[2]) , . ci (carry[1]) , . s (s[2]) , . co (carry[2]) ) ; // instanta i 3 Sum_elem i 3 (. a (a[3]) , . b (b[3]) , . ci (carry[2]) , . s (s[3]) , . co (s[4] )) ; endmodule

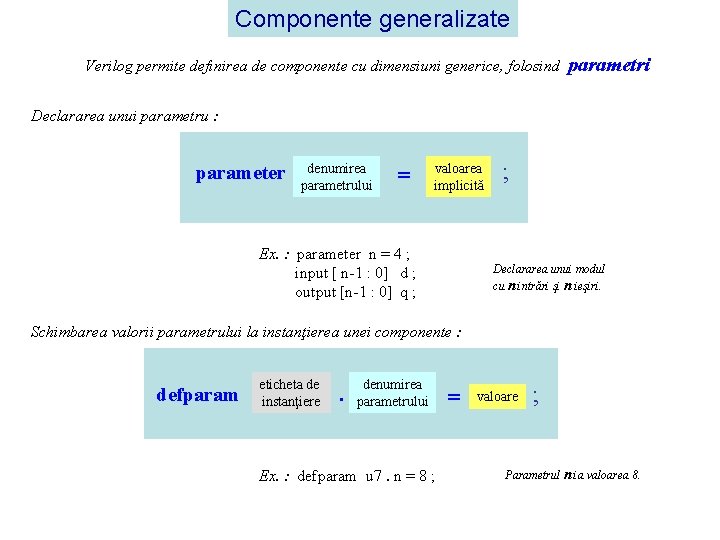

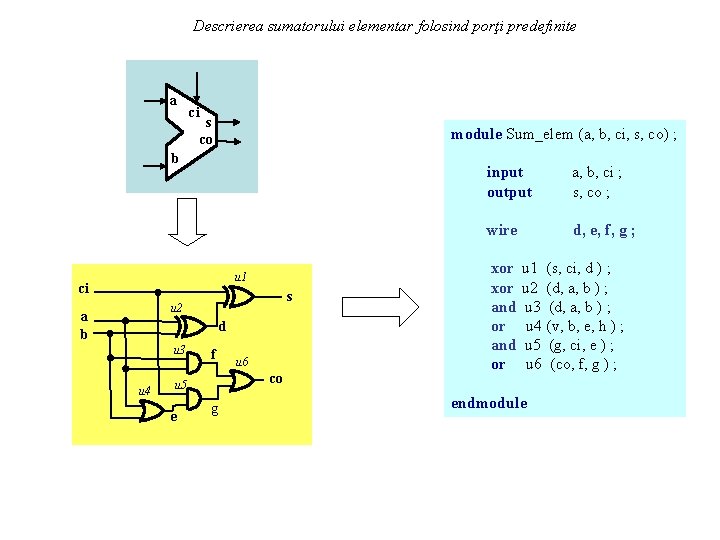

Componente generalizate Verilog permite definirea de componente cu dimensiuni generice, folosind parametri Declararea unui parametru : parameter denumirea parametrului = valoarea implicită Ex. : parameter n = 4 ; input [ n-1 : 0] d ; output [n-1 : 0] q ; ; Declararea unui modul cu n intrări şi n ieşiri. Schimbarea valorii parametrului la instanţierea unei componente : defparam eticheta de instanţiere . denumirea parametrului Ex. : defparam u 7. n = 8 ; = valoare ; Parametrul n ia valoarea 8.

![Rg u 1 a3 0 d v7 4 q Rg u 3 clk rst Rg u 1 a[3: 0] d v[7: 4] q Rg u 3 clk rst](https://slidetodoc.com/presentation_image_h2/3c3abacaa1cf9722dbad64819ed9aac6/image-23.jpg)

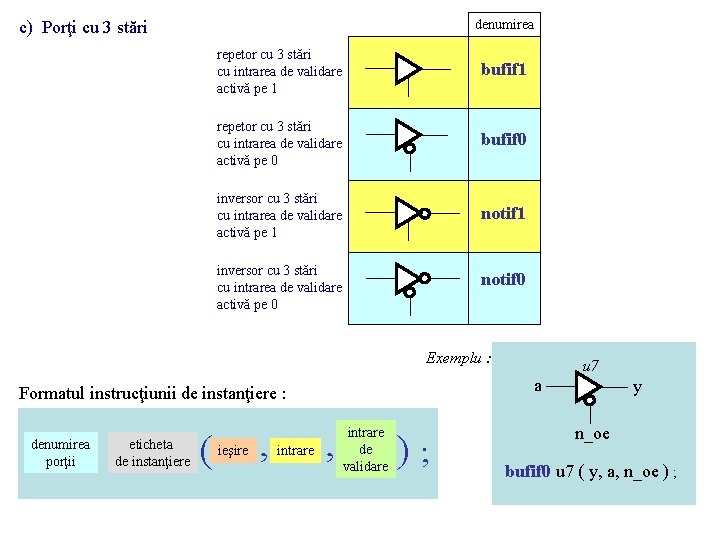

Rg u 1 a[3: 0] d v[7: 4] q Rg u 3 clk rst load v[7: 0] d y[7: 0] q Rg u 2 clk b[3: 0] d q v[3: 0] clk rst load clock reset ld 1 ld 2 ld[1: 3] ld 3 module Rg (d, clk, rst, load, q) ; parameter n = 3 ; input [n: 0] d ; input clk, rst, load ; output [n: 0] q ; reg [n: 0] q; always @ (posedge clk) begin if (rst) q <= b’ 0 ; else if (load) q <= d; endmodule Descrie registrul generalizat Rg Descrie schema module Schema (a, b, clock, reset, ld, y) ; input [3: 0] a, b; input clock, reset ; input[1: 3] ld ; output [7: 0] y; p[3: 0] wire[7: 0] v; Rg u 1 (. d (a), . clk (clock), . rst (reset), . load (ld[1]), . q (v[7: 4] ) ) ; Rg u 2 (. d (b), . clk (clock), . rst (reset), . load (ld[2]), . q (v[3: 0] ) ) ; defparam u 3. n = 7 ; Rg u 3 (. d (v), . clk (clock), . rst (reset), . load (ld[3]), . q (y) ) ; endmodule

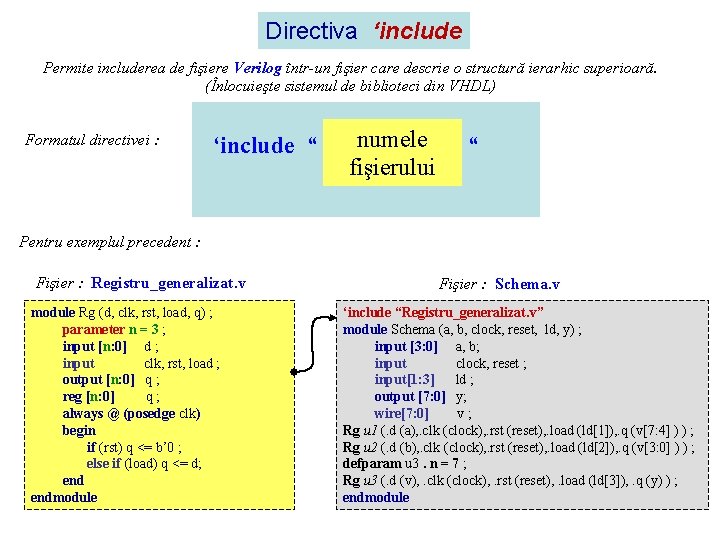

Directiva ‘include Permite includerea de fişiere Verilog într-un fişier care descrie o structură ierarhic superioară. (Înlocuieşte sistemul de biblioteci din VHDL) Formatul directivei : ‘include “ numele fişierului “ Pentru exemplul precedent : Fişier : Registru_generalizat. v module Rg (d, clk, rst, load, q) ; parameter n = 3 ; input [n: 0] d ; input clk, rst, load ; output [n: 0] q ; reg [n: 0] q; always @ (posedge clk) begin if (rst) q <= b’ 0 ; else if (load) q <= d; endmodule Fişier : Schema. v ‘include “Registru_generalizat. v” module Schema (a, b, clock, reset, ld, y) ; input [3: 0] a, b; input clock, reset ; input[1: 3] ld ; output [7: 0] y; wire[7: 0] v; Rg u 1 (. d (a), . clk (clock), . rst (reset), . load (ld[1]), . q (v[7: 4] ) ) ; Rg u 2 (. d (b), . clk (clock), . rst (reset), . load (ld[2]), . q (v[3: 0] ) ) ; defparam u 3. n = 7 ; Rg u 3 (. d (v), . clk (clock), . rst (reset), . load (ld[3]), . q (y) ) ; endmodule

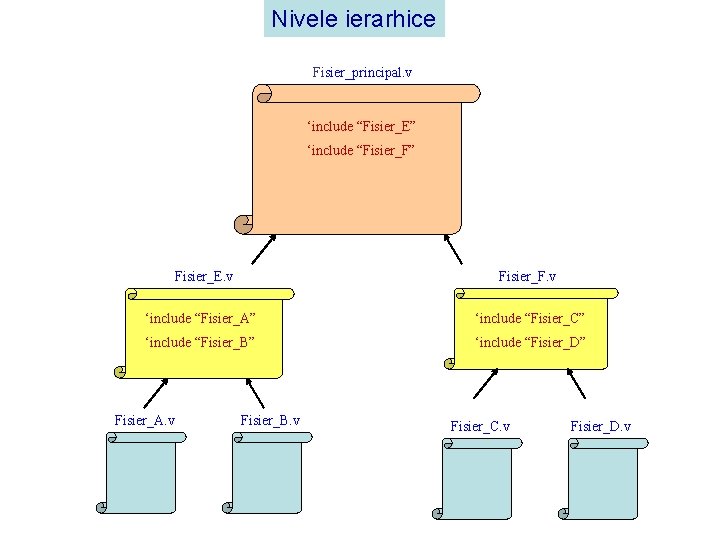

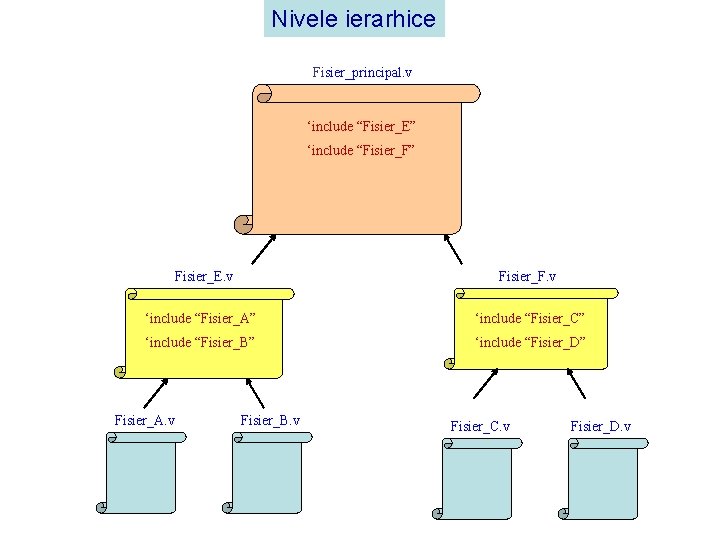

Nivele ierarhice Fisier_principal. v ‘include “Fisier_E” ‘include “Fisier_F” Fisier_E. v Fisier_F. v ‘include “Fisier_A” ‘include “Fisier_C” ‘include “Fisier_B” ‘include “Fisier_D” Fisier_A. v Fisier_B. v Fisier_C. v Fisier_D. v