Department of Computer and Information Science School of

- Slides: 24

Department of Computer and Information Science, School of Science, IUPUI CSCI 230 Information Representation: Machine Instructions Dale Roberts, Lecturer IUPUI droberts@cs. iupui. edu Dale Roberts

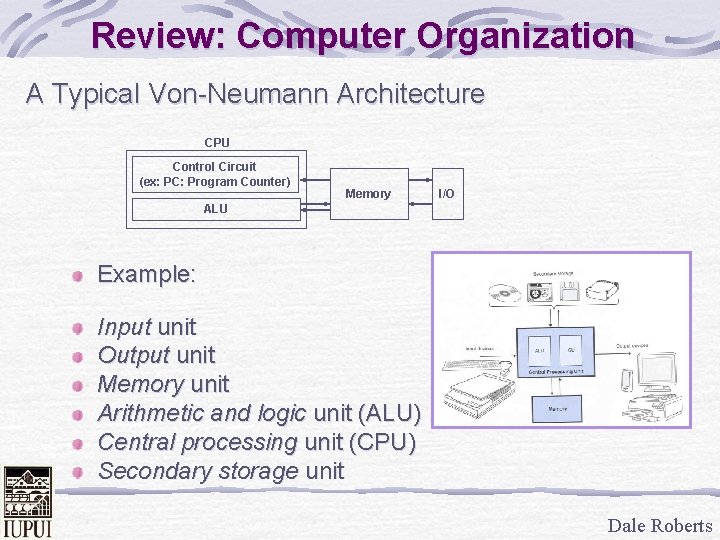

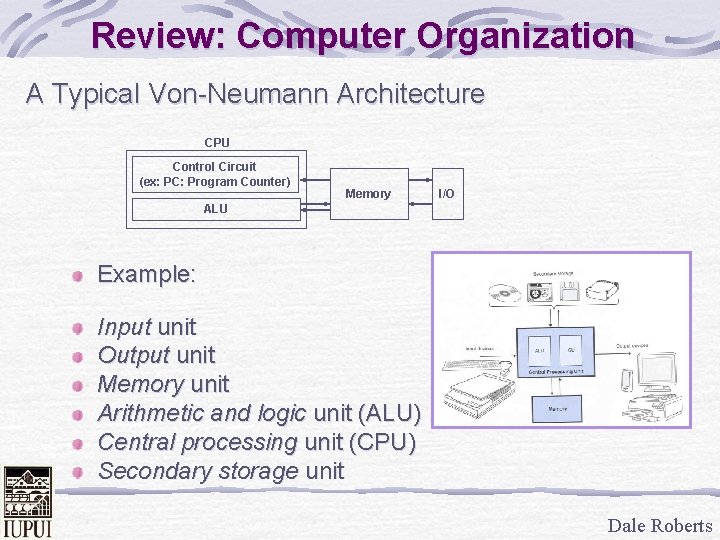

Review: Computer Organization A Typical Von-Neumann Architecture CPU Control Circuit (ex: PC: Program Counter) Memory I/O ALU Example: Input unit Output unit Memory unit Arithmetic and logic unit (ALU) Central processing unit (CPU) Secondary storage unit Dale Roberts

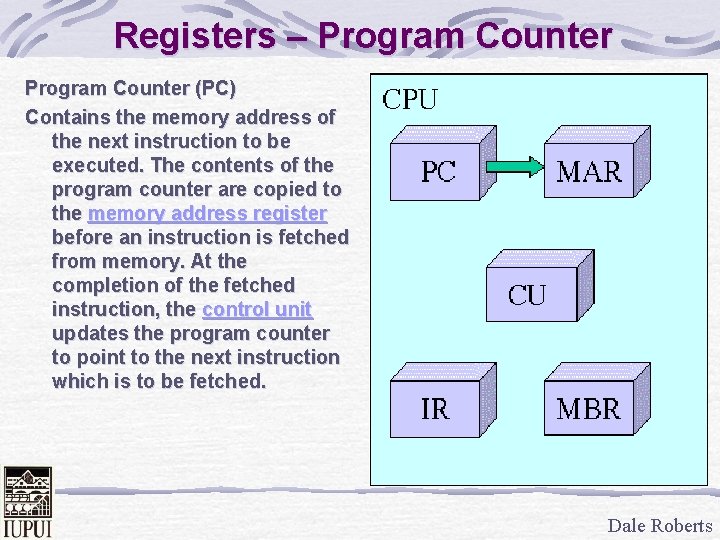

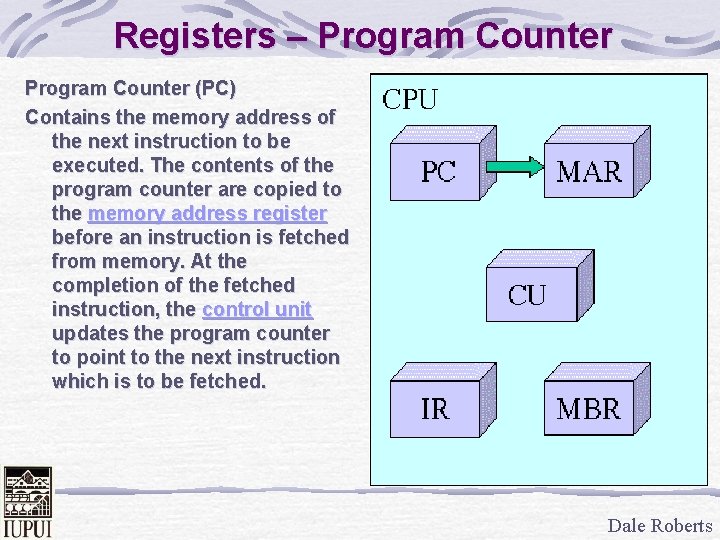

Registers – Program Counter (PC) Contains the memory address of the next instruction to be executed. The contents of the program counter are copied to the memory address register before an instruction is fetched from memory. At the completion of the fetched instruction, the control unit updates the program counter to point to the next instruction which is to be fetched. Dale Roberts

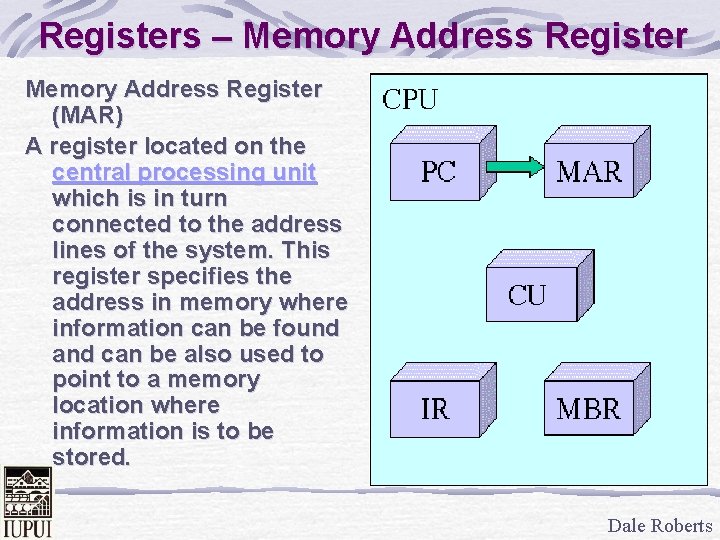

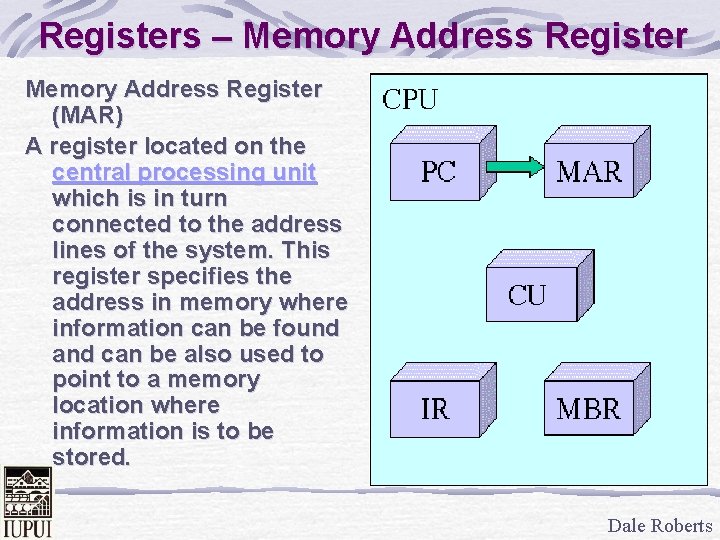

Registers – Memory Address Register (MAR) A register located on the central processing unit which is in turn connected to the address lines of the system. This register specifies the address in memory where information can be found and can be also used to point to a memory location where information is to be stored. Dale Roberts

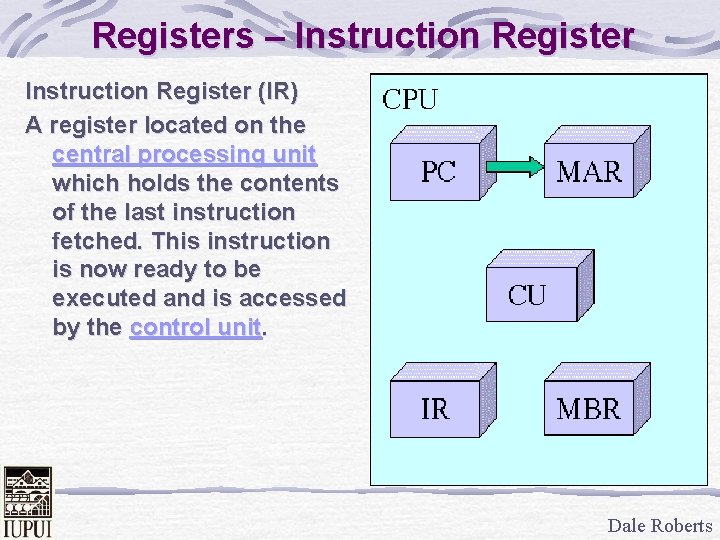

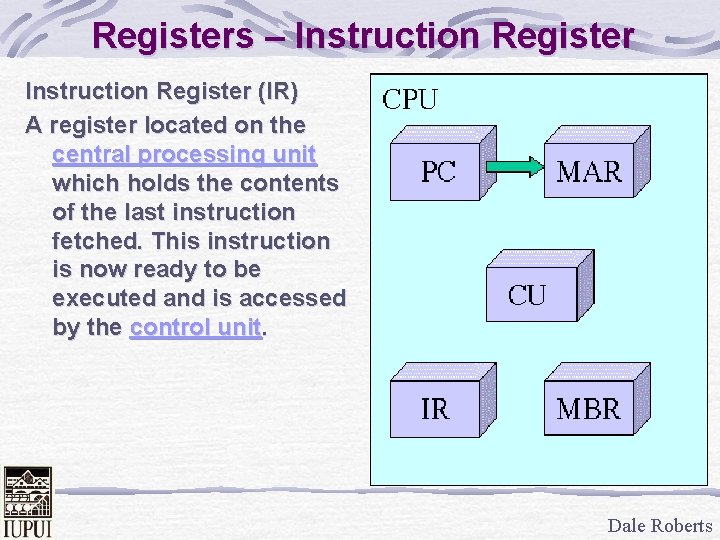

Registers – Instruction Register (IR) A register located on the central processing unit which holds the contents of the last instruction fetched. This instruction is now ready to be executed and is accessed by the control unit. Dale Roberts

IR Structure The Instruction Register typically has a structure that includes operation code and an optional operand. Everyone calles the operation code an “Opcode” It is up to the manufacturer to determine how many bits comprise an instruction, and which bits store the opcode and operand. Dale Roberts

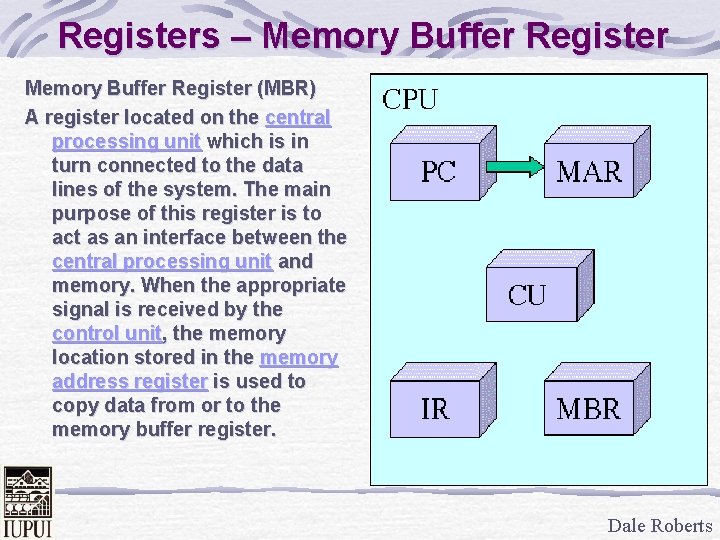

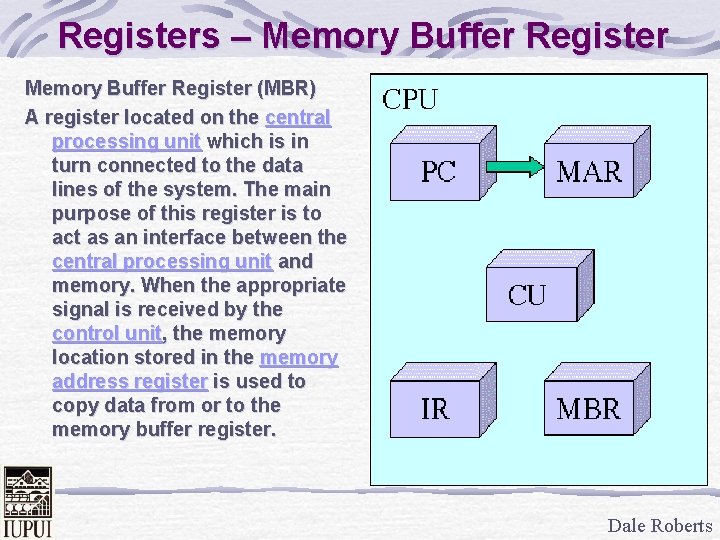

Registers – Memory Buffer Register (MBR) A register located on the central processing unit which is in turn connected to the data lines of the system. The main purpose of this register is to act as an interface between the central processing unit and memory. When the appropriate signal is received by the control unit, the memory location stored in the memory address register is used to copy data from or to the memory buffer register. Dale Roberts

Registers - Accumulator (ACC) A register located on the central processing unit. The contents can be used by the arithmetic-logic unit for arithmetic and logic operations, and by the memory buffer register. Usually, all results generated by the arithmetic-logic unit end up in the accumulator. Dale Roberts

Arithmetic Logic Unit Arithmetic-Logic Unit (ALU) Performs arithmetic operations such as addition and subtraction as well as logical operations such as AND, OR and NOT. Most operations require two operands. One of these operands usually comes from memory via the memory buffer register, while the other is the previously loaded value stored in the accumulator. The results of an arithmetic-logic unit operation is usually transfered to the accumulator. Dale Roberts

Memory is made up of a series of zero's (0) and one's (1) called bits or binary. These individual bits are grouped together in lots of eight and are referred to as a byte. Every byte in memory can be accessed by a unique address which identifies its location. The memory in modern computers contains millions of bytes and is often referred to as random-access memory (RAM). Memory interacts with the MAR and MBR to read and write values from memory via a bus. Dale Roberts

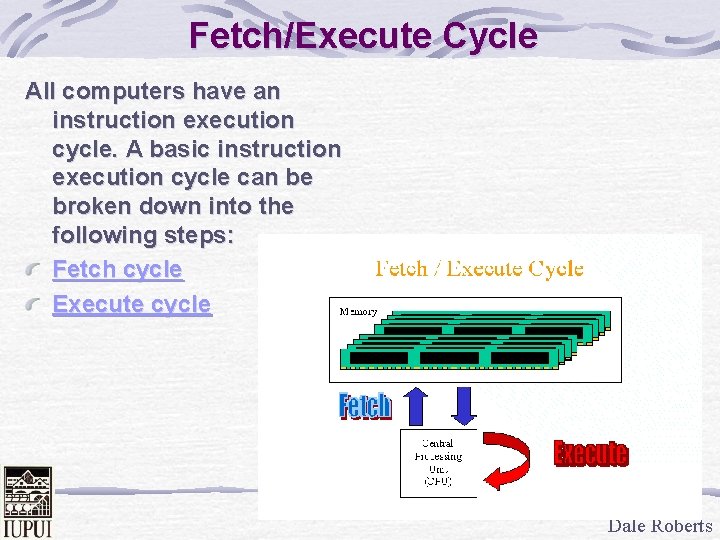

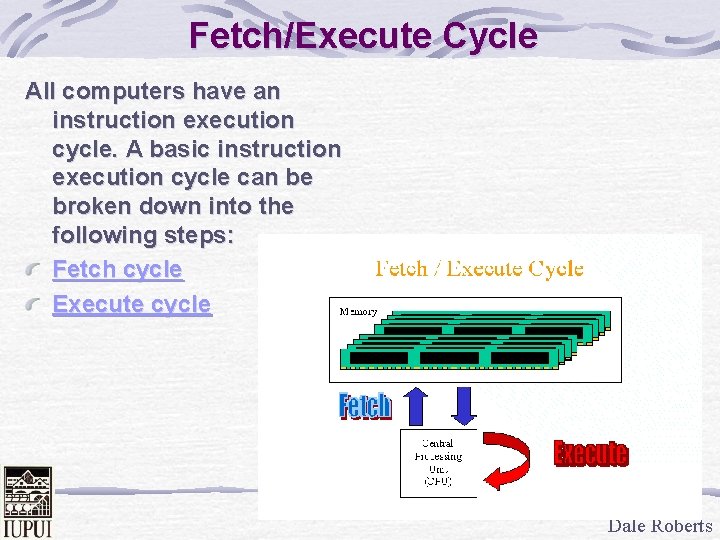

Fetch/Execute Cycle All computers have an instruction execution cycle. A basic instruction execution cycle can be broken down into the following steps: Fetch cycle Execute cycle Dale Roberts

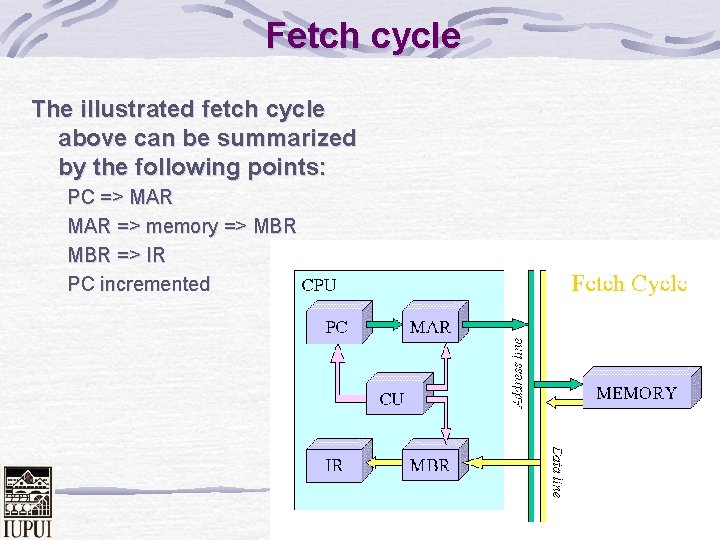

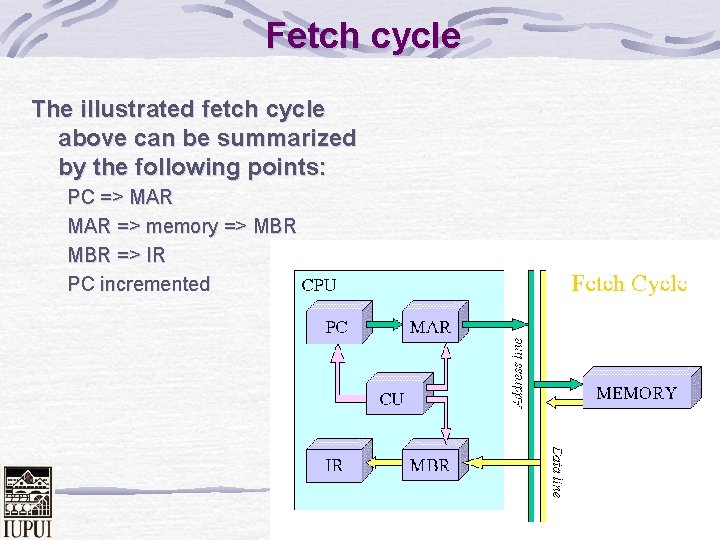

Fetch cycle The illustrated fetch cycle above can be summarized by the following points: PC => MAR => memory => MBR => IR PC incremented Dale Roberts

Execute Cycle After the CPU has finished fetching an instruction, the CU checks the contents of the IR and determines which type of execution is to be carried out next. This process is known as the decoding phase. The instruction is now ready for the execution cycle. Dale Roberts

Types of Opcodes The actions within the execution cycle can be categorized into the following four groups: CPU - Memory: Data may be transferred from memory to the CPU or from the CPU to memory. CPU - I/O: Data may be transferred from an I/O module to the CPU or from the CPU to an I/O module. Data Processing: The CPU may perform some arithmetic or logic operation on data via the arithmetic-logic unit (ALU). Control: An instruction may specify that the sequence of operation may be altered. For example, the program counter (PC) may be updated with a new memory address to reflect that the next instruction fetched, should be read from this new location. Dale Roberts

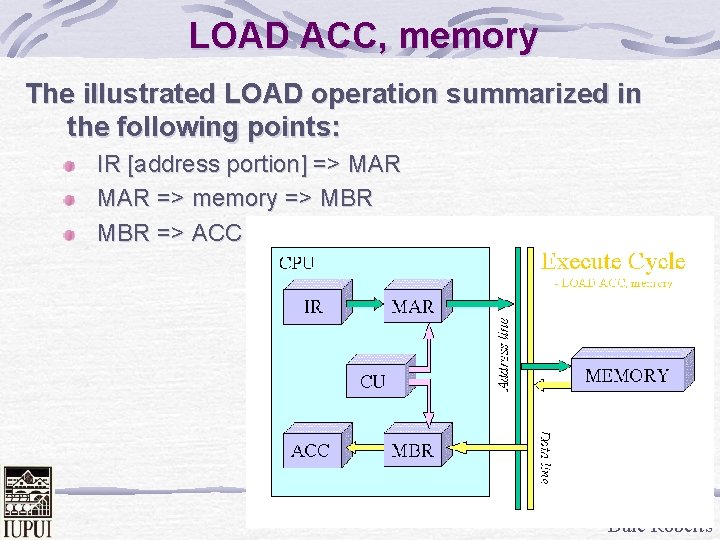

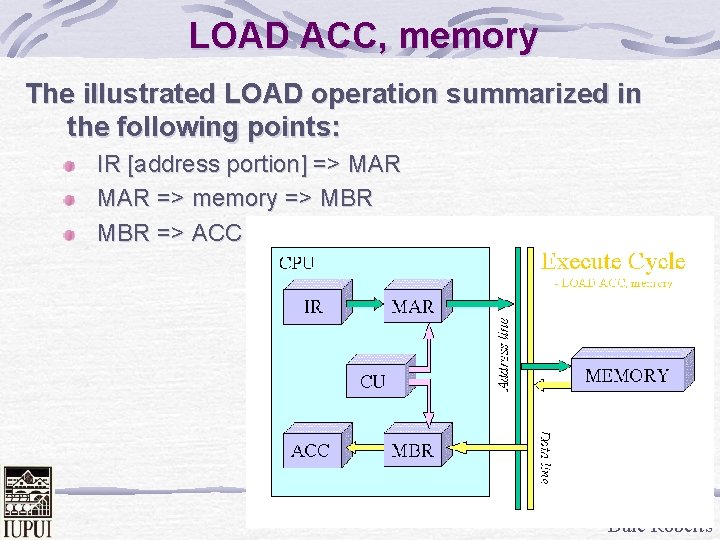

LOAD ACC, memory The illustrated LOAD operation summarized in the following points: IR [address portion] => MAR => memory => MBR => ACC Dale Roberts

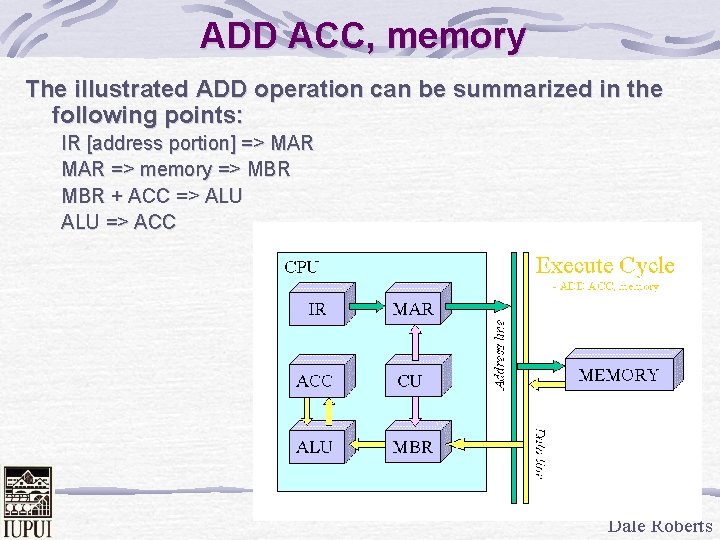

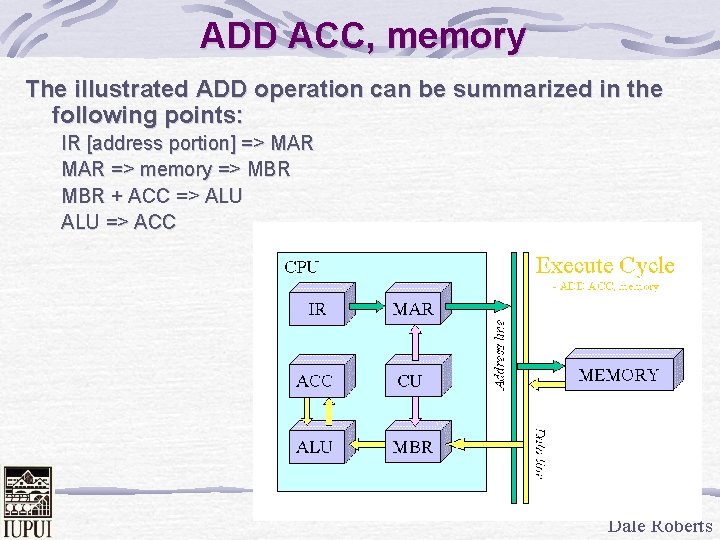

ADD ACC, memory The illustrated ADD operation can be summarized in the following points: IR [address portion] => MAR => memory => MBR + ACC => ALU => ACC Dale Roberts

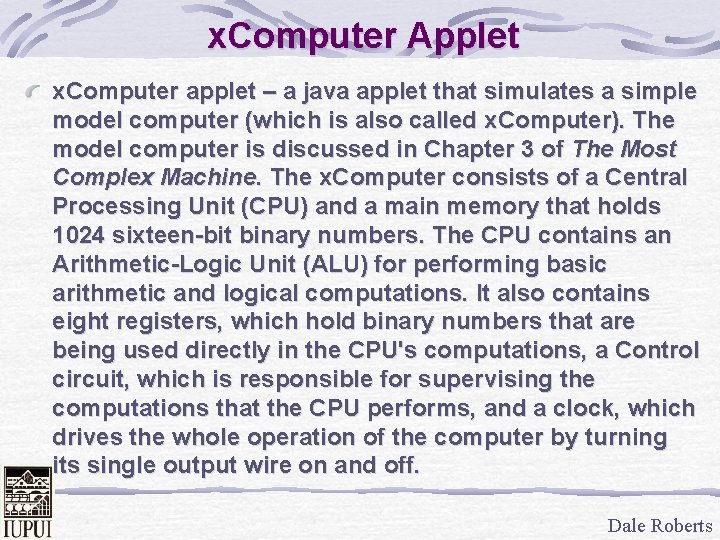

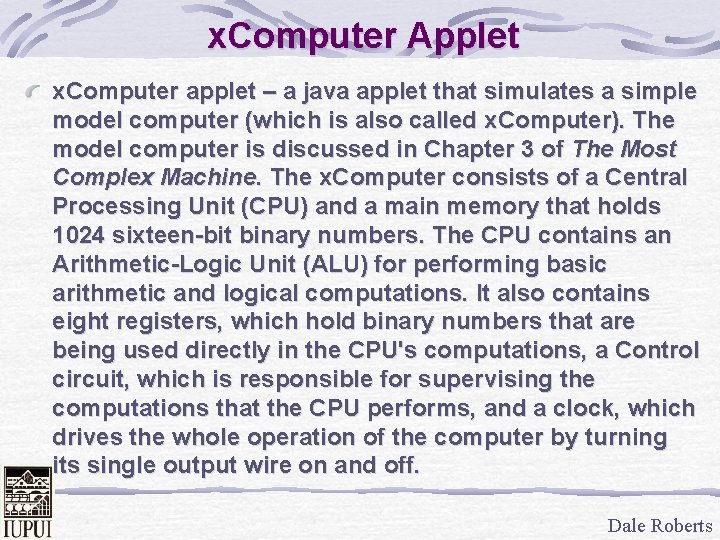

x. Computer Applet x. Computer applet – a java applet that simulates a simple model computer (which is also called x. Computer). The model computer is discussed in Chapter 3 of The Most Complex Machine. The x. Computer consists of a Central Processing Unit (CPU) and a main memory that holds 1024 sixteen-bit binary numbers. The CPU contains an Arithmetic-Logic Unit (ALU) for performing basic arithmetic and logical computations. It also contains eight registers, which hold binary numbers that are being used directly in the CPU's computations, a Control circuit, which is responsible for supervising the computations that the CPU performs, and a clock, which drives the whole operation of the computer by turning its single output wire on and off. Dale Roberts

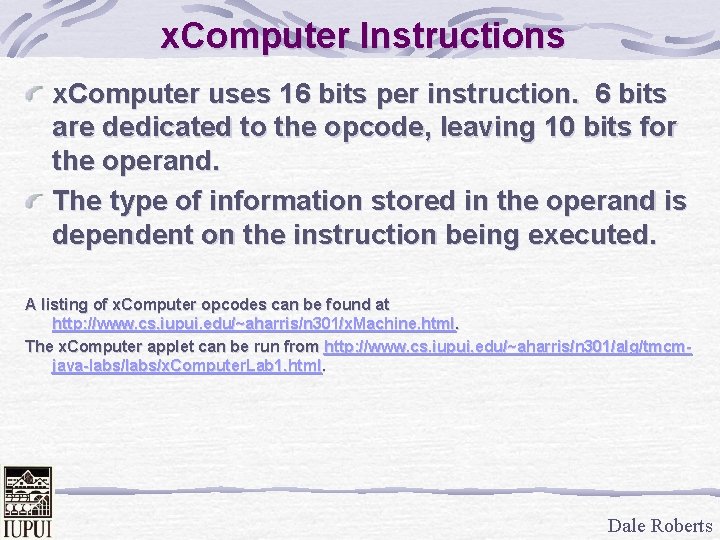

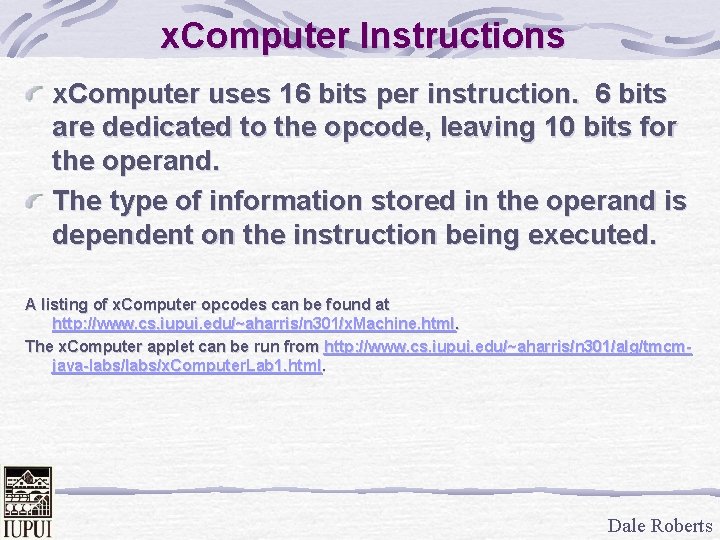

x. Computer Instructions x. Computer uses 16 bits per instruction. 6 bits are dedicated to the opcode, leaving 10 bits for the operand. The type of information stored in the operand is dependent on the instruction being executed. A listing of x. Computer opcodes can be found at http: //www. cs. iupui. edu/~aharris/n 301/x. Machine. html. The x. Computer applet can be run from http: //www. cs. iupui. edu/~aharris/n 301/alg/tmcmjava-labs/x. Computer. Lab 1. html. Dale Roberts

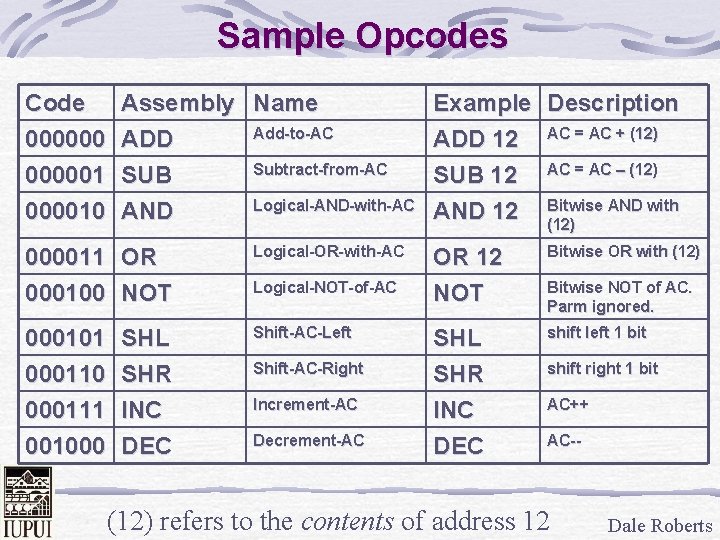

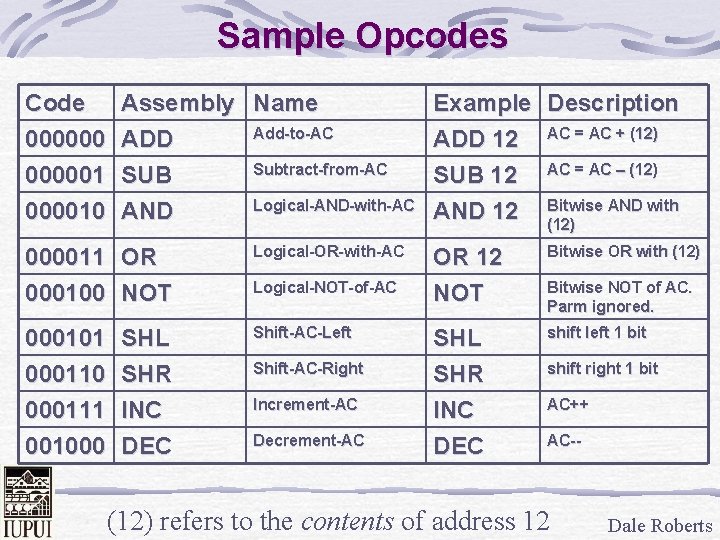

Sample Opcodes Code 0000001 000010 Assembly Name Add-to-AC ADD Subtract-from-AC SUB Logical-AND-with-AC AND 000011 OR 000100 NOT Logical-OR-with-AC 000101 000110 000111 001000 Shift-AC-Left SHL SHR INC DEC Logical-NOT-of-AC Shift-AC-Right Increment-AC Decrement-AC Example Description ADD 12 AC = AC + (12) SUB 12 AC = AC – (12) AND with AND 12 Bitwise (12) OR 12 NOT Bitwise OR with (12) SHL SHR INC DEC shift left 1 bit Bitwise NOT of AC. Parm ignored. shift right 1 bit AC++ AC-- (12) refers to the contents of address 12 Dale Roberts

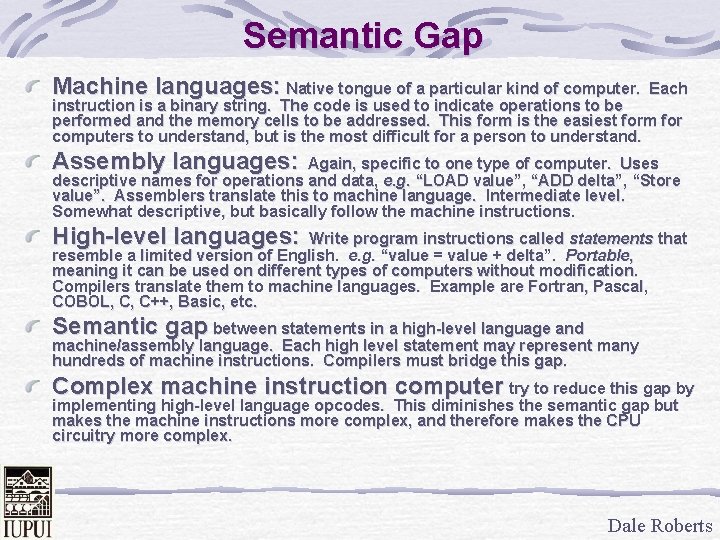

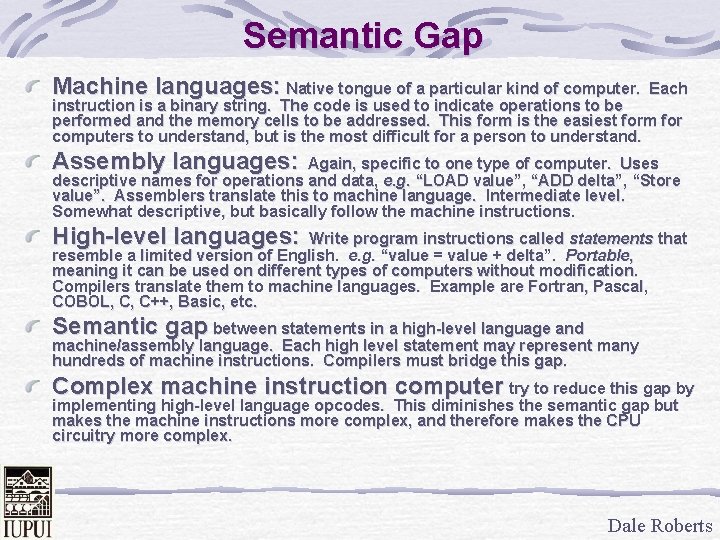

Semantic Gap Machine languages: Native tongue of a particular kind of computer. Each instruction is a binary string. The code is used to indicate operations to be performed and the memory cells to be addressed. This form is the easiest form for computers to understand, but is the most difficult for a person to understand. Assembly languages: Again, specific to one type of computer. Uses descriptive names for operations and data, e. g. “LOAD value”, “ADD delta”, “Store value”. Assemblers translate this to machine language. Intermediate level. Somewhat descriptive, but basically follow the machine instructions. High-level languages: Write program instructions called statements that resemble a limited version of English. e. g. “value = value + delta”. Portable, meaning it can be used on different types of computers without modification. Compilers translate them to machine languages. Example are Fortran, Pascal, COBOL, C, C++, Basic, etc. Semantic gap between statements in a high-level language and machine/assembly language. Each high level statement may represent many hundreds of machine instructions. Compilers must bridge this gap. Complex machine instruction computer try to reduce this gap by implementing high-level language opcodes. This diminishes the semantic gap but makes the machine instructions more complex, and therefore makes the CPU circuitry more complex. Dale Roberts

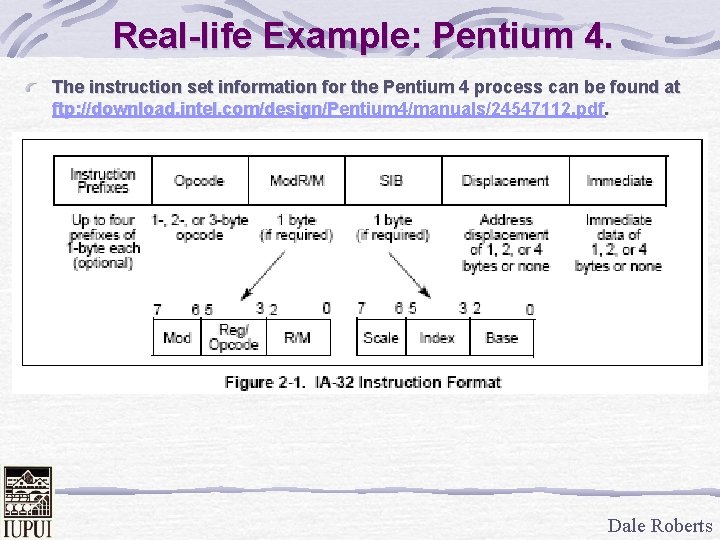

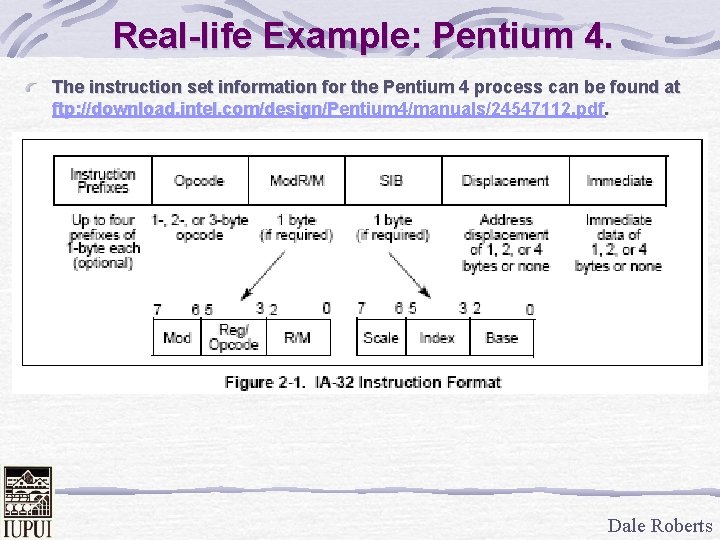

Real-life Example: Pentium 4. The instruction set information for the Pentium 4 process can be found at ftp: //download. intel. com/design/Pentium 4/manuals/24547112. pdf. Dale Roberts

Pentium 4 ADD Description Adds the first operand (destination operand) and the second operand (source operand) and stores the result in the destination operand. The destination operand can be a register or a memory location; the source operand can be an immediate, a register, or a memory location. (However, two memory operands cannot be used in one instruction. ) When an immediate value is used as an operand, it is sign-extended to the length of the destination operand format. The ADD instruction performs integer addition. It evaluates the result for both signed and unsigned integer operands and sets the OF and CF flags to indicate a carry (overflow) in the signed or unsigned result, respectively. The SF flag indicates the sign of the signed result. This instruction can be used with a LOCK prefix to allow the instruction to be executed atomically. Operation DEST ← DEST + SRC; So you can see that the instructions are a little more complicated in real life than in x. Computer. But the same principles apply. Dale Roberts

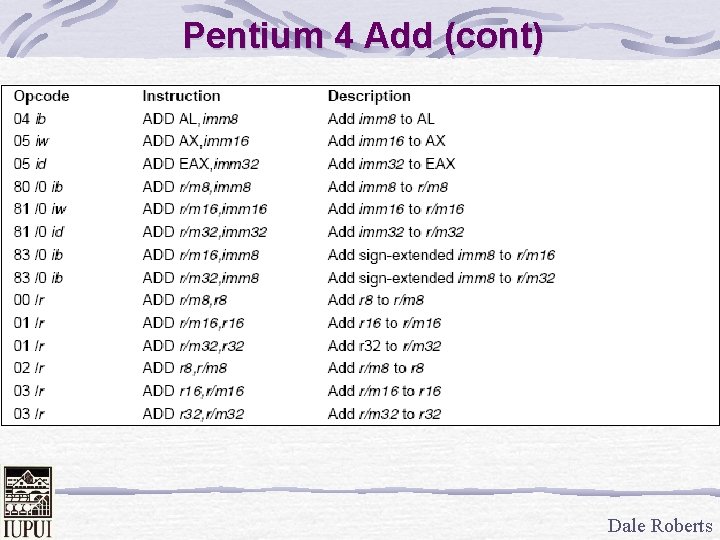

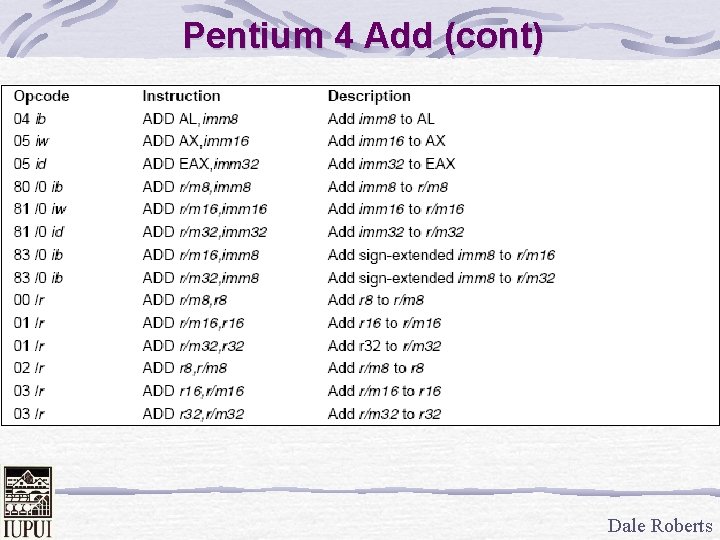

Pentium 4 Add (cont) Dale Roberts

Acknowledgements Several graphics and terms were obtained from Jonathan Michael Auld Central Queensland University. x. Computer and its machine instructions were developed by David Eck. Dale Roberts