Delays in Verilog Programmable Logic Design 40 493

Delays in Verilog Programmable Logic Design (40 -493) Fall 2001 Computer Engineering Department Sharif University of Technology Maziar Gudarzi

Introduction n Delays are crucial in REAL simulations Post-synthesis simulation n Post-layout simulation n n FPGA counter-part: Post-P&R simulation n Delay Models Represent different physical concepts n Two most-famous models n Inertial delay n Transport delay n

Delay Models Delays in Verilog

Delay Models Inertial Delay n The inertia of a circuit node to change value n Abstractly models the RC circuit seen at the node n Different types Input inertial delay n Output inertial delay n

Delay Models Transport Delay n Represents the propagation time of signals from module inputs to its outputs n Models the internal propagation delays of electrical elements

Delay Types Delays in Verilog

Delay Types n Rise Delay n Fall Delay n Turn-Off Delay n Min/Typ/Max Delay values

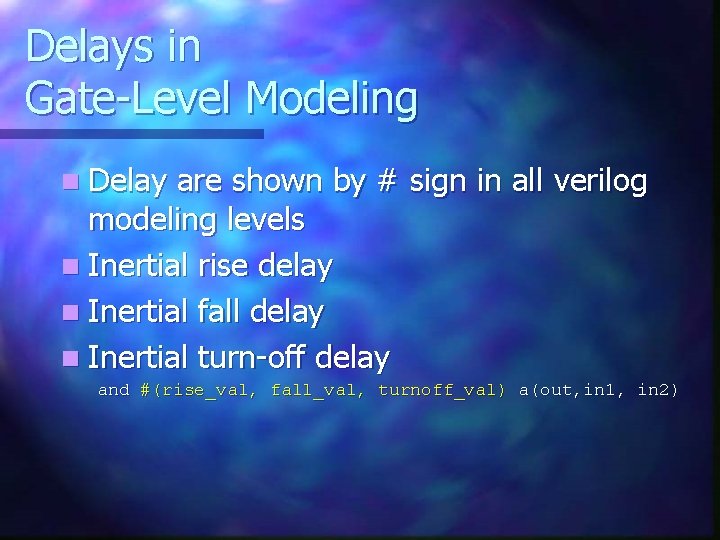

Delays in Gate-Level Modeling Delays in Verilog

Delays in Gate-Level Modeling n Delay are shown by # sign in all verilog modeling levels n Inertial rise delay n Inertial fall delay n Inertial turn-off delay and #(rise_val, fall_val, turnoff_val) a(out, in 1, in 2)

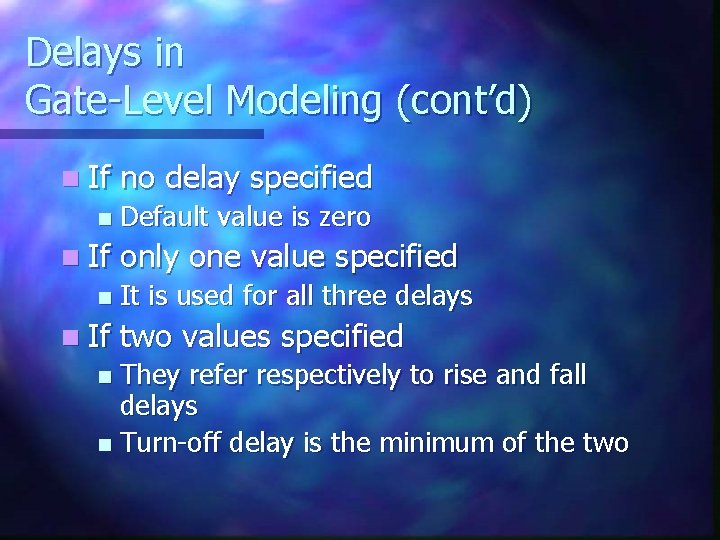

Delays in Gate-Level Modeling (cont’d) n If no delay specified n Default value is zero n If n n If only one value specified It is used for all three delays two values specified They refer respectively to rise and fall delays n Turn-off delay is the minimum of the two n

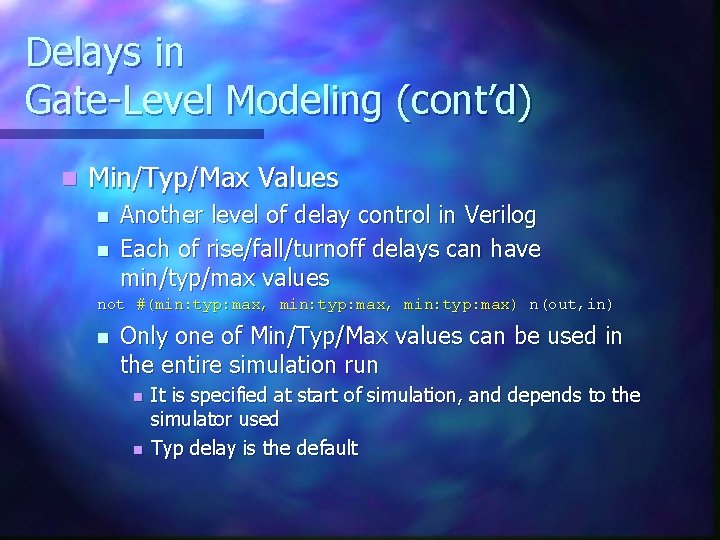

Delays in Gate-Level Modeling (cont’d) n Min/Typ/Max Values n n Another level of delay control in Verilog Each of rise/fall/turnoff delays can have min/typ/max values not #(min: typ: max, min: typ: max) n(out, in) n Only one of Min/Typ/Max values can be used in the entire simulation run n n It is specified at start of simulation, and depends to the simulator used Typ delay is the default

Delays in Dataflow Modeling Delays in Verilog

Delays in Dataflow Modeling n Regular Assignment Delays assign #delay out = in 1 & in 2; n As in Gate-Level Modeling the delay is output-inertial delay

Delays in Dataflow Modeling (cont’d) n Implicit Continuous Assignment Delay wire #delay out = in 1 & in 2;

Delays in Behavioral Modeling Delays in Verilog

Delay in Behavioral Modeling

Today Summary n Delays n Models n n Inertial/Transport Types Rise/Fall/Turn-off n Min/Typ/Max Values n n Delays in Verilog Gate-Level Modeling n Dataflow Modeling n Behavioral Modeling n

Complementary Notes n Assignment n 6 Chapter 8: All 6 Exercises with Model. Sim (submit the Verilog source codes to ce 493@ce. sharif. edu) n Design appropriate test-benches to exhaustively test the results and report the errors n Due date: Saturday, Day 15 th n n Lab. Final Project Announce your group members today n Start your work n

Complementary Notes (cont’d) n Don’t forget to subscribe to course mailing list: ce 493 list

- Slides: 19