Delay Modeling Have already seen where gate propagation

- Slides: 30

Delay Modeling • Have already seen where gate propagation delay is a function of Þ input slew rate ÞOutput capacitance load • Output slew rate is also function of input slew rate, output load • Can calculate propagation delay, output slew via either table lookup or direct calculation ÞTable lookup fast, but to get good accuracy may need lots of data points (input slew axis * output load axis * environment) ÞDelay modeling can reduce data needed, but can be inaccurate 9/18/2020

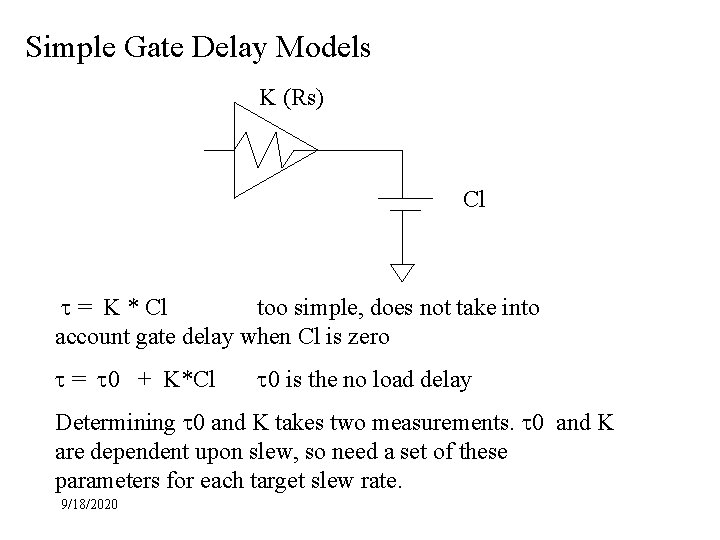

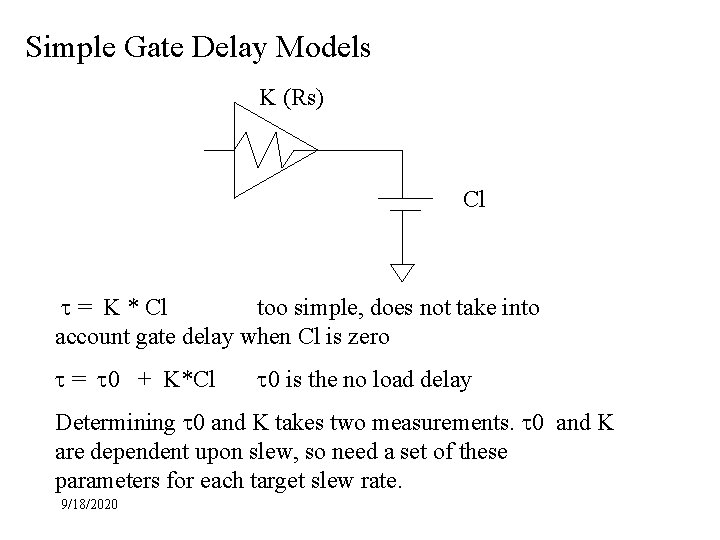

Simple Gate Delay Models K (Rs) Cl t = K * Cl too simple, does not take into account gate delay when Cl is zero t = t 0 + K*Cl t 0 is the no load delay Determining t 0 and K takes two measurements. t 0 and K are dependent upon slew, so need a set of these parameters for each target slew rate. 9/18/2020

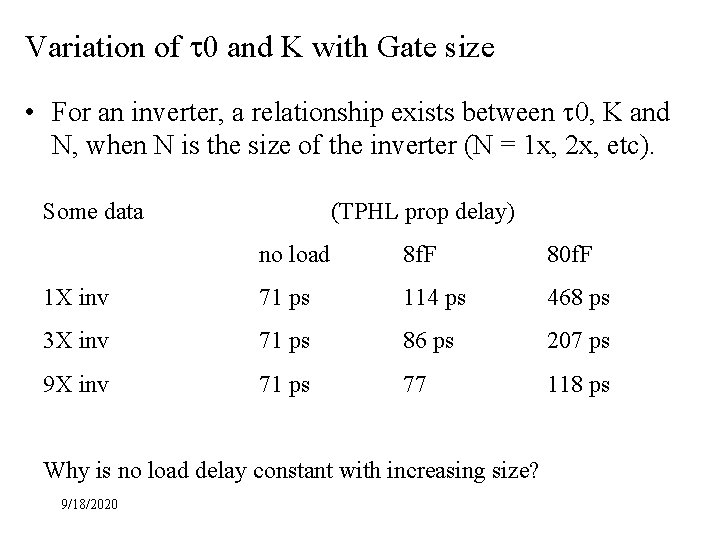

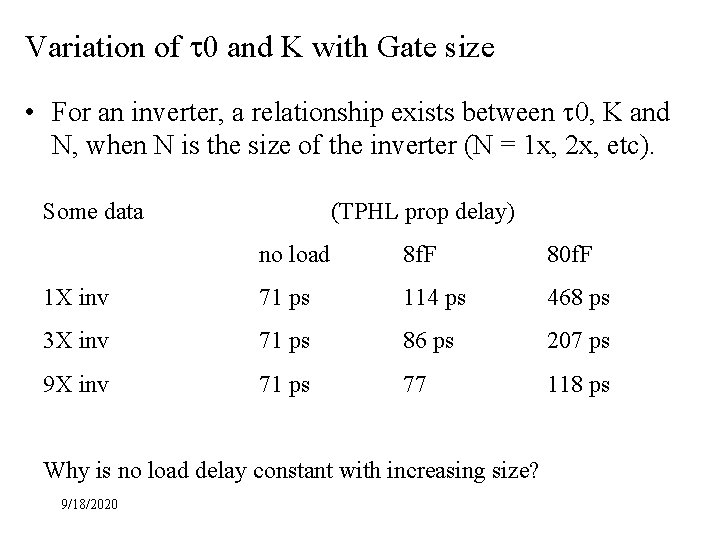

Variation of t 0 and K with Gate size • For an inverter, a relationship exists between t 0, K and N, when N is the size of the inverter (N = 1 x, 2 x, etc). Some data (TPHL prop delay) no load 8 f. F 80 f. F 1 X inv 71 ps 114 ps 468 ps 3 X inv 71 ps 86 ps 207 ps 9 X inv 71 ps 77 118 ps Why is no load delay constant with increasing size? 9/18/2020

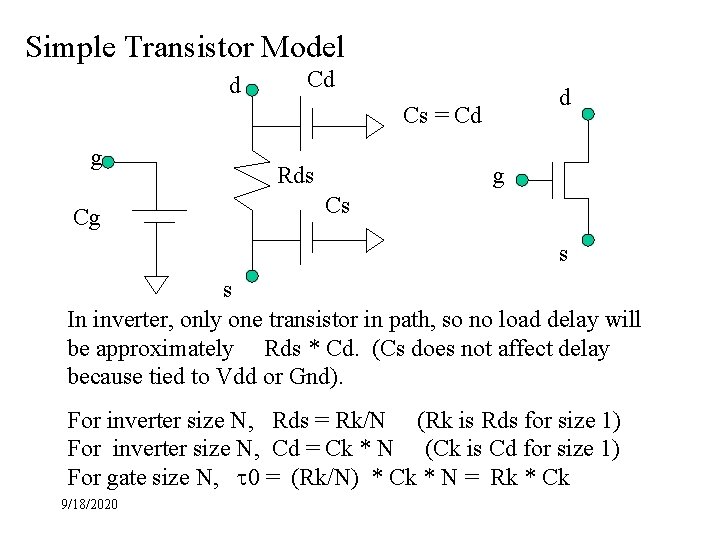

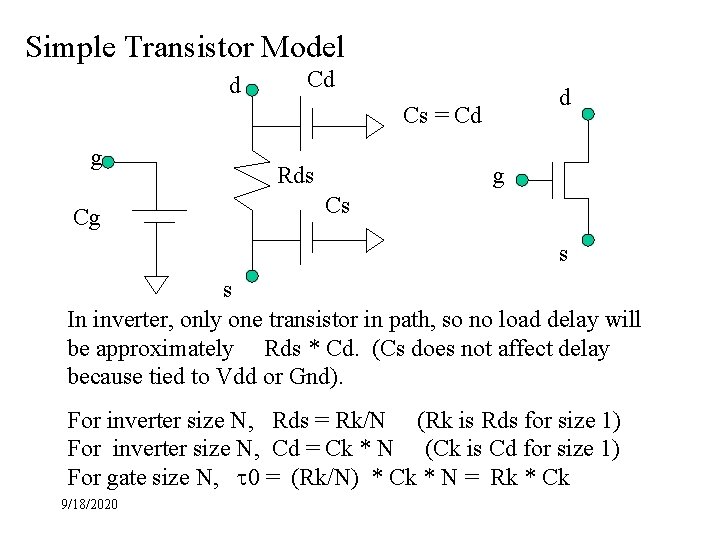

Simple Transistor Model d Cd d Cs = Cd g Cg Rds g Cs s s In inverter, only one transistor in path, so no load delay will be approximately Rds * Cd. (Cs does not affect delay because tied to Vdd or Gnd). For inverter size N, Rds = Rk/N (Rk is Rds for size 1) For inverter size N, Cd = Ck * N (Ck is Cd for size 1) For gate size N, t 0 = (Rk/N) * Ck * N = Rk * Ck 9/18/2020

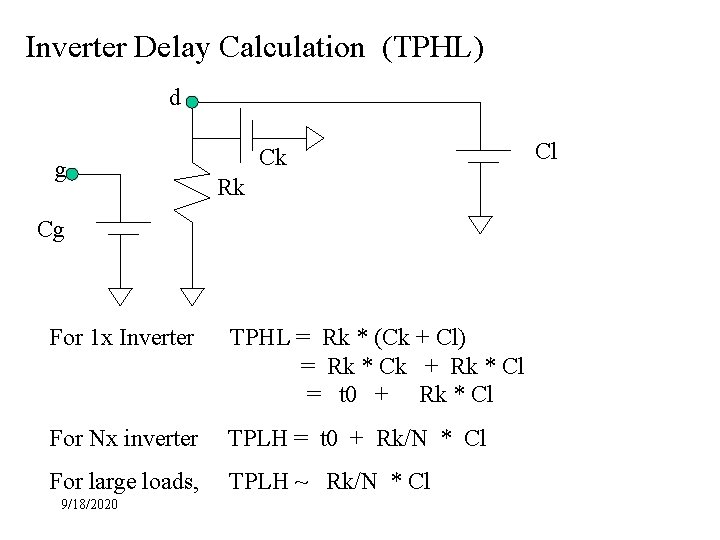

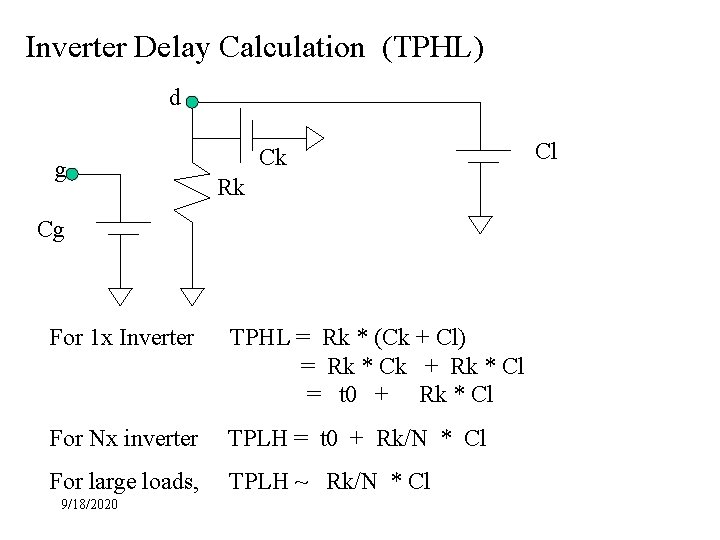

Inverter Delay Calculation (TPHL) d g Ck Rk Cg For 1 x Inverter TPHL = Rk * (Ck + Cl) = Rk * Ck + Rk * Cl = t 0 + Rk * Cl For Nx inverter TPLH = t 0 + Rk/N * Cl For large loads, TPLH ~ Rk/N * Cl 9/18/2020 Cl

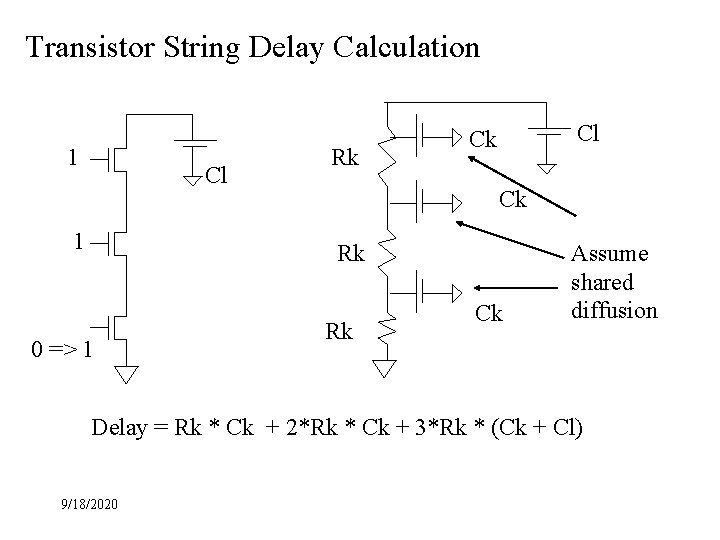

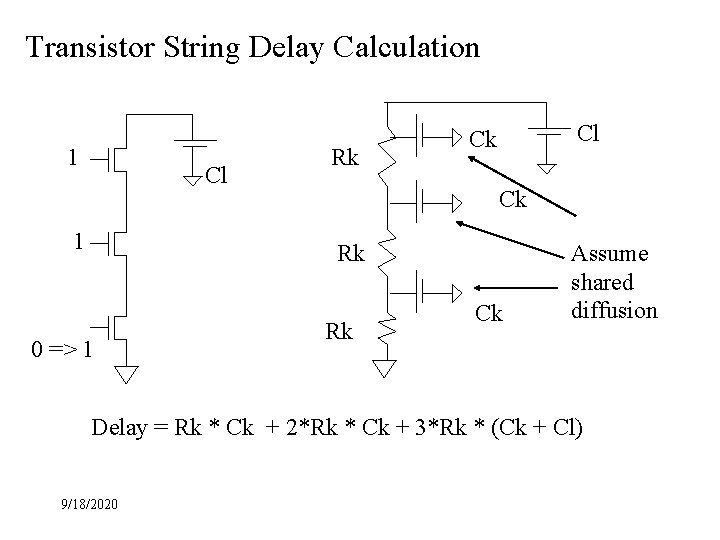

Transistor String Delay Calculation 1 Cl 1 Rk Cl Ck Ck Rk 0 => 1 Rk Ck Assume shared diffusion Delay = Rk * Ck + 2*Rk * Ck + 3*Rk * (Ck + Cl) 9/18/2020

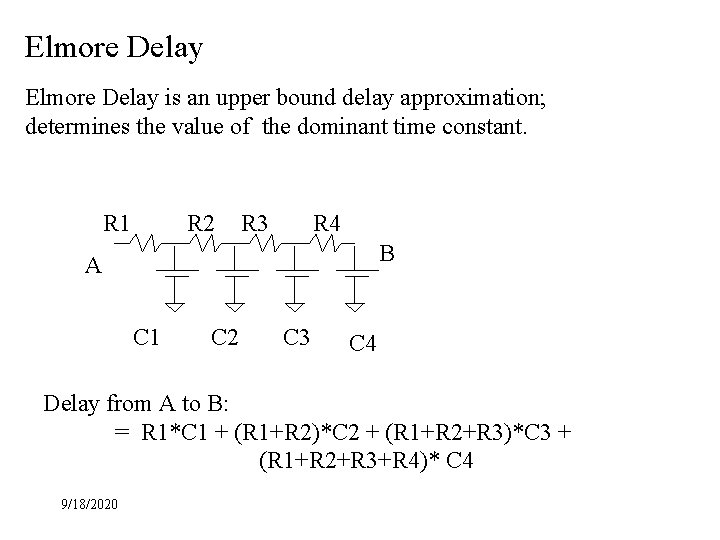

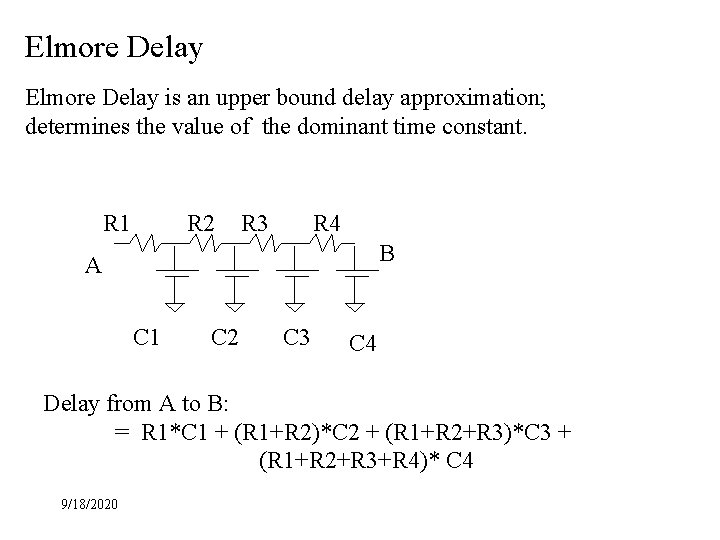

Elmore Delay is an upper bound delay approximation; determines the value of the dominant time constant. R 1 R 2 R 3 R 4 B A C 1 C 2 C 3 C 4 Delay from A to B: = R 1*C 1 + (R 1+R 2)*C 2 + (R 1+R 2+R 3)*C 3 + (R 1+R 2+R 3+R 4)* C 4 9/18/2020

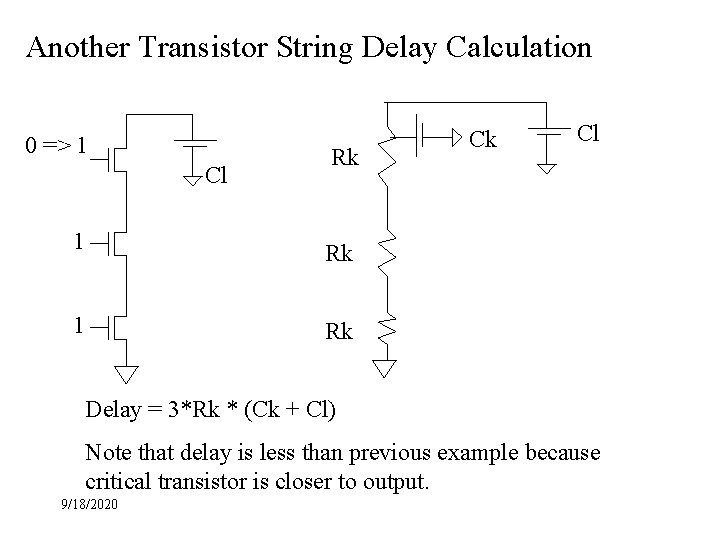

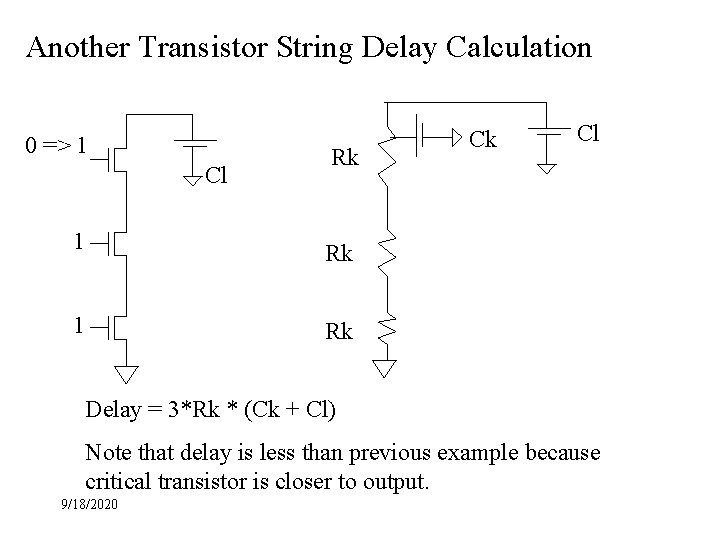

Another Transistor String Delay Calculation 0 => 1 Cl Rk 1 Rk Ck Cl Delay = 3*Rk * (Ck + Cl) Note that delay is less than previous example because critical transistor is closer to output. 9/18/2020

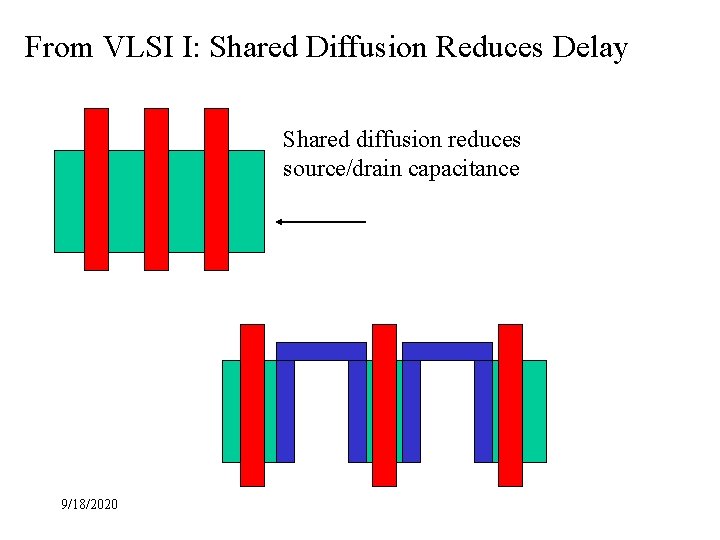

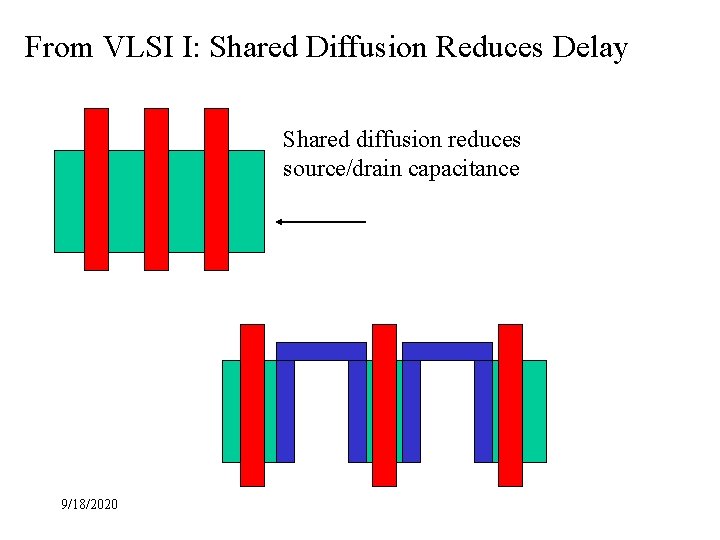

From VLSI I: Shared Diffusion Reduces Delay Shared diffusion reduces source/drain capacitance 9/18/2020

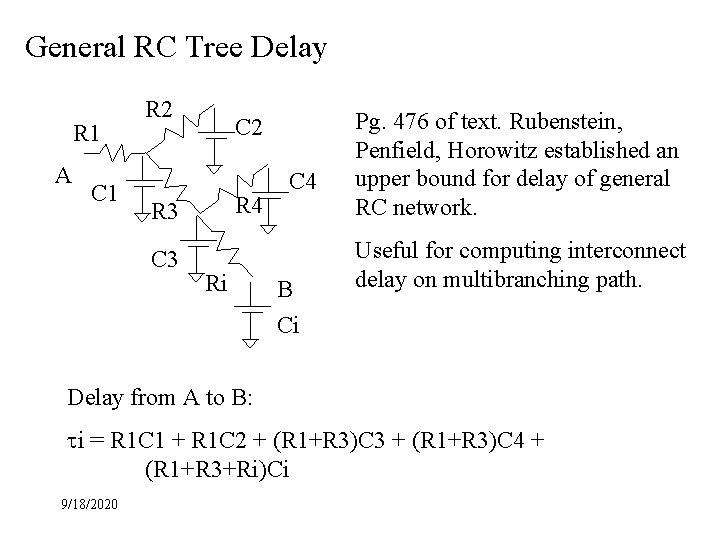

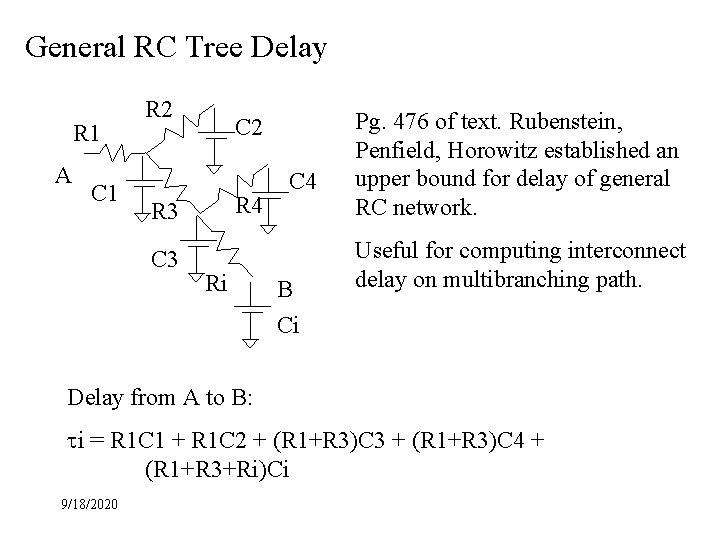

General RC Tree Delay R 1 A C 1 R 2 C 2 R 4 R 3 C 3 Ri C 4 B Ci Pg. 476 of text. Rubenstein, Penfield, Horowitz established an upper bound for delay of general RC network. Useful for computing interconnect delay on multibranching path. Delay from A to B: ti = R 1 C 1 + R 1 C 2 + (R 1+R 3)C 3 + (R 1+R 3)C 4 + (R 1+R 3+Ri)Ci 9/18/2020

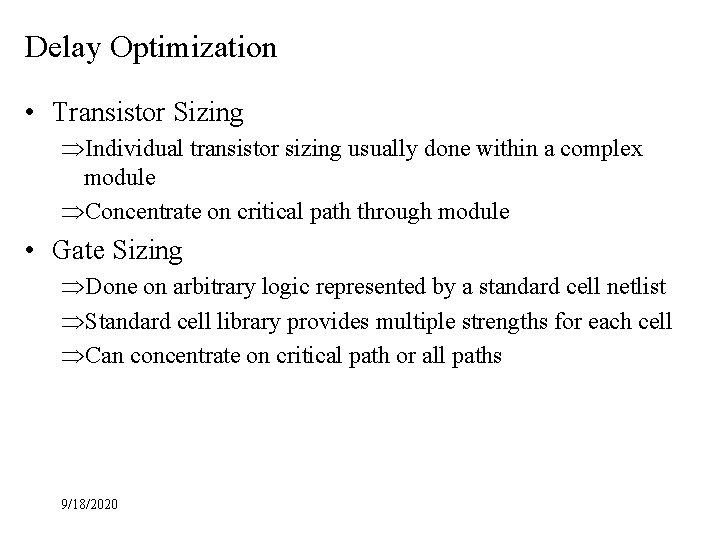

Delay Optimization • Transistor Sizing ÞIndividual transistor sizing usually done within a complex module ÞConcentrate on critical path through module • Gate Sizing ÞDone on arbitrary logic represented by a standard cell netlist ÞStandard cell library provides multiple strengths for each cell ÞCan concentrate on critical path or all paths 9/18/2020

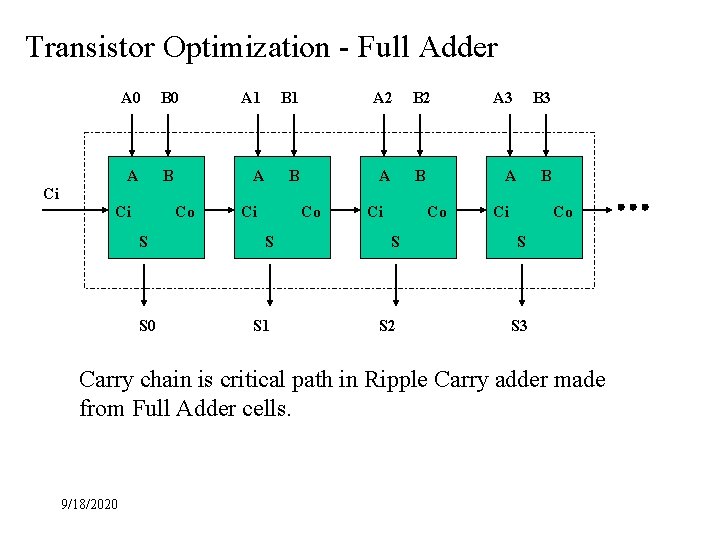

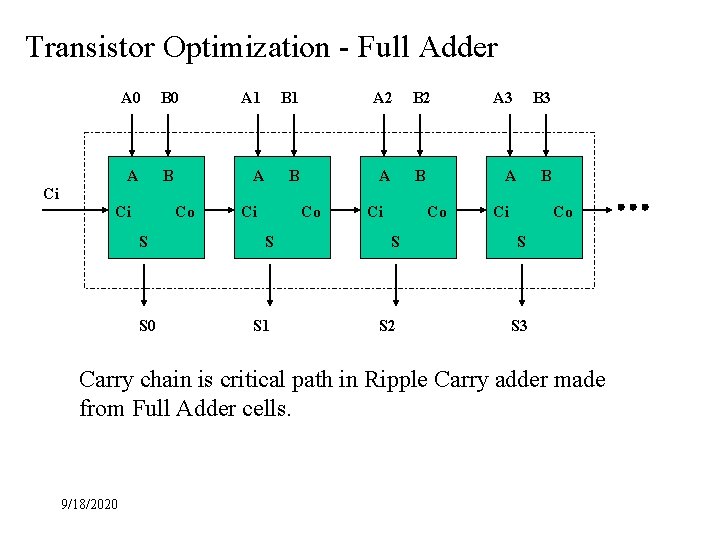

Transistor Optimization - Full Adder A 0 B 0 A B A 1 B 1 A 2 B 2 A B A 3 B 3 A B Ci Ci Co S S 0 Ci Co S S 1 S 2 S 3 Carry chain is critical path in Ripple Carry adder made from Full Adder cells. 9/18/2020

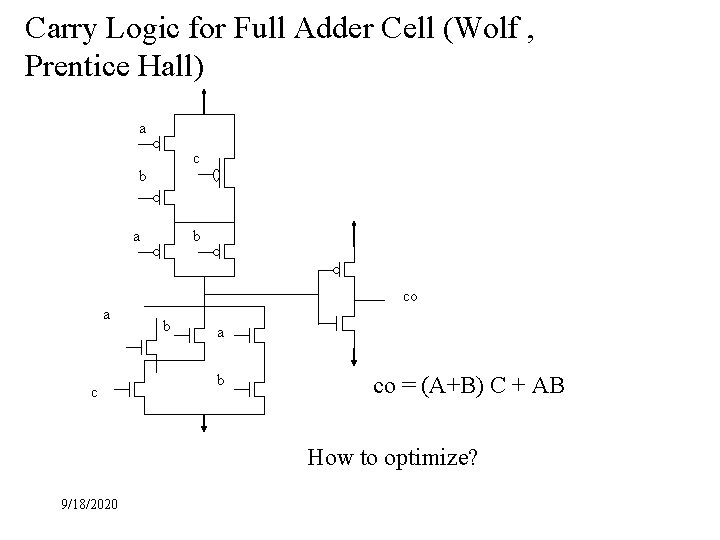

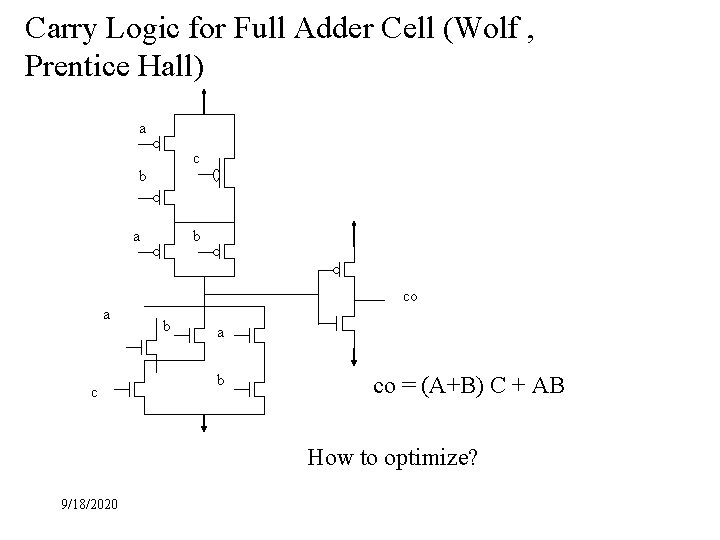

Carry Logic for Full Adder Cell (Wolf , Prentice Hall) a c b a b co = (A+B) C + AB How to optimize? 9/18/2020

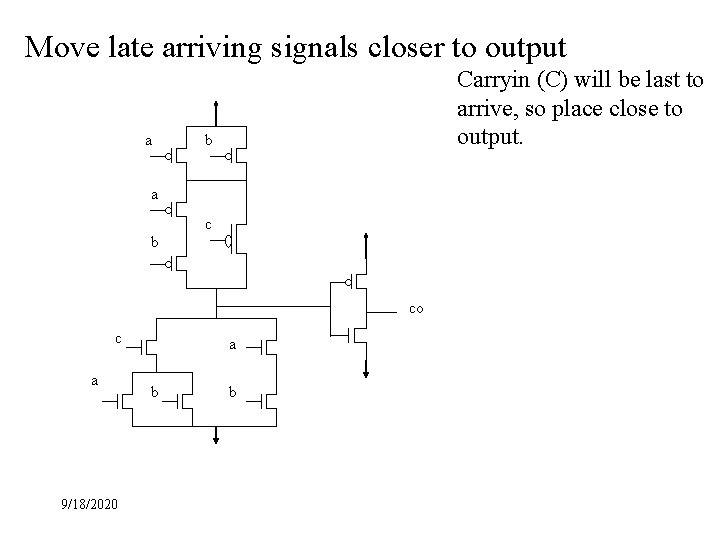

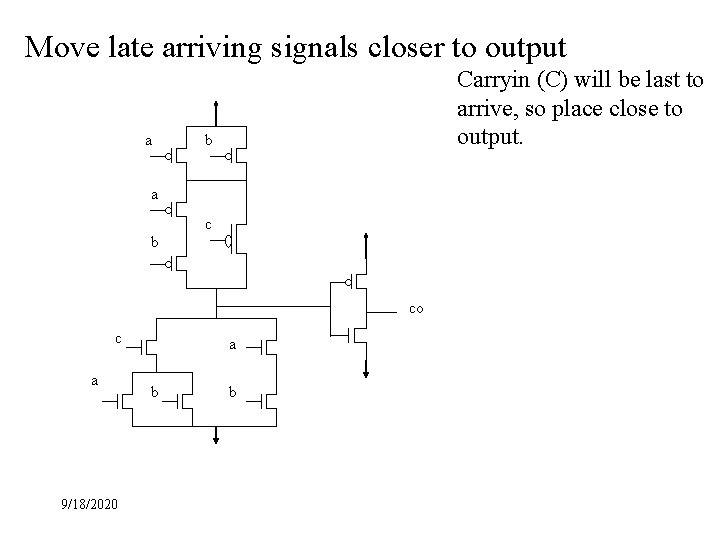

Move late arriving signals closer to output a Carryin (C) will be last to arrive, so place close to output. b a c b co c a 9/18/2020 a b b

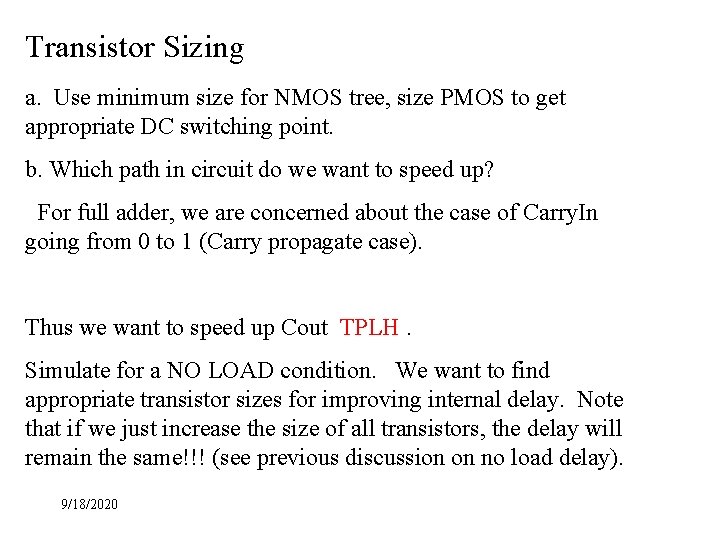

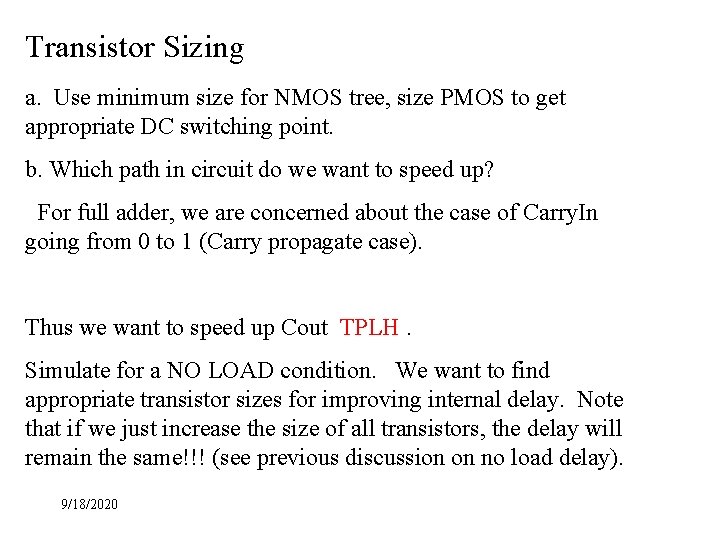

Transistor Sizing a. Use minimum size for NMOS tree, size PMOS to get appropriate DC switching point. b. Which path in circuit do we want to speed up? For full adder, we are concerned about the case of Carry. In going from 0 to 1 (Carry propagate case). Thus we want to speed up Cout TPLH. Simulate for a NO LOAD condition. We want to find appropriate transistor sizes for improving internal delay. Note that if we just increase the size of all transistors, the delay will remain the same!!! (see previous discussion on no load delay). 9/18/2020

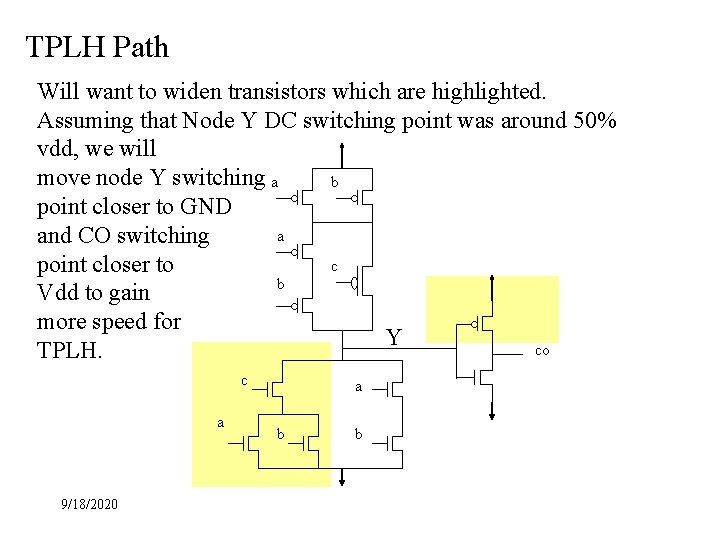

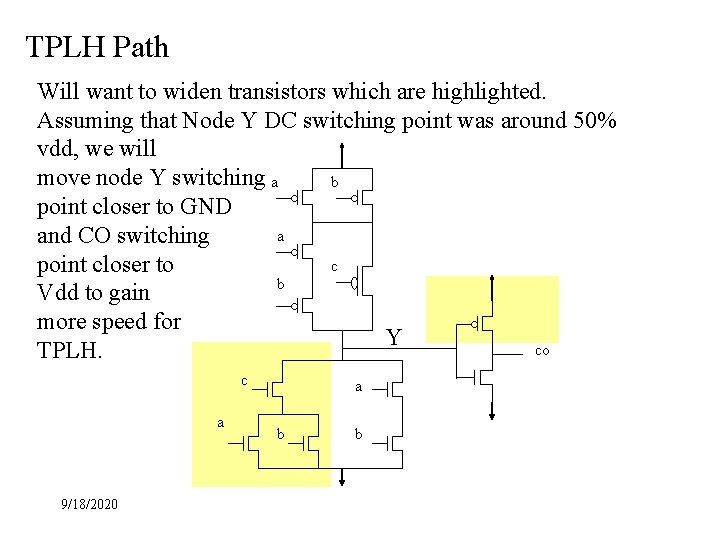

TPLH Path Will want to widen transistors which are highlighted. Assuming that Node Y DC switching point was around 50% vdd, we will move node Y switching a b point closer to GND a and CO switching c point closer to b Vdd to gain more speed for Y co TPLH. c a 9/18/2020 a b b

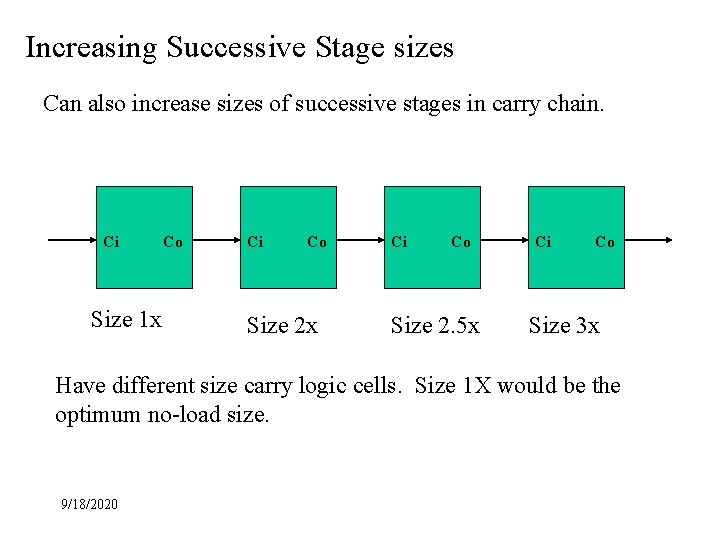

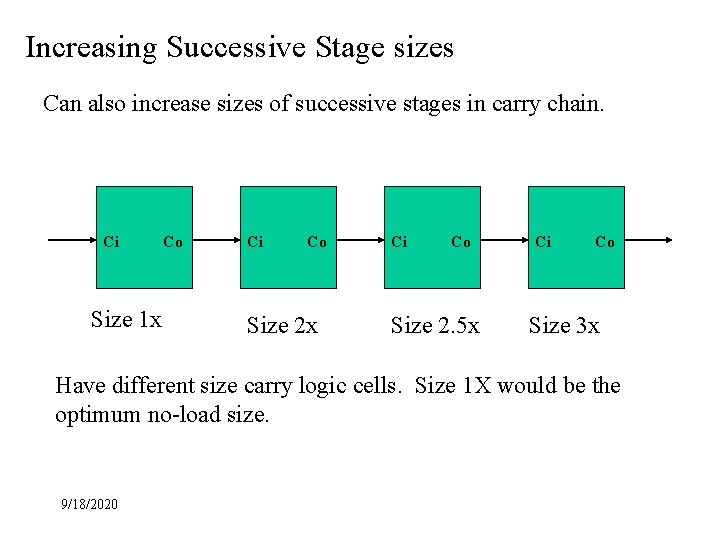

Increasing Successive Stage sizes Can also increase sizes of successive stages in carry chain. Ci Size 1 x Co Ci Co Size 2 x Ci Co Size 2. 5 x Ci Co Size 3 x Have different size carry logic cells. Size 1 X would be the optimum no-load size. 9/18/2020

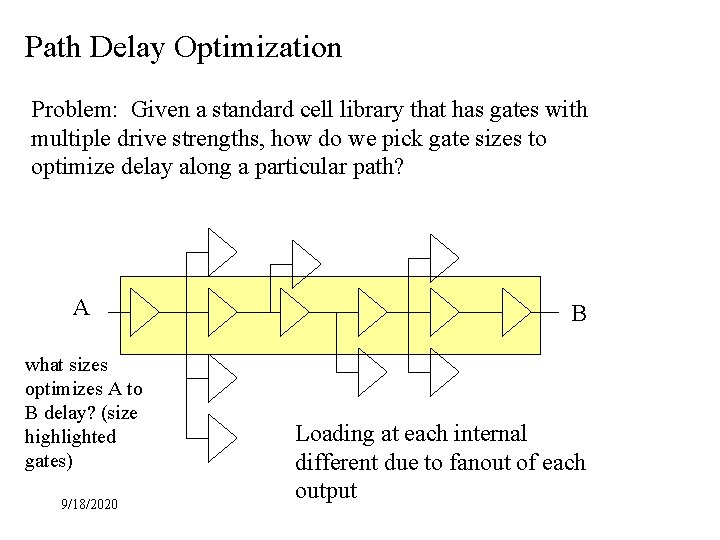

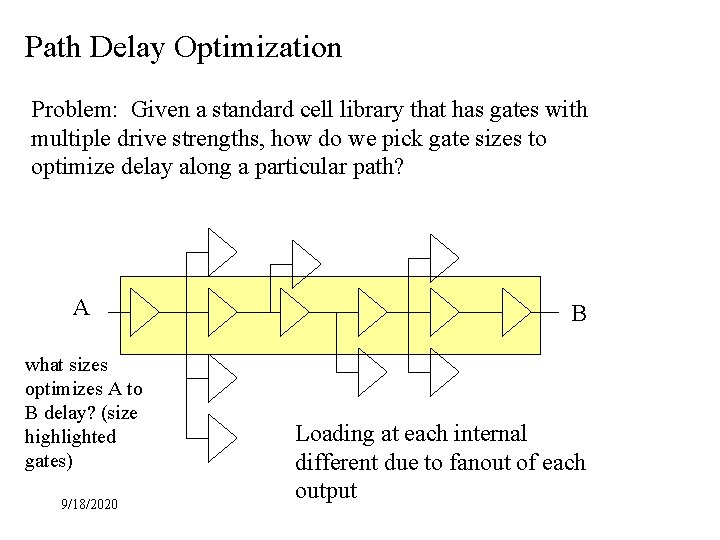

Path Delay Optimization Problem: Given a standard cell library that has gates with multiple drive strengths, how do we pick gate sizes to optimize delay along a particular path? A what sizes optimizes A to B delay? (size highlighted gates) 9/18/2020 B Loading at each internal different due to fanout of each output

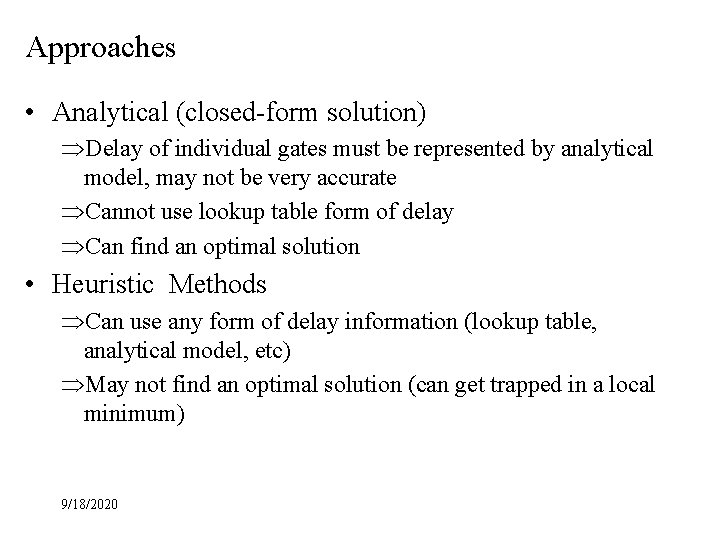

Approaches • Analytical (closed-form solution) ÞDelay of individual gates must be represented by analytical model, may not be very accurate ÞCannot use lookup table form of delay ÞCan find an optimal solution • Heuristic Methods ÞCan use any form of delay information (lookup table, analytical model, etc) ÞMay not find an optimal solution (can get trapped in a local minimum) 9/18/2020

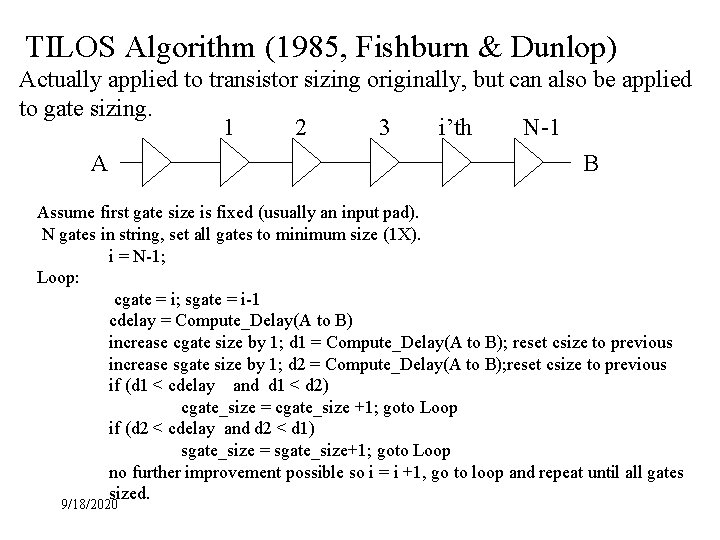

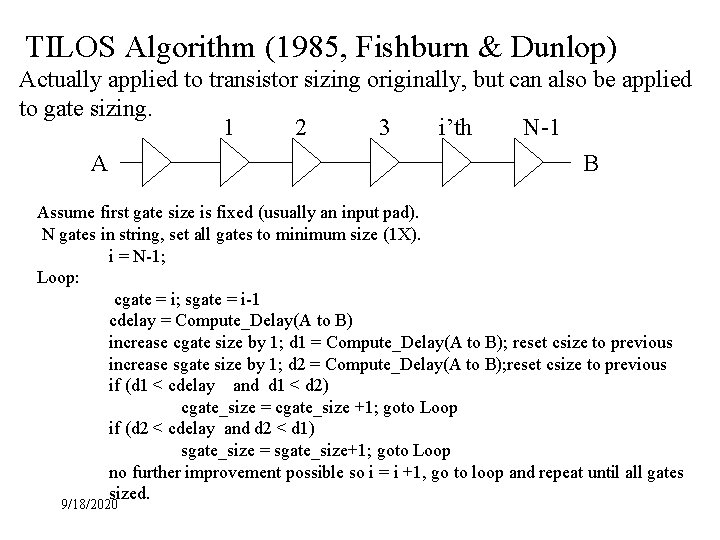

TILOS Algorithm (1985, Fishburn & Dunlop) Actually applied to transistor sizing originally, but can also be applied to gate sizing. 1 2 3 i’th N-1 A B Assume first gate size is fixed (usually an input pad). N gates in string, set all gates to minimum size (1 X). i = N-1; Loop: cgate = i; sgate = i-1 cdelay = Compute_Delay(A to B) increase cgate size by 1; d 1 = Compute_Delay(A to B); reset csize to previous increase sgate size by 1; d 2 = Compute_Delay(A to B); reset csize to previous if (d 1 < cdelay and d 1 < d 2) cgate_size = cgate_size +1; goto Loop if (d 2 < cdelay and d 2 < d 1) sgate_size = sgate_size+1; goto Loop no further improvement possible so i = i +1, go to loop and repeat until all gates sized. 9/18/2020

TILOS Algorithm Comments • Note that algorithm starts at end of the path and works toward the start of the path • When cgate = 1, then we cannot size the supporting gate because the first gate in the string is assumed to be a fixed size • A ‘greedier’ version of the algorithm only sizes the ‘cgate’ (current gate) and does not size the supporting gate ÞDoes not produce as good a result 9/18/2020

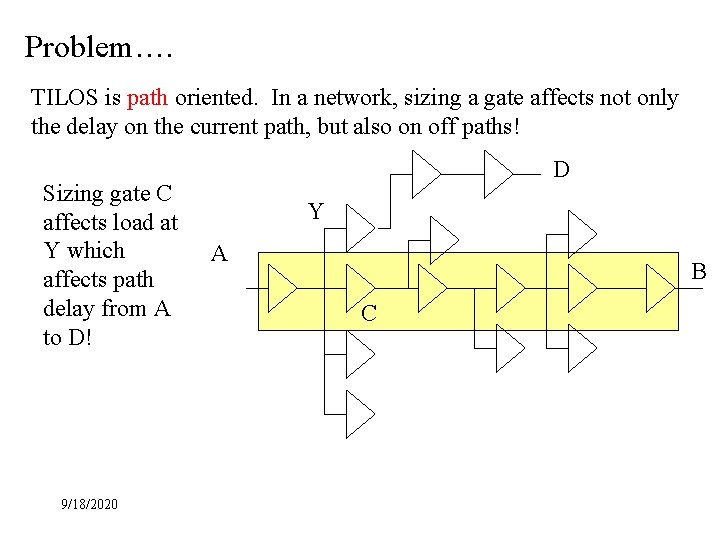

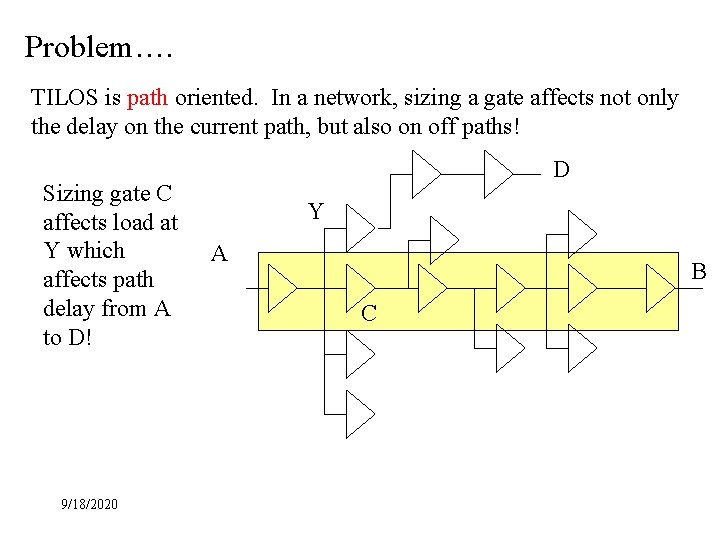

Problem…. TILOS is path oriented. In a network, sizing a gate affects not only the delay on the current path, but also on off paths! Sizing gate C affects load at Y which affects path delay from A to D! 9/18/2020 D Y A B C

Path-Oriented Algorithms • Path Oriented algorithms are applied to each path in the network ÞDependencies between paths cause problems ÞNumber of paths grows exponentially with the number of gates in a network!!! • Would like an algorithm that would be able to optimize all paths in a network, and yet have linear execution time with the number of gates. 9/18/2020

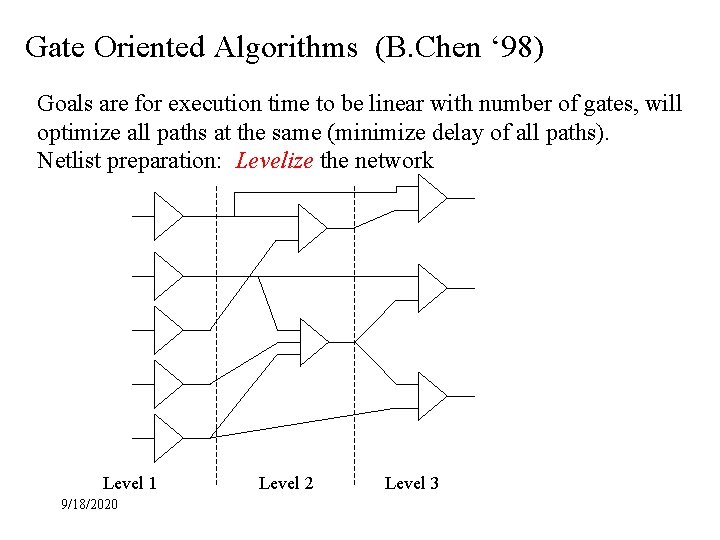

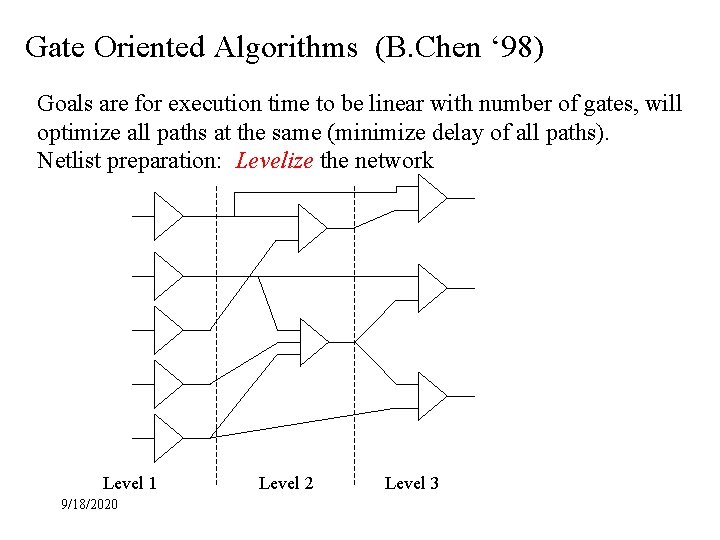

Gate Oriented Algorithms (B. Chen ‘ 98) Goals are for execution time to be linear with number of gates, will optimize all paths at the same (minimize delay of all paths). Netlist preparation: Levelize the network Level 1 9/18/2020 Level 2 Level 3

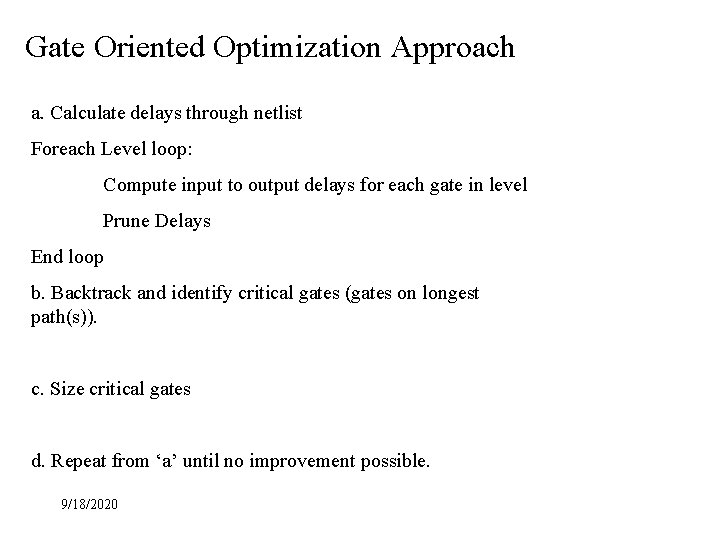

Gate Oriented Optimization Approach a. Calculate delays through netlist Foreach Level loop: Compute input to output delays for each gate in level Prune Delays End loop b. Backtrack and identify critical gates (gates on longest path(s)). c. Size critical gates d. Repeat from ‘a’ until no improvement possible. 9/18/2020

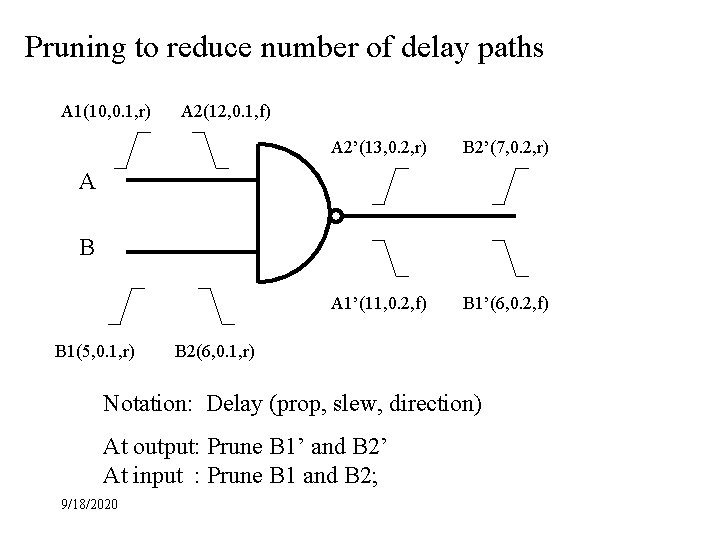

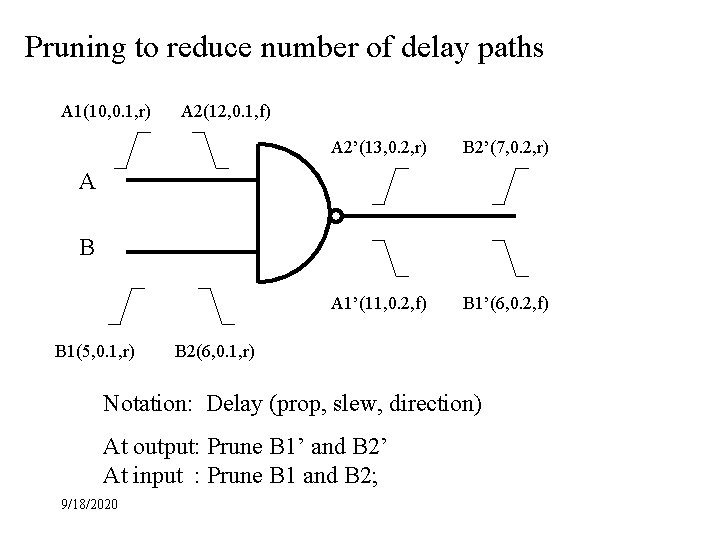

Pruning to reduce number of delay paths A 1(10, 0. 1, r) A 2(12, 0. 1, f) A 2’(13, 0. 2, r) B 2’(7, 0. 2, r) A 1’(11, 0. 2, f) B 1’(6, 0. 2, f) A B B 1(5, 0. 1, r) B 2(6, 0. 1, r) Notation: Delay (prop, slew, direction) At output: Prune B 1’ and B 2’ At input : Prune B 1 and B 2; 9/18/2020

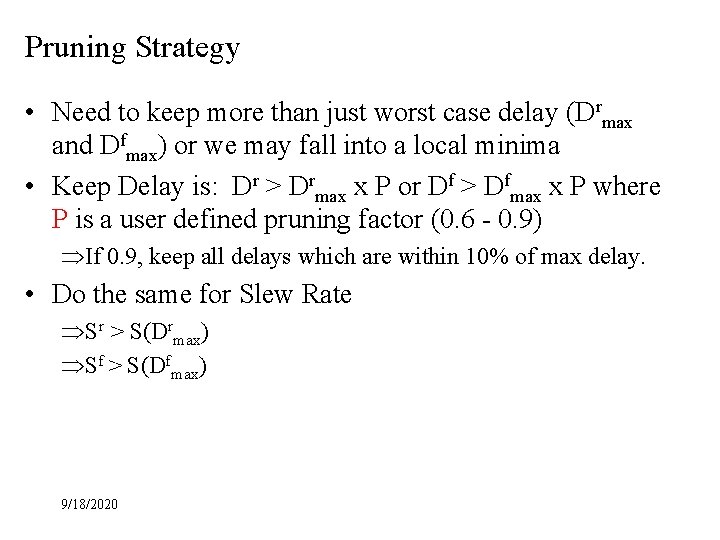

Pruning Strategy • Need to keep more than just worst case delay (Drmax and Dfmax) or we may fall into a local minima • Keep Delay is: Dr > Drmax x P or Df > Dfmax x P where P is a user defined pruning factor (0. 6 - 0. 9) ÞIf 0. 9, keep all delays which are within 10% of max delay. • Do the same for Slew Rate ÞSr > S(Drmax) ÞSf > S(Dfmax) 9/18/2020

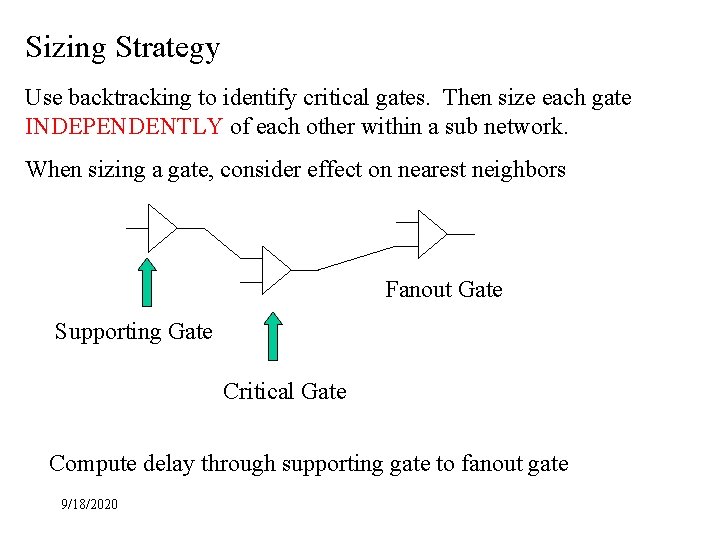

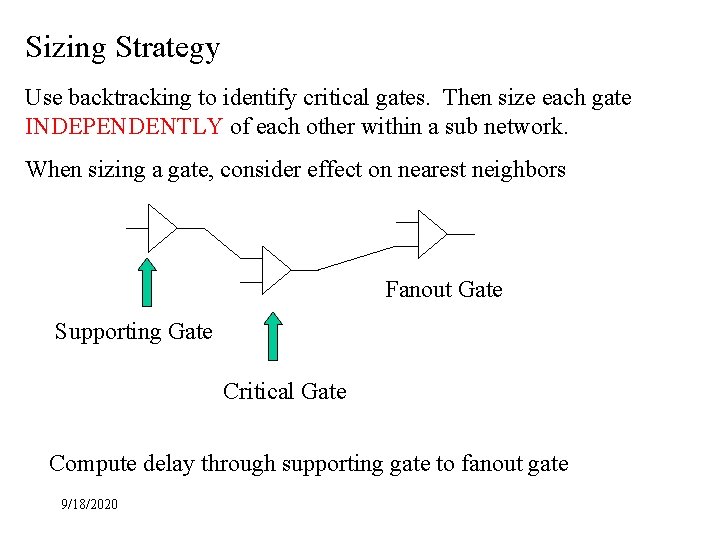

Sizing Strategy Use backtracking to identify critical gates. Then size each gate INDEPENDENTLY of each other within a sub network. When sizing a gate, consider effect on nearest neighbors Fanout Gate Supporting Gate Critical Gate Compute delay through supporting gate to fanout gate 9/18/2020

Results (B. Chen ‘ 98) • Found that Gate sizing approach yielded as good or better results than path-oriented approach done by Synopsys • Achieved 10 x or better execution time speedup in most cases • Only drawback is that all paths are affected ÞCould be used for first cut at sizing where you wanted to ‘minimize’ all gate delays first. 9/18/2020

Parallelism • This algorithm can be parallelized because gates are sized independently of each other. • Delay computation and identification of critical gates are not easily parallelized. • Results found that sizing accounted for about 60% of the runtime. ÞMaximum possible speedup is then about 2. 5 if just concentrate on gate sizing. • To get better speedup, would need to parallelize delay computation and identification critical gates. 9/18/2020