Delay Fault Testing Present and Future Jubayer Mahmod

Delay Fault Testing – Present and Future Jubayer Mahmod, Spencer Millican, Ujjwal Guin, and Vishwani Agrawal

Structure Delay vs. stuck-at fault testing Delay fault models – nuances and strategies � Path delay fault (PDF) model � Transition delay fault (TDF) model � Small delay defects (SDDs) Scan chains for delay fault testing Current literature directions � GPGPU-enabled simulation � Security 2

Motivation for delay fault testing © Chip Design Magazine Survey Citations/Year 12 10 8 6 4 2 1948 1951 1954 1957 1960 1963 1966 1969 1972 1975 1978 1981 1984 1987 1990 1993 1996 1999 2002 2005 2008 2011 2014 2017 0 © CC BY-SA 3. 0 3

Delay vs. stuck-at fault test 4

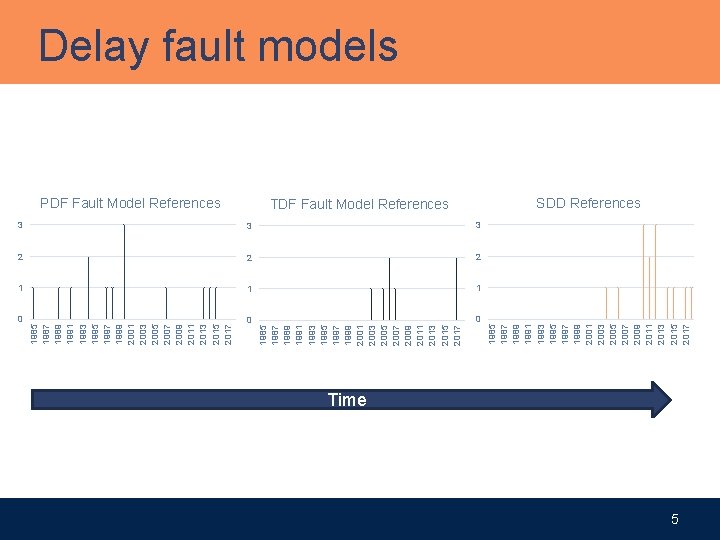

3 3 3 2 2 2 1 1 1 0 0 0 TDF Fault Model References 1985 1987 1989 1991 1993 1995 1997 1999 2001 2003 2005 2007 2009 2011 2013 2015 2017 PDF Fault Model References 1985 1987 1989 1991 1993 1995 1997 1999 2001 2003 2005 2007 2009 2011 2013 2015 2017 Delay fault models SDD References Time 5

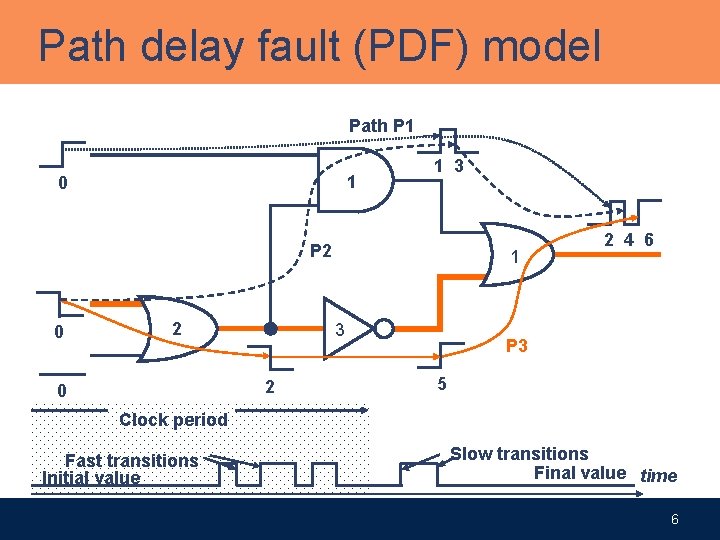

Path delay fault (PDF) model Path P 1 1 0 1 3 P 2 0 2 3 2 0 1 2 4 6 P 3 5 Clock period Fast transitions Initial value Slow transitions Final value time 6

PDF - Robustness Non-robust Test U 1 S 0 R 1 Robust Test (singularly testable faults) R 1 S 0 U 1 R 1 F 0 U 1 U 0 R 1 U 0 7

PDF – computational complexity 8

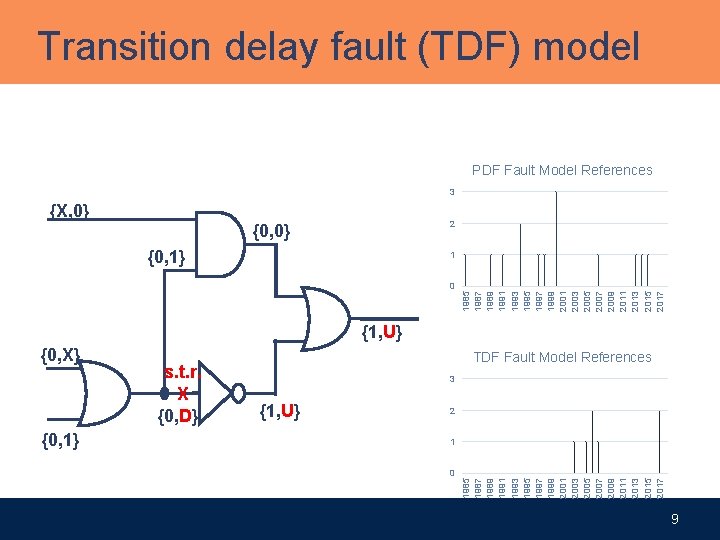

Transition delay fault (TDF) model PDF Fault Model References 3 {X, 0} 2 {0, 0} {0, 1} 1 1985 1987 1989 1991 1993 1995 1997 1999 2001 2003 2005 2007 2009 2011 2013 2015 2017 0 {1, U} {0, 1} s. t. r. X {0, D} TDF Fault Model References 3 {1, U} 2 1 0 1985 1987 1989 1991 1993 1995 1997 1999 2001 2003 2005 2007 2009 2011 2013 2015 2017 {0, X} 9

Small delay defects (SDDs) – The TDF detection problem SDD References 3 2 1 0 1985 1987 1989 1991 1993 1995 1997 1999 2001 2003 2005 2007 2009 2011 2013 2015 2017 A second trend is illustrated in Figure 6, which shows the additional propagation delay for a set of timing-related failures. Although the data it limited, it suggests there are more small delay defects than large delay defects. Figures 5 and 6 suggest that there may be many small delay defects and that faster designs may be more sensitive to these additional (small) delays. This assumes, however, that the additional propagation delays of timingrelated defects do not scale as designs get faster. P. Nigh & Anne Gattiker, “Test Method Evaluation Experiments & Data”, ITC, 2000. 10

TDF – SDD Detection problem Not detected! {X, 0} {0, 1} X s. t. f. Detected! {1, U} {0, X} s. t. r. X {0, D} {1, U} {0, 1} 11

Segment delay fault (SDF) model Fan-in Cone Transition launch Fan-out Cone Transition propagate 12

Unspecified transition faults – detecting SDDs with modified TDFs Optimistic {X, 0} {0, 0} {1, X} {0, 1} {1, X} D Q {1, X} {0, X} s. t. r. X {0, X} Pessimistic {1, X} D Q {1, 1} {0, 1} 13

Faster-than-speed testing Faster-than-speed Testing References 3 2 1 1948 1951 1954 1957 1960 1963 1966 1969 1972 1975 1978 1981 1984 1987 1990 1993 1996 1999 2002 2005 2008 2011 2014 2017 0 [123] R. T. Uppu, R. K. Uppu, A. D. Singh, and A. Chatterjee, “A high throughput multiplier design exploiting input based statistical distribution in completion delays, ” in Proc. 26 th International Conference on VLSI Design, Jan. 2013, pp. 109– 114. 14

X-canceling MISRs Scan Chain MISR … … Decompressor/LFSR Scan Chain Selection 15

The two-vector scanning problem 16

Scan-hold / enhanced scan CK period CK circuit CK TC HL HL HOLD PO HOLD SFF Scanout result V 1 settles SFF SCANIN CK TC CK: system clock TC: test control HOLD: hold signal SFF: scan flip-flop HL: hold latch TC Scanin V 1 states V 1 PI applied Scan mode Normal mode SCANOUT Combinational Normal mode PI Scanin V 2 states Result latched V 2 PI Capture applied Launch 17

Using existing scan architectures Launch-off-shift (LOS) “skew load” Launch-off-capture (LOC) “broadside” 18

Multiple scan enables PI Combinational PO circuit CK TC 1 SCANOUT 2 SFF SCANIN 1 SFF SCANIN 2 CK TC 2 CK: system clock TC 1, TC 2: test control SFF: scan flip-flop 19

GPU-based fault simulation Thambawita, Vajira, Roshan Ragel, and Dhammika Elkaduwe. “To Use or Not to Use: Graphics Processing Units for Pattern Matching Algorithms, ” December 25, 2014. 20

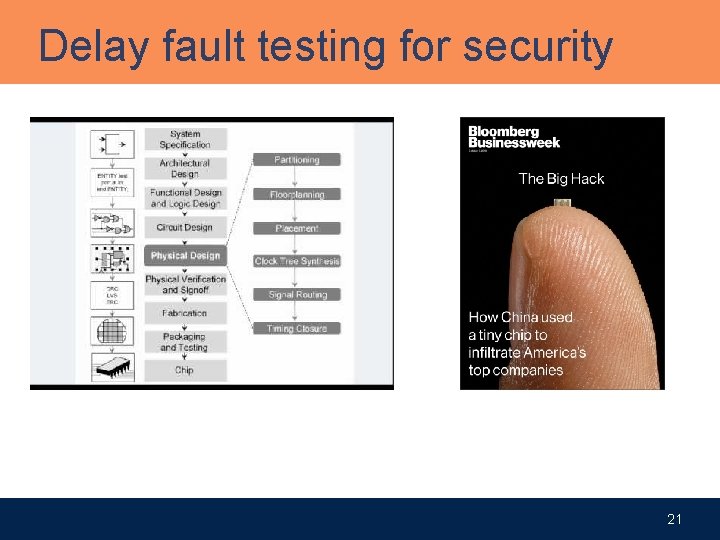

Delay fault testing for security 21

ATPG to find trojan-induced delays 22

IC Recycling detection using machine learning of measured delays 23

What else is next? Signal integrity & process variation Asynchronous & self-timed circuits Emerging nano-devices 24

Thank you

- Slides: 25