Defect Tolerance for Yield Enhancement of FPGA Interconnect

- Slides: 28

Defect Tolerance for Yield Enhancement of FPGA Interconnect Using Fine-grain and Coarse-grain Redundancy Anthony J. Yu August 15, 2005

Outline Introduction and motivation n Previous works n New architectures n Coarse-grain redundancy (CGR) n Fine-grain redundancy (FGR) n Comparisons n Conclusions n 2

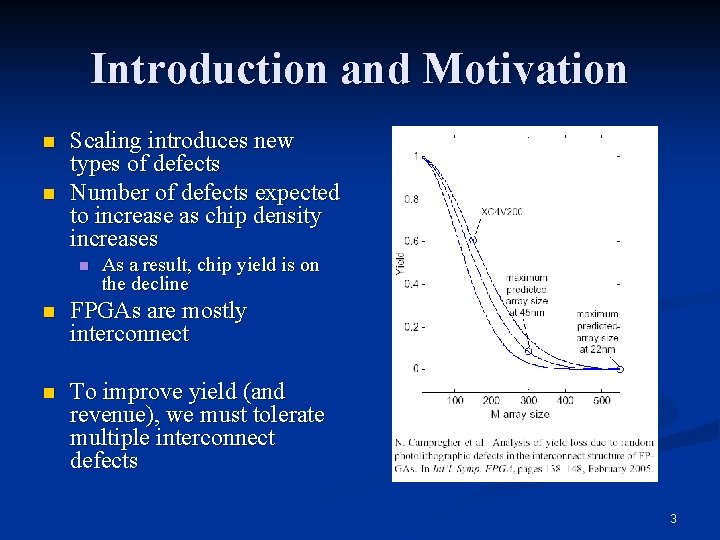

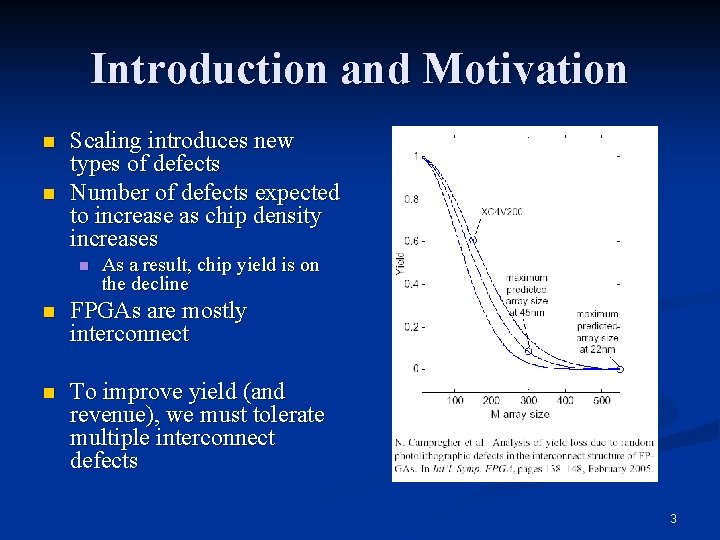

Introduction and Motivation n n Scaling introduces new types of defects Number of defects expected to increase as chip density increases n As a result, chip yield is on the decline n FPGAs are mostly interconnect n To improve yield (and revenue), we must tolerate multiple interconnect defects 3

General Defect Tolerant Techniques n Defect-tolerant techniques minimize impact (cost) of manufacturing defects n FPGA defect-tolerance can be loosely categorized into three classes: n n n Software Redundancy – use CAD tools to map around the defects Hardware Redundancy – incorporate spare resources to assist in defect correction (eg. Spare row/column) Run-time Redundancy – protection against transient faults such as SEUs (eg. TMR) 4

Previous work – 1 – Xilinx n Xilinx’s Defect-Tolerant Approach n n n Customer gives Xilinx configuration bitstream Xilinx tests FPGA devices against bitstream n n n Customer (knowingly) purchases “less that perfect” parts Sells FPGA parts that “appear” perfect Defects avoid the bitstream Limitation: n Chips work only with given bitstream – no changes! 5

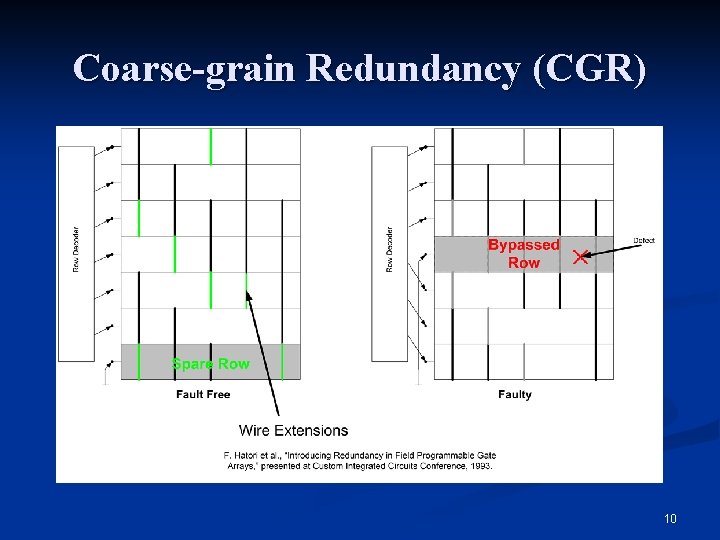

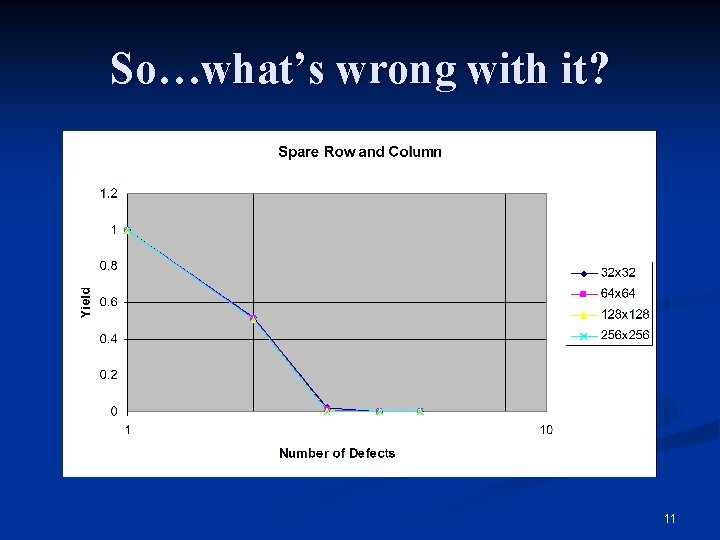

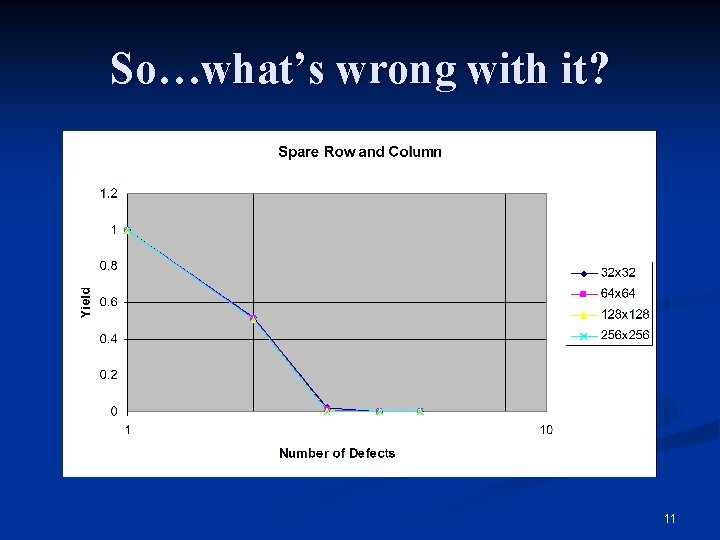

Previous work – 2 – Altera n Altera’s Defect-Tolerant Approach n n n Make defective resources inaccessible to user Coarse-grain architecture n n Spare row and column in array (like memories) Defective row/column must be bypassed n n Customer purchases “seemingly perfect” parts Use the spare row/column instead Limitation: n Does not scale well (multiple defects) 6

Objectives n Problem n n FPGA yield is on decline because of aggressive technology scaling Important objectives to improve yield: Tolerate interconnect defects (dominates area) n Tolerate multiple defects (future trend) n Preserve timing (no timing re-verification) n Fast correction time (production use) n 7

Contributions n New fine-grain redundancy architecture Coarse-grain architecture with multiple spare rows and columns n Detailed evaluation of fine-grain and coarse-grain redundancy n n n Area, delay, yield estimates Publications: n n n Non-redundant architecture paper, at FPT’ 04 Fine-grain architecture paper, to appear in FPL’ 05 Yield comparison paper, to appear in FPT’ 05 8

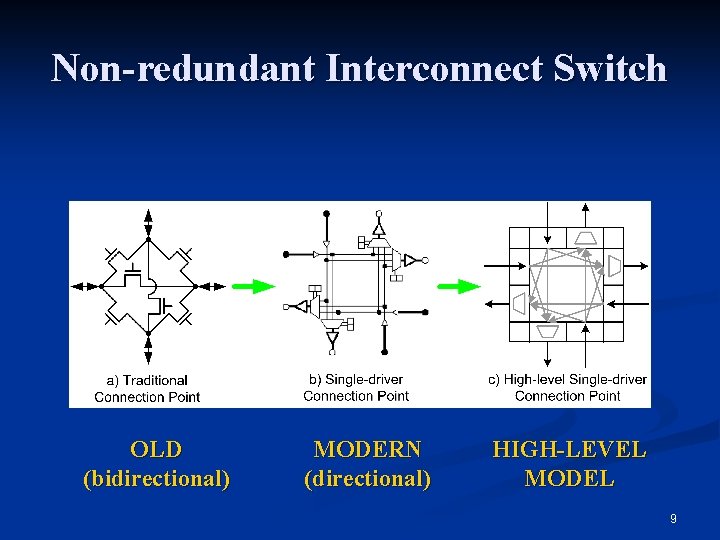

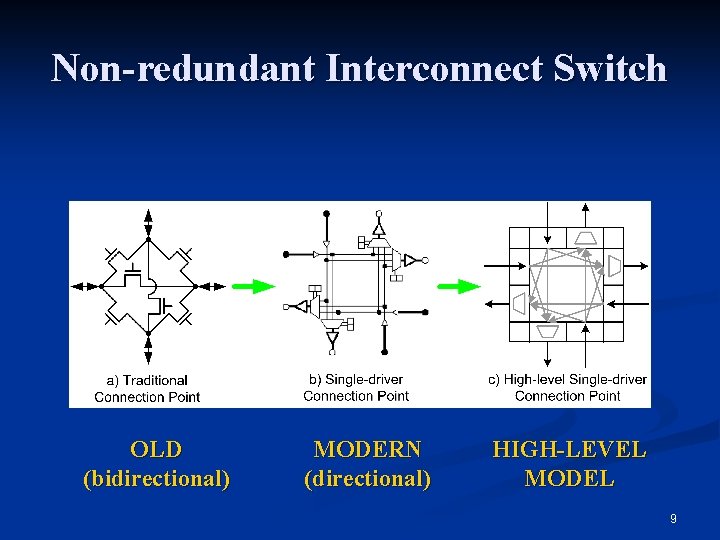

Non-redundant Interconnect Switch OLD (bidirectional) MODERN (directional) HIGH-LEVEL MODEL 9

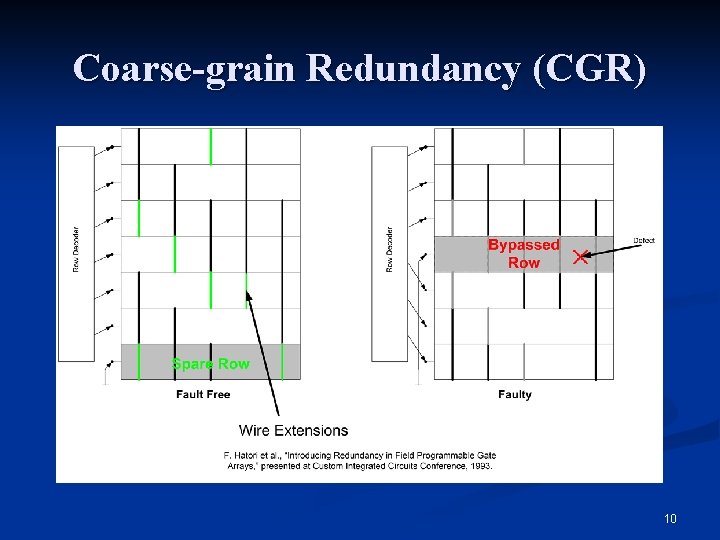

Coarse-grain Redundancy (CGR) 10

So…what’s wrong with it? 11

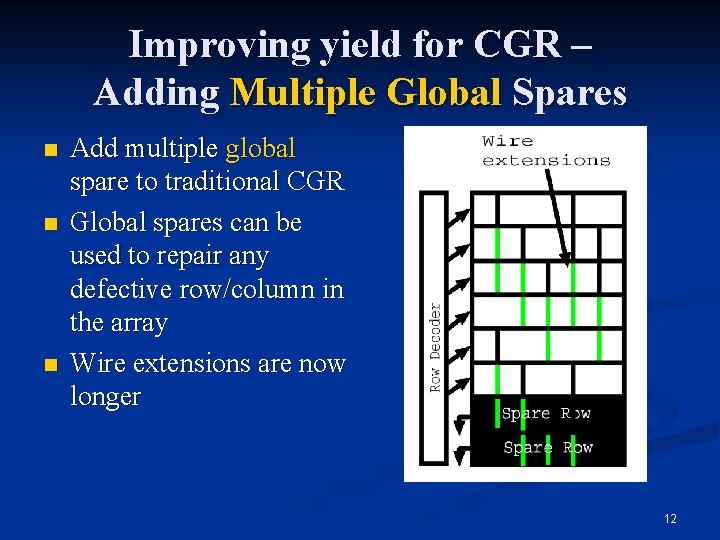

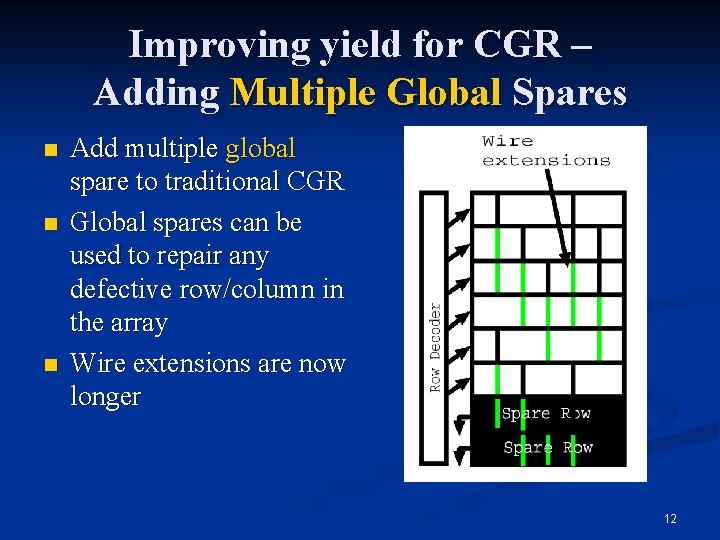

Improving yield for CGR – Adding Multiple Global Spares n n n Add multiple global spare to traditional CGR Global spares can be used to repair any defective row/column in the array Wire extensions are now longer 12

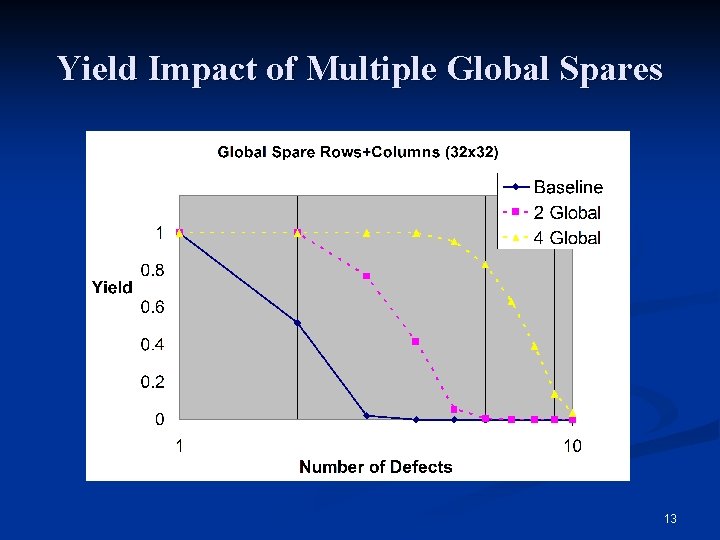

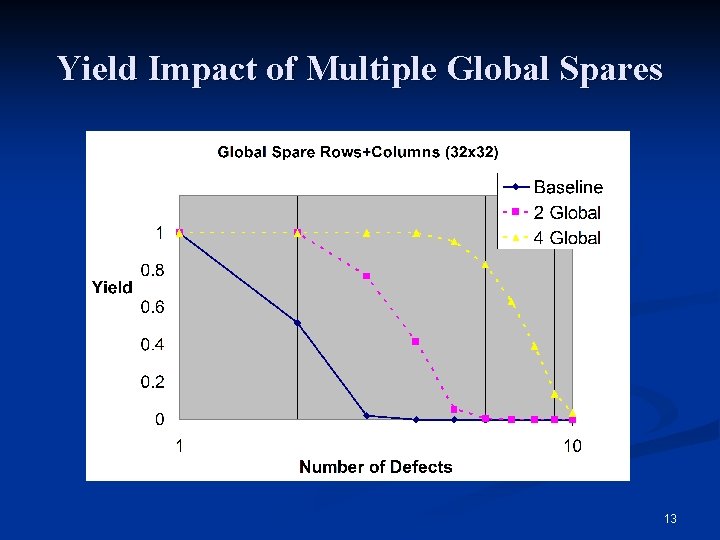

Yield Impact of Multiple Global Spares 13

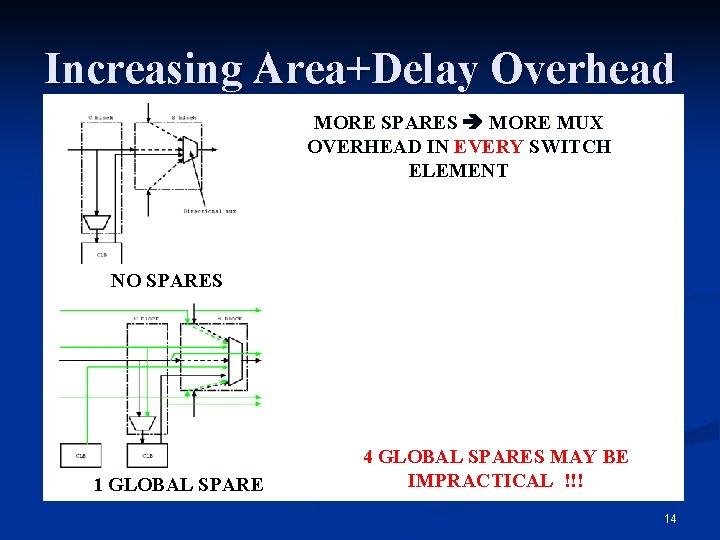

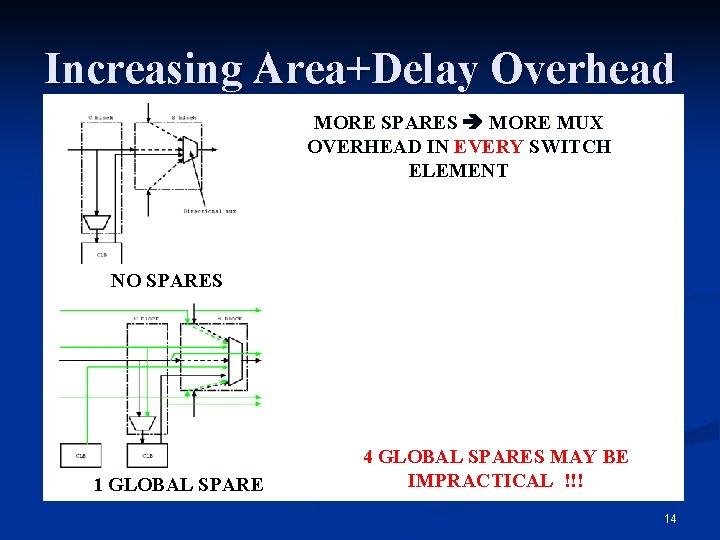

Increasing Area+Delay Overhead MORE SPARES MORE MUX OVERHEAD IN EVERY SWITCH ELEMENT NO SPARES 2 GLOBAL SPARES 1 GLOBAL SPARE 4 GLOBAL SPARES MAY BE IMPRACTICAL !!! 14

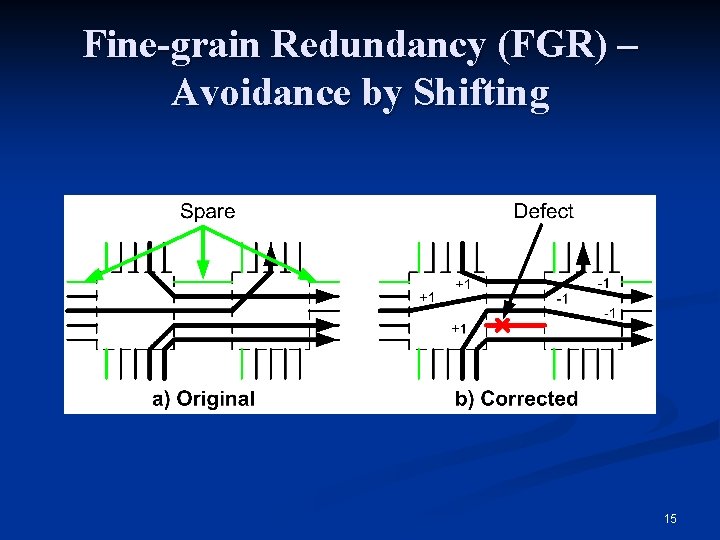

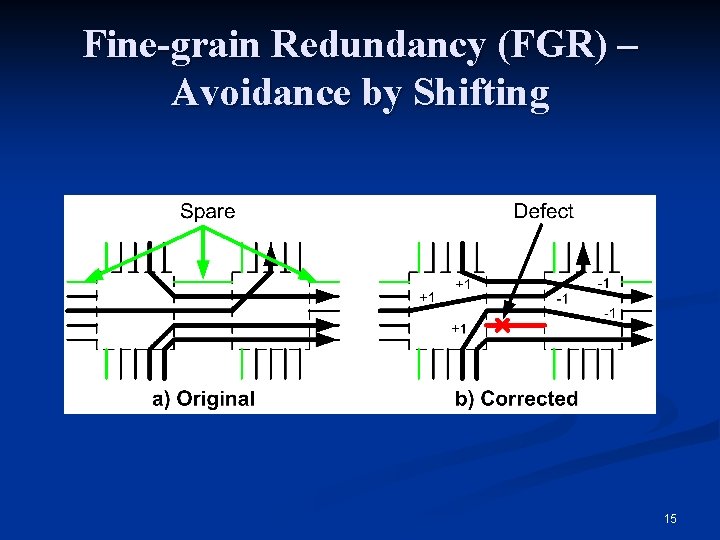

Fine-grain Redundancy (FGR) – Avoidance by Shifting 15

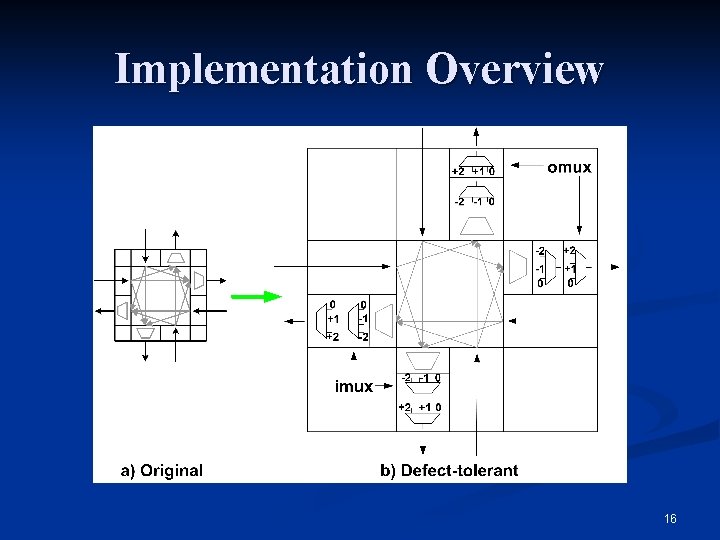

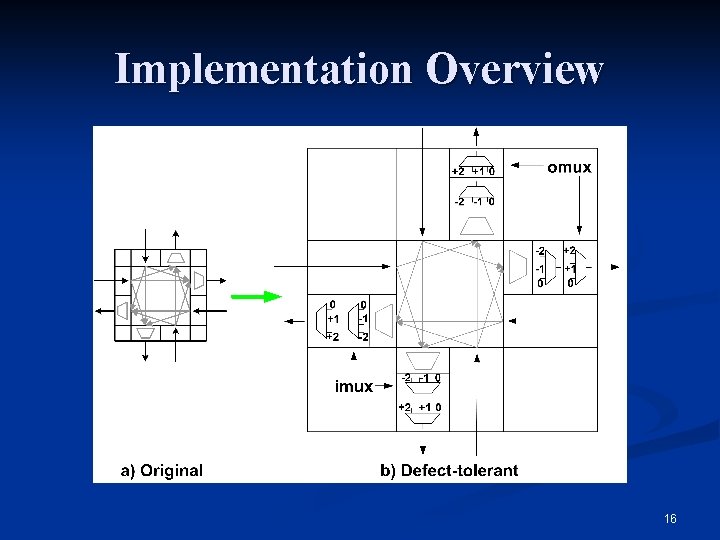

Implementation Overview 16

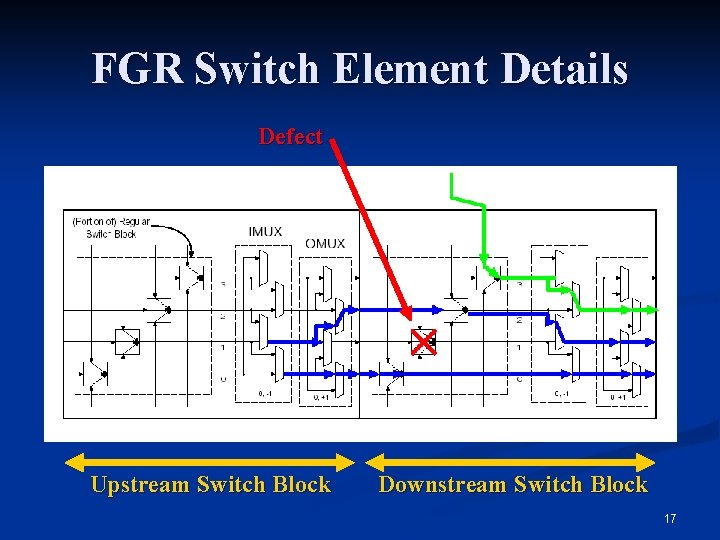

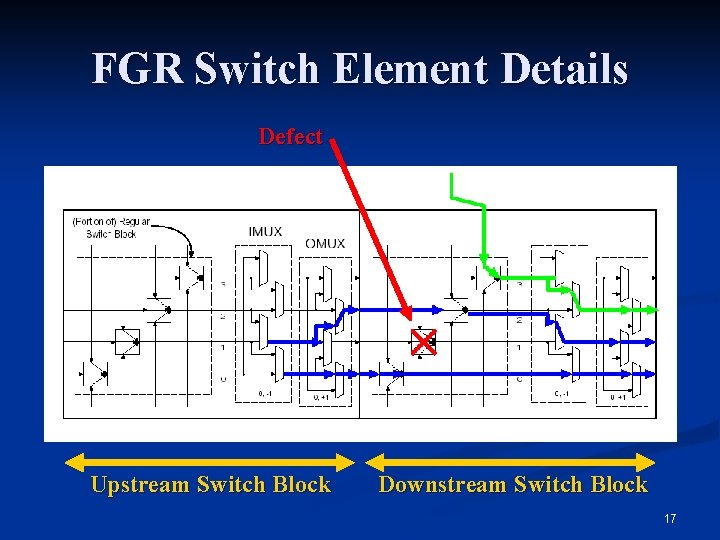

FGR Switch Element Details Defect Upstream Switch Block Downstream Switch Block 17

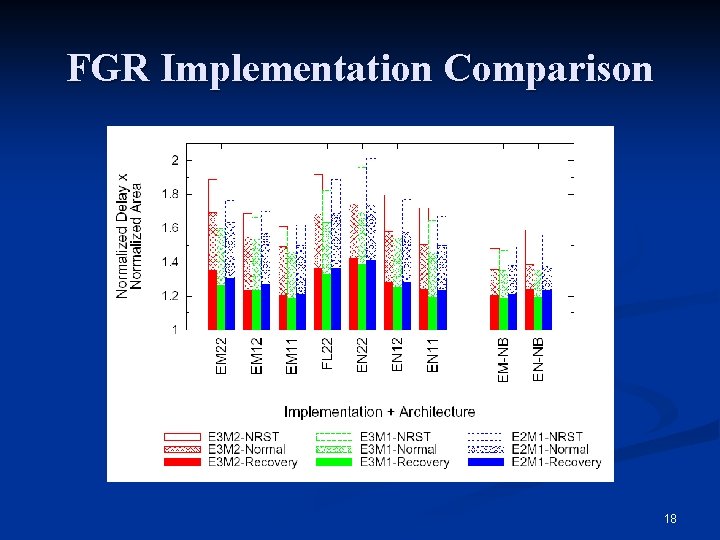

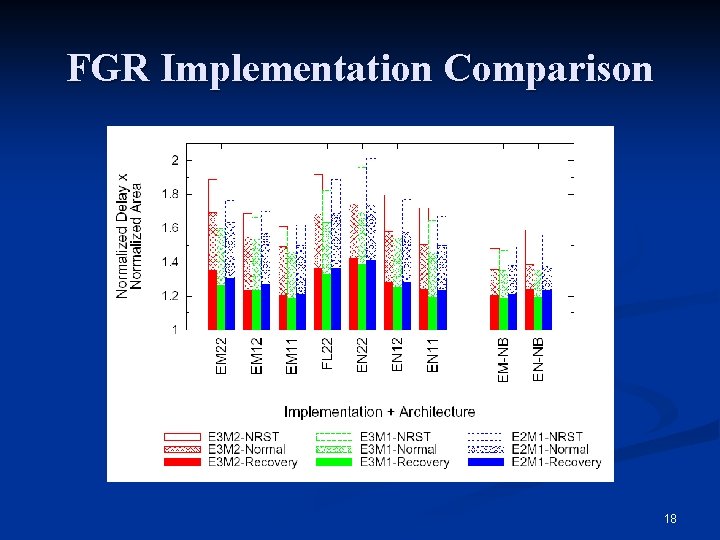

FGR Implementation Comparison 18

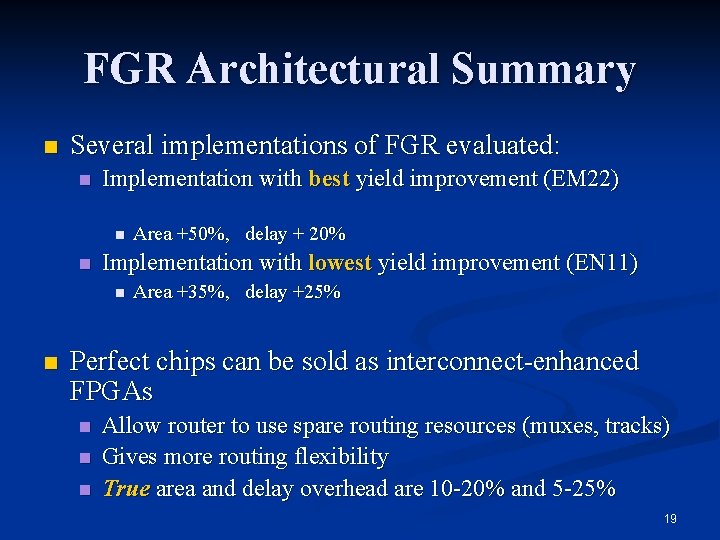

FGR Architectural Summary n Several implementations of FGR evaluated: n Implementation with best yield improvement (EM 22) n n Implementation with lowest yield improvement (EN 11) n n Area +50%, delay + 20% Area +35%, delay +25% Perfect chips can be sold as interconnect-enhanced FPGAs n n n Allow router to use spare routing resources (muxes, tracks) Gives more routing flexibility True area and delay overhead are 10 -20% and 5 -25% 19

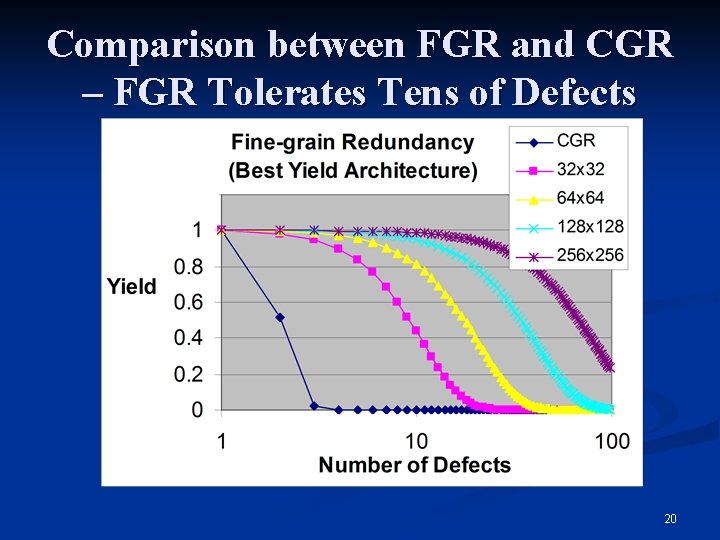

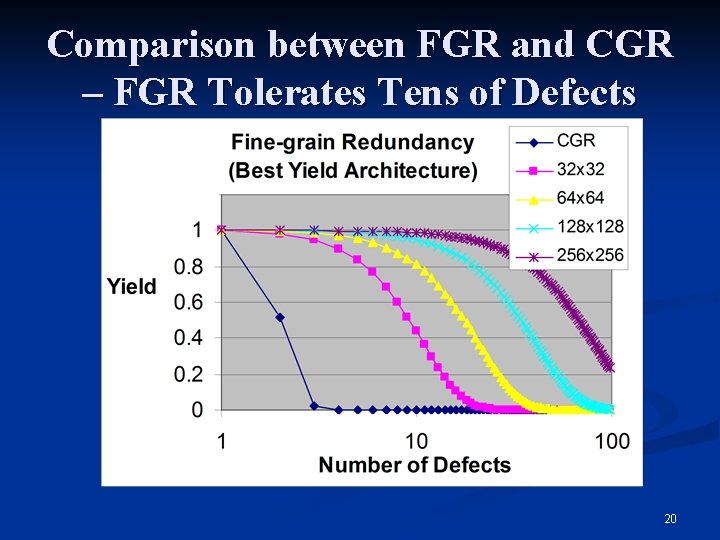

Comparison between FGR and CGR – FGR Tolerates Tens of Defects 20

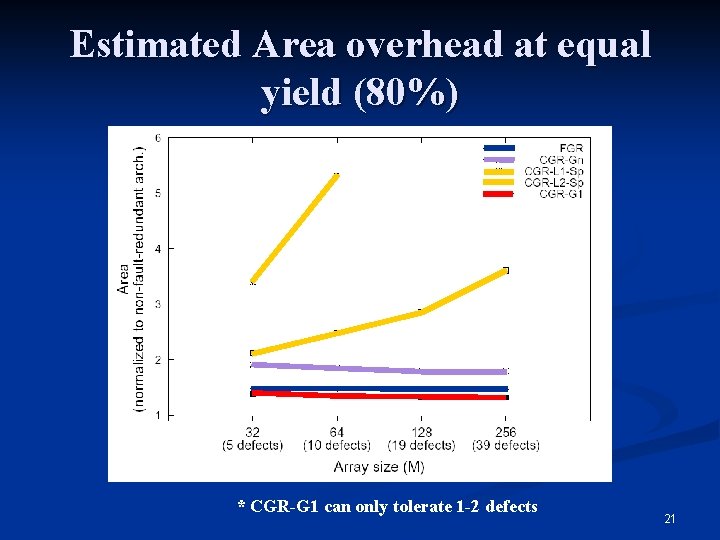

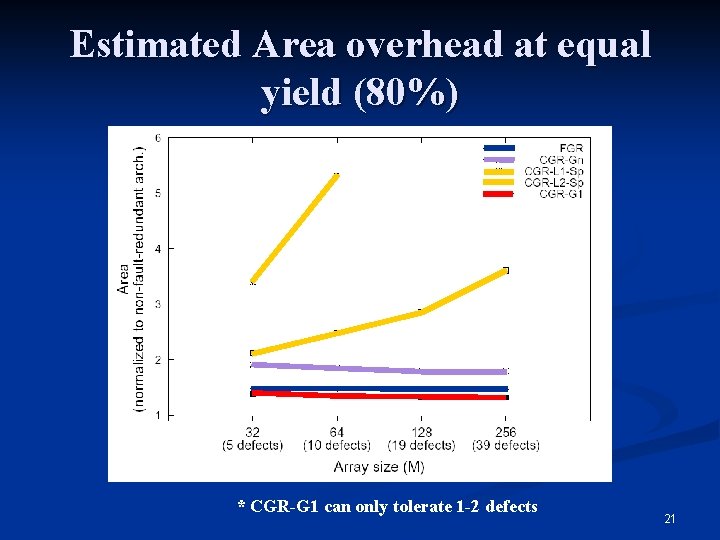

Estimated Area overhead at equal yield (80%) * CGR-G 1 can only tolerate 1 -2 defects 21

Limitations of Study & Architectures n FGR Does not tolerate defects in the logic n Cannot tolerate clustered defects n Requires a detailed fault map n n CGR Assumes that all defects can be corrected with a single row/column n Bypass circuitry is approximated n 22

Conclusions CGR is effective for 1 or 2 defects n FGR meets desired objectives: n Tolerates multiple randomly distributed defects n Defect correction does not perturb timing n Tolerates an increasing number of defects as array size increases n Correction can be applied quickly n n FGR potentially capable of correcting crosstalk faults, but is not explored in thesis 23

Contributions n New fine-grain redundancy architecture Coarse-grain architecture with multiple spare rows and columns n Detailed evaluation of fine-grain and coarse-grain redundancy n n Detailed circuit-level design improved area, delay estimates Yield comparison Publications: n n n Non-redundant architecture paper, at FPT’ 04 Fine-grain architecture paper, to appear in FPL’ 05 Yield comparison paper, to appear in FPT’ 05 24

Thank you! anthonyy@ece. ubc. ca

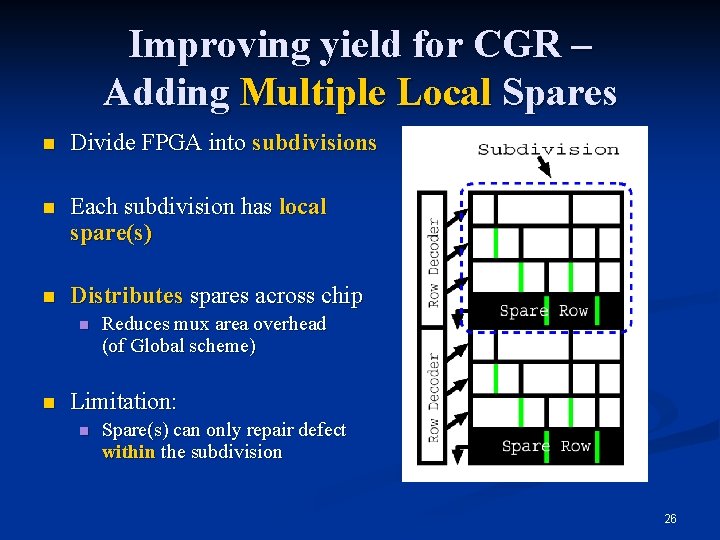

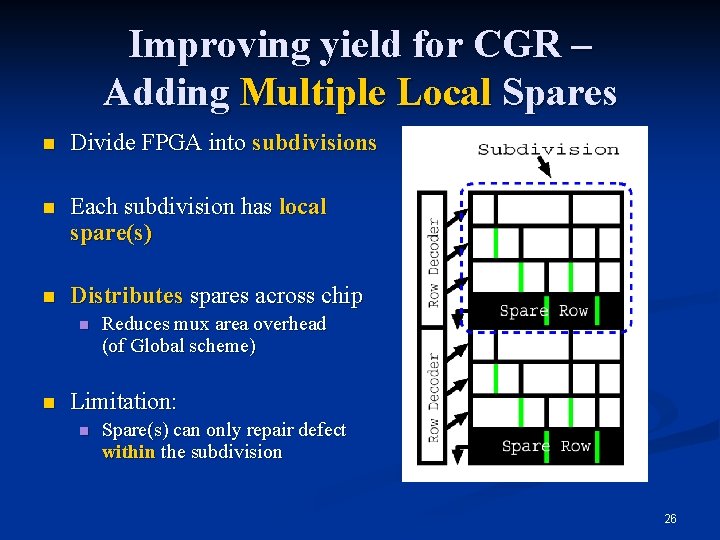

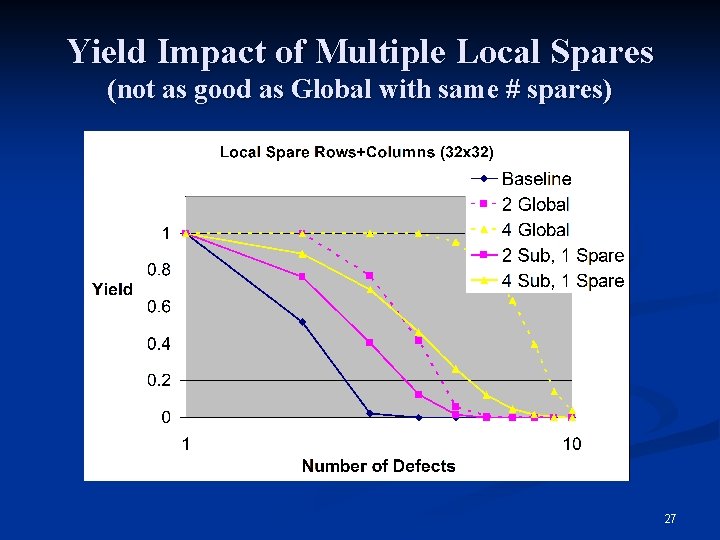

Improving yield for CGR – Adding Multiple Local Spares n Divide FPGA into subdivisions n Each subdivision has local spare(s) n Distributes spares across chip n n Reduces mux area overhead (of Global scheme) Limitation: n Spare(s) can only repair defect within the subdivision 26

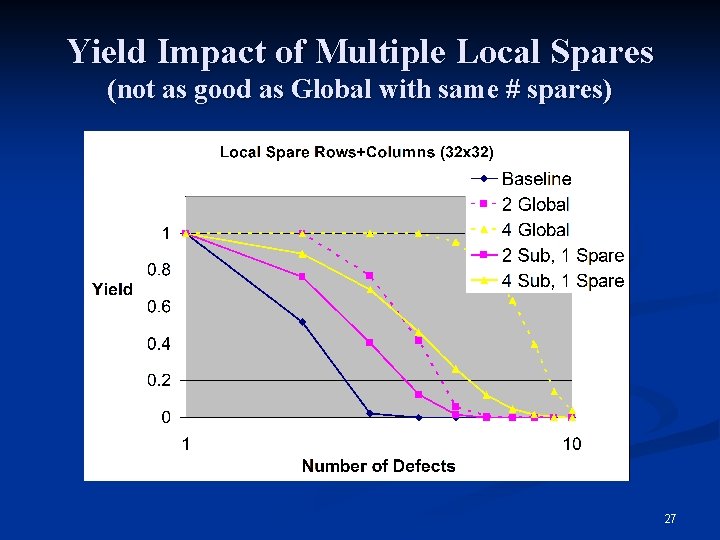

Yield Impact of Multiple Local Spares (not as good as Global with same # spares) 27

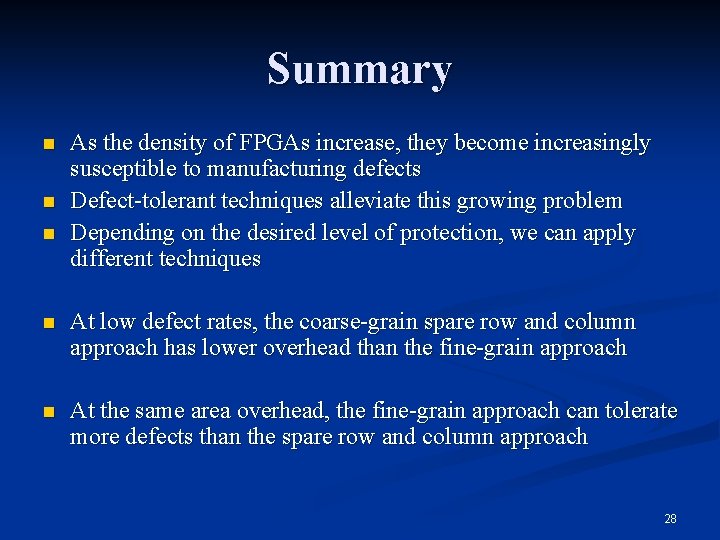

Summary n n n As the density of FPGAs increase, they become increasingly susceptible to manufacturing defects Defect-tolerant techniques alleviate this growing problem Depending on the desired level of protection, we can apply different techniques n At low defect rates, the coarse-grain spare row and column approach has lower overhead than the fine-grain approach n At the same area overhead, the fine-grain approach can tolerate more defects than the spare row and column approach 28