DDR Evolution and Memory Market Trends Bill Gervasi

DDR Evolution and Memory Market Trends Bill Gervasi Technology Analyst wmgervasi@attbi. com

Topics to Cover n The SDRAM Roadmap n DDR-I & DDR-II Comparison n Why DDR-I 400 is Boutique n Memory Modules Changes 2

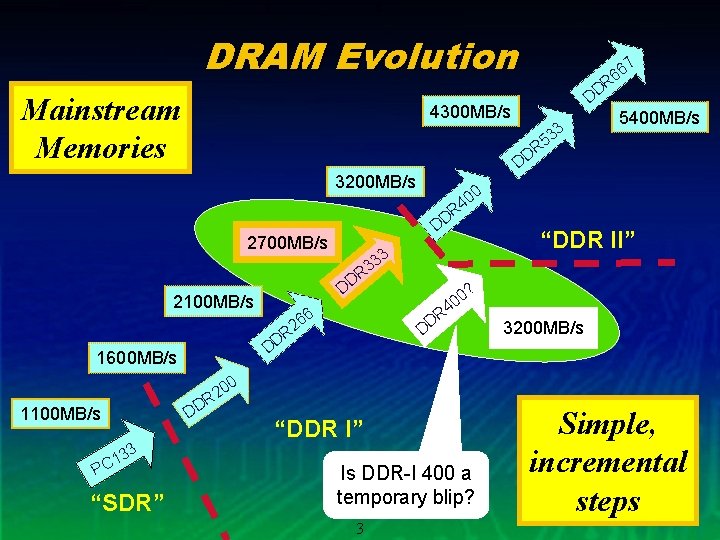

DRAM Evolution Mainstream Memories 5400 MB/s D 6 DD 20 R DD 33 “DDR II” 3 ? 0 40 R DD 6 R 2 1600 MB/s 0 40 R D D 2100 MB/s 3200 MB/s 0 “DDR I” 3 “SDR” 33 5 R D 2700 MB/s 13 PC DD 4300 MB/s 3200 MB/s 1100 MB/s 7 6 6 R Is DDR-I 400 a temporary blip? 3 Simple, incremental steps

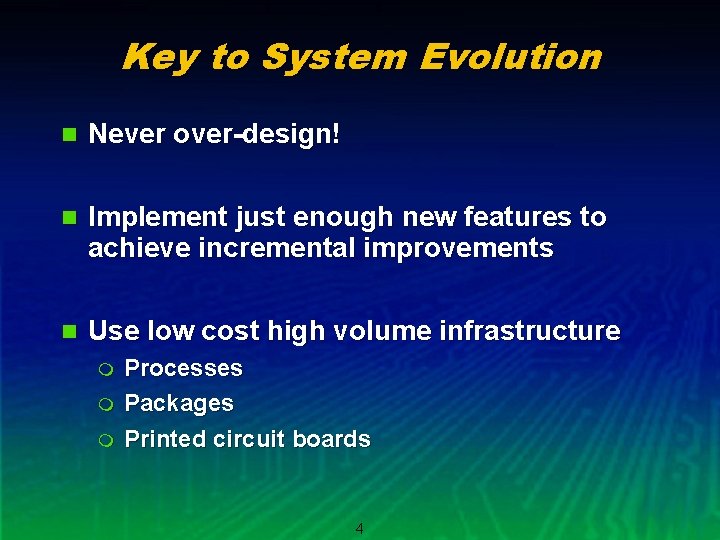

Key to System Evolution n Never over-design! n Implement just enough new features to achieve incremental improvements n Use low cost high volume infrastructure m m m Processes Packages Printed circuit boards 4

Posed To Me at Platform & JEDEX Why will DDR-I at 400 MHz data rate be a “boutique” solution? Why will DDR-II at 400 MHz data rate be a “mainstream” solution? The answer is to look at what new is going into DDR-II 5

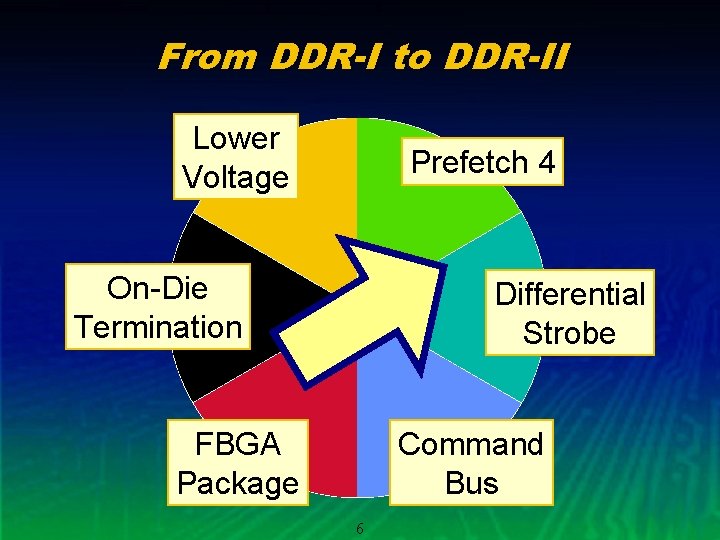

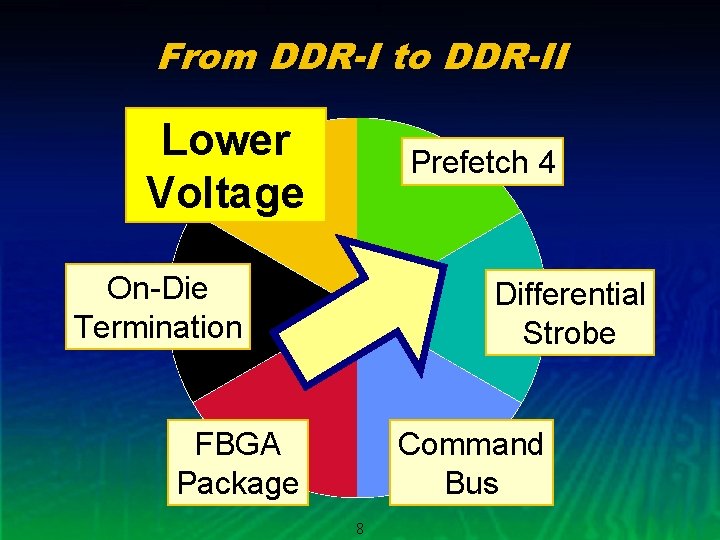

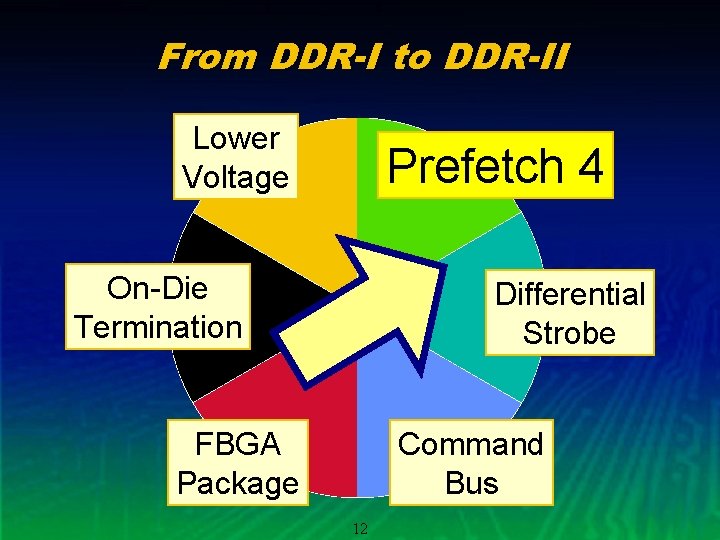

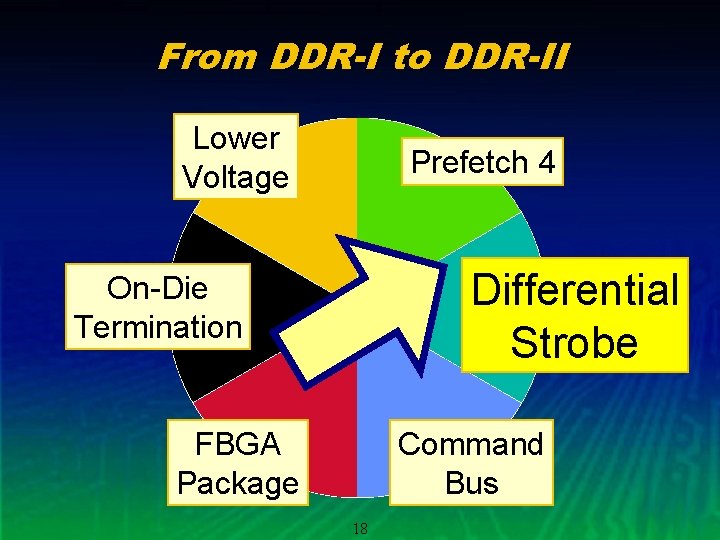

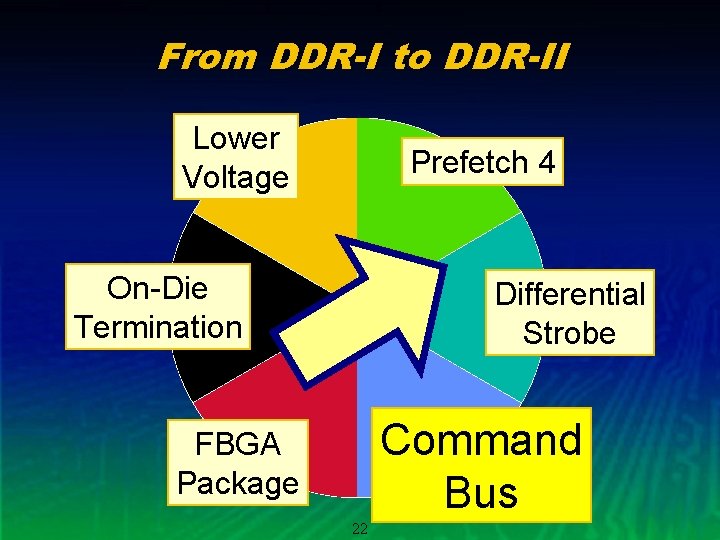

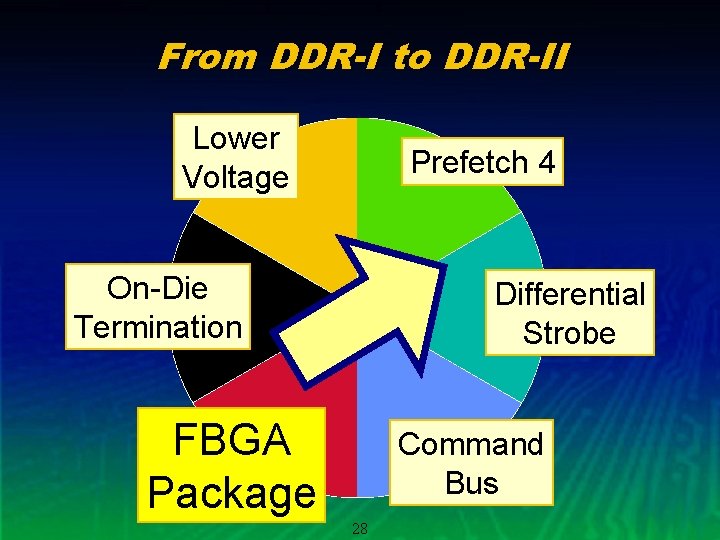

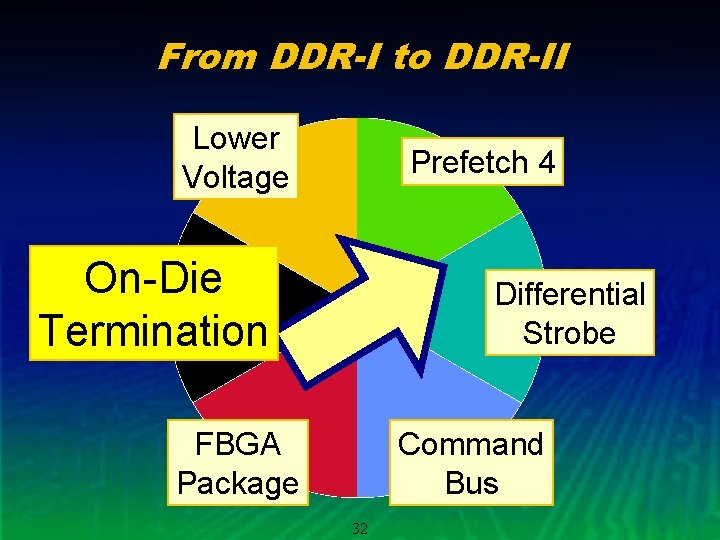

From DDR-I to DDR-II Lower Voltage Prefetch 4 On-Die Termination Differential Strobe FBGA Package Command Bus 6

The DDR II Family n DDR II similarities to DDR I: m n Compatible RAS/CAS command set & protocol DDR II differences from DDR I: m m DDR I = 2. 5 V, DDR II = 1. 8 V Prefetch 4 Differential data strobes Improved command bus utilization: u u m Write latency as a function of read latency Additive latency to help fill holes New FBGA package & memory modules u Tighter package parasitics 7

From DDR-I to DDR-II Lower Voltage Prefetch 4 On-Die Termination Differential Strobe FBGA Package Command Bus 8

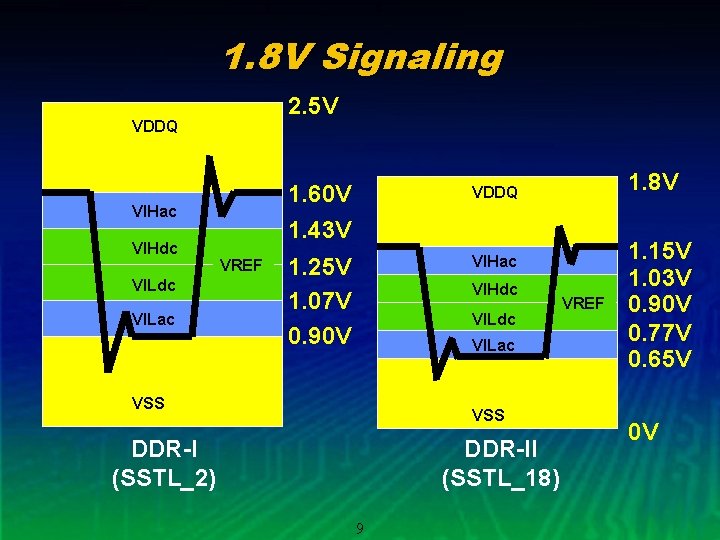

1. 8 V Signaling 2. 5 V VDDQ VIHac VIHdc VILac VREF 1. 60 V 1. 43 V VDDQ 1. 25 V 1. 07 V 0. 90 V VIHac VIHdc VILac VSS DDR-I (SSTL_2) DDR-II (SSTL_18) 9 1. 8 V VREF 1. 15 V 1. 03 V 0. 90 V 0. 77 V 0. 65 V 0 V

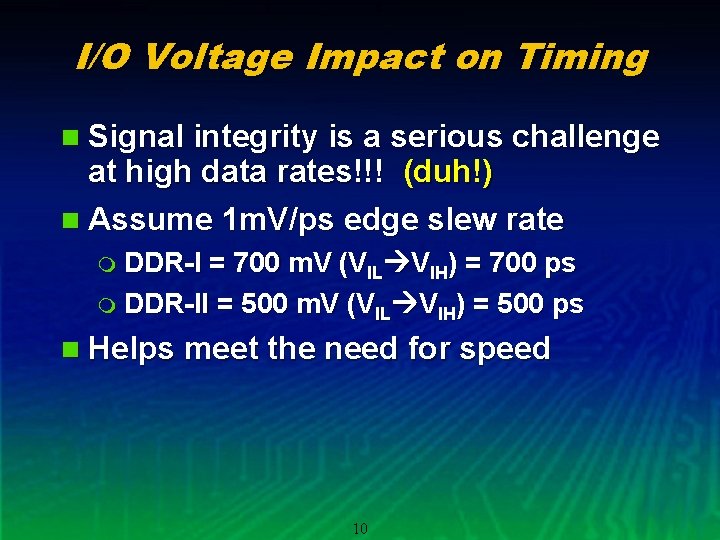

I/O Voltage Impact on Timing n Signal integrity is a serious challenge at high data rates!!! (duh!) n Assume 1 m. V/ps edge slew rate m DDR-I = 700 m. V (VIL VIH) = 700 ps m DDR-II = 500 m. V (VIL VIH) = 500 ps n Helps meet the need for speed 10

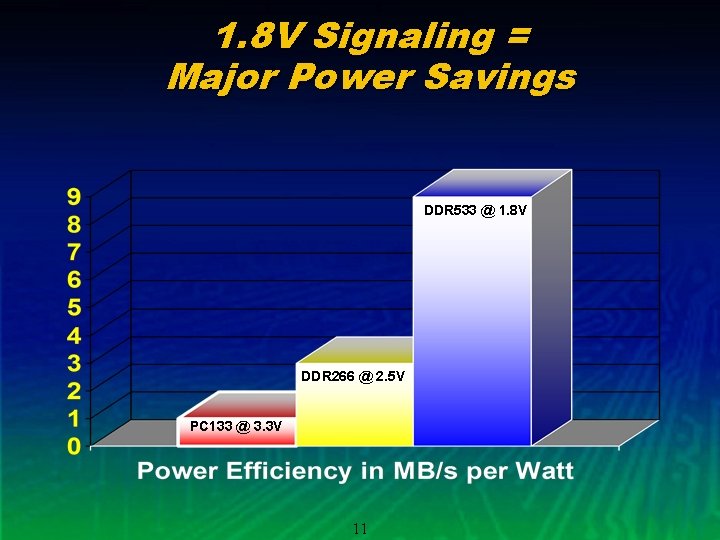

1. 8 V Signaling = Major Power Savings DDR 533 @ 1. 8 V DDR 266 @ 2. 5 V PC 133 @ 3. 3 V 11

From DDR-I to DDR-II Lower Voltage Prefetch 4 4 Prefetch On-Die Termination Differential Strobe FBGA Package Command Bus 12

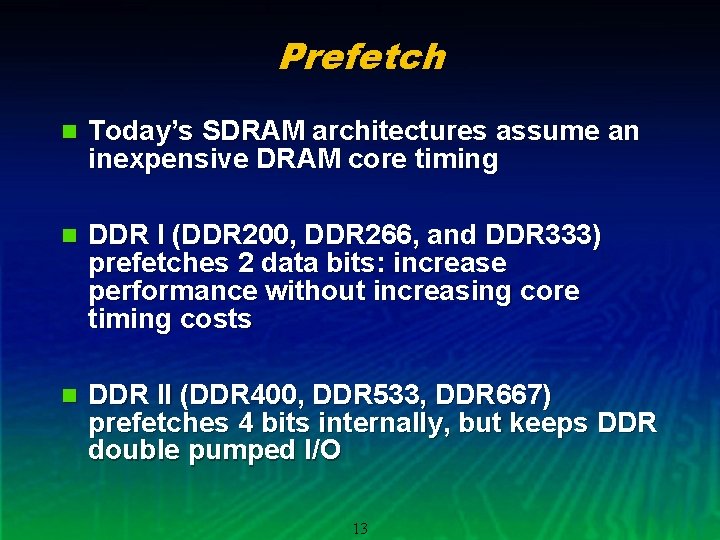

Prefetch n Today’s SDRAM architectures assume an inexpensive DRAM core timing n DDR I (DDR 200, DDR 266, and DDR 333) prefetches 2 data bits: increase performance without increasing core timing costs n DDR II (DDR 400, DDR 533, DDR 667) prefetches 4 bits internally, but keeps DDR double pumped I/O 13

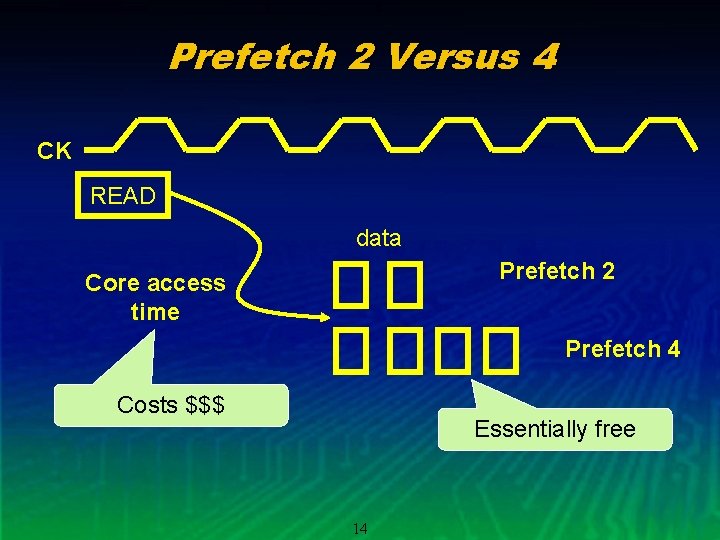

Prefetch 2 Versus 4 CK READ data Prefetch 2 Core access time Prefetch 4 Costs $$$ Essentially free 14

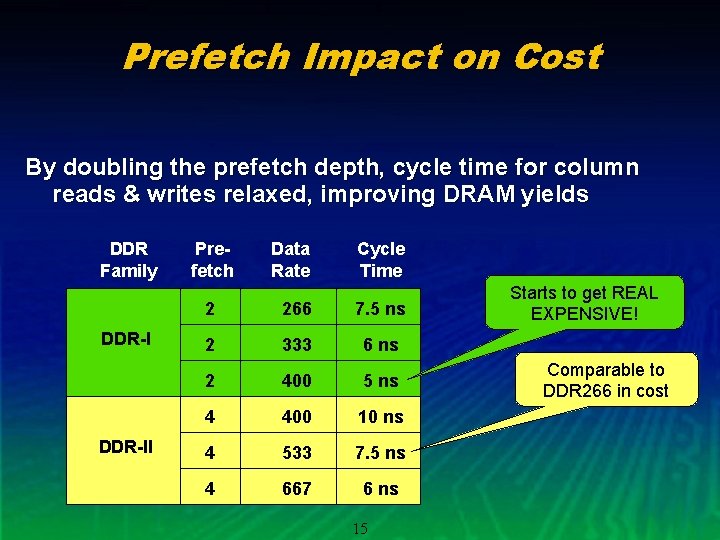

Prefetch Impact on Cost By doubling the prefetch depth, cycle time for column reads & writes relaxed, improving DRAM yields DDR Family DDR-II Prefetch Data Rate Cycle Time 2 266 7. 5 ns 2 333 6 ns 2 400 5 ns 4 400 10 ns 4 533 7. 5 ns 4 667 6 ns 15 Starts to get REAL EXPENSIVE! Comparable to DDR 266 in cost

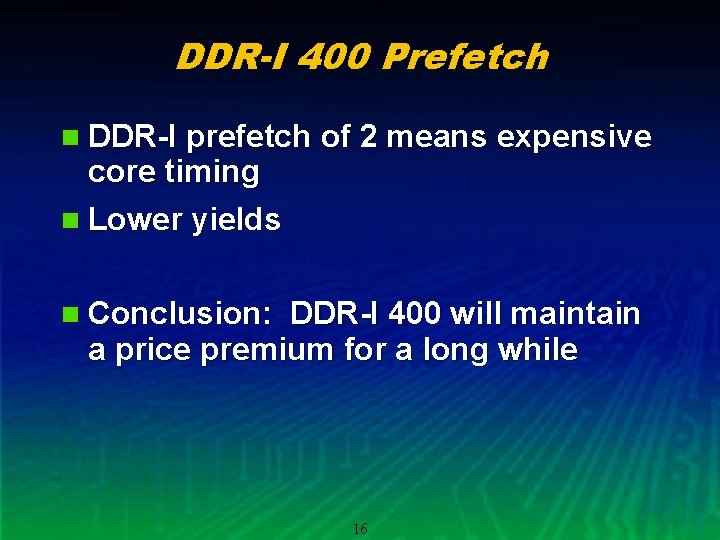

DDR-I 400 Prefetch n DDR-I prefetch of 2 means expensive core timing n Lower yields n Conclusion: DDR-I 400 will maintain a price premium for a long while 16

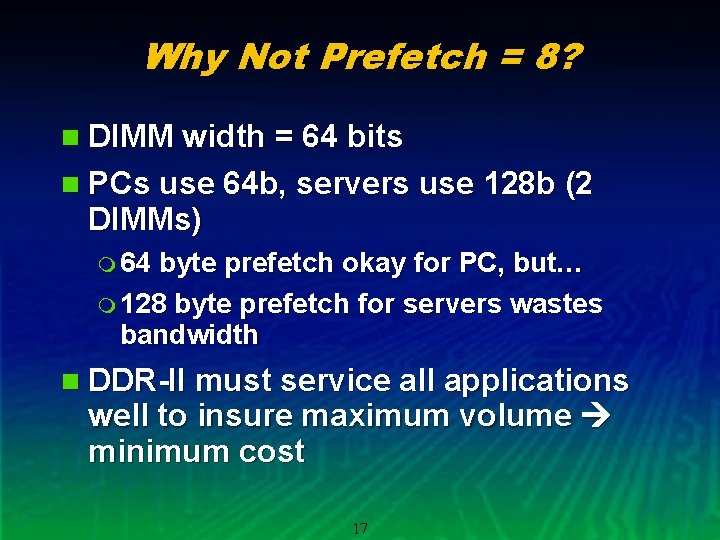

Why Not Prefetch = 8? n DIMM width = 64 bits n PCs use 64 b, servers use 128 b (2 DIMMs) m 64 byte prefetch okay for PC, but… m 128 byte prefetch for servers wastes bandwidth n DDR-II must service all applications well to insure maximum volume minimum cost 17

From DDR-I to DDR-II Lower Voltage Prefetch 4 Differential Strobe On-Die Termination FBGA Package Command Bus 18

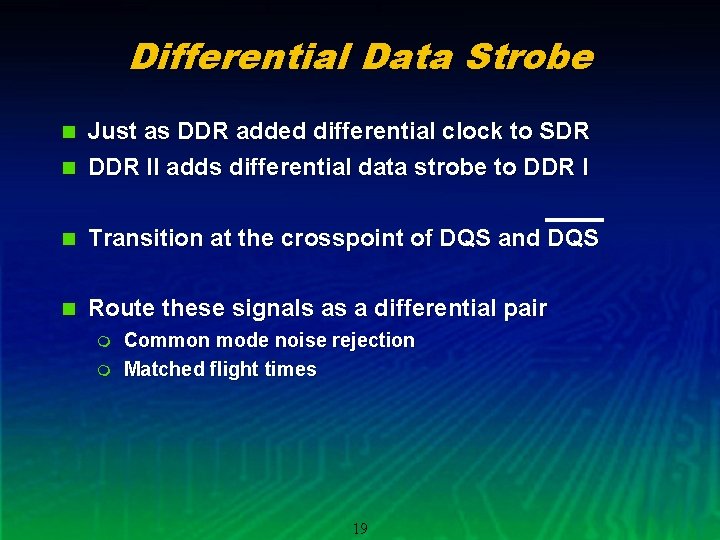

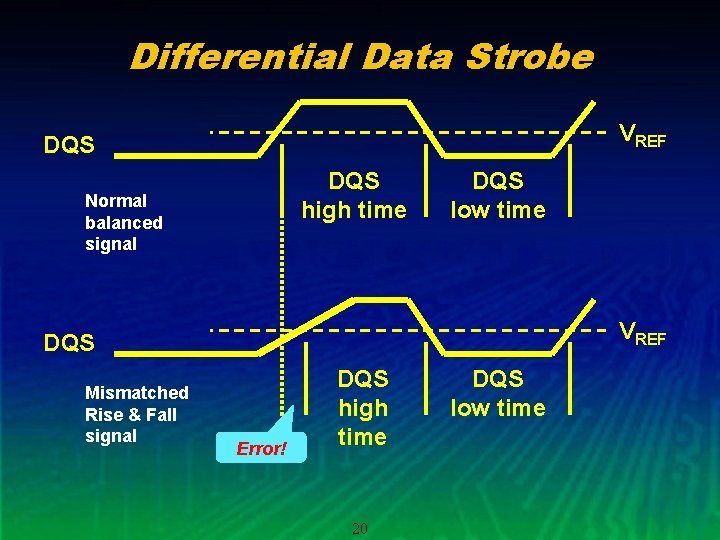

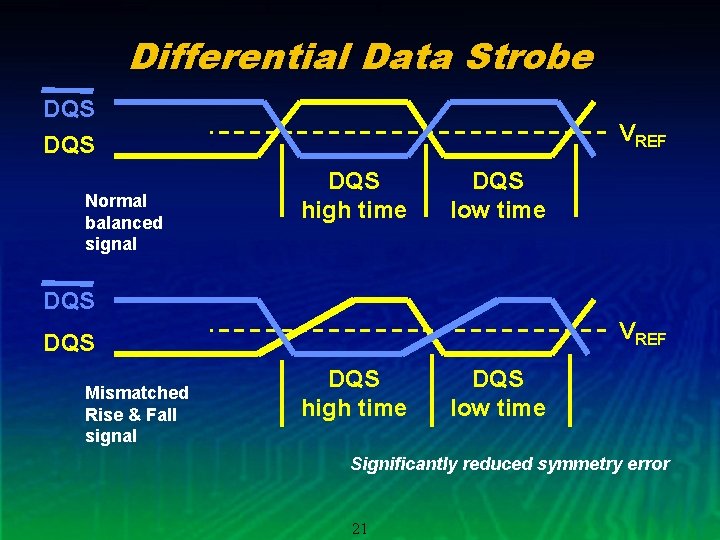

Differential Data Strobe Just as DDR added differential clock to SDR n DDR II adds differential data strobe to DDR I n n Transition at the crosspoint of DQS and DQS n Route these signals as a differential pair m m Common mode noise rejection Matched flight times 19

Differential Data Strobe VREF DQS high time Normal balanced signal DQS low time VREF DQS Mismatched Rise & Fall signal Error! DQS high time 20 DQS low time

Differential Data Strobe DQS VREF DQS Normal balanced signal DQS high time DQS low time DQS VREF DQS Mismatched Rise & Fall signal DQS high time DQS low time Significantly reduced symmetry error 21

From DDR-I to DDR-II Lower Voltage Prefetch 4 On-Die Termination Differential Strobe Command Bus FBGA Package 22

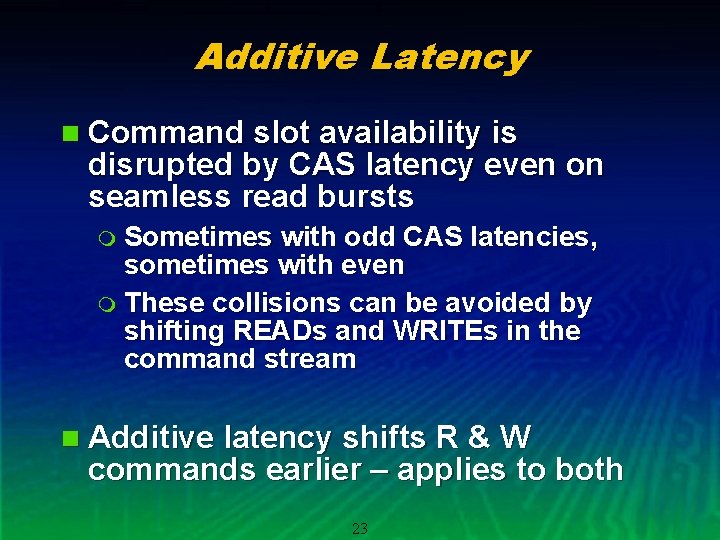

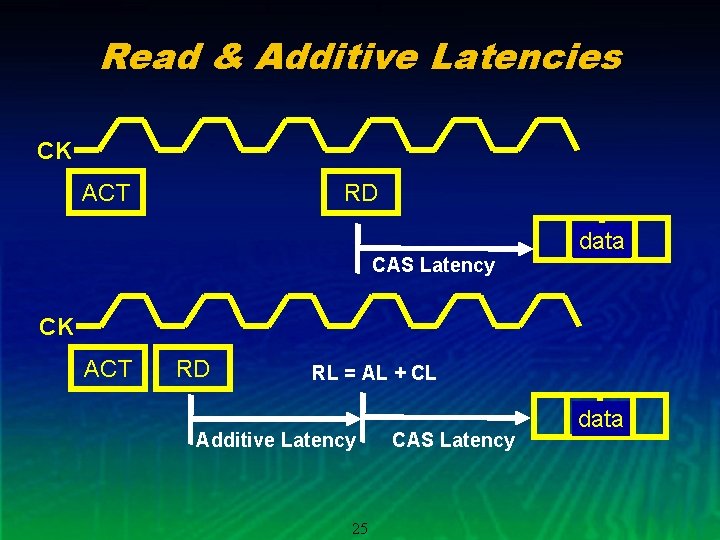

Additive Latency n Command slot availability is disrupted by CAS latency even on seamless read bursts m Sometimes with odd CAS latencies, sometimes with even m These collisions can be avoided by shifting READs and WRITEs in the command stream n Additive latency shifts R & W commands earlier – applies to both 23

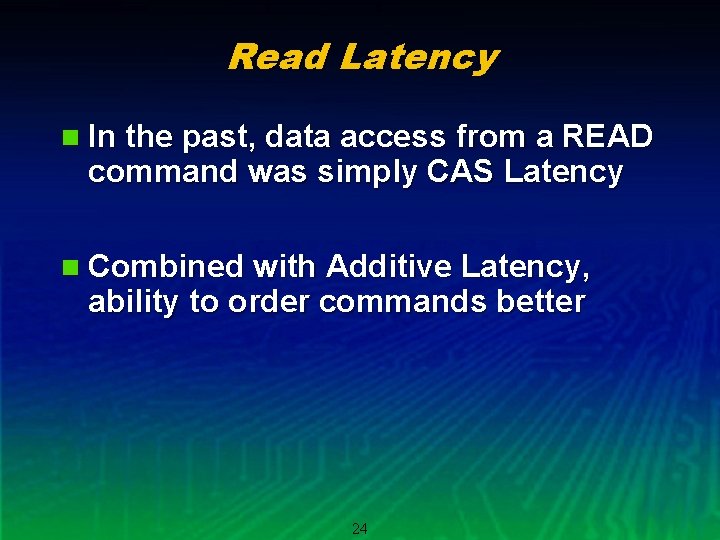

Read Latency n In the past, data access from a READ command was simply CAS Latency n Combined with Additive Latency, ability to order commands better 24

Read & Additive Latencies CK ACT RD CAS Latency data CK ACT RD RL = AL + CL Additive Latency 25 CAS Latency data

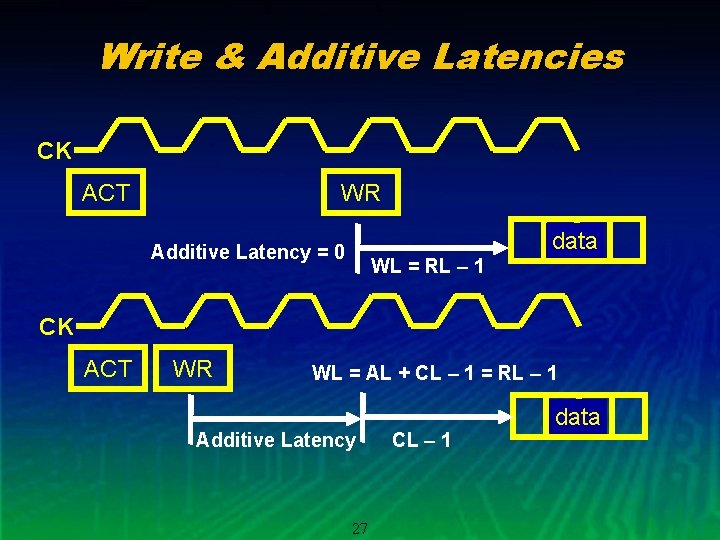

Write Latency n Complex controllers had collisions between command slots and data bus availability n These are eliminated in DDR II by setting Write Latency = Read Latency – 1 n Combined with Additive Latency, lots of flexibility in ordering commands 26

Write & Additive Latencies CK ACT WR data Additive Latency = 0 WL = RL – 1 CK ACT WR WL = AL + CL – 1 = RL – 1 Additive Latency 27 CL – 1 data

From DDR-I to DDR-II Lower Voltage Prefetch 4 On-Die Termination Differential Strobe FBGA Package Command Bus 28

Managing Power (and its relationship to packaging) 29

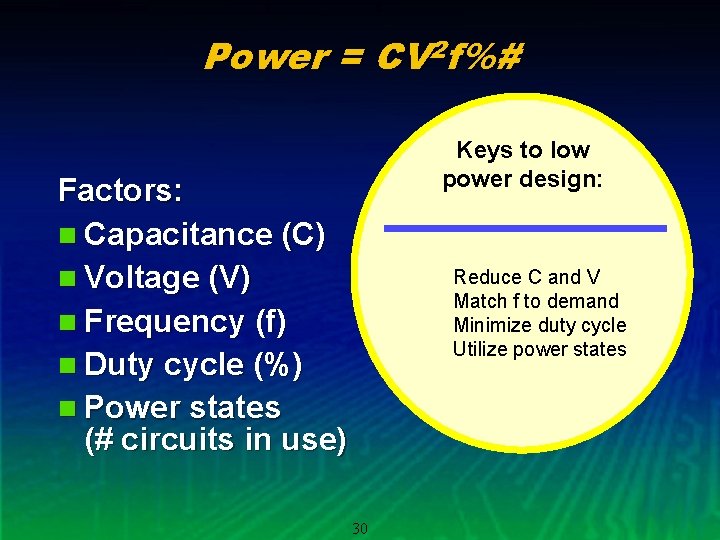

Power = CV 2 f%# Keys to low power design: Factors: n Capacitance (C) n Voltage (V) n Frequency (f) n Duty cycle (%) n Power states (# circuits in use) Reduce C and V Match f to demand Minimize duty cycle Utilize power states 30

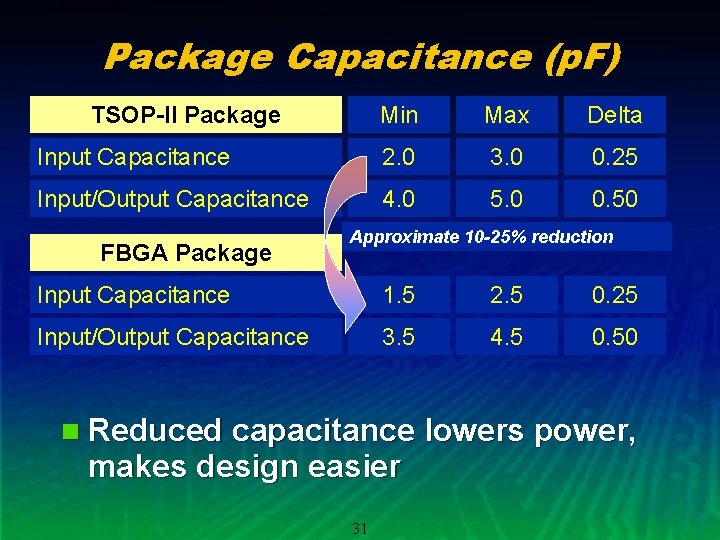

Package Capacitance (p. F) TSOP-II Package Min Max Delta Input Capacitance 2. 0 3. 0 0. 25 Input/Output Capacitance 4. 0 5. 0 0. 50 FBGA Package Approximate 10 -25% reduction Input Capacitance 1. 5 2. 5 0. 25 Input/Output Capacitance 3. 5 4. 5 0. 50 n Reduced capacitance lowers power, makes design easier 31

From DDR-I to DDR-II Lower Voltage Prefetch 4 On-Die Termination Differential Strobe FBGA Package Command Bus 32

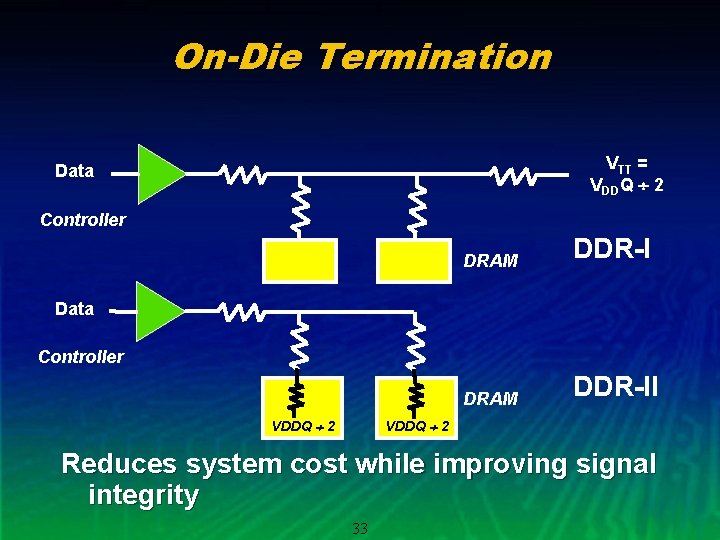

On-Die Termination VTT = VDDQ ¸ 2 Data Controller DRAM DDR-II Data Controller VDDQ ¸ 2 Reduces system cost while improving signal integrity 33

DDR-I 400 Issues n DDR-I 400 systems are hard to design robustly n No vendor interoperability guarantees n DDR-II offers other performance benefits besides peak data rate n DDR-I 400 runs hot n Exists because DDR-II is late 34

DDR-I 400 Conclusion n The JEDEC roadmap represents the industry focus for mainstream products m DDR-I tops out at 333 MHz data rate m DDR-II starts at 400 MHz data rate n This DOES NOT mean that DDR-I at 400 MHz data rate will not ship in volume n It DOES mean that there will be price premiums for this speed bin 35

Modules 36

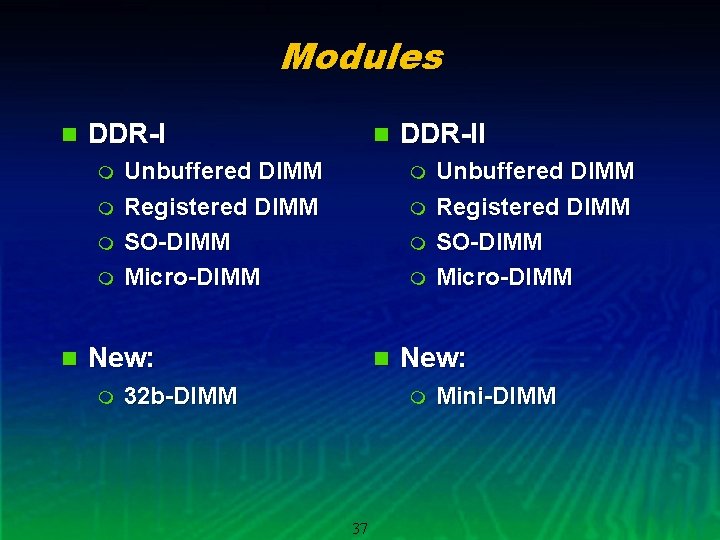

Modules n DDR-I m m n n Unbuffered DIMM Registered DIMM SO-DIMM Micro-DIMM m m New: m DDR-II n 32 b-DIMM New: m 37 Unbuffered DIMM Registered DIMM SO-DIMM Micro-DIMM Mini-DIMM

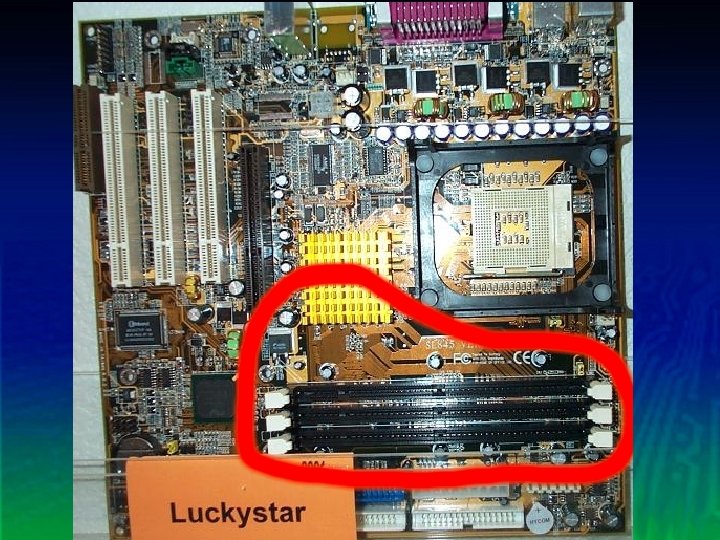

Unbuffered & Registered DIMMs n Same physical size: 133 mm (5. 25”) n New socket; more pins, tighter pitch n “Same plane referencing” pinout n Target markets unchanged m Servers m Workstations m Full form factor desktop PC 38

SO-DIMM n Same size as before: 67. 6 x 31. 75 mm n Same 200 pin socket as before m Uses 1. 8 V key position n No longer supports x 72 (ECC) or registered n Target markets change: m DDR-I: Mobile, blade server m DDR-II: Does not support blade server, small form factor PC possible 39

Mini-DIMM n New to DDR-II… no DDR-I equivalent n Supports x 72 (ECC) and registered n Larger than SO-DIMM: 82 mm n New socket required n Target market: blade server n Intent is to support stacking m If anyone figures out how to stack BGA 40

Micro-DIMM n Same footprint: 45. 5 x 30 -ish mm n New connector m High pin count mezzanine connector m Two part: one on mobo, one on module m 0. 4 mm pitch 41

32 b-DIMM n New to DDR-I… no DDR-II version yet n X 32 only n Ultra low cost n New connector n Target market: peripherals, e. g. printers 42

What Can Change? 43

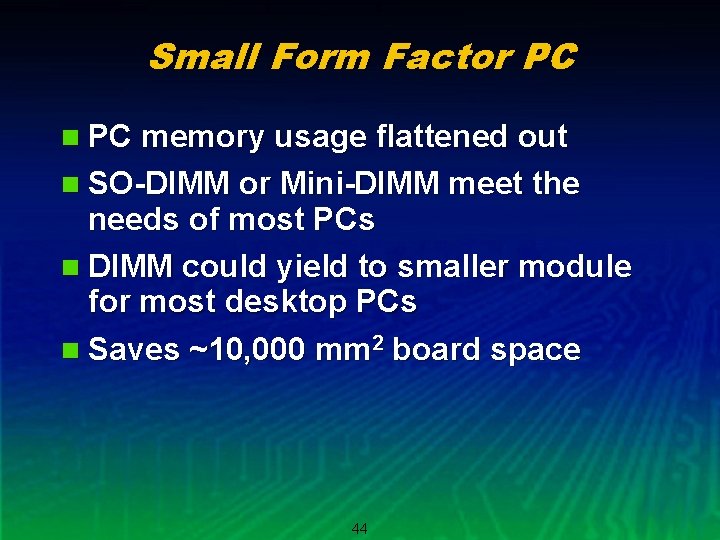

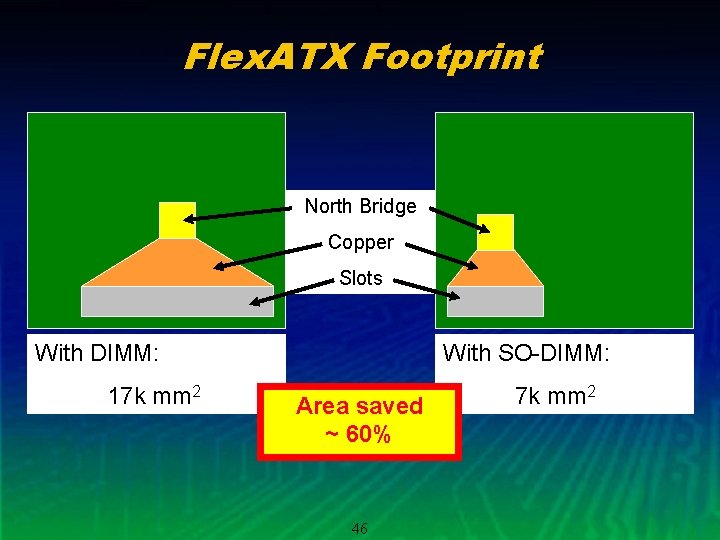

Small Form Factor PC n PC memory usage flattened out n SO-DIMM or Mini-DIMM meet the needs of most PCs n DIMM could yield to smaller module for most desktop PCs n Saves ~10, 000 mm 2 board space 44

45

Flex. ATX Footprint North Bridge Copper Slots With DIMM: 17 k mm 2 With SO-DIMM: Area saved ~ 60% 46 7 k mm 2

Mobile n DDR-I SO-DIMM had 2 X capacity of Micro-DIMM (assuming TSOP) n DDR-II Micro-DIMM has same capacity as SO-DIMM n Differences: m SO-DIMM supports 1 st generation die m Micro-DIMM connector change scary n However, possible that the Micro- DIMM displaces the SO-DIMM for all mobile market 47

Small Module Capacity 48

Summary n DDR-II offers many incremental improvements over DDR-I m Lower voltage, higher prefetch, differential strobes, more efficient command bus, higher quality package, on-die termination DDR-I 400 likely to stay a profitable niche n New module configurations may impact markets – watch for growth of Micro-DIMM, possible shrink of SO-DIMM in DDR-II generation n 49

Thank You 50

- Slides: 50