Datapaths for Instruction Fetch and Memory Accesses CS

![C version temp = A[j]; for (i = j; i > 0; i--) A[i] C version temp = A[j]; for (i = j; i > 0; i--) A[i]](https://slidetodoc.com/presentation_image_h2/00b7672845211d57affa270e1faf7911/image-5.jpg)

- Slides: 12

Datapaths for Instruction Fetch and Memory Accesses CS 3432 Fall 2020 Shirley Moore, Instructor svmoore@utep. edu November 3, 2020 1

Schedule for Today’s Class • Announcements • Make appointments to discuss midterm exam at https: //calendly. com/svmoore (choose 15 or 30 minute appointment) • Midterm retake exams (3 parts) will be ready Thursday • Drop deadline extended to December 3, drops this semester will not count towards 6 course drop limit; no decision yet on S/U grading option • • • First paragraph on p. A-64 explains why DRAM is slower than SRAM Finish array addressing review problems from last class (10 minutes) Memory Design Problems (20 minutes) Instruction fetch datapath (20 minutes) load/store datapath (20 minutes) Wrapup 2

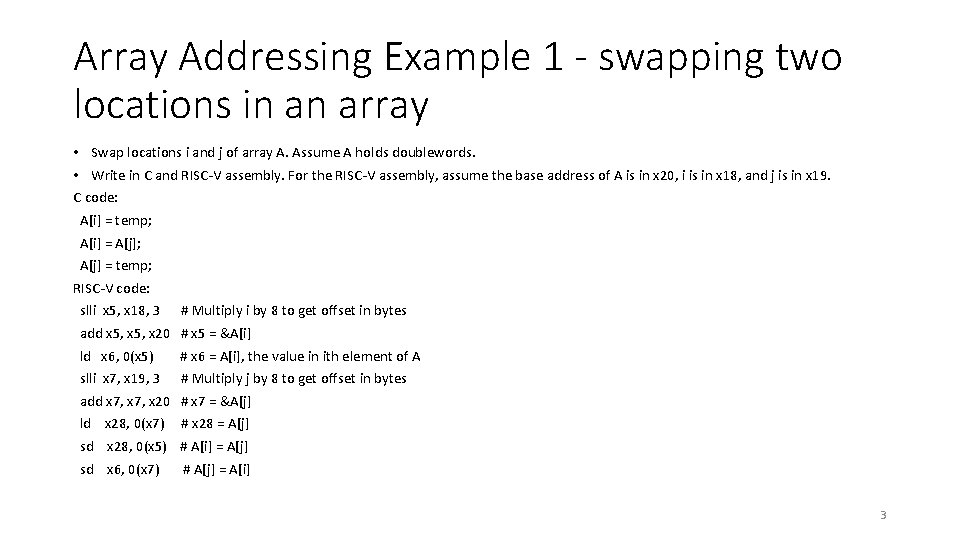

Array Addressing Example 1 - swapping two locations in an array • Swap locations i and j of array A. Assume A holds doublewords. • Write in C and RISC-V assembly. For the RISC-V assembly, assume the base address of A is in x 20, i is in x 18, and j is in x 19. C code: A[i] = temp; A[i] = A[j]; A[j] = temp; RISC-V code: slli x 5, x 18, 3 # Multiply i by 8 to get offset in bytes add x 5, x 20 # x 5 = &A[i] ld x 6, 0(x 5) # x 6 = A[i], the value in ith element of A slli x 7, x 19, 3 # Multiply j by 8 to get offset in bytes add x 7, x 20 # x 7 = &A[j] ld x 28, 0(x 7) # x 28 = A[j] sd x 28, 0(x 5) # A[i] = A[j] sd x 6, 0(x 7) # A[j] = A[i] 3

Example 2 - Bubble the value in location j of array A up to location 0. • Element in location j-1 should move to location j, element in location j -2 should move to location j-1, etc. • Write in both C and assembly. inside the loop in C: a[i] = a[i-1] in RISC-V, don’t do the array indexing inside the loop; instead set up a pointer in a register to where a[i] is and decrement by 8 each time through the loop until it gets to the base address. 4

![C version temp Aj for i j i 0 i Ai C version temp = A[j]; for (i = j; i > 0; i--) A[i]](https://slidetodoc.com/presentation_image_h2/00b7672845211d57affa270e1faf7911/image-5.jpg)

C version temp = A[j]; for (i = j; i > 0; i--) A[i] = A[i-1]; A[0]= temp; RISC-V version Assume j is in x 18 and the base address of A is in x 20. addi slli add ld loop: beq ld sd addi jal done: sd x 5, x 18, 0 x 5, 3 x 5, x 20 x 6, 0(x 5) x 5, x 20, done x 7, -8(x 5) x 7, 0(x 5) x 5, -8 x 0, loop x 6, 0(x 20) # x 5 = j # Mutliply by 8 to get offset in bytes # x 5 = &A[j] # x 6 = temp = A[j] # exit loop if we have reached &A[0] # x 7 = A[i-1] # A[i] = A[i-1] # A[0] = temp = A[j] 5

Example 3 - Remove a value from a linked list • Assume a linked list where nodes have the following type: struct node { long int val; long int *next; } • Write the code to remove a specified value from the list if it exists. Write in both C and RISC-V assembly. For the RISC-V assembly, assume the address of the head node of the list is in register x 20 and that the value to remove is in x 18. 6

Example 3 - C version // Remove value from list pointed to by head. struct node *head, *current, *prev; if (head != NULL) { prev = head; if (head->val == value) { head = head->next; free(prev); } else { current = prev->next; while (current != NULL && current->val != value) { prev = current; current = current->next; } if (current != NULL) { prev->next = current->next; free(current); } } } Try to write RISC-V version for next class. Assume we can call a procedure named free that takes an address and the number of bytes to free as arguments and returns 0 if successful and -1 otherwise. 7

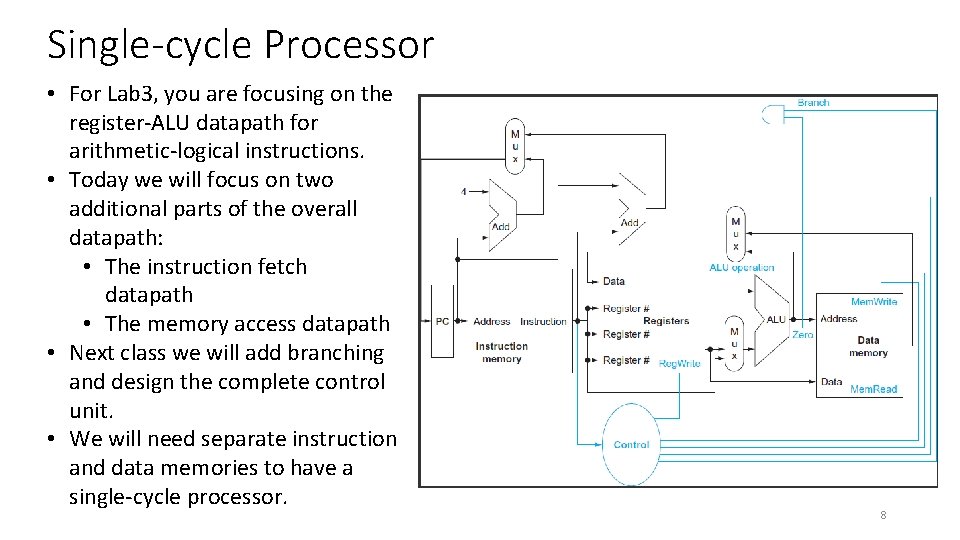

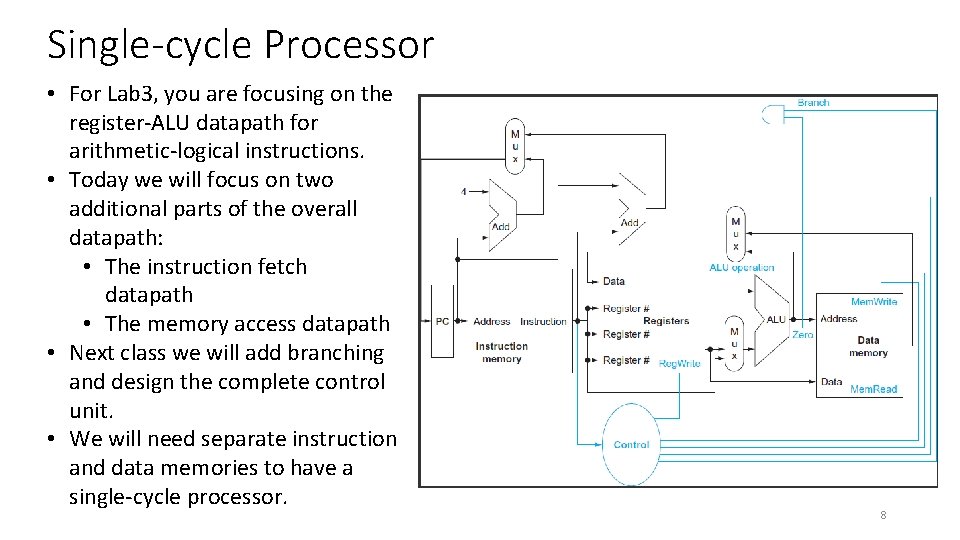

Single-cycle Processor • For Lab 3, you are focusing on the register-ALU datapath for arithmetic-logical instructions. • Today we will focus on two additional parts of the overall datapath: • The instruction fetch datapath • The memory access datapath • Next class we will add branching and design the complete control unit. • We will need separate instruction and data memories to have a single-cycle processor. 8

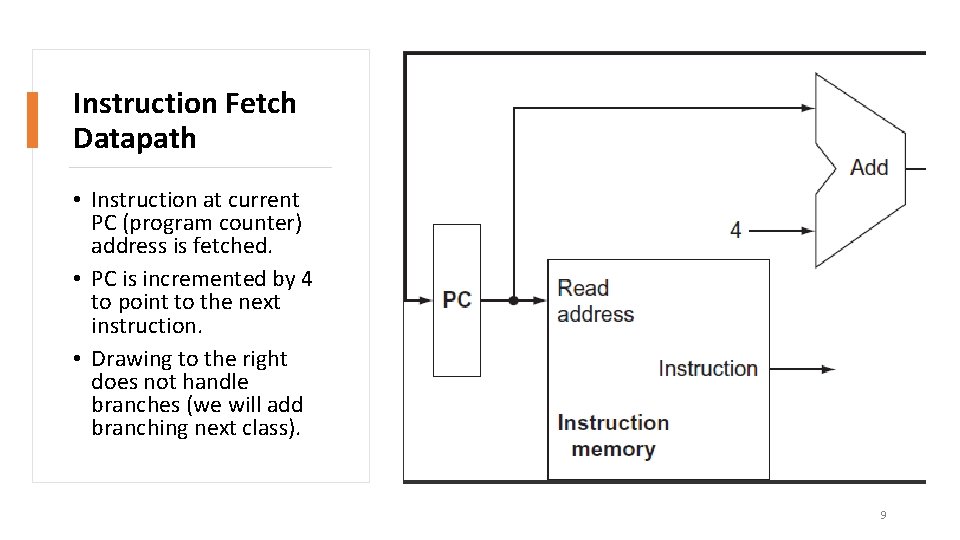

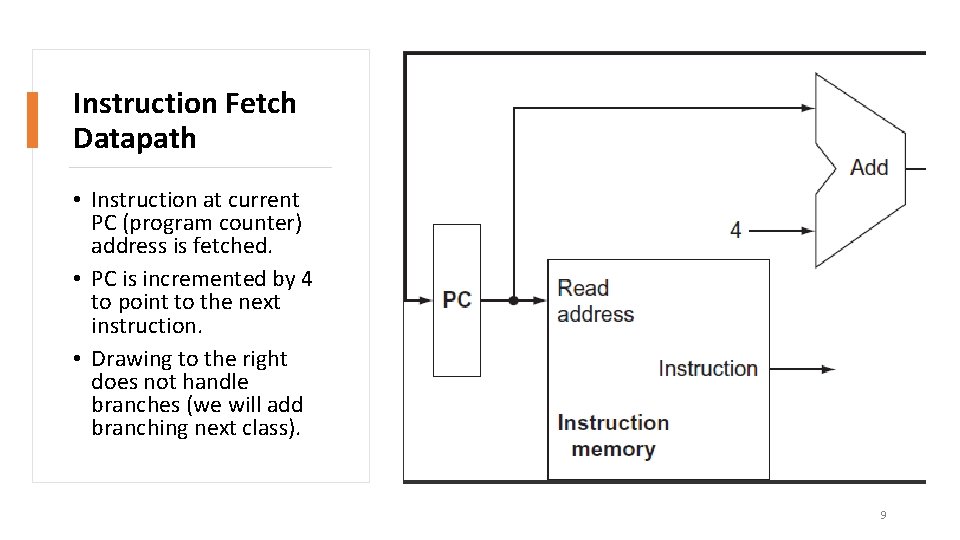

Instruction Fetch Datapath • Instruction at current PC (program counter) address is fetched. • PC is incremented by 4 to point to the next instruction. • Drawing to the right does not handle branches (we will add branching next class). 9

Let’s build the instruction fetch path in Logisim • Need separate instruction and data memories since we are implementing a single-cycle processor • Instruction memory should have 32 -bit read data width and byte addressability. • Program counter (PC) • Special-purpose register that always contains the address of the next instruction to be fetched • How many bits do we need for the PC? • Adder • What bit width is required for the adder? • To what should the second input be hardwired? • Logisim demo • instpath 1. circ • fact 6. txt 10

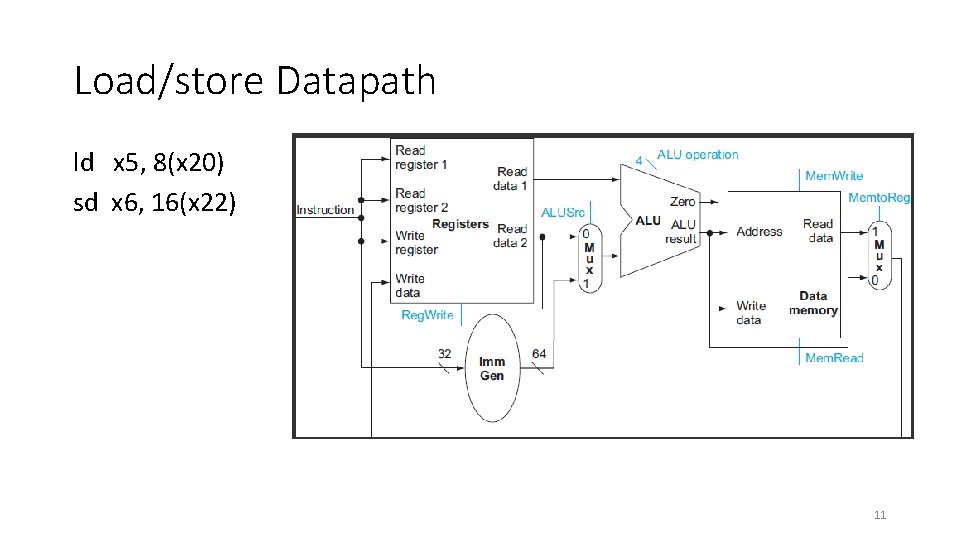

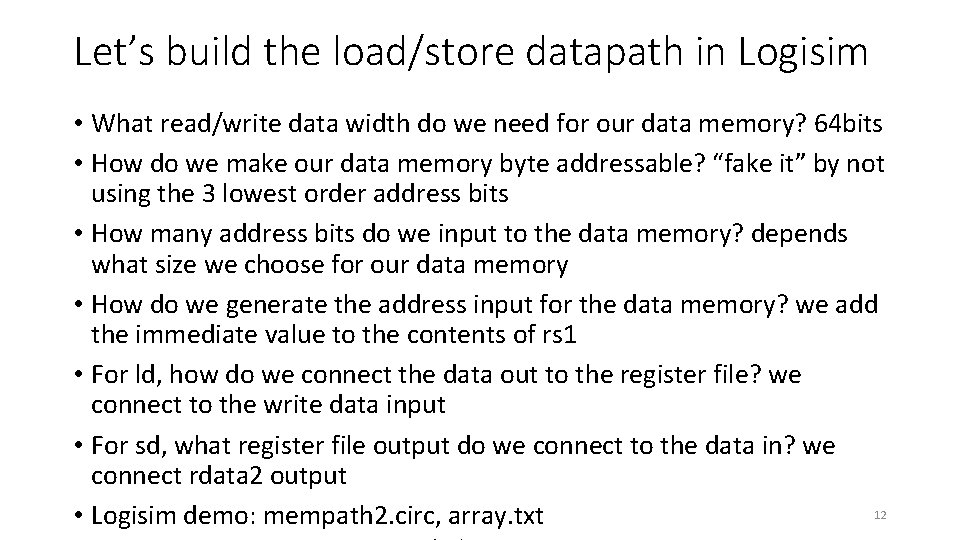

Load/store Datapath ld x 5, 8(x 20) sd x 6, 16(x 22) 11

Let’s build the load/store datapath in Logisim • What read/write data width do we need for our data memory? 64 bits • How do we make our data memory byte addressable? “fake it” by not using the 3 lowest order address bits • How many address bits do we input to the data memory? depends what size we choose for our data memory • How do we generate the address input for the data memory? we add the immediate value to the contents of rs 1 • For ld, how do we connect the data out to the register file? we connect to the write data input • For sd, what register file output do we connect to the data in? we connect rdata 2 output 12 • Logisim demo: mempath 2. circ, array. txt