Datapath and Control Andreas Klappenecker CPSC 321 Computer

- Slides: 22

Datapath and Control Andreas Klappenecker CPSC 321 Computer Architecture

Administrative Issues n Exam has been graded n n Grades need to be entered by TA Attendance in the labs Lab 3 assignment Make-up exam T 2: 00 pm-2: 50 pm

Goal of this lecture n Revisit the single-cycle processor n n datapath control Why are the instructions structured in the way they are? Multi-cycle processor

The Single-Cycle Processor Revisited

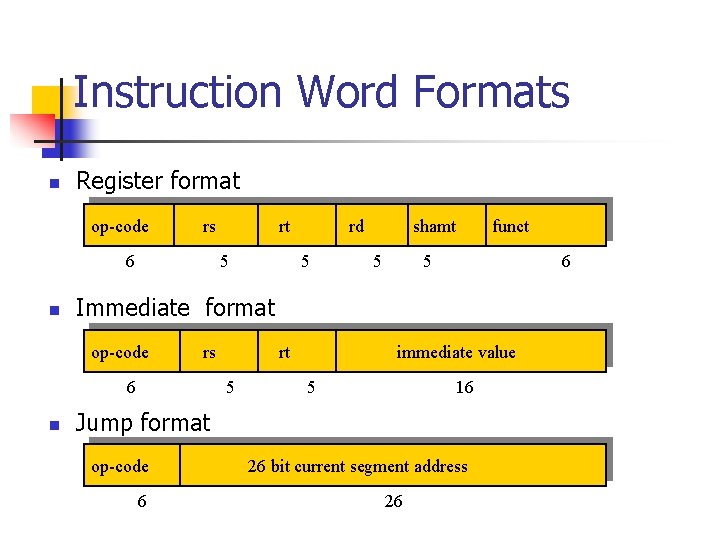

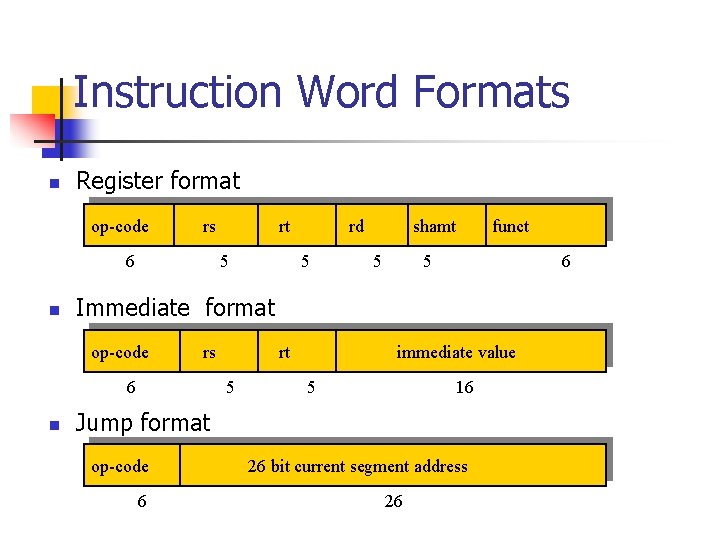

Instruction Word Formats n Register format op-code rs 6 n 5 rd 5 shamt 5 funct 5 6 Immediate format op-code rs 6 n rt rt 5 immediate value 5 16 Jump format op-code 6 26 bit current segment address 26

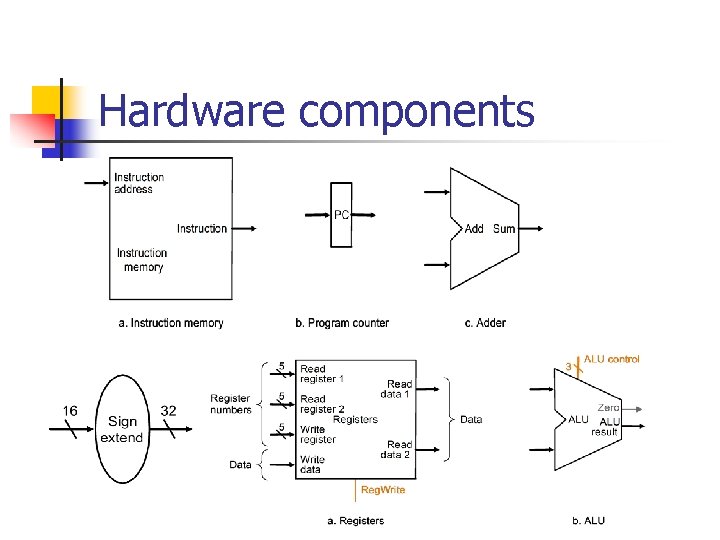

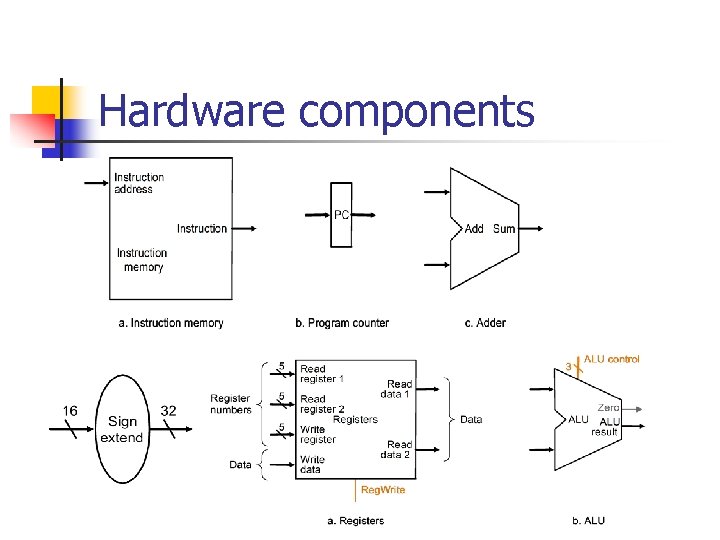

Hardware components

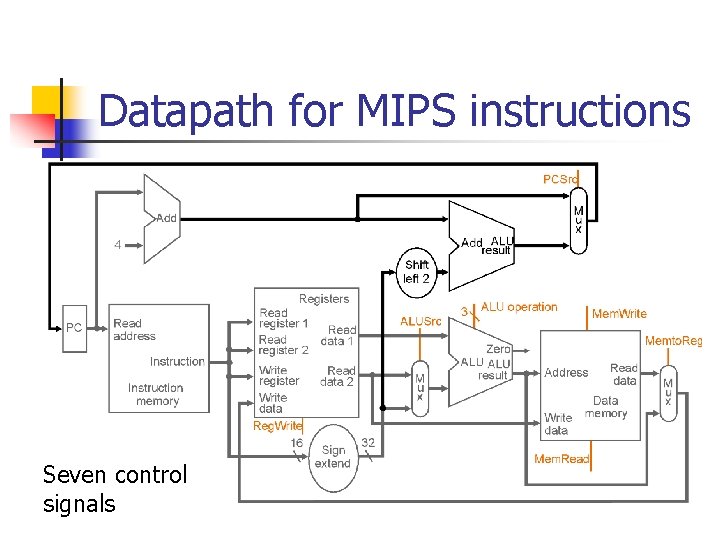

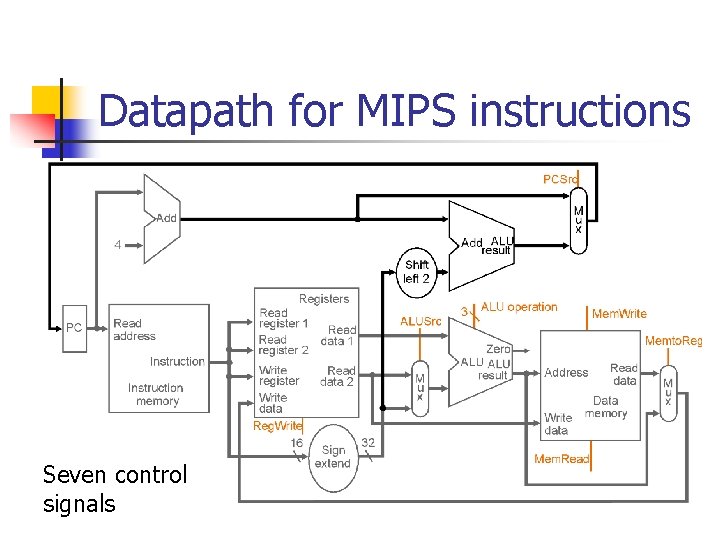

Datapath for MIPS instructions Seven control signals

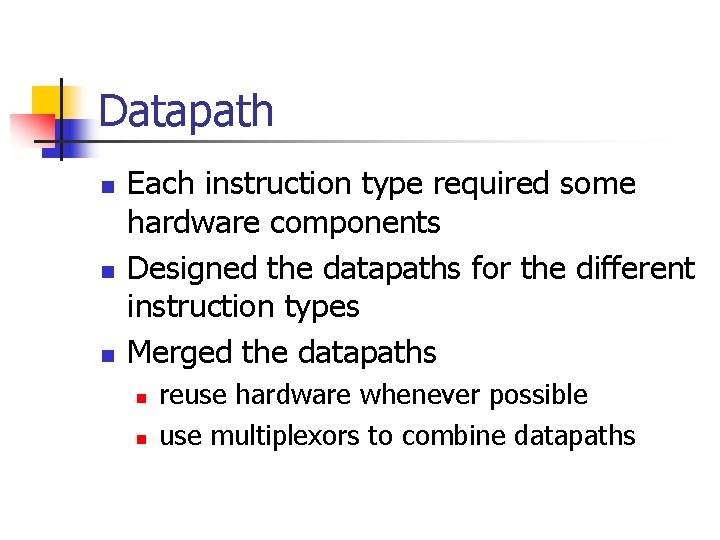

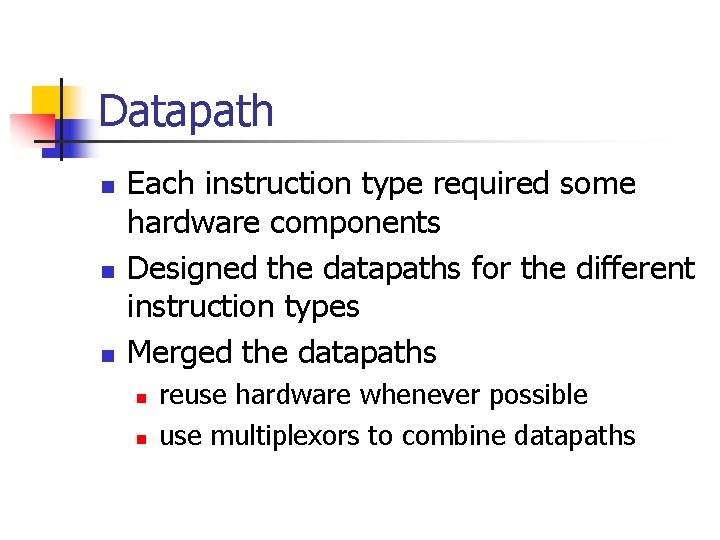

Datapath n n n Each instruction type required some hardware components Designed the datapaths for the different instruction types Merged the datapaths n n reuse hardware whenever possible use multiplexors to combine datapaths

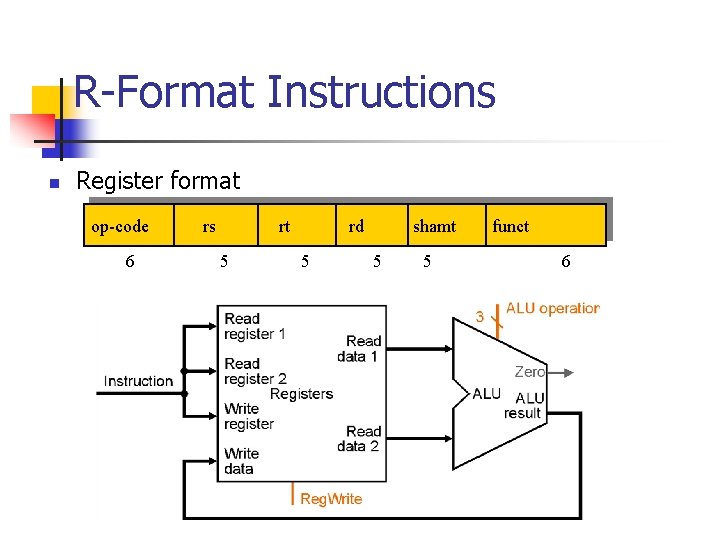

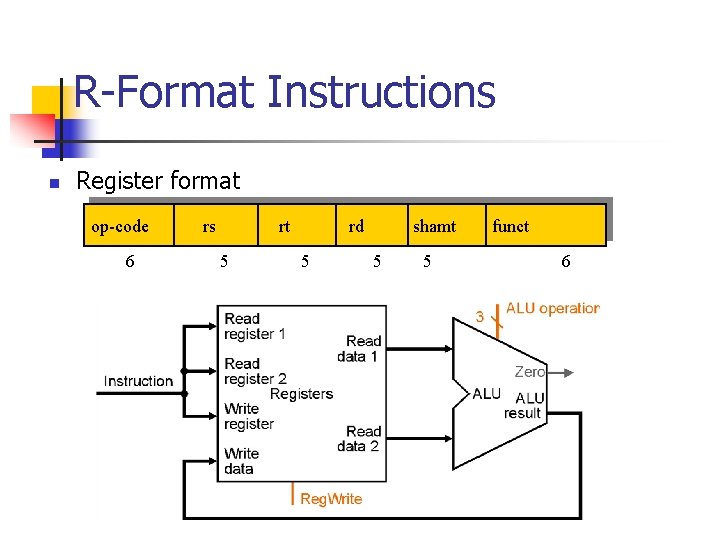

R-Format Instructions n Register format op-code 6 rs rt 5 rd 5 shamt 5 5 funct 6

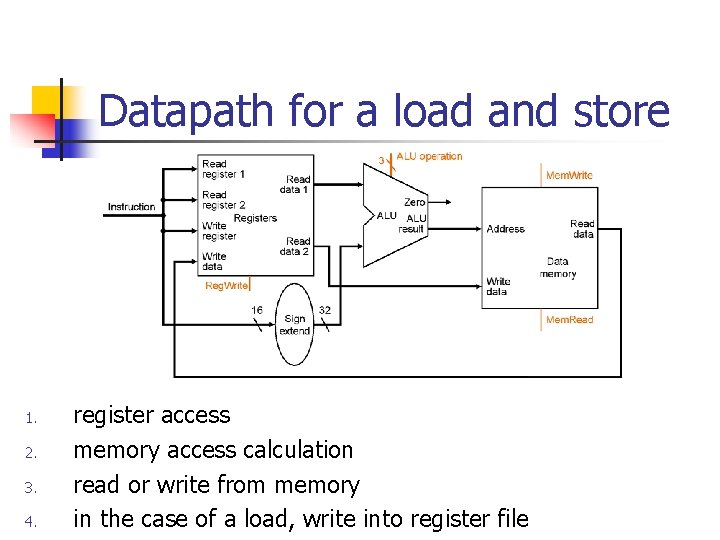

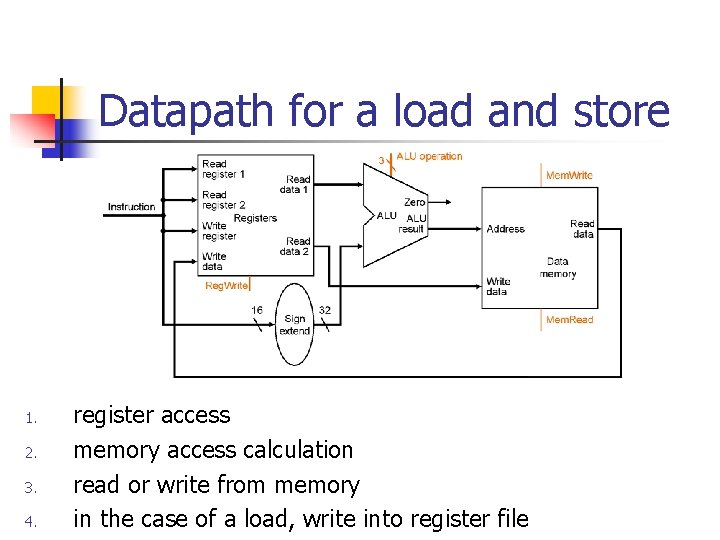

Datapath for a load and store 1. 2. 3. 4. register access memory access calculation read or write from memory in the case of a load, write into register file

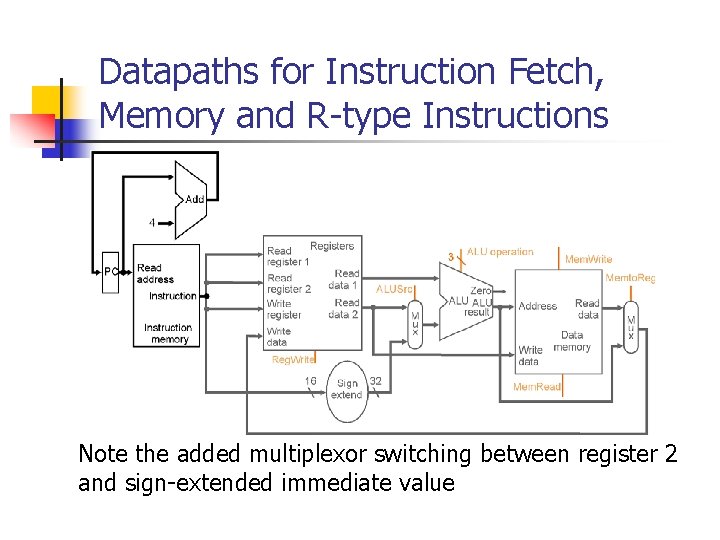

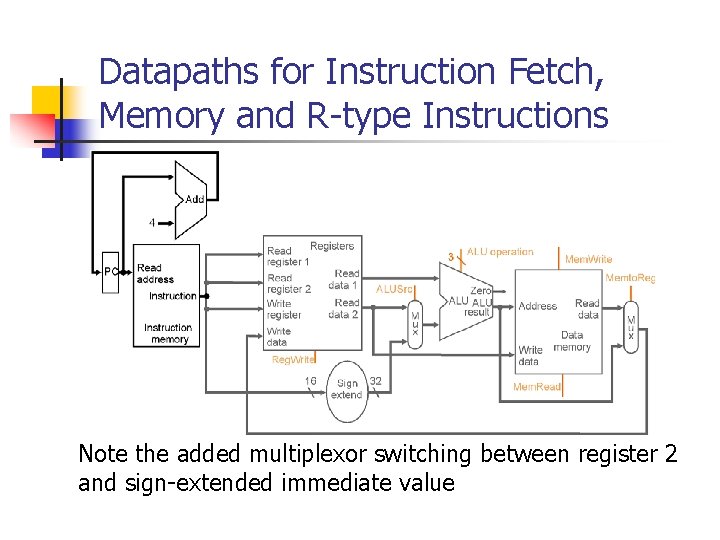

Datapaths for Instruction Fetch, Memory and R-type Instructions Note the added multiplexor switching between register 2 and sign-extended immediate value

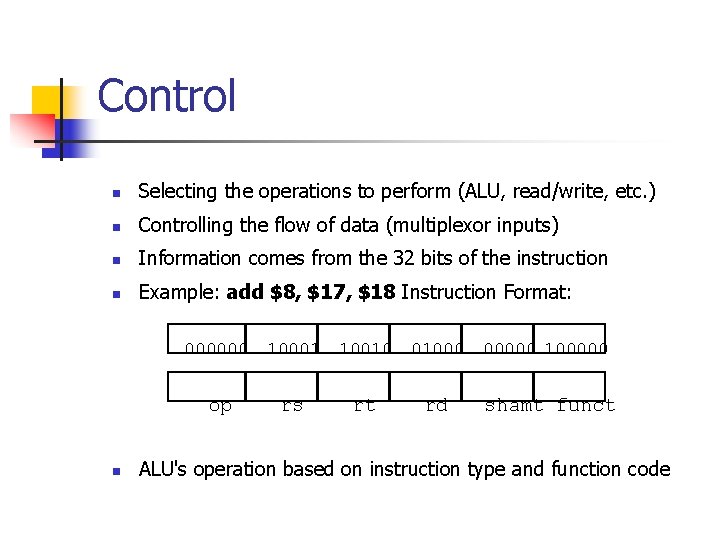

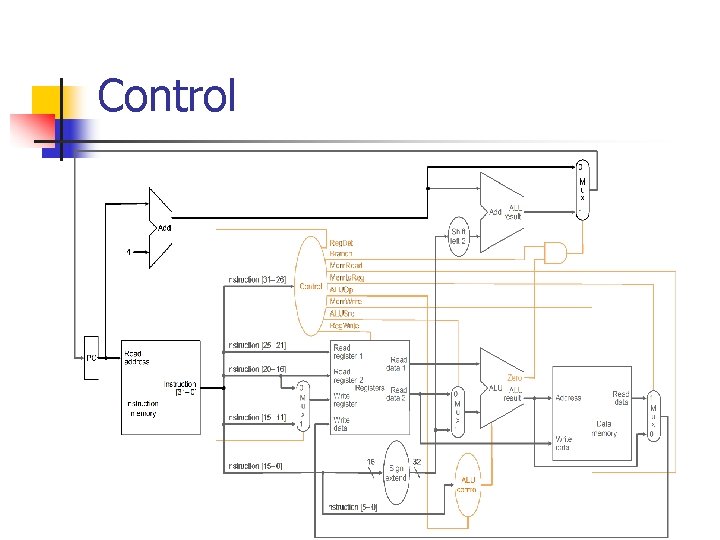

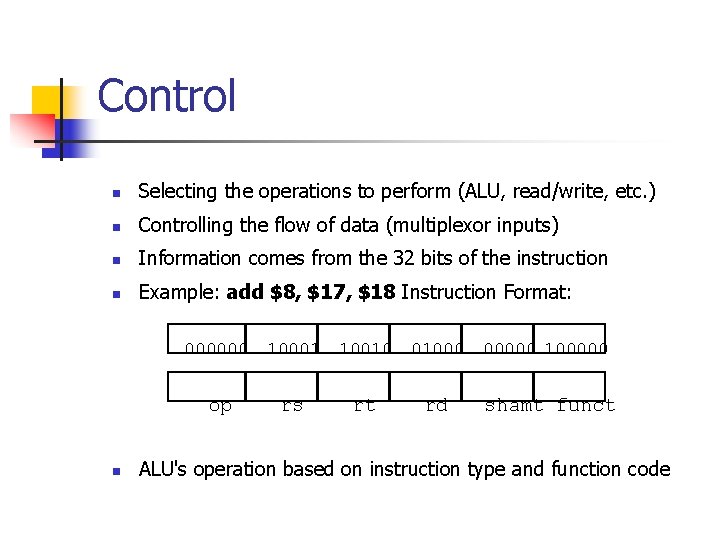

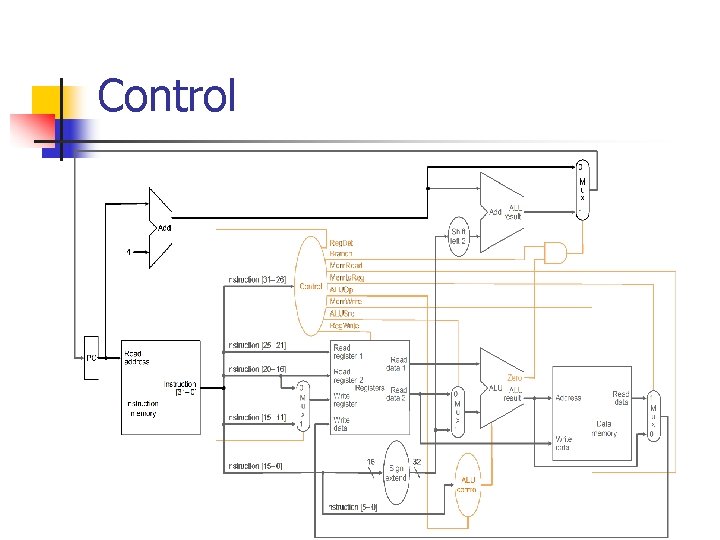

Control n Selecting the operations to perform (ALU, read/write, etc. ) n Controlling the flow of data (multiplexor inputs) n Information comes from the 32 bits of the instruction n Example: add $8, $17, $18 Instruction Format: 000000 op n 10001 10010 01000 00000 100000 rs rt rd shamt funct ALU's operation based on instruction type and function code

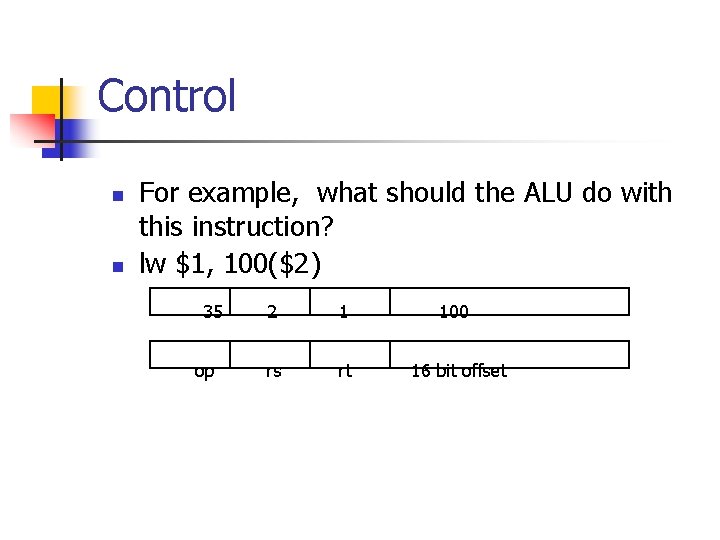

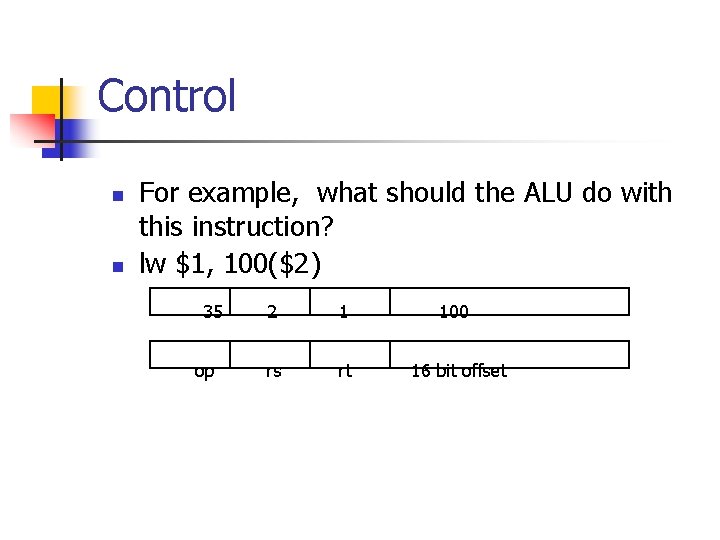

Control n n For example, what should the ALU do with this instruction? lw $1, 100($2) 35 op 2 1 100 rs rt 16 bit offset

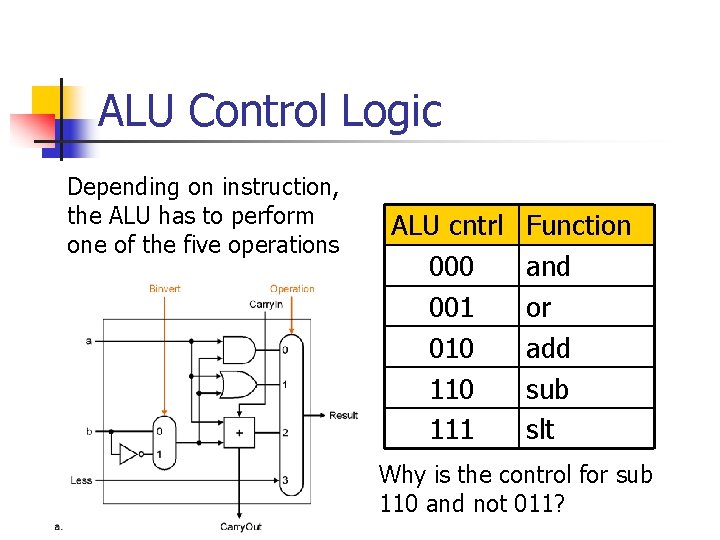

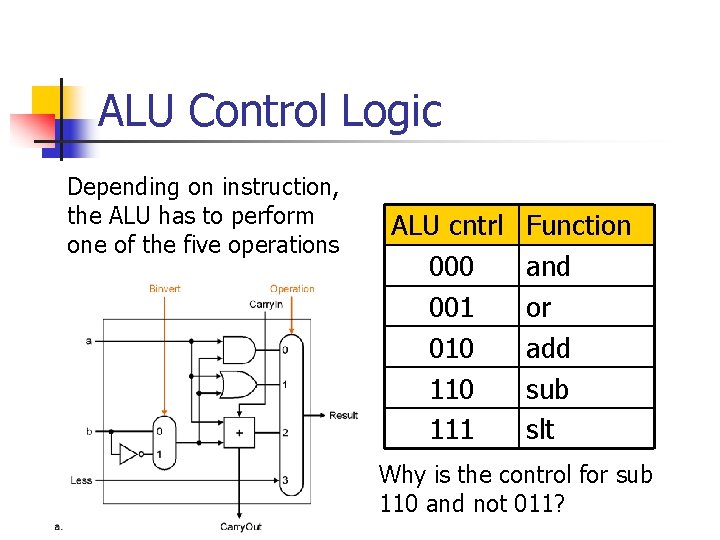

ALU Control Logic Depending on instruction, the ALU has to perform one of the five operations ALU cntrl 000 001 010 111 Function and or add sub slt Why is the control for sub 110 and not 011?

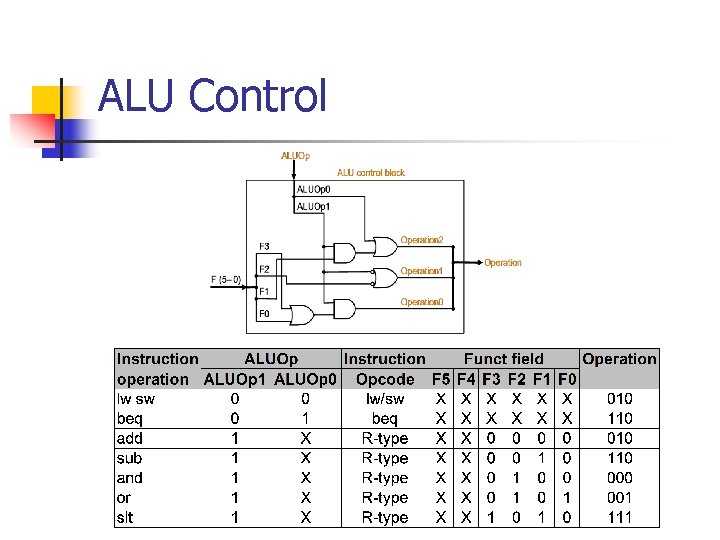

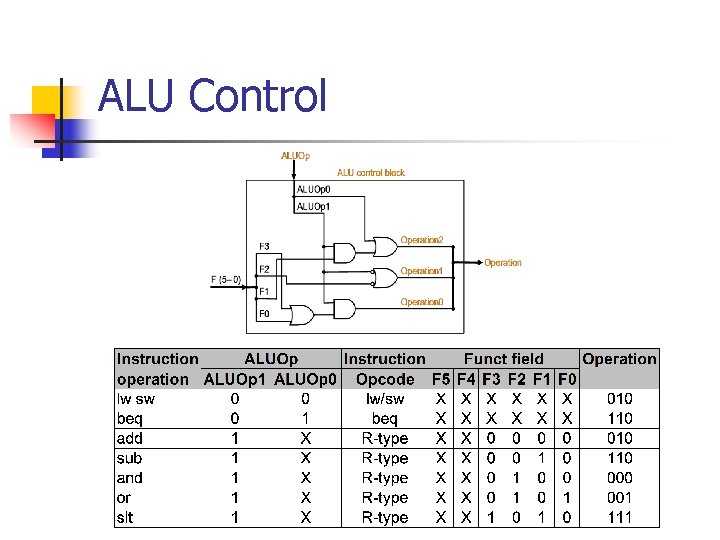

ALU Control

Control

Multi-Cycle Processor

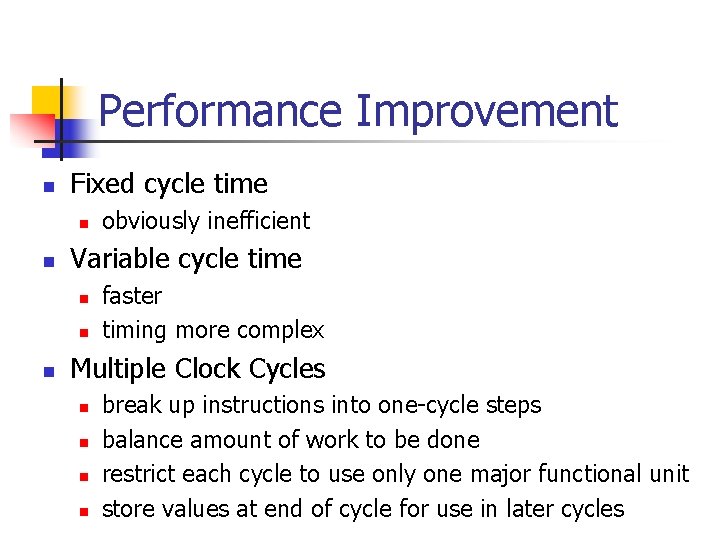

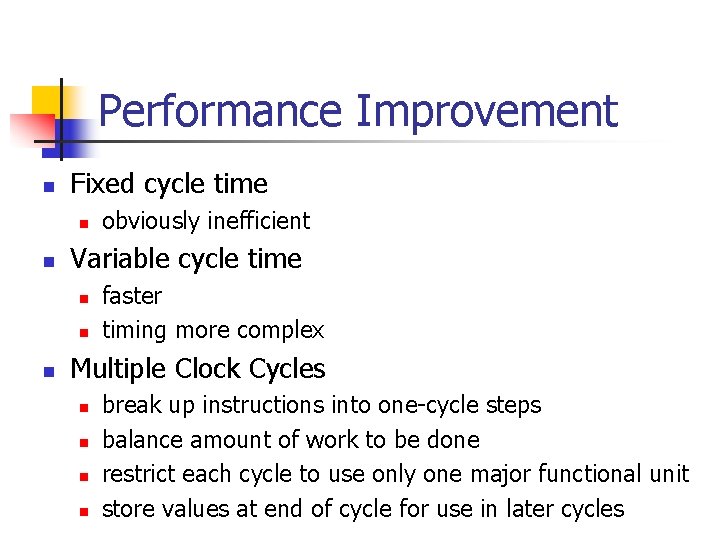

Performance Improvement n Fixed cycle time n n Variable cycle time n n n obviously inefficient faster timing more complex Multiple Clock Cycles n n break up instructions into one-cycle steps balance amount of work to be done restrict each cycle to use only one major functional unit store values at end of cycle for use in later cycles

Multicycle Approach n Reuse functional units n n n Control signals not just determined by instruction n n ALU used to compute address and to increment PC Memory used for instruction and data additional complexity is introduced here Finite state machine can be used for control

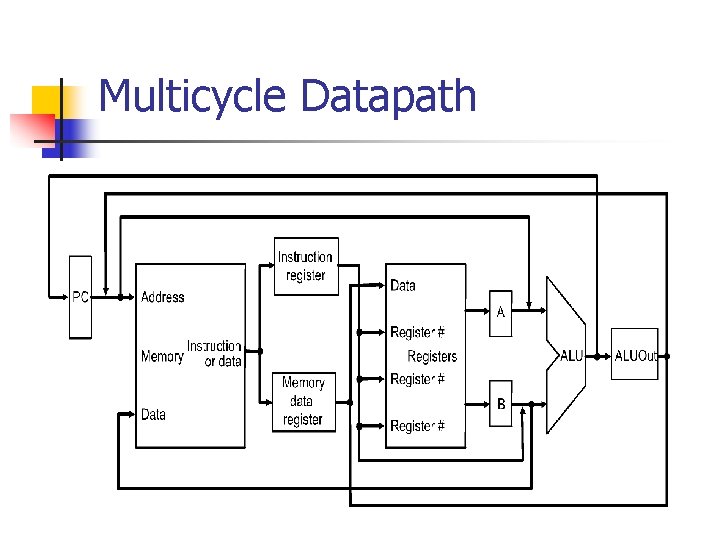

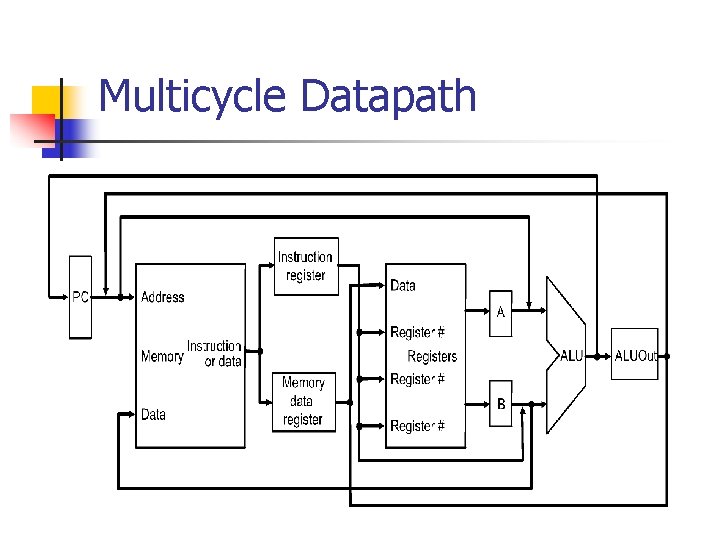

Multicycle Datapath

Outlook n n Discuss the details of the datapath Instruction fetch/decode/execute cycle Construct the finite state machine for control More complicated processors: Use microprogramming to simplify control

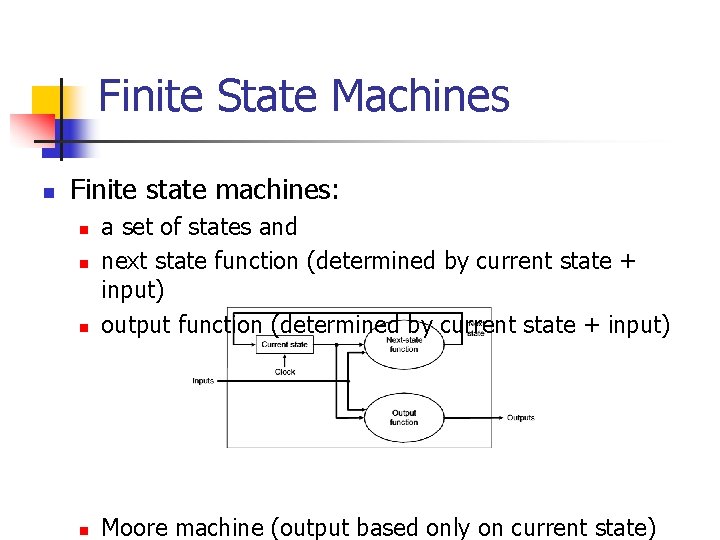

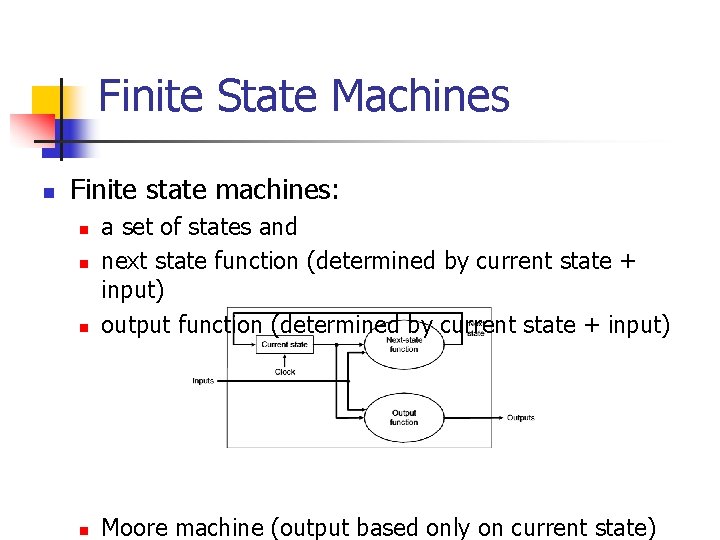

Finite State Machines n Finite state machines: n a set of states and next state function (determined by current state + input) output function (determined by current state + input) n Moore machine (output based only on current state) n n