Data Types and Operators 1 Data Types Represent

![Net Declaration wire[7: 0] data_bus; // 8 -bit vector wire, data_bus[7] -> MSB wire[0: Net Declaration wire[7: 0] data_bus; // 8 -bit vector wire, data_bus[7] -> MSB wire[0:](https://slidetodoc.com/presentation_image_h/2d1139df4fe29248c6953d16b5b7abd5/image-9.jpg)

![Memories Memory size … Word size reg[31: 0] cache_memory[0: 1023]; reg[31: 0] word_register; reg[7: Memories Memory size … Word size reg[31: 0] cache_memory[0: 1023]; reg[31: 0] word_register; reg[7:](https://slidetodoc.com/presentation_image_h/2d1139df4fe29248c6953d16b5b7abd5/image-14.jpg)

![Example of De-referencing module testbench(); reg [3: 0] a, b; wire [3: 0] y; Example of De-referencing module testbench(); reg [3: 0] a, b; wire [3: 0] y;](https://slidetodoc.com/presentation_image_h/2d1139df4fe29248c6953d16b5b7abd5/image-17.jpg)

![Indirect Substitution of Parameters module param; wire [7: 0] y 1; wire [3: 0] Indirect Substitution of Parameters module param; wire [7: 0] y 1; wire [3: 0]](https://slidetodoc.com/presentation_image_h/2d1139df4fe29248c6953d16b5b7abd5/image-21.jpg)

- Slides: 30

Data Types and Operators 1

Data Types Represent values of signals in physical circuit in a digital format Nets – n Represent physical connectivity variable – n Abstractions of storage elements Nets and registers may be either scalars or vectors ELEN 468 Lecture 4 2

Storage Variable Storage variable = register n reg, integer, realtime, time Abstraction of storage element Need not correspond directly to physical storage element in circuit Static – its value is assigned under program flow 3

Value Assignment Explicitly – through behavioral statements Implicitly – driven by a gate A net may be assigned value explicitly only through continuous assignment A register variable may be assigned value only within a behavior 4

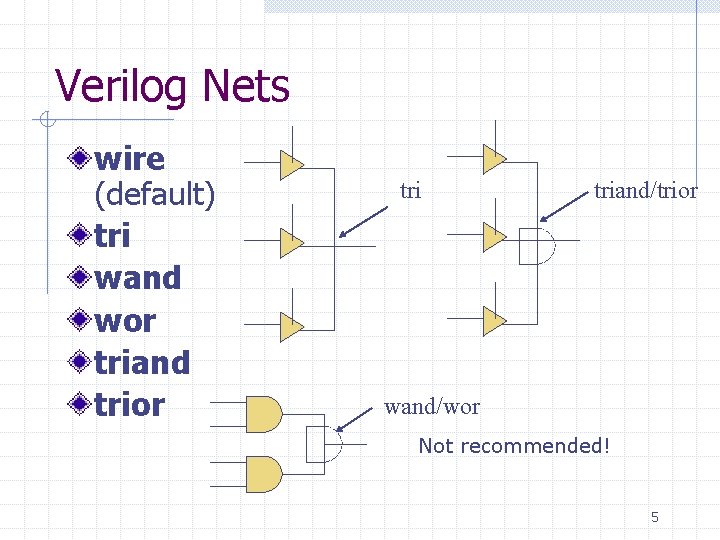

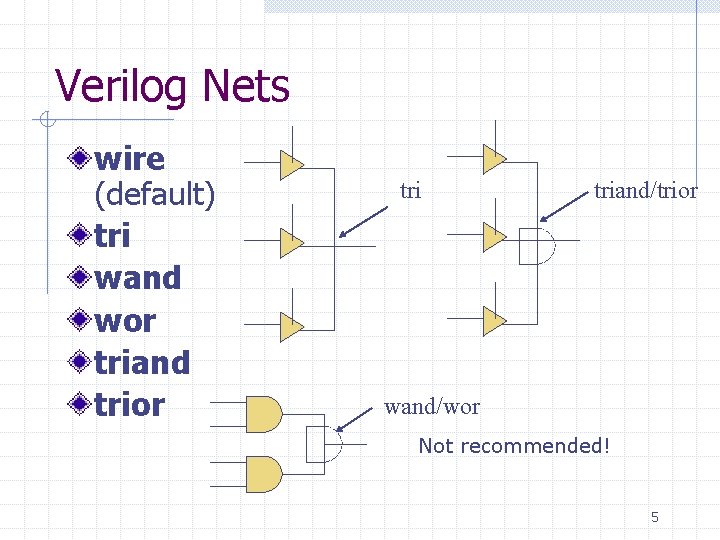

Verilog Nets wire (default) tri wand wor triand trior triand/trior wand/wor Not recommended! 5

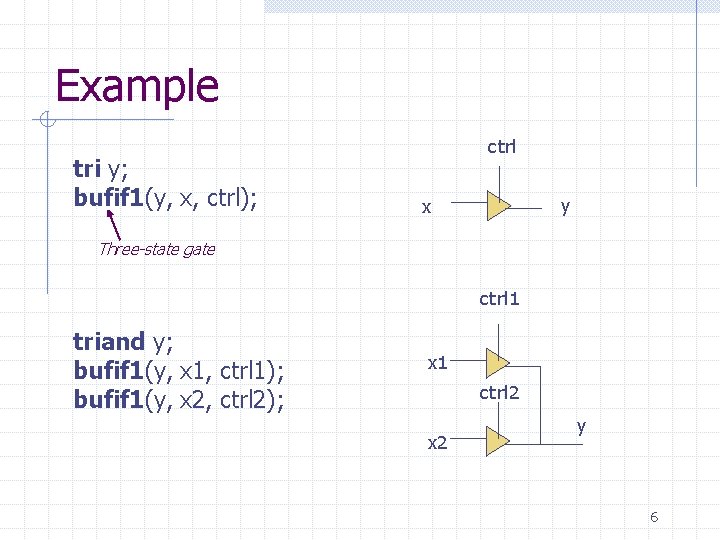

Example tri y; bufif 1(y, x, ctrl); ctrl y x Three-state gate ctrl 1 triand y; bufif 1(y, x 1, ctrl 1); bufif 1(y, x 2, ctrl 2); x 1 ctrl 2 x 2 y 6

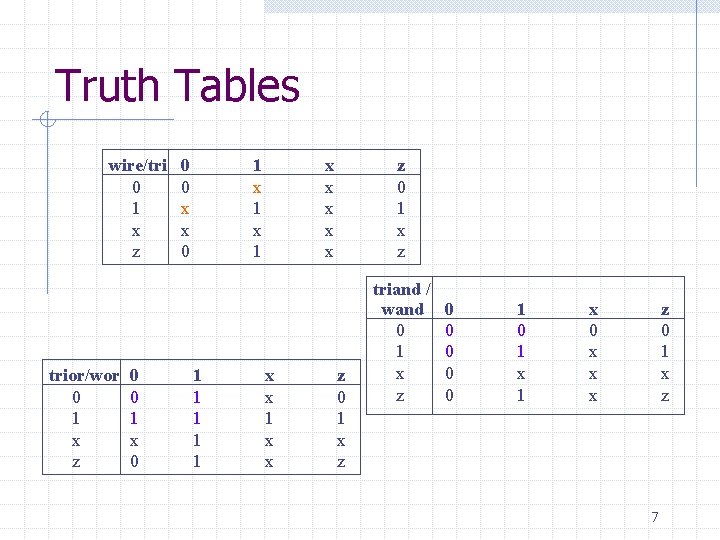

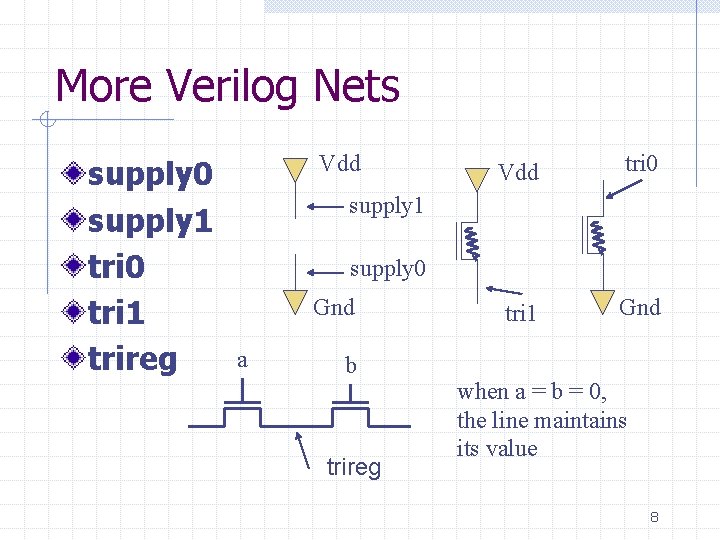

Truth Tables wire/tri 0 1 x z trior/wor 0 1 x z 0 0 1 x 0 0 0 x x 0 1 x 1 1 1 x x x x 1 x x z 0 1 x z triand / wand 0 1 x z 0 0 0 1 x 1 x 0 x x x z 0 1 x z 7

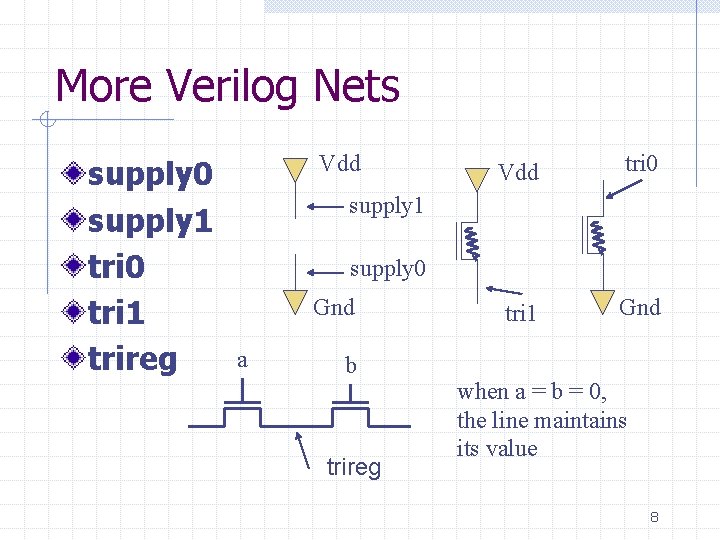

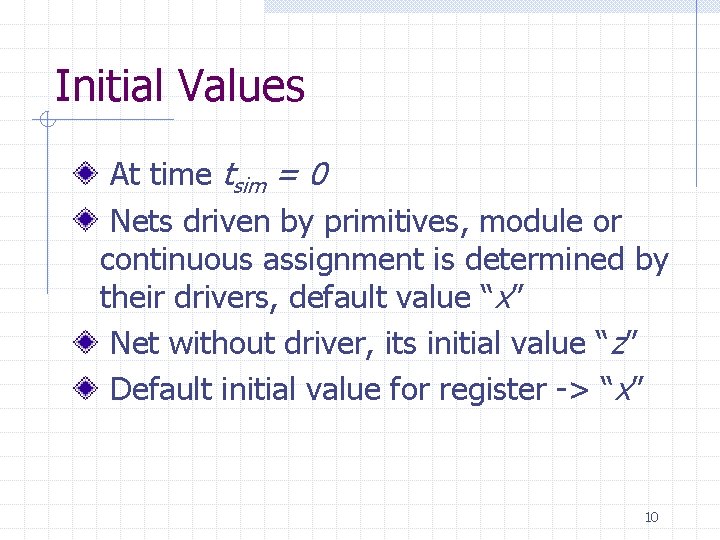

More Verilog Nets supply 0 supply 1 tri 0 tri 1 trireg Vdd tri 0 tri 1 Gnd supply 1 supply 0 Gnd a b trireg when a = b = 0, the line maintains its value 8

![Net Declaration wire7 0 databus 8 bit vector wire databus7 MSB wire0 Net Declaration wire[7: 0] data_bus; // 8 -bit vector wire, data_bus[7] -> MSB wire[0:](https://slidetodoc.com/presentation_image_h/2d1139df4fe29248c6953d16b5b7abd5/image-9.jpg)

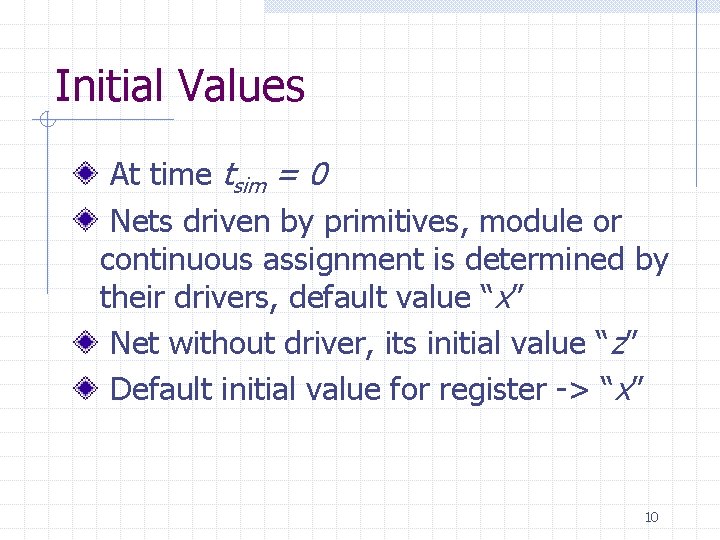

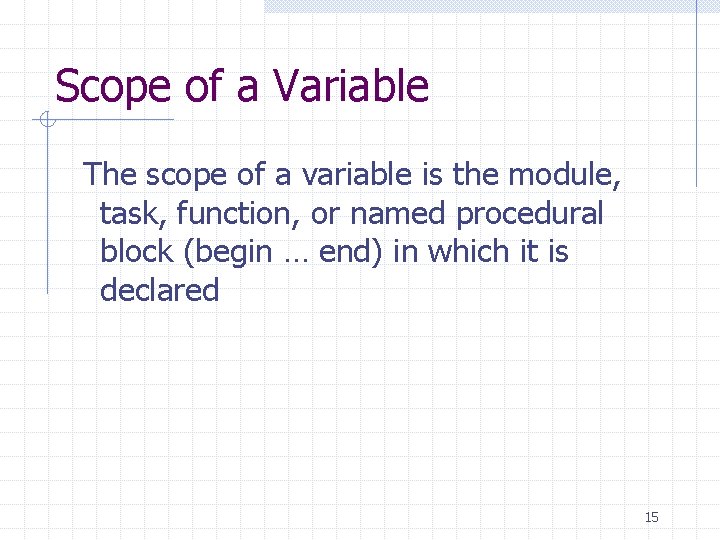

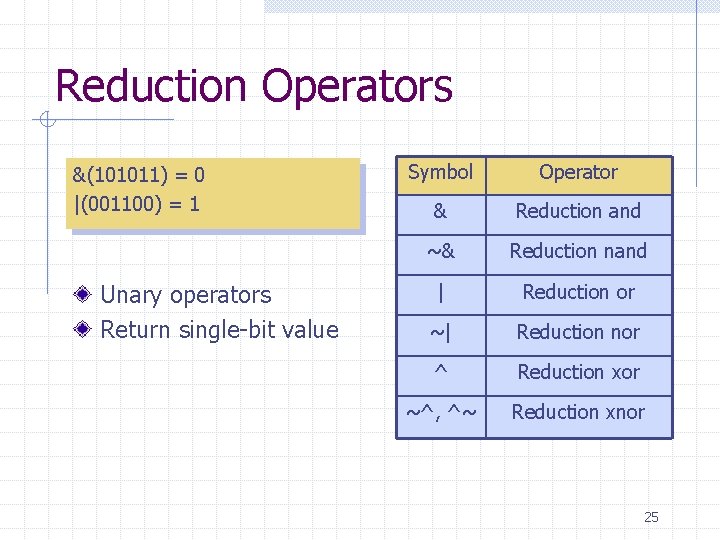

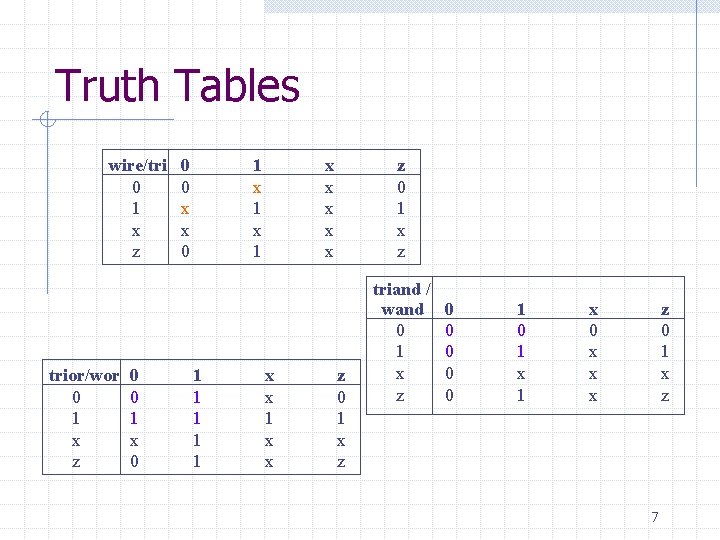

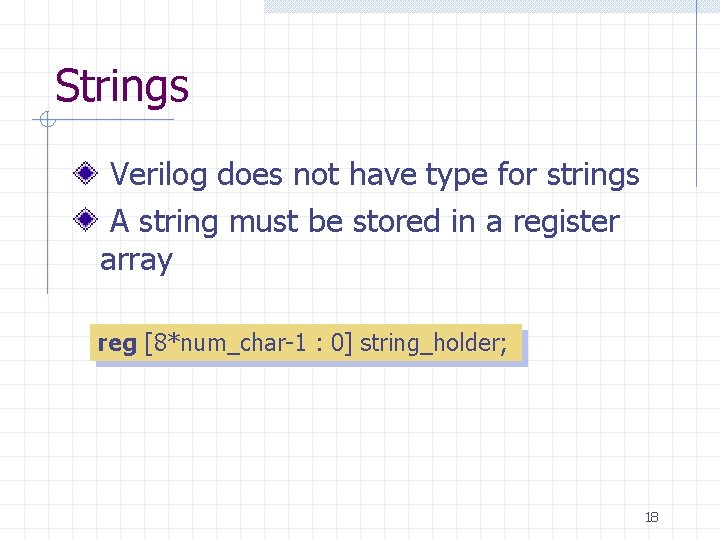

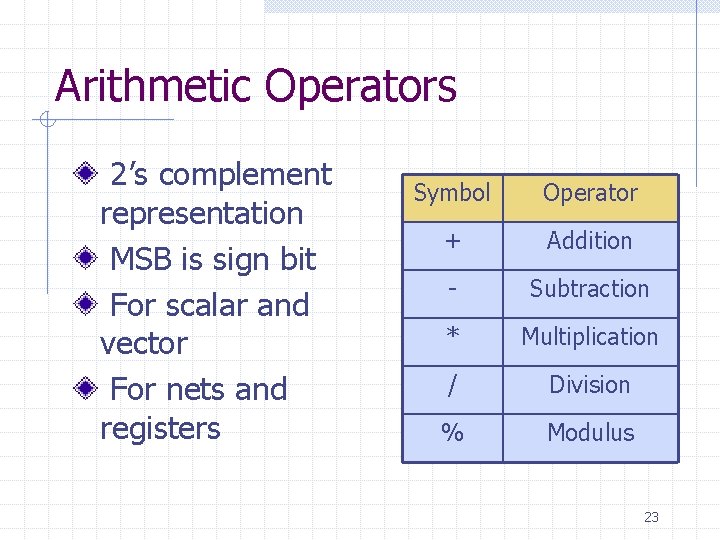

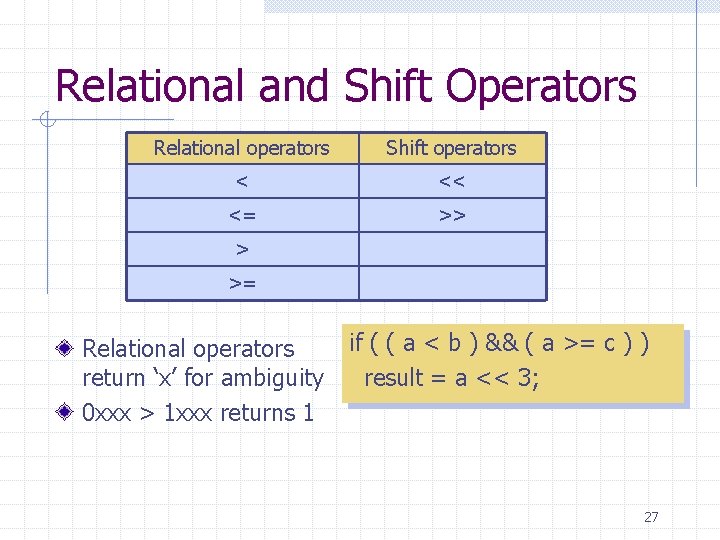

Net Declaration wire[7: 0] data_bus; // 8 -bit vector wire, data_bus[7] -> MSB wire[0: 3] control_bus; // control_bus[0] -> MSB data_bus[5], data_bus[3: 5], data_bus[k+2] // access wire scalared[7: 0] bus_a; // “scalared” is default wire vectored[7: 0] bus_b; // Individual bits may not be referenced wire y 1, z_5; // Multiple declaration wire A = B+C, D = E+F; // Implicit continuous assignment wand A, B, C; trireg[7: 0] A; 9

Initial Values At time tsim = 0 Nets driven by primitives, module or continuous assignment is determined by their drivers, default value “x” Net without driver, its initial value “z” Default initial value for register -> “x” 10

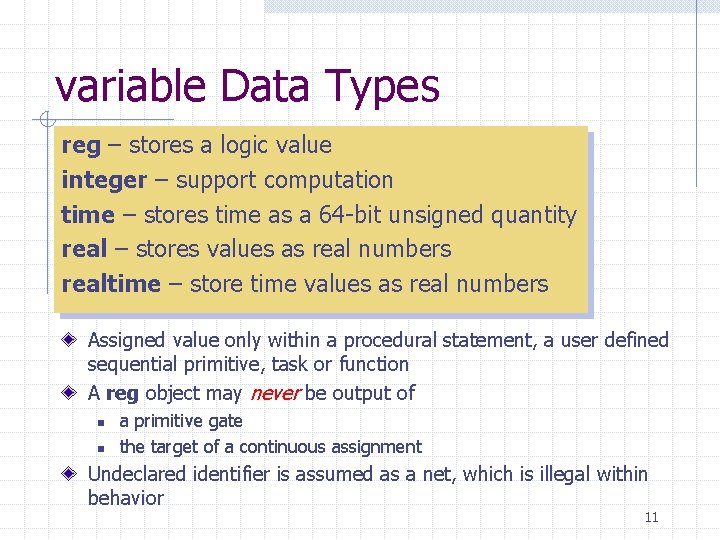

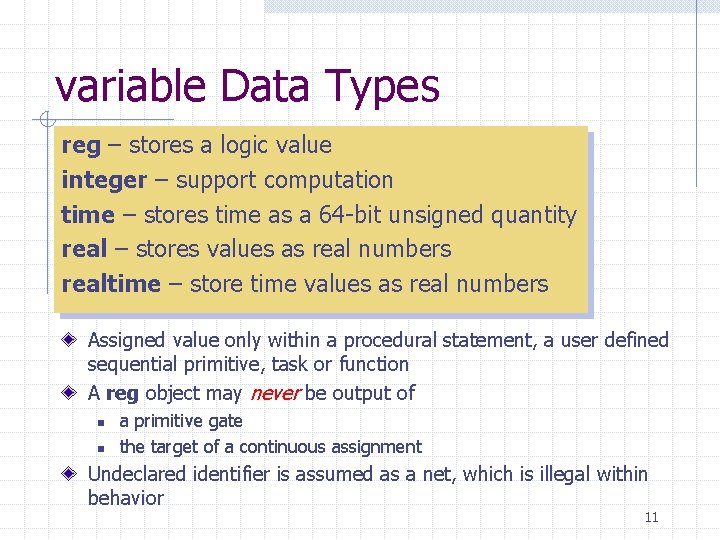

variable Data Types reg – stores a logic value integer – support computation time – stores time as a 64 -bit unsigned quantity real – stores values as real numbers realtime – store time values as real numbers Assigned value only within a procedural statement, a user defined sequential primitive, task or function A reg object may never be output of n n a primitive gate the target of a continuous assignment Undeclared identifier is assumed as a net, which is illegal within behavior 11

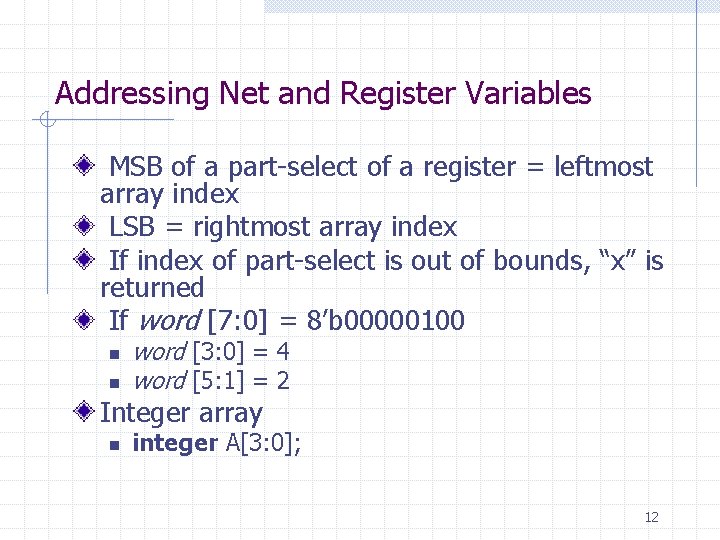

Addressing Net and Register Variables MSB of a part-select of a register = leftmost array index LSB = rightmost array index If index of part-select is out of bounds, “x” is returned If word [7: 0] = 8’b 00000100 n n word [3: 0] = 4 word [5: 1] = 2 Integer array n integer A[3: 0]; 12

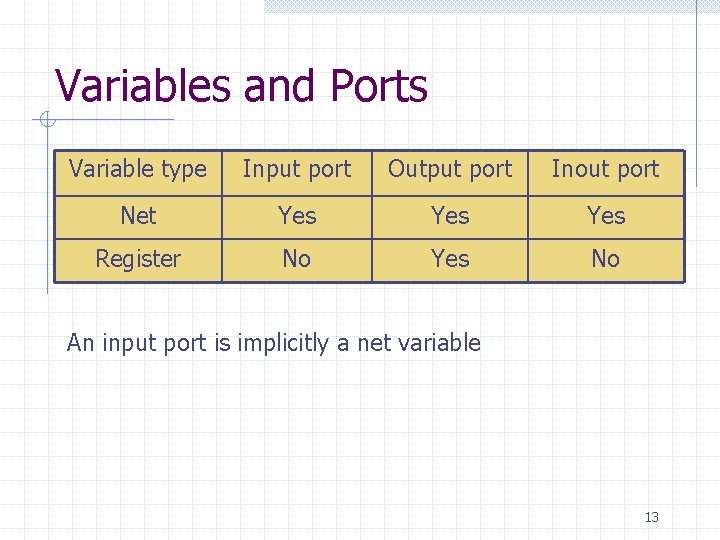

Variables and Ports Variable type Input port Output port Inout port Net Yes Yes Register No Yes No An input port is implicitly a net variable 13

![Memories Memory size Word size reg31 0 cachememory0 1023 reg31 0 wordregister reg7 Memories Memory size … Word size reg[31: 0] cache_memory[0: 1023]; reg[31: 0] word_register; reg[7:](https://slidetodoc.com/presentation_image_h/2d1139df4fe29248c6953d16b5b7abd5/image-14.jpg)

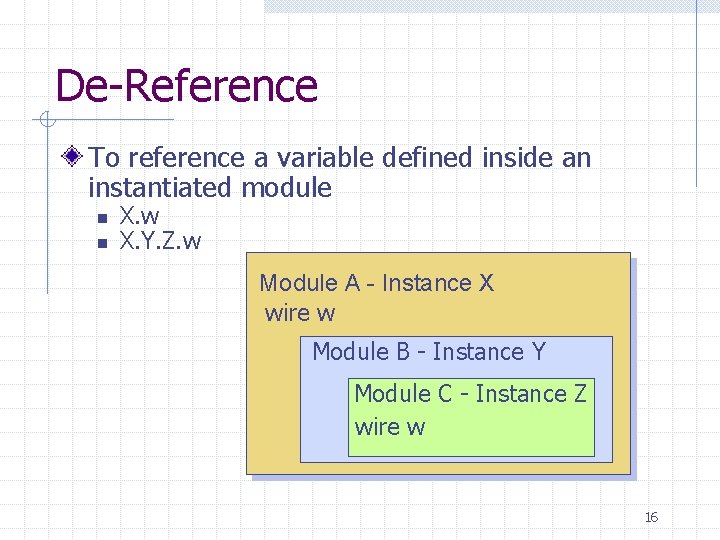

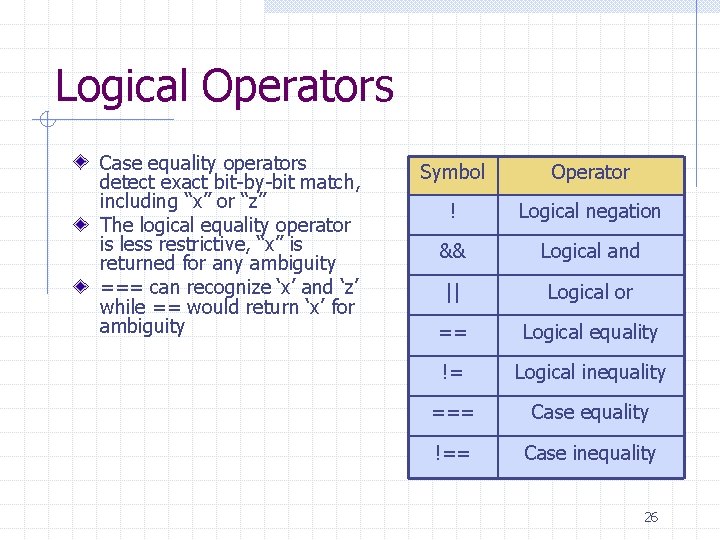

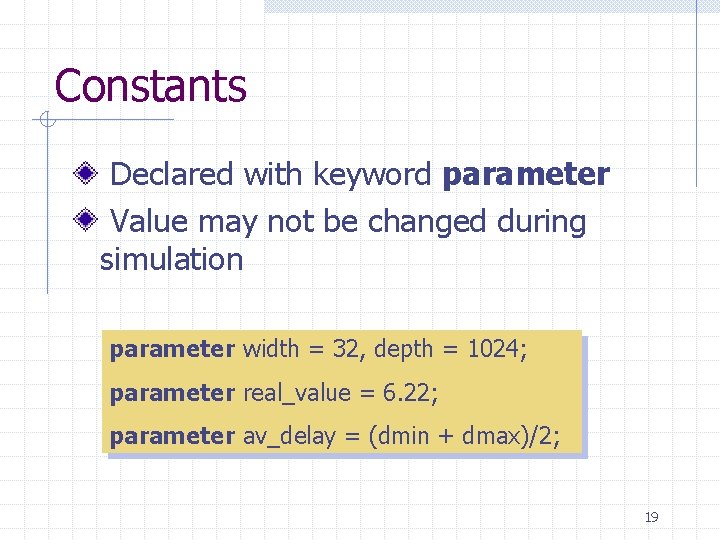

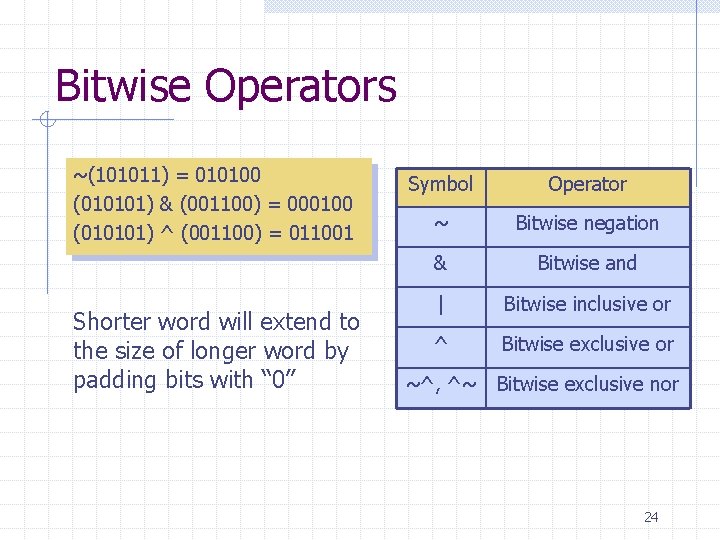

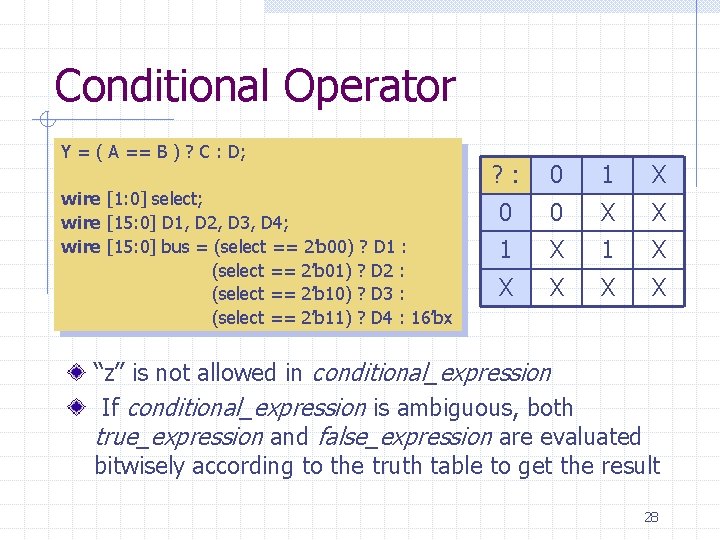

Memories Memory size … Word size reg[31: 0] cache_memory[0: 1023]; reg[31: 0] word_register; reg[7: 0] instr_register; … word_register = cache_memory[17]; … // a loop … instr_register[k] = word_register[k+4]; … Individual bits within a memory cannot be addressed directly The word is fetched to a register, then bit can be accessed 14

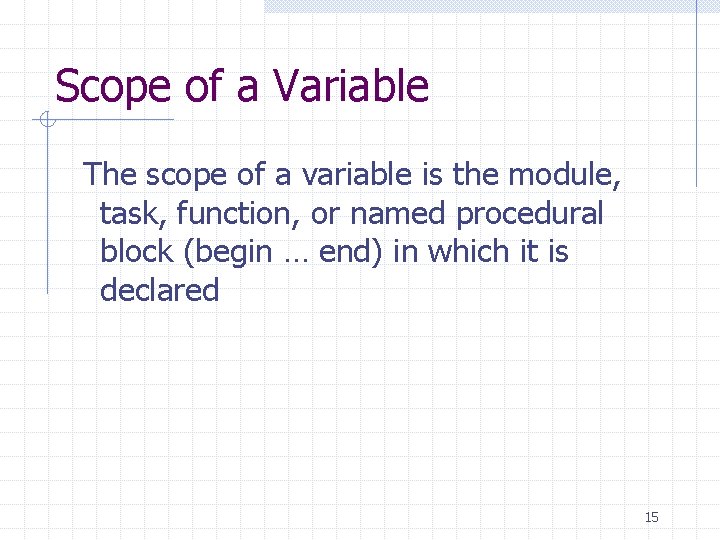

Scope of a Variable The scope of a variable is the module, task, function, or named procedural block (begin … end) in which it is declared 15

De-Reference To reference a variable defined inside an instantiated module n n X. w X. Y. Z. w Module A - Instance X wire w Module B - Instance Y Module C - Instance Z wire w 16

![Example of Dereferencing module testbench reg 3 0 a b wire 3 0 y Example of De-referencing module testbench(); reg [3: 0] a, b; wire [3: 0] y;](https://slidetodoc.com/presentation_image_h/2d1139df4fe29248c6953d16b5b7abd5/image-17.jpg)

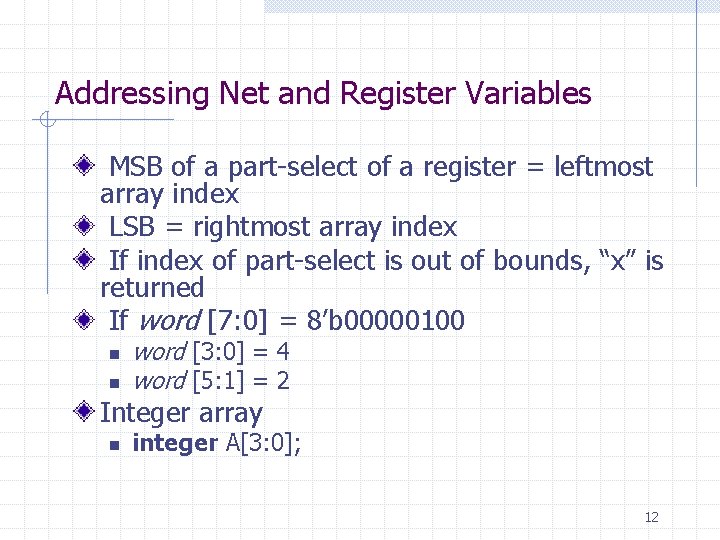

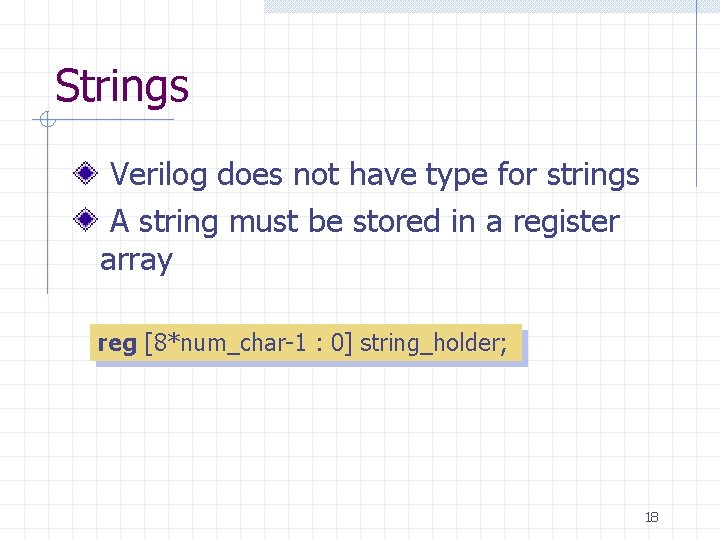

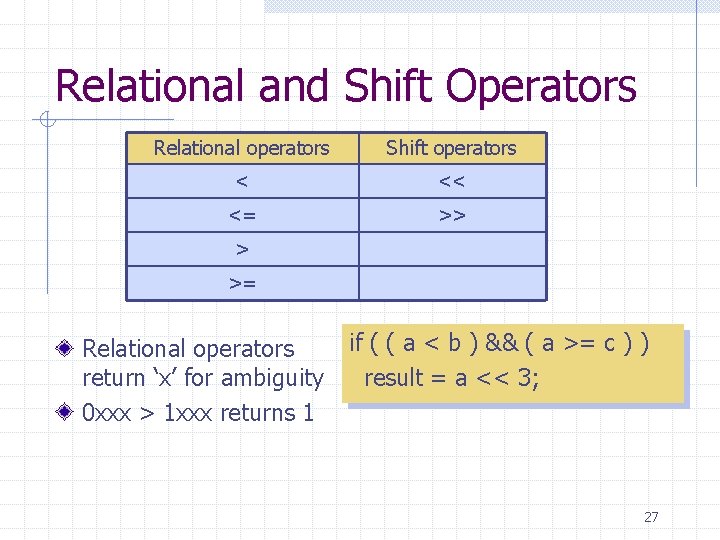

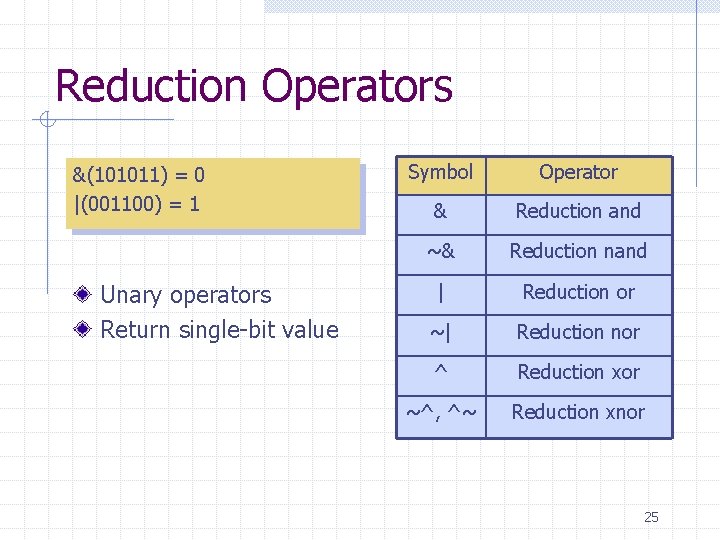

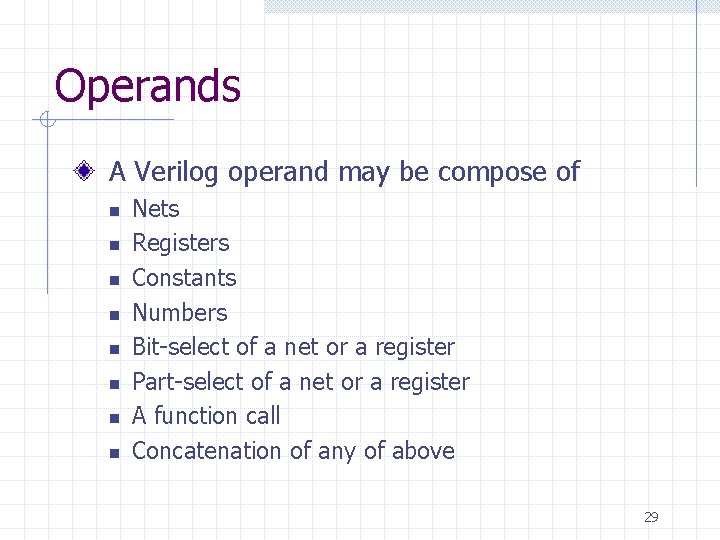

Example of De-referencing module testbench(); reg [3: 0] a, b; wire [3: 0] y; adder M 1 (y, a, b); initial $monitor($time, , ”%”, M 1. c); endmodule adder(y, a, b); … wire c; … endmodule 17

Strings Verilog does not have type for strings A string must be stored in a register array reg [8*num_char-1 : 0] string_holder; 18

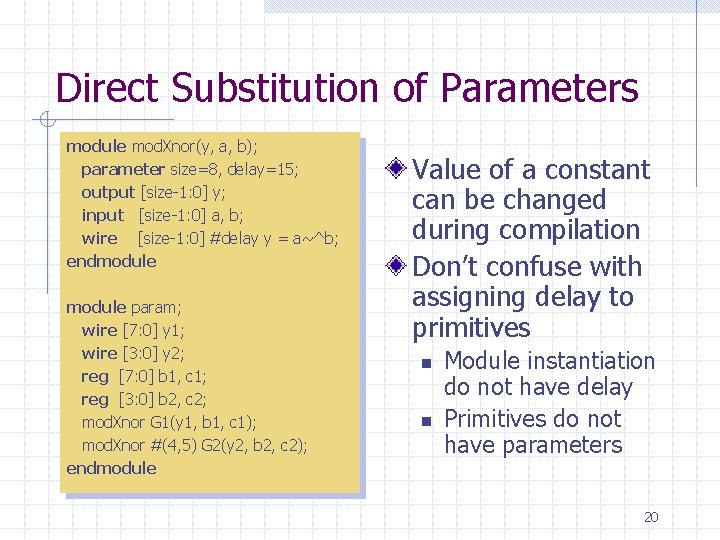

Constants Declared with keyword parameter Value may not be changed during simulation parameter width = 32, depth = 1024; parameter real_value = 6. 22; parameter av_delay = (dmin + dmax)/2; 19

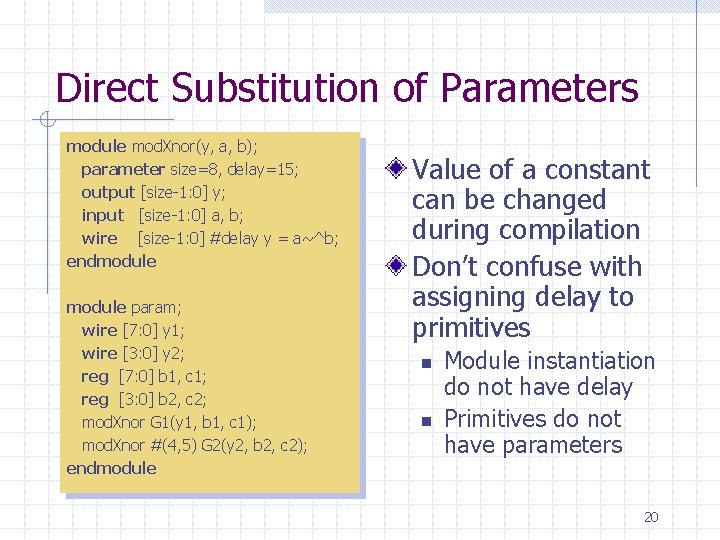

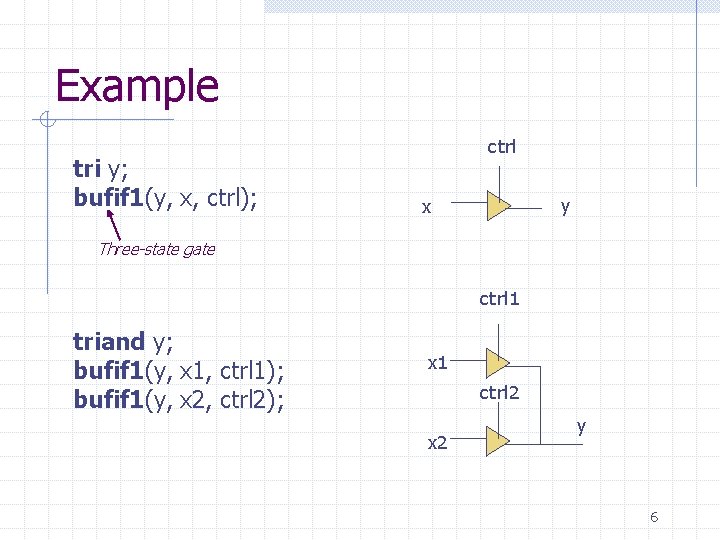

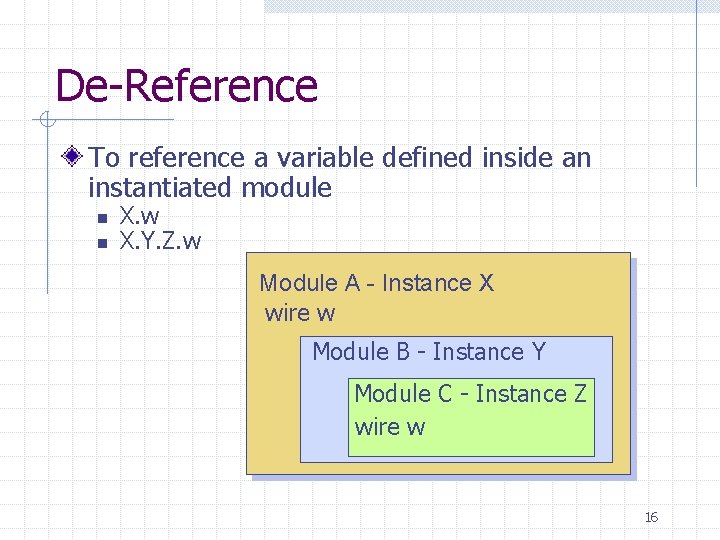

Direct Substitution of Parameters module mod. Xnor(y, a, b); parameter size=8, delay=15; output [size-1: 0] y; input [size-1: 0] a, b; wire [size-1: 0] #delay y = a~^b; endmodule param; wire [7: 0] y 1; wire [3: 0] y 2; reg [7: 0] b 1, c 1; reg [3: 0] b 2, c 2; mod. Xnor G 1(y 1, b 1, c 1); mod. Xnor #(4, 5) G 2(y 2, b 2, c 2); endmodule Value of a constant can be changed during compilation Don’t confuse with assigning delay to primitives n n Module instantiation do not have delay Primitives do not have parameters 20

![Indirect Substitution of Parameters module param wire 7 0 y 1 wire 3 0 Indirect Substitution of Parameters module param; wire [7: 0] y 1; wire [3: 0]](https://slidetodoc.com/presentation_image_h/2d1139df4fe29248c6953d16b5b7abd5/image-21.jpg)

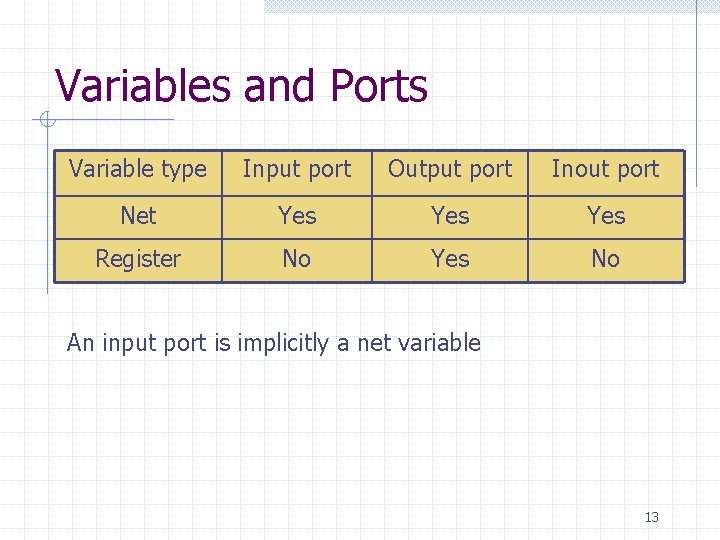

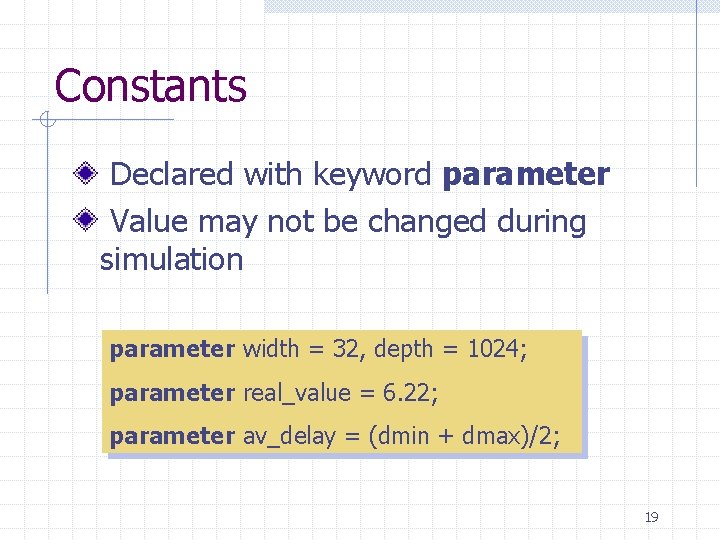

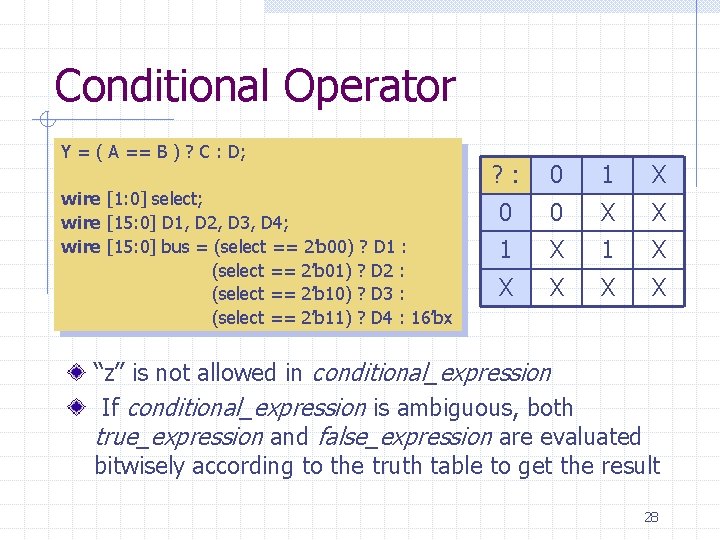

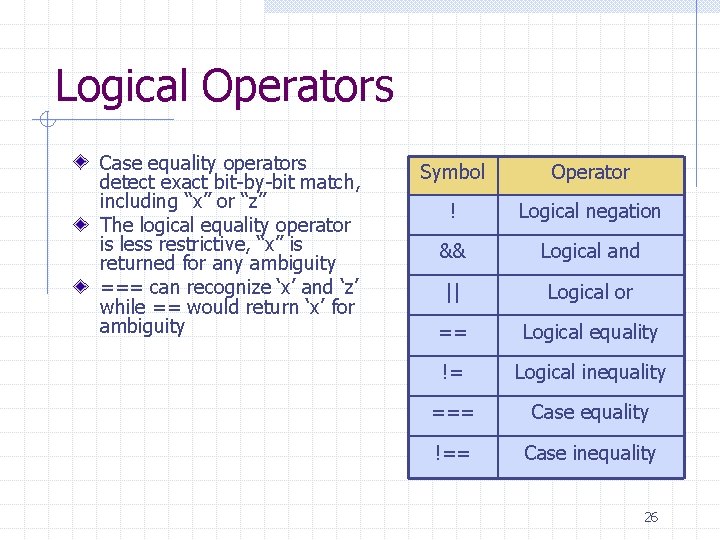

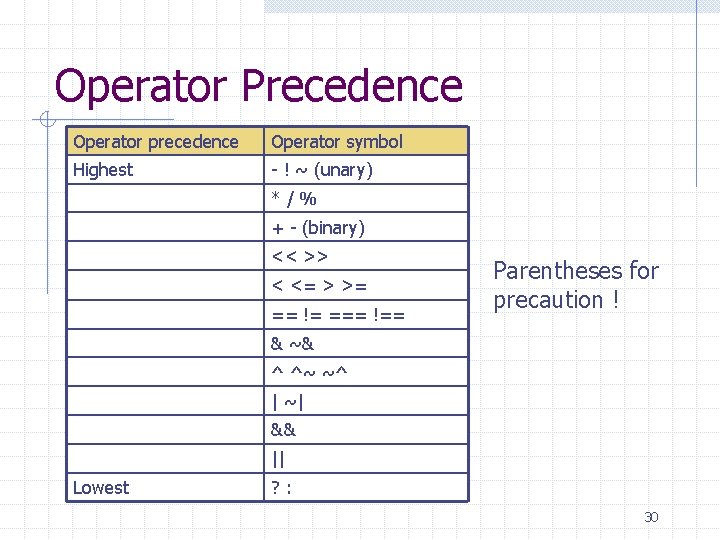

Indirect Substitution of Parameters module param; wire [7: 0] y 1; wire [3: 0] y 2; reg [7: 0] b 1, c 1; reg [3: 0] b 2, c 2; mod. Xnor G 1(y 1, b 1, c 1); mod. Xnor G 2(y 2, b 2, c 2); endmodule Declare a separate module where defparam is used with hierarchical pathname module annotate; defparam. G 2. size = 4; parem. G 2. delay = 5; endmodule 21

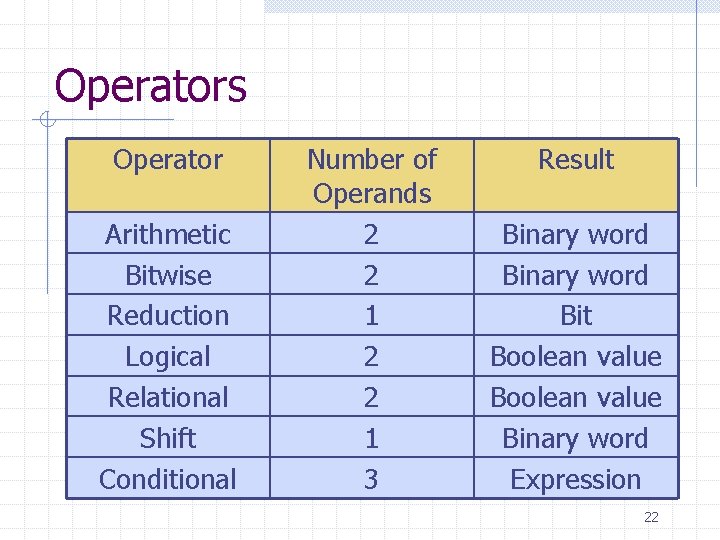

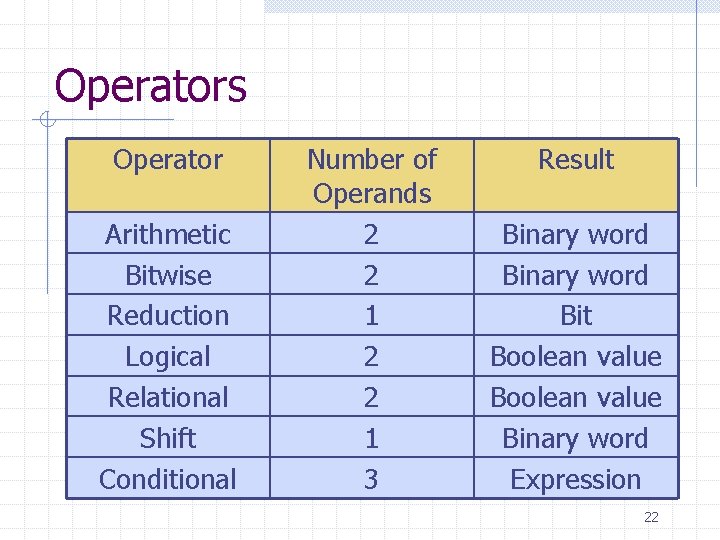

Operators Operator Arithmetic Bitwise Reduction Logical Relational Shift Conditional Number of Operands 2 2 1 3 Result Binary word Bit Boolean value Binary word Expression 22

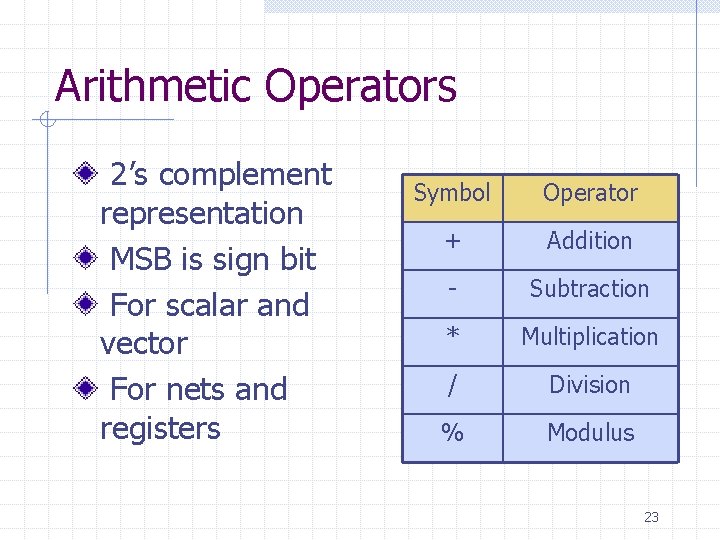

Arithmetic Operators 2’s complement representation MSB is sign bit For scalar and vector For nets and registers Symbol Operator + Addition - Subtraction * Multiplication / Division % Modulus 23

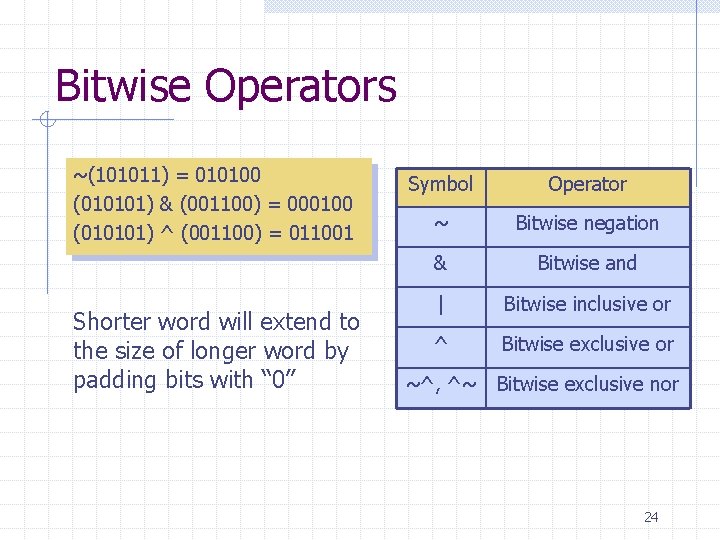

Bitwise Operators ~(101011) = 010100 (010101) & (001100) = 000100 (010101) ^ (001100) = 011001 Shorter word will extend to the size of longer word by padding bits with “ 0” Symbol Operator ~ Bitwise negation & Bitwise and | Bitwise inclusive or ^ Bitwise exclusive or ~^, ^~ Bitwise exclusive nor 24

Reduction Operators &(101011) = 0 |(001100) = 1 Unary operators Return single-bit value Symbol Operator & Reduction and ~& Reduction nand | Reduction or ~| Reduction nor ^ Reduction xor ~^, ^~ Reduction xnor 25

Logical Operators Case equality operators detect exact bit-by-bit match, including “x” or “z” The logical equality operator is less restrictive, “x” is returned for any ambiguity === can recognize ‘x’ and ‘z’ while == would return ‘x’ for ambiguity Symbol Operator ! Logical negation && Logical and || Logical or == Logical equality != Logical inequality === Case equality !== Case inequality 26

Relational and Shift Operators Relational operators Shift operators < << <= >> > >= Relational operators return ‘x’ for ambiguity 0 xxx > 1 xxx returns 1 if ( ( a < b ) && ( a >= c ) ) result = a << 3; 27

Conditional Operator Y = ( A == B ) ? C : D; wire [1: 0] select; wire [15: 0] D 1, D 2, D 3, D 4; wire [15: 0] bus = (select == 2’b 00) ? D 1 : (select == 2’b 01) ? D 2 : (select == 2’b 10) ? D 3 : (select == 2’b 11) ? D 4 : 16’bx ? : 0 1 X 0 0 X X 1 X X X “z” is not allowed in conditional_expression If conditional_expression is ambiguous, both true_expression and false_expression are evaluated bitwisely according to the truth table to get the result 28

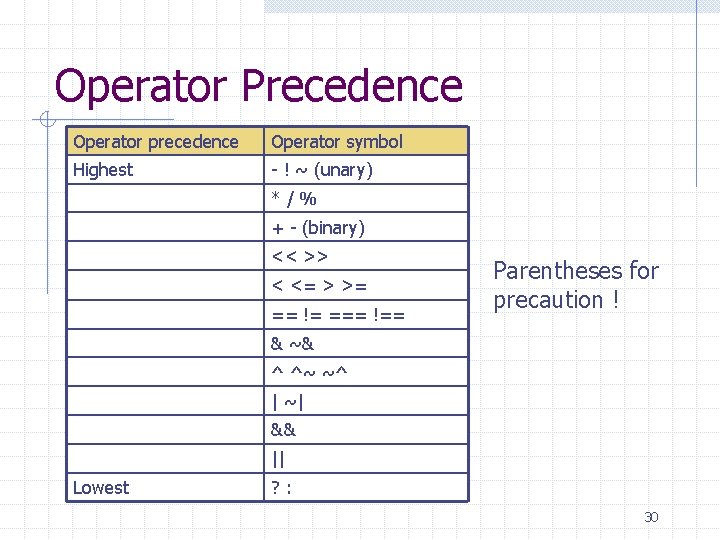

Operands A Verilog operand may be compose of n n n n Nets Registers Constants Numbers Bit-select of a net or a register Part-select of a net or a register A function call Concatenation of any of above 29

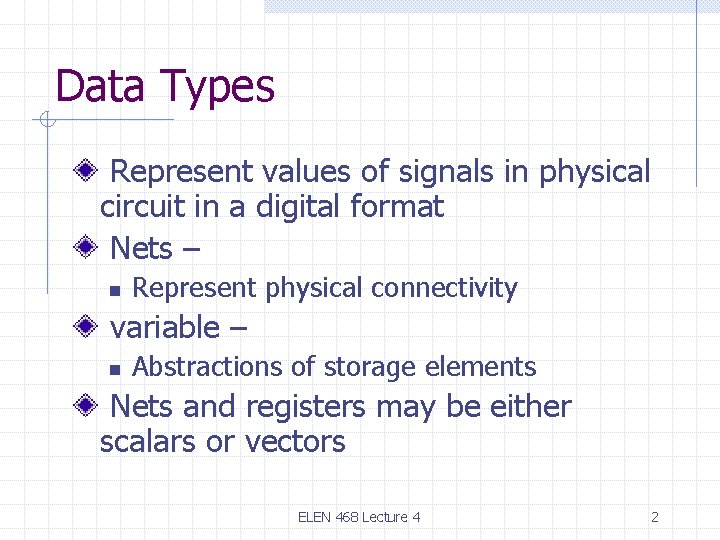

Operator Precedence Operator precedence Operator symbol Highest - ! ~ (unary) */% + - (binary) << >> < <= > >= == != === !== Parentheses for precaution ! & ~& ^ ^~ ~^ | ~| && || Lowest ? : 30