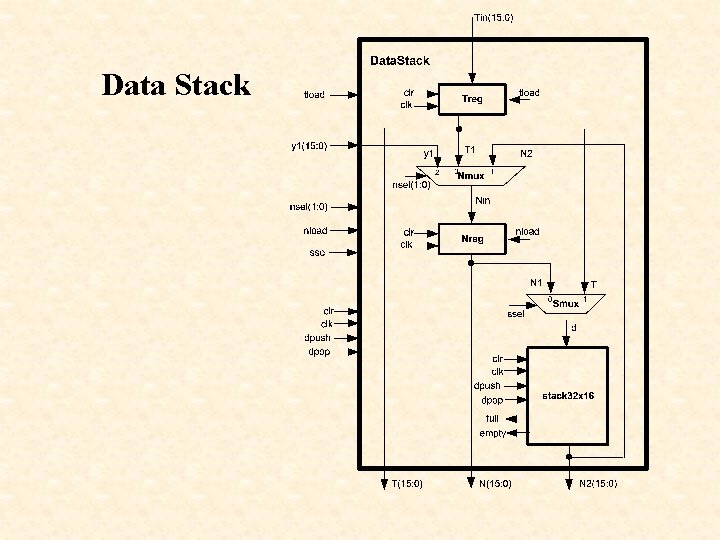

Data Stack Lab 7 A 32 x 16

Data Stack Lab 7

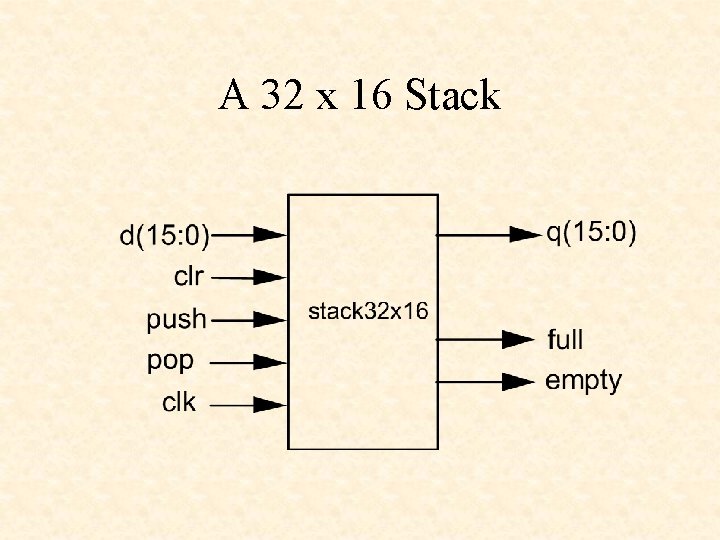

A 32 x 16 Stack

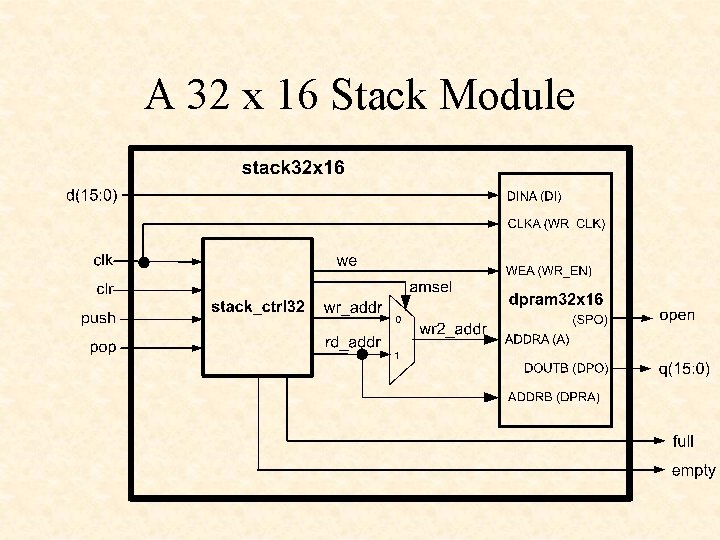

A 32 x 16 Stack Module

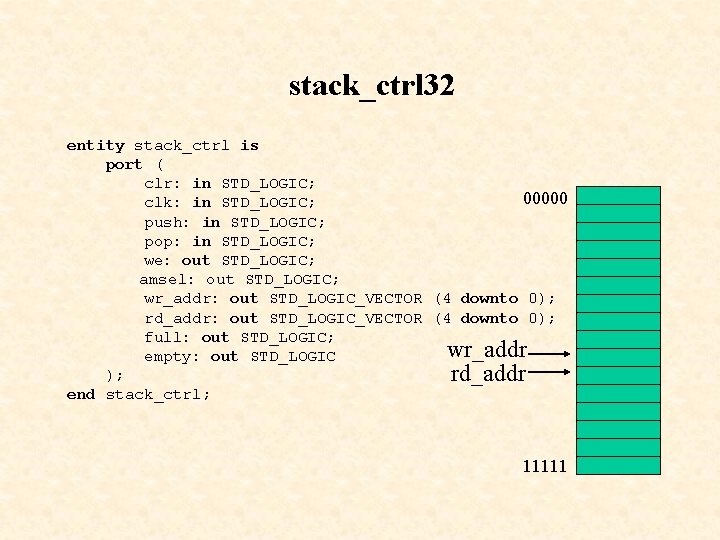

stack_ctrl 32 entity stack_ctrl is port ( clr: in STD_LOGIC; 00000 clk: in STD_LOGIC; push: in STD_LOGIC; pop: in STD_LOGIC; we: out STD_LOGIC; amsel: out STD_LOGIC; wr_addr: out STD_LOGIC_VECTOR (4 downto 0); rd_addr: out STD_LOGIC_VECTOR (4 downto 0); full: out STD_LOGIC; wr_addr empty: out STD_LOGIC ); rd_addr end stack_ctrl; 11111

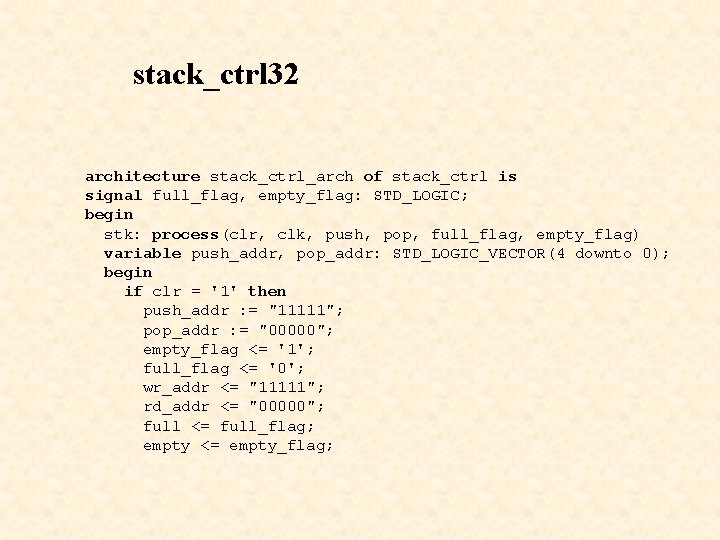

stack_ctrl 32 architecture stack_ctrl_arch of stack_ctrl is signal full_flag, empty_flag: STD_LOGIC; begin stk: process(clr, clk, push, pop, full_flag, empty_flag) variable push_addr, pop_addr: STD_LOGIC_VECTOR(4 downto 0); begin if clr = '1' then push_addr : = "11111"; pop_addr : = "00000"; empty_flag <= '1'; full_flag <= '0'; wr_addr <= "11111"; rd_addr <= "00000"; full <= full_flag; empty <= empty_flag;

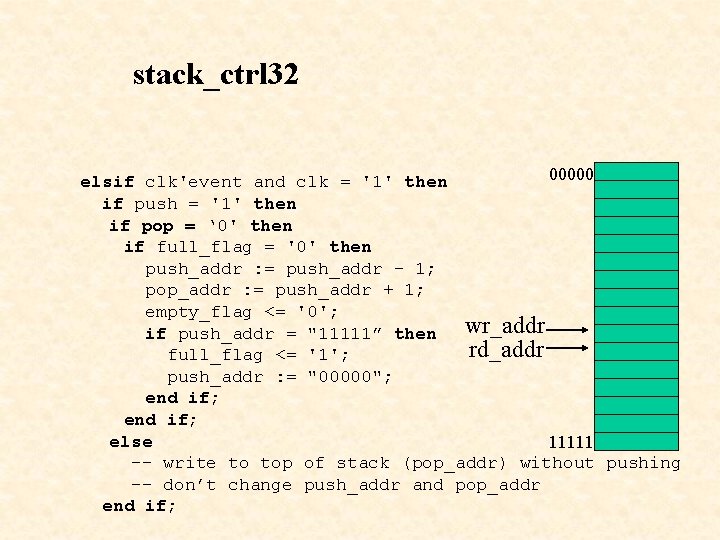

stack_ctrl 32 00000 elsif clk'event and clk = '1' then if push = '1' then if pop = ‘ 0' then if full_flag = '0' then push_addr : = push_addr - 1; pop_addr : = push_addr + 1; empty_flag <= '0'; wr_addr if push_addr = "11111” then rd_addr full_flag <= '1'; push_addr : = "00000"; end if; else 11111 –- write to top of stack (pop_addr) without pushing -- don’t change push_addr and pop_addr end if;

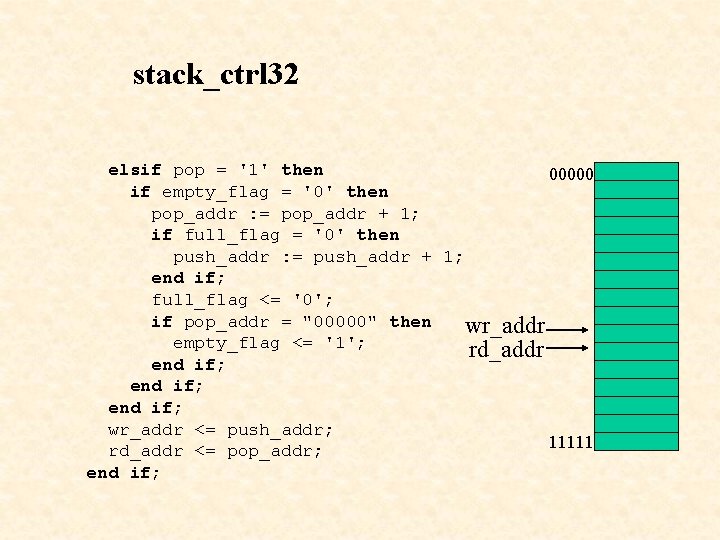

stack_ctrl 32 elsif pop = '1' then 00000 if empty_flag = '0' then pop_addr : = pop_addr + 1; if full_flag = '0' then push_addr : = push_addr + 1; end if; full_flag <= '0'; if pop_addr = "00000" then wr_addr empty_flag <= '1'; rd_addr end if; wr_addr <= push_addr; 11111 rd_addr <= pop_addr; end if;

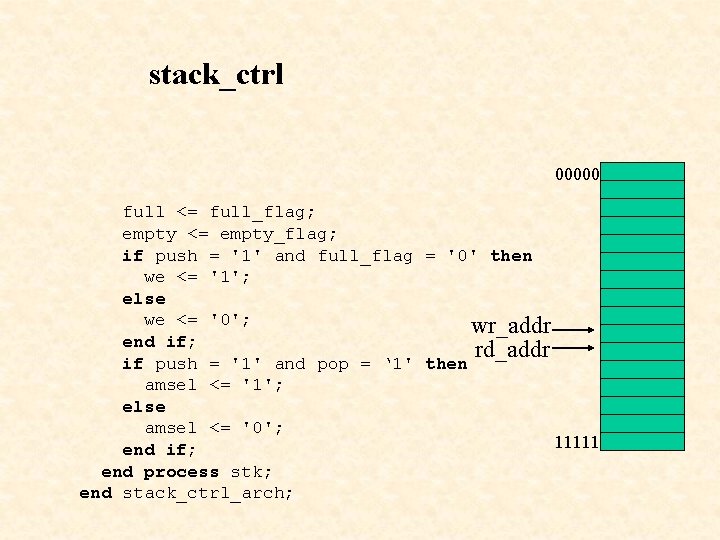

stack_ctrl 00000 full <= full_flag; empty <= empty_flag; if push = '1' and full_flag = '0' then we <= '1'; else we <= '0'; wr_addr end if; rd_addr if push = '1' and pop = ‘ 1' then amsel <= '1'; else amsel <= '0'; 11111 end if; end process stk; end stack_ctrl_arch;

A 32 x 16 Stack Module

Data Stack

- Slides: 10