DATA PATH fetch and execute cycle Organisasi Prosesor

![Eksekusi instruksi yang ukurannya tetap do { 1. IR [[PC]] // Fetch instruksi 2. Eksekusi instruksi yang ukurannya tetap do { 1. IR [[PC]] // Fetch instruksi 2.](https://slidetodoc.com/presentation_image/8def4d9c3cceed62f61d9a5b4760d3d3/image-4.jpg)

![Mengambil Data dari Memori Read Instruksi: MOV R 2, [R 1] ; R 2 Mengambil Data dari Memori Read Instruksi: MOV R 2, [R 1] ; R 2](https://slidetodoc.com/presentation_image/8def4d9c3cceed62f61d9a5b4760d3d3/image-8.jpg)

![Menyimpan Data ke Memori Write Instruksi: MOV [R 1], R 2 ; [R 1] Menyimpan Data ke Memori Write Instruksi: MOV [R 1], R 2 ; [R 1]](https://slidetodoc.com/presentation_image/8def4d9c3cceed62f61d9a5b4760d3d3/image-9.jpg)

![Tahapan Eksekusi Instruksi: Add. R 1, [R 3] ; R 1 [R 1] + Tahapan Eksekusi Instruksi: Add. R 1, [R 3] ; R 1 [R 1] +](https://slidetodoc.com/presentation_image/8def4d9c3cceed62f61d9a5b4760d3d3/image-11.jpg)

- Slides: 16

DATA PATH fetch and execute cycle

Organisasi Prosesor (Single-bus) Control lines Address lines Memory bus Data lines PC Instruction Decoder MAR IR MDR R 0 Y R(n-1) ALU control lines Add Sub ALU XOR Carry-in Z TEMP Control Unit Datapath Unit

• • • PC: MAR: MDR: ALU: IR: SP: Program Counter Memory Address Register Memory Data Register Arithmetic & Logic Unit Instruction Register Stack Pointer

![Eksekusi instruksi yang ukurannya tetap do 1 IR PC Fetch instruksi 2 Eksekusi instruksi yang ukurannya tetap do { 1. IR [[PC]] // Fetch instruksi 2.](https://slidetodoc.com/presentation_image/8def4d9c3cceed62f61d9a5b4760d3d3/image-4.jpg)

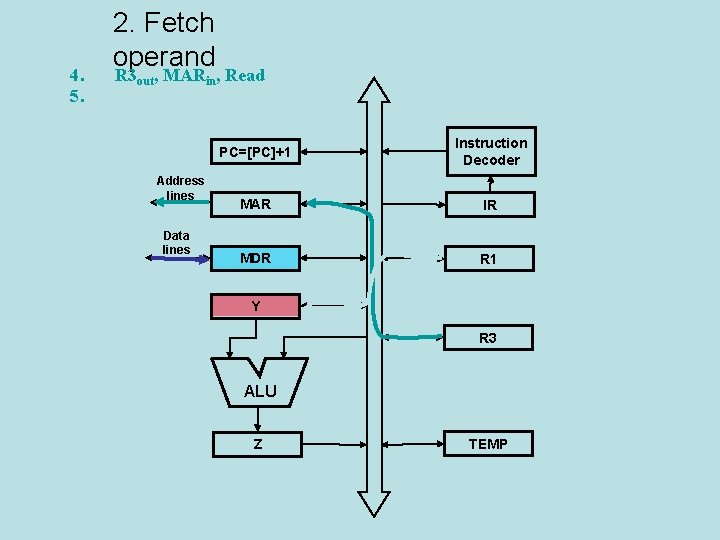

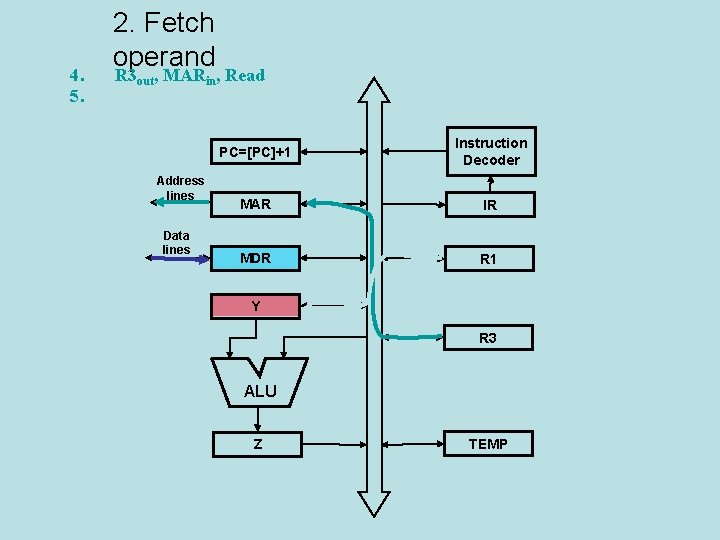

Eksekusi instruksi yang ukurannya tetap do { 1. IR [[PC]] // Fetch instruksi 2. PC [PC] + d // Tunjuk ke lokasi instruksi berikutnya 3. Eksekusi instruksi } while (!stop) Eksekusi instruksi yang ukurannya bervariasi do { // Fetch instruksi IR [[PC]] PC [PC] + d } while (!end-of-instruction) Eksekusi instruksi } while (!stop)

Operasi-operasi Dasar Dalam Eksekusi Instruksi • • Pertukaran Data Antar-Register Operasi Aritmatika & Logika di Datapath Mengambil (fetching) Data dari Memori Menyimpan (storing) Data ke Memori

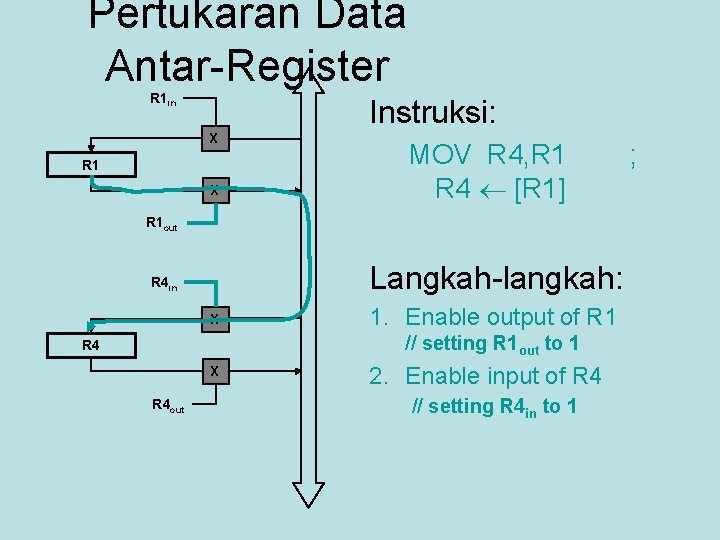

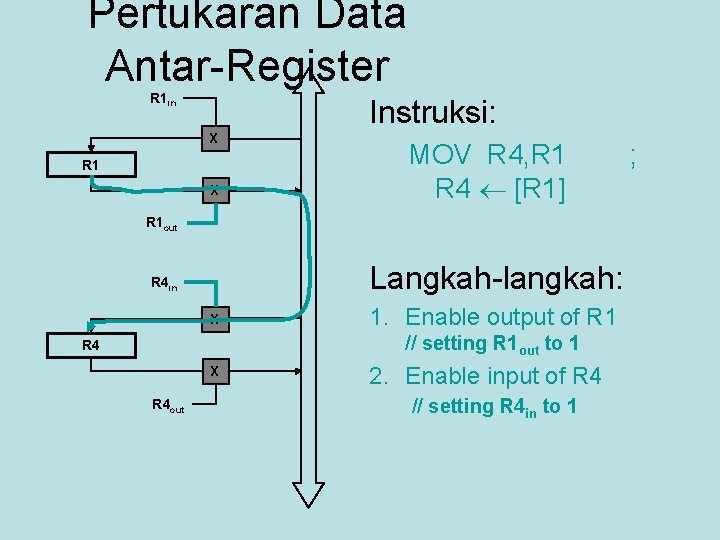

Pertukaran Data Antar-Register R 1 in Instruksi: X R 1 X MOV R 4, R 1 R 4 [R 1] R 1 out Langkah-langkah: R 4 in X 1. Enable output of R 1 // setting R 1 out to 1 R 4 X R 4 out 2. Enable input of R 4 // setting R 4 in to 1 ;

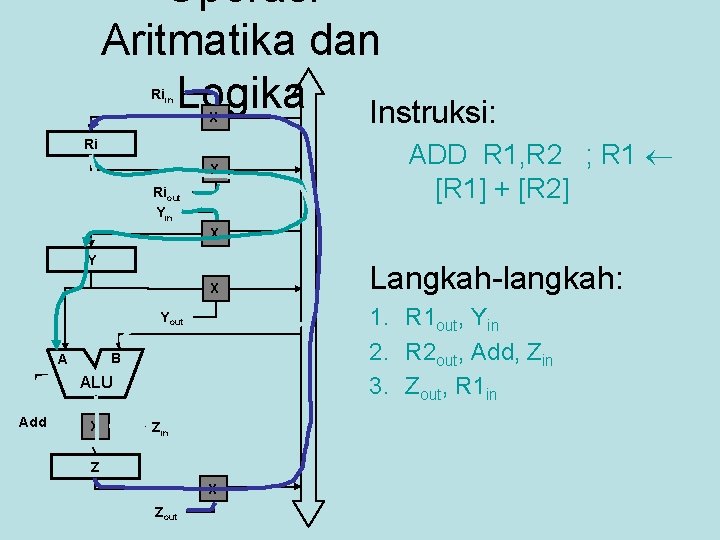

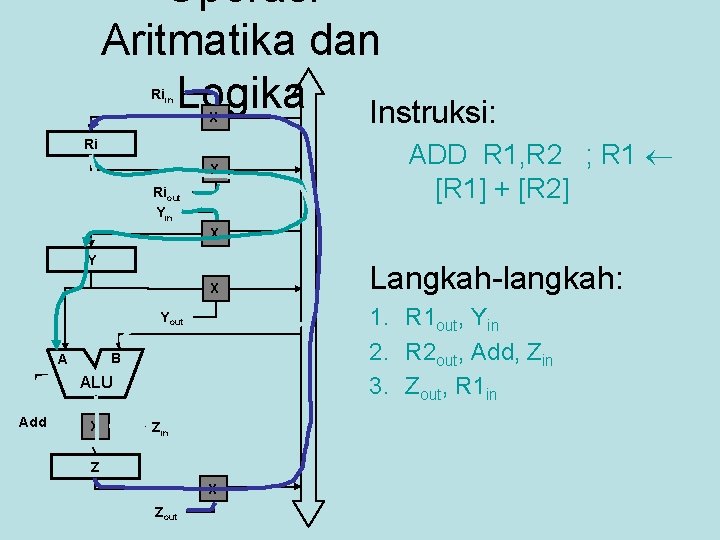

Operasi Aritmatika dan Logika Instruksi: Riin X Riout Yin ADD R 1, R 2 ; R 1 [R 1] + [R 2] X Y X 1. R 1 out, Yin 2. R 2 out, Add, Zin 3. Zout, R 1 in Yout B A ALU Add X Zin Z X Zout Langkah-langkah:

![Mengambil Data dari Memori Read Instruksi MOV R 2 R 1 R 2 Mengambil Data dari Memori Read Instruksi: MOV R 2, [R 1] ; R 2](https://slidetodoc.com/presentation_image/8def4d9c3cceed62f61d9a5b4760d3d3/image-8.jpg)

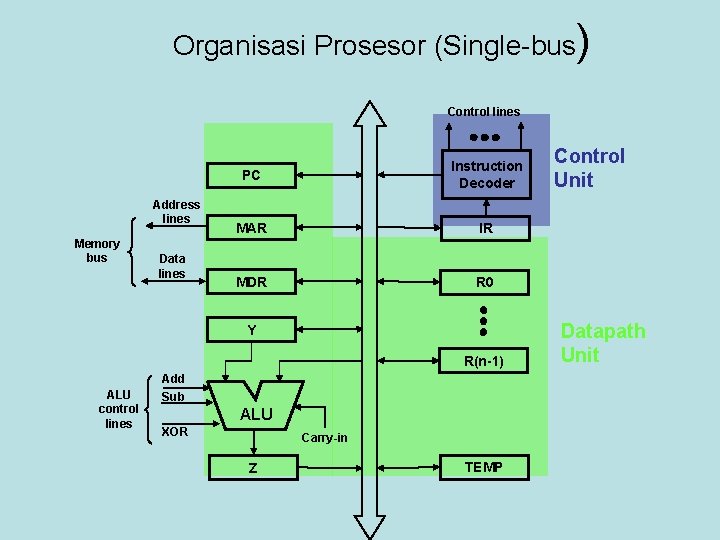

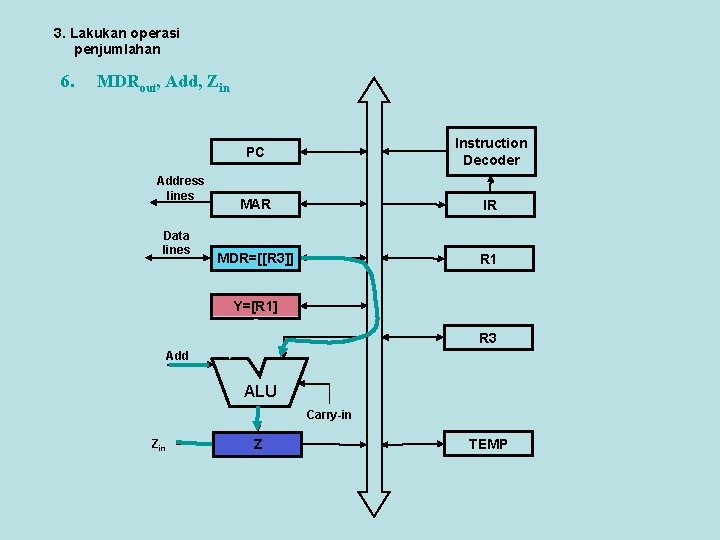

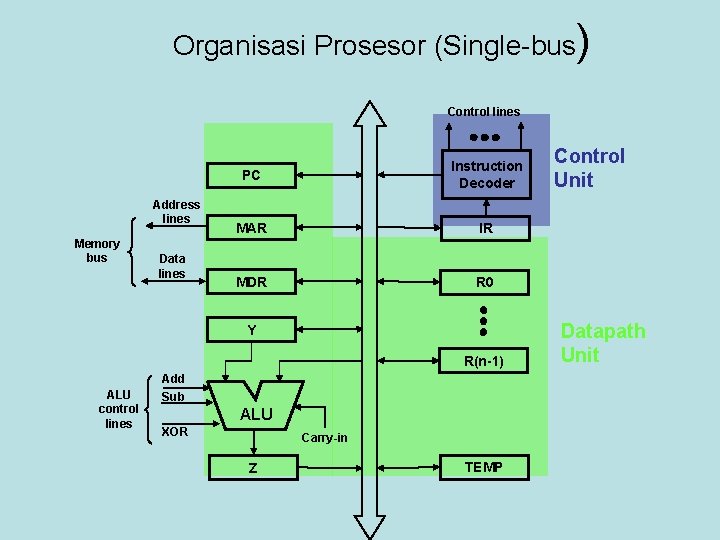

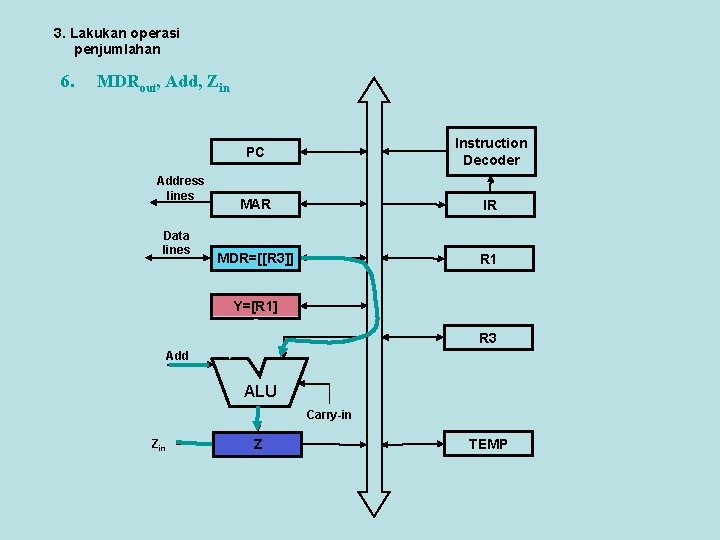

Mengambil Data dari Memori Read Instruksi: MOV R 2, [R 1] ; R 2 Address lines [[R 1]] Data lines Langkah-langkah: 1. MAR [R 1] 2. Read 3. Tunggu sinyal MFC // MFC = Memory Function Completed // Pada saat MFC aktif: // MDR M[MAR] 4. R 2 [MDR] MFC PC Instruction Decoder MAR IR MDR R 1 Y R 2 Add Sub ALU XOR Carry-in Z TEMP

![Menyimpan Data ke Memori Write Instruksi MOV R 1 R 2 R 1 Menyimpan Data ke Memori Write Instruksi: MOV [R 1], R 2 ; [R 1]](https://slidetodoc.com/presentation_image/8def4d9c3cceed62f61d9a5b4760d3d3/image-9.jpg)

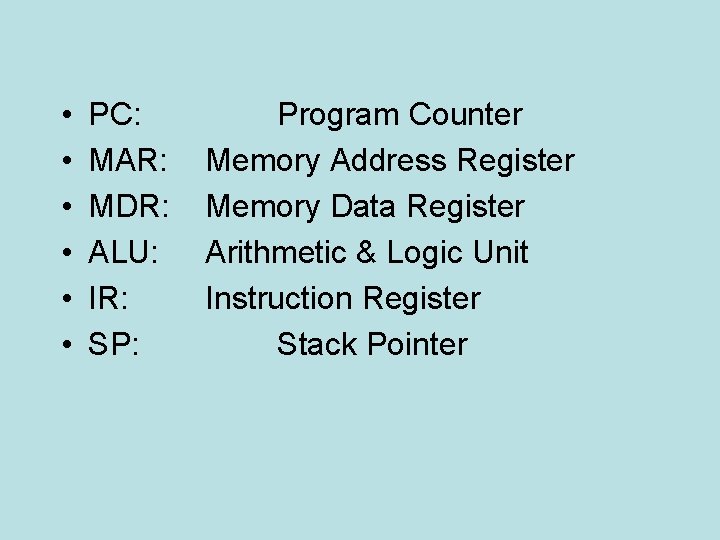

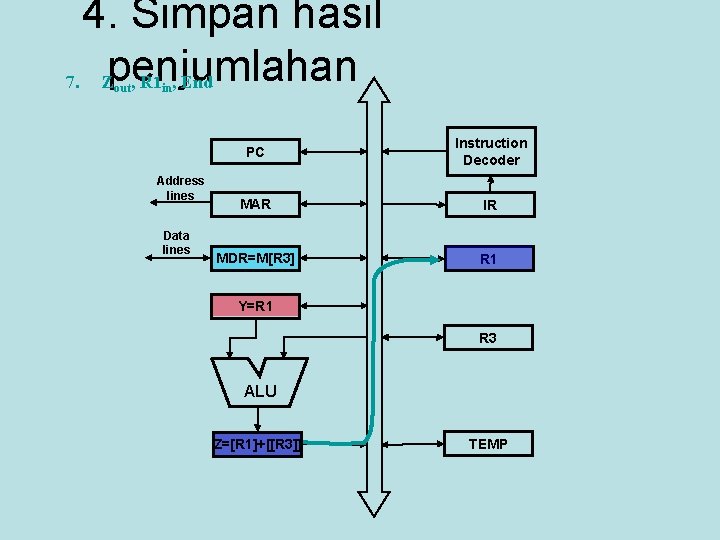

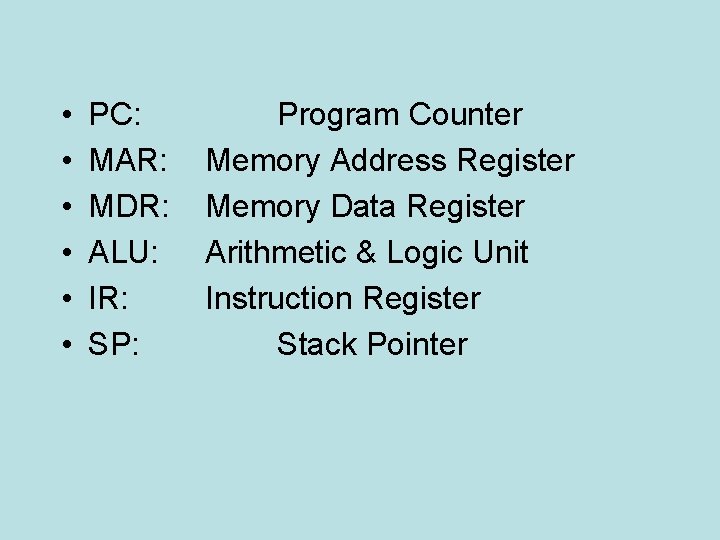

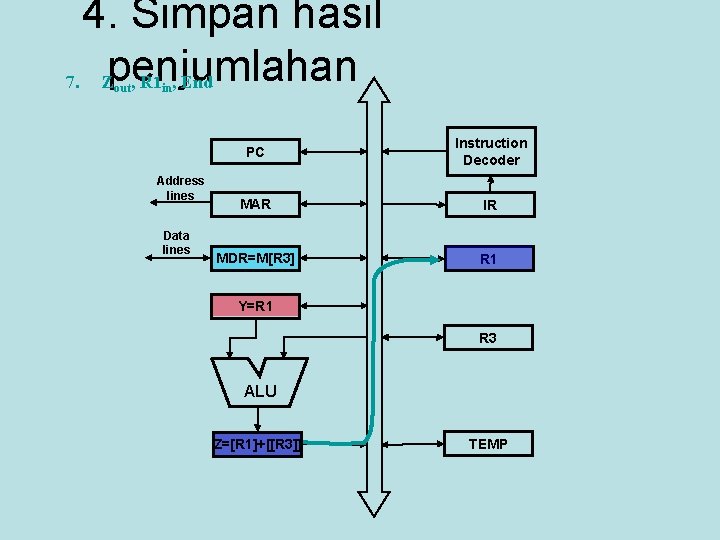

Menyimpan Data ke Memori Write Instruksi: MOV [R 1], R 2 ; [R 1] Address lines [R 2] Data lines Langkah-langkah: 1. MAR [R 1] 2. MDR [R 2], Write 3. Tunggu sinyal MFC // MFC = Memory Function Completed // Pada saat MFC aktif: // M[MAR] MDR MFC PC Instruction Decoder MAR IR MDR R 1 Y R 2 Add Sub ALU XOR Carry-in Z TEMP

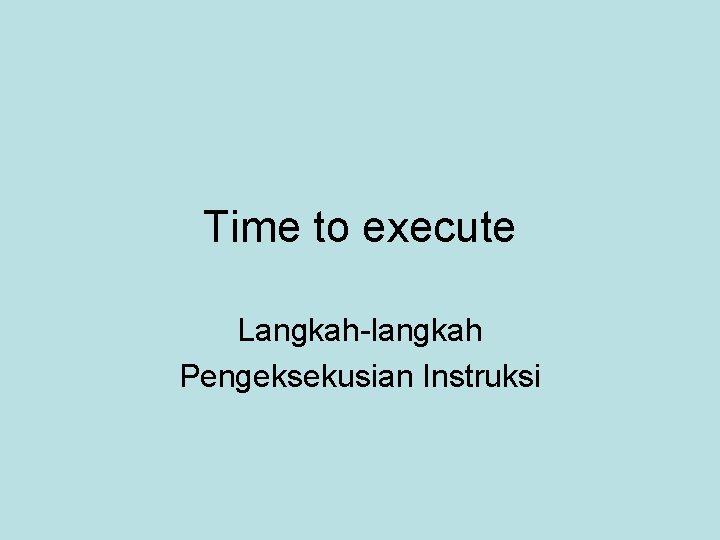

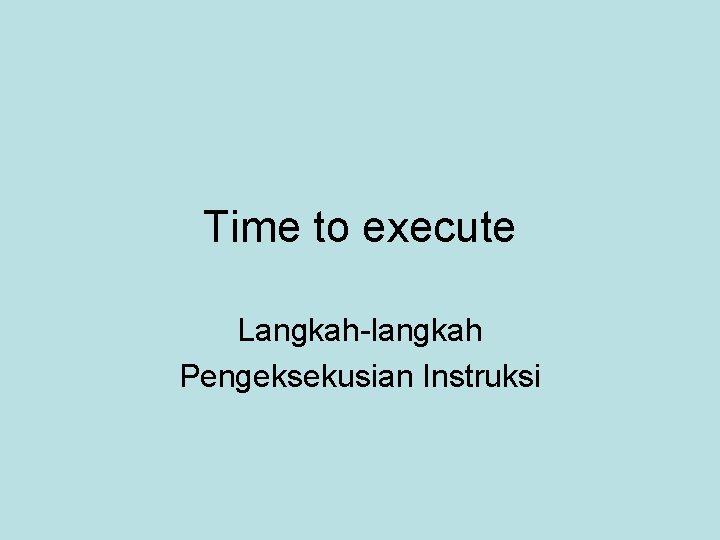

Time to execute Langkah-langkah Pengeksekusian Instruksi

![Tahapan Eksekusi Instruksi Add R 1 R 3 R 1 R 1 Tahapan Eksekusi Instruksi: Add. R 1, [R 3] ; R 1 [R 1] +](https://slidetodoc.com/presentation_image/8def4d9c3cceed62f61d9a5b4760d3d3/image-11.jpg)

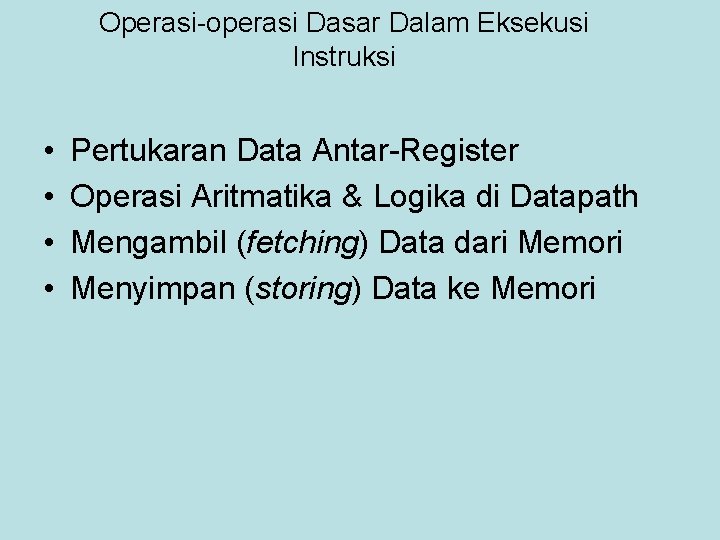

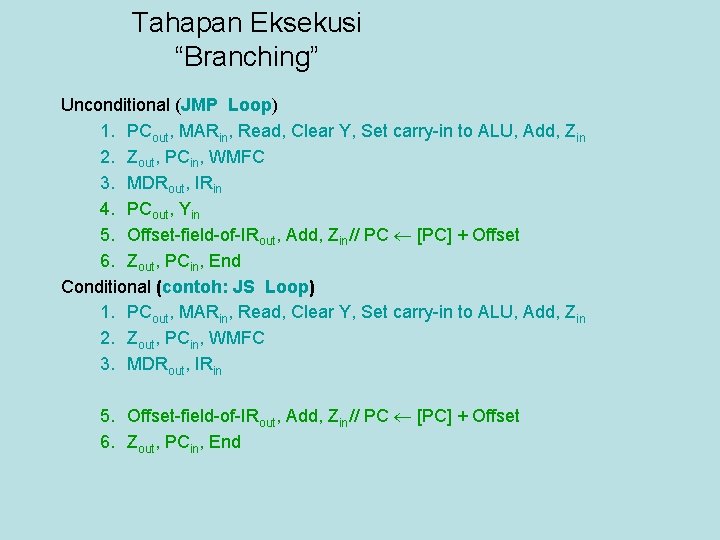

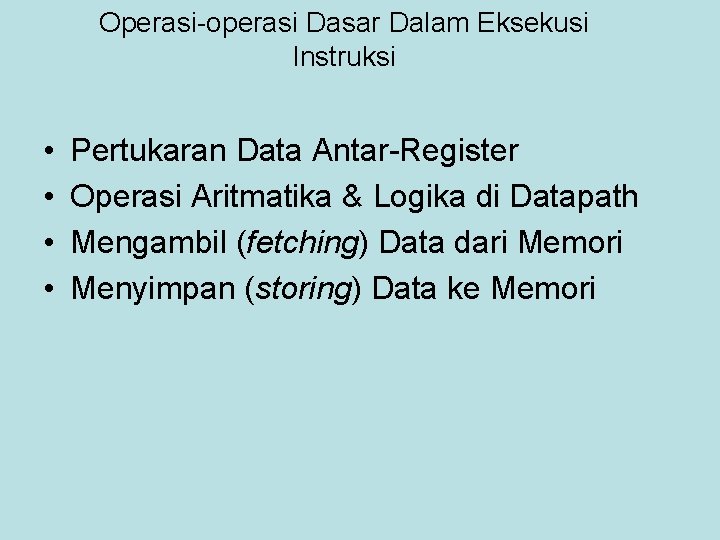

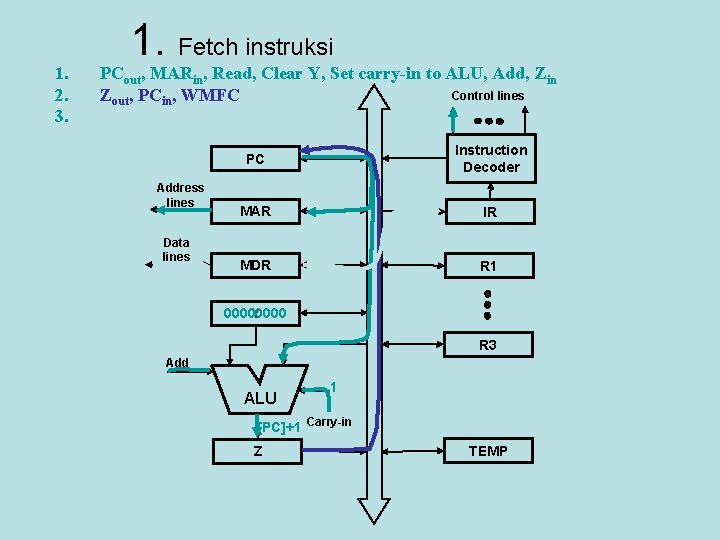

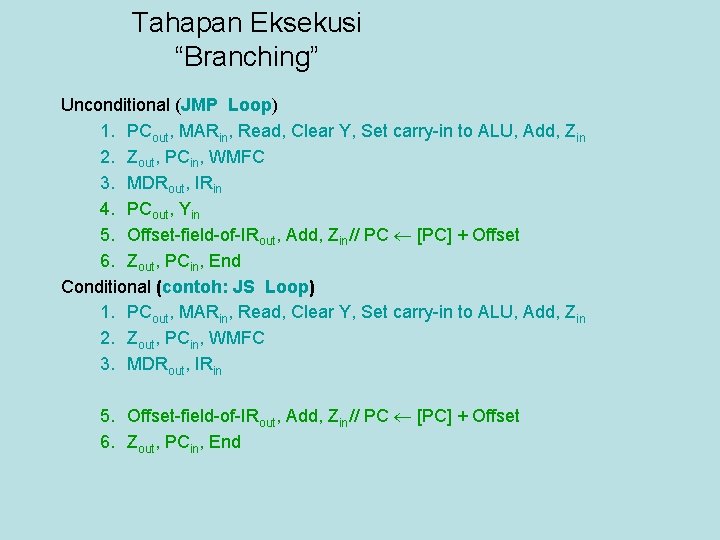

Tahapan Eksekusi Instruksi: Add. R 1, [R 3] ; R 1 [R 1] + [[R 3]] Langkah-langkah: 1. Fetch instruksi 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 2. Fetch operand (isi lokasi memori yg ditunjuk oleh R 3) 4. R 3 out, MARin, Read 5. R 1 out, Yin, WMFC 3. Lakukan operasi penjumlahan 6. MDRout, Add, Zin 4. Simpan hasil penjumlahan di R 1 7. Zout, R 1 in, End

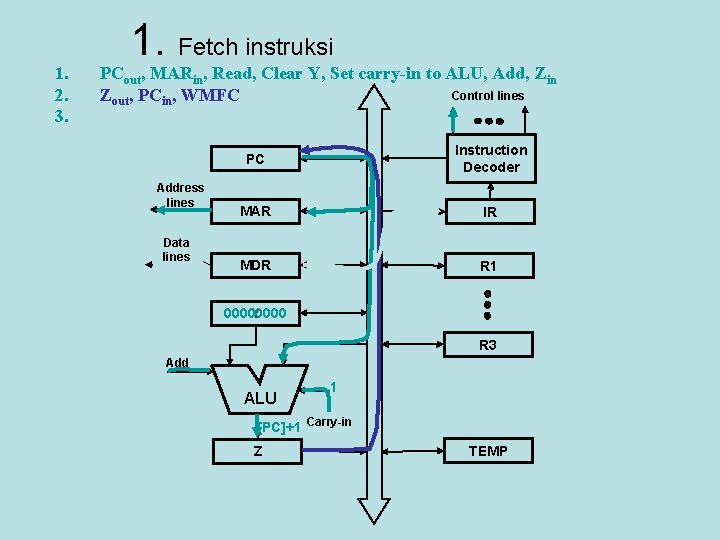

1. 2. 3. 1. Fetch instruksi PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin Control lines Zout, PCin, WMFC MDRout, IRin Address lines Data lines PC Instruction Decoder MAR IR MDR R 1 0000 Y R 3 Add ALU 1 [PC]+1 Carry-in Z TEMP

4. 5. 2. Fetch operand R 3 out, MARin, Read R 1 out, Yin, WMFC Address lines Data lines PC=[PC]+1 Instruction Decoder MAR IR MDR R 1 Y R 3 ALU Z TEMP

3. Lakukan operasi penjumlahan 6. MDRout, Add, Zin Address lines Data lines PC Instruction Decoder MAR IR MDR=[[R 3]] R 1 Y=[R 1] R 3 Add ALU Carry-in Z TEMP

4. Simpan hasil 7. Zpenjumlahan , R 1 , End out in Address lines Data lines PC Instruction Decoder MAR IR MDR=M[R 3] R 1 Y=R 1 R 3 ALU Z=[R 1]+[[R 3]] TEMP

Tahapan Eksekusi “Branching” Unconditional (JMP Loop) 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. PCout, Yin 5. Offset-field-of-IRout, Add, Zin // PC [PC] + Offset 6. Zout, PCin, End Conditional (contoh: JS Loop) 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. PCout, Yin , If SF=0 then End// take the branch? 5. Offset-field-of-IRout, Add, Zin // PC [PC] + Offset 6. Zout, PCin, End