Data Object Types A VHDL object consists of

Data Object Types A VHDL object consists of one of the following: –Signal, Which represents interconnection wires that connect component instantiation ports together. –Variable, Which is used for local storage of temporary data, visible only inside a process. –Constant, which names specific values. 1

Objects • Objects are used to represent & store the data in the system being described in VHDL. • Object contains a value of a specific type. • The name given to object is called identifier. • Each object has a type & class. – Class indicates how the object is used in the model & what can be done with the object. – Type indicates what type of data the object contains. 2

Every data object belongs to one of the following three classes: 1. Constant: An object of constant cla^s can hold a single value of a given type. This value is assigned to the object before simulation starts and the value cannot be changed during the course of the simulation. 2. Variable: An object of variable class can also hold a single value of a given type. However in this case, different values can be assigned to the object at different times using a variable assignment statement. 3. Signal: An object belonging to the signal class has a past history of values, a current value, and a set of future values. Future values can be assigned to a signal object using a signal assignment statement. 3

• Signal objects can be regarded as wires in a circuit while variable and constant objects are analogous to their counterparts in a high -level programming language like C or Pascal. • Signal objects are typically used to model wires and flip-flops while variable and constant objects are typically used to model the behavior of the circuit. 4

Signal • Signal objects are used to connect entities together to form models. • Signals are the means for communication of dynamic data between entities. • A signal declaration looks like this: Signal_name : Signal_type [: = initial_value] The Keyword SIGNAL is followed by one or more signal names. 5

• Each Signal name creates a new signal. • Separating the signal names from the signal type is colon. • Signal type specifies the data type of the information that the signal contains. • The signal can contain an initial value specifier so that the signal value may initialized. • Signals can be declared in entity declaration sections, architecture declarations and package declarations. 6

• Signals in package declaration are also referred to as global signals because they can be shared among entities. • Each signal has a history of values I. e. holds a list of values which include current value of signal & set of possible future values that are to appear on the signal. • Computed value is assigned to signal after delay called ‘delta delay’. 7

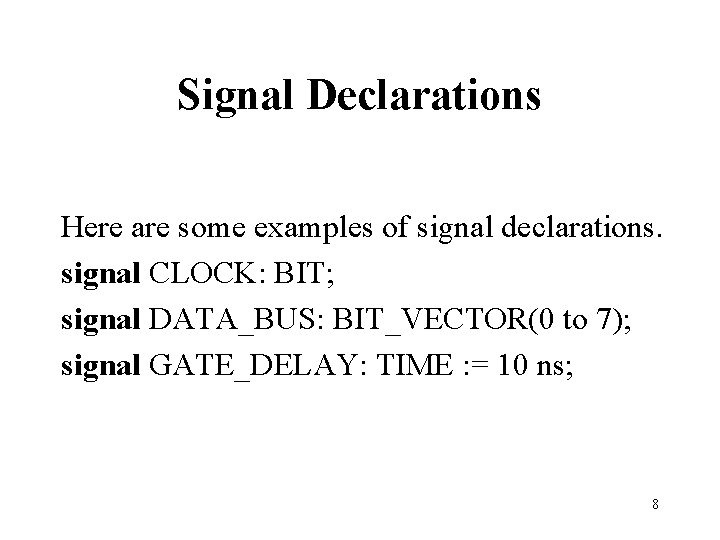

Signal Declarations Here are some examples of signal declarations. signal CLOCK: BIT; signal DATA_BUS: BIT_VECTOR(0 to 7); signal GATE_DELAY: TIME : = 10 ns; 8

Variable • Variable are used for local storage in process statements and subprograms. • All assignment to variable occur immediately. • A variable declaration looks like this: Variable variable_name: variable_type [: value] 9

• The keyword VARIABLE is followed by one or more variable names. • Each name creates a new variable. • The construct variable_type defines the data type of the variable, and an optional initial value can be specified. • Variable can be declared in the process declaration and subprogram declaration sections only. 10

• Variable are inherently more efficient because assignments happen immediately, while signals must be scheduled to occur. • Variables take less memory, while signals need more information to allow for scheduling and signal attributes. • Using a Signal would have required a WAIT statement to synchronize the signal assignment to the same execution iteration as the usage. 11

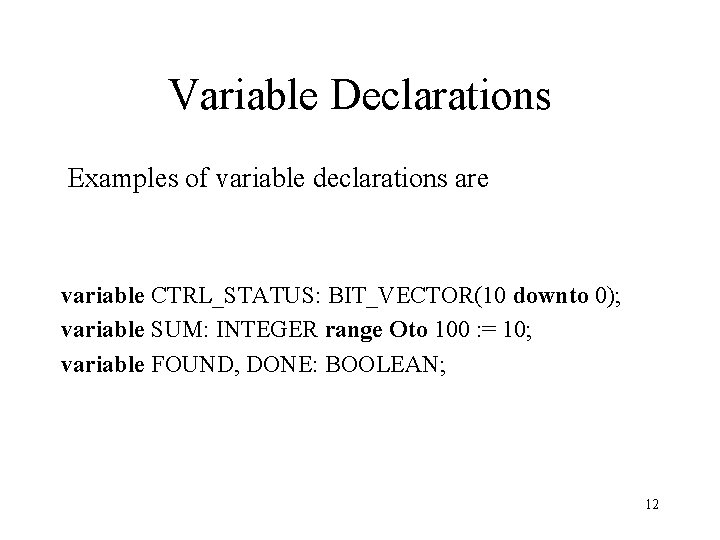

Variable Declarations Examples of variable declarations are variable CTRL_STATUS: BIT_VECTOR(10 downto 0); variable SUM: INTEGER range Oto 100 : = 10; variable FOUND, DONE: BOOLEAN; 12

Signal vs Variables • A Signal has three properties attached to it: type, value and time. while a variable has only two properties attached to it type and value. • Use signals as channels of communication between concurrent statement. In non-synthesizeable models, avoid using signals to describe storage elements. Use variable instead. • Signals occupy about two orders of magnitude more storage than variable during simulation. Signals also cost a performance penalty due to the simulation overhead necessary to maintain the data structures representing signals. 13

Constants • Constant objects are names assigned to specific values of a type. • Constants give the designer the ability to have a better-documented model, and a model that is easy to update. • Constant declaration : Constant constant_name : type_name [: value]; 14

Constant Declarations Examples of constant declarations are constant RISE_TIME: TIME : = 10 ns; constant BUS_WIDTH: INTEGER : = 8: An example of another form of constant declaration is constant NO_OF_INPUTS: INTEGER; The value of the constant has not been specified in this case. Such a constant is called a deferred constant and it can appear only inside a package declaration. 15

- Slides: 15